#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                     | Active                                                                                            |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A8                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 600MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                            |

| RAM Controllers                    | LPDDR, DDR2                                                                                       |

| Graphics Acceleration              | No                                                                                                |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                       |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 (3), USB 2.0 + PHY (1)                                                                    |

| Voltage - I/O                      | 1.2V, 1.875V, 2.775V, 3.0V                                                                        |

| Operating Temperature              | -40°C ~ 95°C (TC)                                                                                 |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 529-LFBGA                                                                                         |

| Supplier Device Package            | 529-BGA (19x19)                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx512cjm6c                                        |

|                                    |                                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal Name               | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMIC_INT_REQ              | When using the MC13892 power management IC, the PMIC_INT_REQ high-priority interrupt input<br>on i.MX51 should be either floated or tied to NVCC_SRTC_POW with a 4.7 k $\Omega$ to 68 k $\Omega$ resistor.<br>This avoids a continuous current drain on the real-time clock backup battery due to a 100 k $\Omega$<br>on-chip pull-up resistor.<br>PMIC_INT_REQ is not used by the Freescale BSP (board support package) software. The BSP<br>requires that the general-purpose INT output from the MC13892 be connected to the i.MX51 GPIO<br>input GPIO1_8 configured to cause an interrupt that is not high-priority.<br>The original intent was for PMIC_INT_REQ to be connected to a circuit that detects when the<br>battery is almost depleted. In this case, the I/O must be configured as alternate mode 0 (ALT0 =<br>power fail). |

| POR_B                     | This cold reset negative logic input resets all modules and logic in the IC.<br><b>Note:</b> The POR_B input must be immediately asserted at power-up and remain asserted until<br>after the last power rail is at its working voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RESET_IN_B                | <ul> <li>This warm reset negative logic input resets all modules and logic except for the following:</li> <li>Test logic (JTAG, IOMUXC, DAP)</li> <li>SRTC</li> <li>Memory repair – Configuration of memory repair per fuse settings</li> <li>Cold reset logic of WDOG – Some WDOG logic is only reset by POR_B. See WDOG chapter in <i>i.MX51 Multimedia Applications Processor Reference Manual</i> (MCIMX51RM) for details.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

| RREFEXT                   | Determines the reference current for the USB PHY bandgap reference. An external 6.04 k $\Omega$ 1% resistor to GND is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SGND, SVCC, and<br>SVDDGP | These sense lines provide the ability to sense actual on-chip voltage levels on their respective supplies. SGND monitors differentials of the on-chip ground versus an external power source. SVCC monitors on-chip VCC, and SVDDGP monitors VDDGP. Freescale recommends connection of the SVCC and SVDDGP signals to the feedback inputs of switching power-supplies or to test points.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| STR                       | This signal is reserved for Freescale manufacturing use. The user should float this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TEST_MODE                 | TEST_MODE is for Freescale factory use only. This signal is internally connected to an on-chip pull-down device. Users must either float this signal or tie it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VREF                      | When using VREF with DDR-2 I/O, the nominal 0.9 V reference voltage must be half of the NVCC_EMI_DRAM supply. The user must tie VREF to a precision external resistor divider. Use a 1 k $\Omega$ 0.5% resistor to GND and a 1 k $\Omega$ 0.5% resistor to NVCC_EMI_DRAM. Shunt each resistor with a closely-mounted 0.1 $\mu$ F capacitor.<br>To reduce supply current, a pair of 1.5 k $\Omega$ 0.1% resistors can be used. Using resistors with recommended tolerances ensures the ± 2% VREF tolerance (per the DDR-2 specification) is maintained when four DDR-2 ICs plus the i.MX51 are drawing current on the resistor divider.<br><b>Note:</b> When VREF is used with mDDR this signal must be tied to GND.                                                                                                                         |

| VREFOUT                   | This signal determines the Triple Video DAC (TVDAC) reference voltage. The user must tie VREFOUT to an external 1.05 k $\Omega$ 1% resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 44. AC Electrical Characteristics of DDR mobile IO Pads for Slow Mode and |

|---------------------------------------------------------------------------------|

| ovdd=1.65 – 1.95 V (ipp_hve=0) (continued)                                      |

| Parameter                                                        | Symbol | Test<br>Condition | Min<br>rise/fall | Тур         | Max<br>rise/fall | Units |

|------------------------------------------------------------------|--------|-------------------|------------------|-------------|------------------|-------|

| Output Pad di/dt (Low drive) <sup>1</sup>                        | di/dt  | —                 | 12               | 5           | 3                | mA/ns |

| Input Pad Transition Times <sup>2</sup>                          | trfi   | 1.2 pF            | 0.09/0.09        | 0.132/0.128 | 0.212/0.213      | ns    |

| Input Pad Propagation Delay (DDR input),<br>50%-50% <sup>2</sup> | tpi    | 1.2 pF            | 0.3/0.36         | 0.5/0.52    | 0.82/0.94        | _     |

| Maximum Input Transition Times <sup>3</sup>                      | trm    | —                 | _                | —           | 5                | ns    |

<sup>1</sup> Max condition for tpr, tpo, tps and didt: wcs model, 1.1 V, IO 1.65 V, 105 °C and s0-s5=111111. Typ condition for tpr, tpo, tps and didt: typ model, 1.2 V, IO 1.8 V, 25 °C and s0-s5=101010. Min condition for tpr, tpo, tps and didt: bcs model, 1.3 V, IO 1.95 V, -40 °C and s0-s5=000000.

<sup>2</sup> Max condition for trfi and tpi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Typ condition for trfi and tpi: typ model, 1.2 V, IO 1.8 V and 25 °C. Min condition for trfi and tpi: bcs model, 1.3 V, IO 1.95 V and -40 °C.

<sup>3</sup> Hysteresis mode is recommended for input with transition time greater than 25 ns.

# 4.6 Module Timing

This section contains the timing and electrical parameters for the modules in the i.MX51 processor.

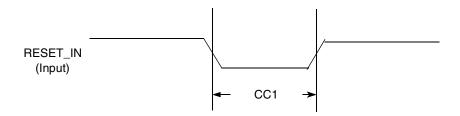

# 4.6.1 Reset Timings Parameters

Figure 12 shows the reset timing and Table 45 lists the timing parameters.

Figure 12. Reset Timing Diagram

**Table 45. Reset Timing Parameters**

| ID  | Parameter                                                          | Min | Max | Unit |

|-----|--------------------------------------------------------------------|-----|-----|------|

| CC1 | Duration of RESET_IN to be qualified as valid (input slope = 5 ns) | 50  | _   | ns   |

# 4.6.5 **DPLL Electrical Parameters**

Table 48 shows the DPLL electrical parameters.

| Table 48. DPLL Electrical Parameters |

|--------------------------------------|

|--------------------------------------|

| Parameter                                                        | Test Conditions/Remarks                                                                                                                                    | Min       | Тур  | Мах                                                     | Unit                 |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|---------------------------------------------------------|----------------------|

| Reference clock frequency range <sup>1</sup>                     | _                                                                                                                                                          | 10        |      | 100                                                     | MHz                  |

| Reference clock frequency range after pre-divider                | _                                                                                                                                                          | 10        | _    | 40                                                      | MHz                  |

| Output clock frequency range (dpdck_2)                           | _                                                                                                                                                          | 300       | _    | 1025                                                    | MHz                  |

| Pre-division factor <sup>2</sup>                                 | _                                                                                                                                                          | 1         | —    | 16                                                      |                      |

| Multiplication factor integer part                               | —                                                                                                                                                          | 5         | _    | 15                                                      |                      |

| Multiplication factor numerator <sup>3</sup>                     | Should be less than denominator                                                                                                                            | -67108862 | —    | 67108862                                                |                      |

| Multiplication factor denominator <sup>2</sup>                   | —                                                                                                                                                          | 1         | _    | 67108863                                                |                      |

| Output Duty Cycle                                                | —                                                                                                                                                          | 48.5      | 50   | 51.5                                                    | %                    |

| Frequency lock time <sup>4</sup><br>(FOL mode or non-integer MF) | —                                                                                                                                                          | —         | —    | 398                                                     | T <sub>d</sub> pdref |

| Phase lock time                                                  | _                                                                                                                                                          | —         | —    | 100                                                     | μs                   |

| Frequency jitter <sup>5</sup> (peak value)                       | —                                                                                                                                                          | —         | 0.02 | 0.04                                                    | T <sub>dck</sub>     |

| Phase jitter (peak value)                                        | FPL mode, integer and fractional MF                                                                                                                        | —         | 2.0  | 3.5                                                     | ns                   |

| Power dissipation                                                | $f_{dck} = 300 \text{ MHz} @ \text{ avdd} = 1.8 \text{ V},$<br>dvdd = 1.2 V<br>$f_{dck} = 650 \text{ MHz} @ \text{ avdd} = 1.8 \text{ V},$<br>dvdd = 1.2 V | _         | _    | 0.65 (avdd)<br>0.92 (dvdd)<br>1.98 (avdd)<br>1.8 (dvdd) | mW                   |

<sup>1</sup> Device input range cannot exceed the electrical specifications of the CAMP, see Table 47.

<sup>2</sup> The values specified here are internal to DPLL. Inside the DPLL, a "1" is added to the value specified by the user. Therefore, the user has to enter a value "1" less than the desired value at the inputs of DPLL for PDF and MFD.

<sup>3</sup> The maximum total multiplication factor (MFI + MFN/MFD) allowed is 15. Therefore, if the MFI value is 15, MFN value must be zero.

<sup>4</sup> T<sub>dpdref</sub> is the time period of the reference clock after predivider.According to the specification, the maximum lock time in FOL mode is 398 cycles of divided reference clock when DPLL starts after full reset.

<sup>5</sup> Tdck is the time period of the output clock, dpdck\_2.

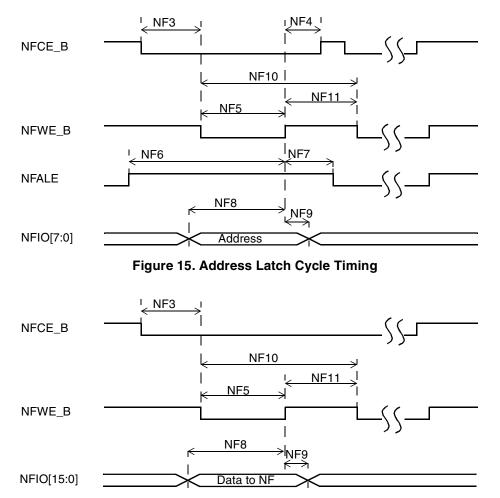

# 4.6.6 NAND Flash Controller (NFC) Parameters

This section provides the relative timing requirements among different signals of NFC at the module level in the different operational modes.

Timing parameters in Figure 14, Figure 15, Figure 16, Figure 17, Figure 19, and Table 50 show the default NFC mode (asymmetric mode) using two Flash clock cycles per one access of RE\_B and WE\_B. Timing parameters in Figure 14, Figure 15, Figure 16, Figure 18, Figure 19, and Table 50 show symmetric NFC mode using one Flash clock cycle per one access of RE\_B and WE\_B.

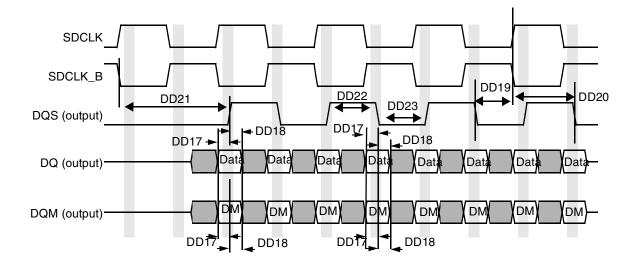

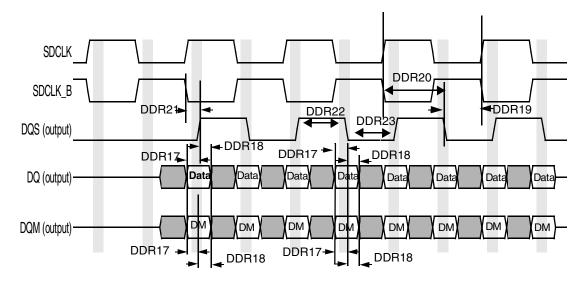

Figure 33 shows the timing diagram for mDDR SDRAM write cycle. The timing parameters for this diagram is shown in Table 56.

Figure 33. mDDR SDRAM Write cycle Timing Diagram

| ID   | Parameter                                                  | Symbol           | 200 MHz <sup>2</sup> |      | 166 MHz |      | 133 MHz |      | Unit |

|------|------------------------------------------------------------|------------------|----------------------|------|---------|------|---------|------|------|

|      | Falanciel                                                  | Symbol           | Min                  | Max  | Min     | Max  | Min     | Max  | Unit |

| DD17 | DQ and DQM setup time to DQS                               | tDS <sup>3</sup> | 0.48                 | —    | 0.6     | —    | 0.8     | _    | ns   |

| DD18 | DQ and DQM hold time to DQS                                | tdh1             | 0.48                 | _    | 0.6     | —    | 0.8     |      | ns   |

| DD19 | Write cycle DQS falling edge to<br>SDCLK output setup time | tDSS             | 0.2                  | —    | 0.2     | —    | 0.2     | -    | tCK  |

| DD20 | Write cycle DQS falling edge to<br>SDCLK output hold time  | tDSH             | 0.2                  | —    | 0.2     | —    | 0.2     | _    | tCK  |

| DD21 | Write command to first DQS latching transition             | tDQSS            | 0.75                 | 1.25 | 0.75    | 1.25 | 0.75    | 1.25 | tCK  |

| DD22 | DQS high level width                                       | <b>t</b> DQSH    | 0.4                  | 0.6  | 0.4     | 0.6  | 0.4     | 0.6  | tCK  |

| DD23 | DQS low level width                                        | tDQSL            | 0.4                  | 0.6  | 0.4     | 0.6  | 0.4     | 0.6  | tCK  |

Table 56. mDDR SDRAM Write Cycle Parameter Table<sup>1</sup>

<sup>1</sup> Test conditions are: Capacitance 15 pF for DDR PADS. Recommended drive strengths is medium for SDCLK and high for address and controls.

<sup>2</sup> SDRAM CLK and DQS related parameters are being measured from the 50% point. that is, high is defined as 50% of signal value and low is defined as 50% as signal value. DDR SDRAM CLK parameters are measured at the crossing point of SDCLK and SDCLK (inverted clock).

<sup>3</sup> This parameter is affected by pad timing. If the slew rate is < 1 V/ns, 0.1 ns should be increased to this value.

- <sup>1</sup> Test conditions are: Capacitance 15 pF for DDR contacts. Recommended drive strengths: Medium for SDCLK and High for address and controls.

- <sup>2</sup> SDCLK and DQS related parameters are measured from the 50% point. For example, a high is defined as 50% of the signal value and a low is defined as 50% of the signal value. DDR SDRAM CLK parameters are measured at the crossing point of SDCLK and SDCLK\_B.

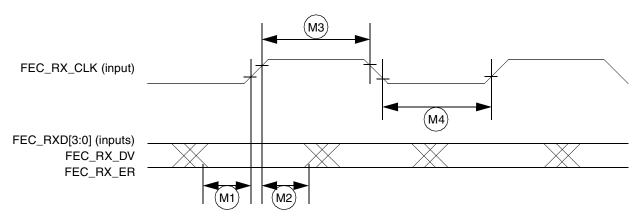

Figure 36 shows the timing diagram for DDR2 SDRM write cycle. The timing parameters for this diagram appear in Table 60.

Figure 36. DDR2 SDRAM Write Cycle Timing Diagram

| ID    | Parameter                                                 | Symbol | SDCLK =          | Unit |      |

|-------|-----------------------------------------------------------|--------|------------------|------|------|

|       | Falanelei                                                 |        | Min              | Max  | Unit |

| DDR17 | DQ & DQM setup time to DQS                                | tDS    | 0.8 <sup>1</sup> | —    | ns   |

| DDR18 | DQ & DQM hold time to DQS                                 |        | 0.8 <sup>2</sup> | —    | ns   |

| DDR19 | DQS falling edge to SDCLK output setup time               |        | 1.6              | —    | ns   |

| DDR20 | DQS falling edge SDCLK output hold time                   |        | 2.4              | —    | ns   |

| DDR21 | DQS latching rising transitions to associated clock edges |        | -0.7             | 0.3  | ns   |

| DDR22 | DQS high level width                                      |        | 0.35             | —    | tCK  |

| DDR23 | DQS low level width                                       | tDQSL  | 0.35             | —    | tCK  |

## Table 60. DDR2 SDRAM Write Cycle Parameter Table

<sup>1</sup> - In order to meet these setup/hold values, write calibration should be performed to place the DQS in the middle of DQ window. The minimum window width is 1.6ns (DDR17+DDR18).

- From DDR controller perspective, the timing is the same for both differential and single ended mode.

<sup>2</sup> - In order to meet these setup/hold values, write calibration should be performed to place the DQS in the middle of DQ window. The minimum window width is 1.6ns (DDR17+DDR18).

- From DDR controller perspective, the timing is the same for both differential and single ended mode.

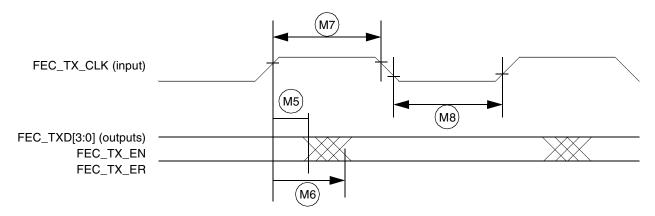

Figure 43. MII Receive Signal Timing Diagram

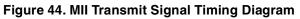

## 4.7.4.2 MII Transmit Signal Timing

The MII transmit signal timing affects the FEC\_TXD[3:0], FEC\_TX\_EN, FEC\_TX\_ER, and FEC\_TX\_CLK signals. The transmitter functions correctly up to a FEC\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed twice the FEC\_TX\_CLK frequency. Table 71 lists MII transmit channel timing parameters and Figure 44 shows MII transmit signal timing diagram for the values listed in Table 71.

| Num | Characteristic <sup>1</sup>                              | Min | Max | Unit              |

|-----|----------------------------------------------------------|-----|-----|-------------------|

| M5  | FEC_TX_CLK to FEC_TXD[3:0], FEC_TX_EN, FEC_TX_ER invalid | 5   | _   | ns                |

| M6  | FEC_TX_CLK to FEC_TXD[3:0], FEC_TX_EN, FEC_TX_ER valid   | _   | 20  | ns                |

| M7  | FEC_TX_CLK pulse width high                              | 35% | 65% | FEC_TX_CLK period |

| M8  | FEC_TX_CLK pulse width low                               | 35% | 65% | FEC_TX_CLK period |

Table 71. MII Transmit Signal Timing

FEC\_TX\_EN, FEC\_TX\_CLK, and FEC\_TXD0 have the same timing in 10 Mbps 7-wire interface mode.

| i.MX51 Applications Proces | sors for Consumer and | Industrial Products, Rev. 6 |

|----------------------------|-----------------------|-----------------------------|

|----------------------------|-----------------------|-----------------------------|

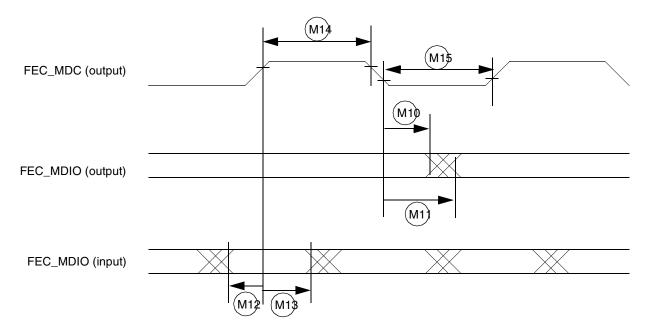

Figure 46. MII Serial Management Channel Timing Diagram

# 4.7.5 Frequency Pre-Multiplier (FPM) Electrical Parameters (CKIL)

The FPM is a DPLL that converts a signal operating in the kilohertz region into a clock signal operating in the megahertz region. The output of the FPM provides the reference frequency for the on-chip DPLLs. Parameters of the FPM are listed in Table 74.

| Parameter                                                              | Min | Тур    | Max   | Unit |

|------------------------------------------------------------------------|-----|--------|-------|------|

| Reference clock frequency range—CKIL                                   | 32  | 32.768 | 256   | kHz  |

| FPM output clock frequency range                                       | 8   | _      | 33    | MHz  |

| FPM multiplication factor (test condition is changed by a factor of 2) | 128 | —      | 1024  |      |

| Lock-in time <sup>1</sup>                                              | —   | —      | 312.5 | μs   |

| Cycle-to-cycle frequency jitter (peak to peak)                         | —   | 8      | 20    | ns   |

Table 74. FPM Specifications

plrf = 1 cycle assumed missed + x cycles for reset deassert + y cycles for calibration and lock x[ts] = {2,3,5,9};

$y[ts] = \{7, 8, 10, 14\};$  where ts is the chosen time scale of the reference clock. In this case reference clock = 32 kHz which makes ts = 0, therefore total time required for achieving lock is 10(1+2+7) cycles or  $312.5 \ \mu$ s.

# 4.7.6 High-Speed I<sup>2</sup>C (HS-I<sup>2</sup>C) Timing Parameters

This section describes the timing parameters of the HS-I<sup>2</sup>C module. This module can operate in the following modes: Standard, Fast and High speed.

## NOTE

See the errata for the HS-I<sup>2</sup>C module in the i.MX51 Chip Errata. There are two standard I<sup>2</sup>C modules that have no errata.

## 4.7.8.6.1 TV Encoder Performance Specifications

All the parameters in the table are defined under the following conditions:

Rset = 1.05 k $\Omega$  ±1%, resistor on VREFOUT pin to Ground

Rload =  $37.5 \Omega \pm 1\%$ , output load to Ground

The TV encoder output specifications are shown in Table 82.

### Table 82. TV Encoder Video Performance Specifications

| Parameter                                     | Conditions                                                 | Min  | Min Typ |      | Unit     |  |

|-----------------------------------------------|------------------------------------------------------------|------|---------|------|----------|--|

| DAC STATIC PERFORMANCE                        | 1 1                                                        |      |         |      |          |  |

| Resolution <sup>1</sup>                       | —                                                          | _    | 10      | —    | Bits     |  |

| Integral Nonlinearity (INL) <sup>2</sup>      | —                                                          | —    | 1       | 2    | LSBs     |  |

| Differential Nonlinearity (DNL) <sup>2</sup>  | —                                                          | —    | 0.6     | 1    | LSBs     |  |

| Channel-to-channel gain matching <sup>2</sup> | —                                                          | _    | 2       | —    | %        |  |

| Full scale output voltage <sup>2</sup>        | Rset = 1.05 kΩ ±1%<br>Rload = 37.5 Ω±1%                    | 1.24 | 1.35    | 1.45 | V        |  |

| DAC DYNAMIC PERFORMANCE                       |                                                            |      |         |      | 1        |  |

| Spurious Free Dynamic Range (SFDR)            | F <sub>out</sub> = 3.38 MHz<br>F <sub>samp</sub> = 216 MHz | _    | 59      | _    | dBc      |  |

| Spurious Free Dynamic Range (SFDR)            | F <sub>out</sub> = 9.28 MHz<br>F <sub>samp</sub> = 297 MHz | —    | 54      | —    | dBc      |  |

| VIDEO PERFORMANCE IN SD MODE <sup>2</sup>     | , 3                                                        |      |         |      | -        |  |

| Short Term Jitter (Line to Line)              | —                                                          | _    | 2.5     | _    | ±ns      |  |

| Long Term Jitter (Field to Field)             | —                                                          | _    | 3.5     | —    | ±ns      |  |

| Frequency Response                            | 0-4.0 MHz                                                  | -0.1 | —       | 0.1  | dB       |  |

|                                               | 5.75 MHz                                                   | -0.7 | —       | 0    | dB       |  |

| Luminance Nonlinearity                        | —                                                          | _    | 0.5     | —    | ±%       |  |

| Differential Gain                             | —                                                          | _    | 0.35    | —    | %        |  |

| Differential Phase                            | —                                                          | _    | 0.6     | —    | Degrees  |  |

| Signal-to-Noise Ratio (SNR)                   | Flat field full bandwidth                                  | _    | 75      | —    | dB       |  |

| Hue Accuracy                                  | —                                                          | _    | 0.8     | —    | ±Degrees |  |

| Color Saturation Accuracy                     | —                                                          | _    | 1.5     | —    | ±%       |  |

| Chroma AM Noise                               | —                                                          | _    | -70     | —    | dB       |  |

| Chroma PM Noise                               | —                                                          | _    | -47     | —    | dB       |  |

| Chroma Nonlinear Phase                        | —                                                          | _    | 0.5     | —    | ±Degrees |  |

| Chroma Nonlinear Gain                         | —                                                          | _    | 2.5     | —    | ±%       |  |

| Chroma/Luma Intermodulation                   |                                                            | _    | 0.1     | —    | ±%       |  |

## 4.7.8.7.2 Asynchronous Parallel Interface Timing Parameters

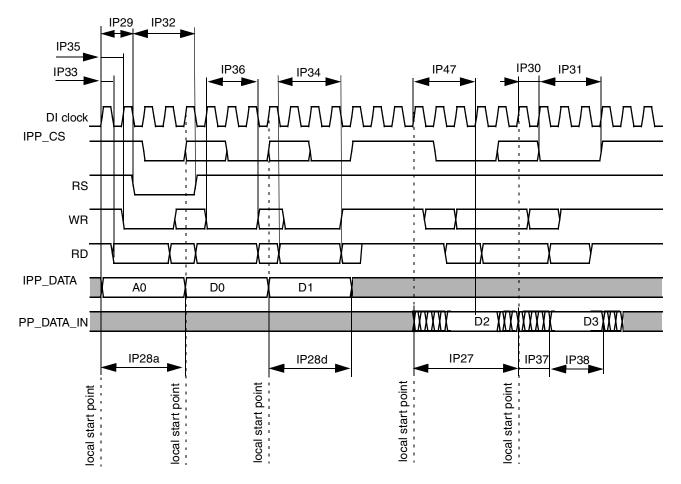

Figure 63 depicts timing of asynchronous parallel interfaces based on the system 80 and system 68k interfaces. Table 84 shows the timing characteristics at display access level. Table 83 shows the timing characteristics at the logical level—from configuration perspective. All timing diagrams are based on active low control signals (signals polarity is controlled through the DI\_DISP\_SIG\_POL register).

Figure 63. Asynchronous Parallel Interface Timing Diagram

| ID    | Parameter                       | Symbol | Value         | Description                                       | Unit |

|-------|---------------------------------|--------|---------------|---------------------------------------------------|------|

| IP27  | Read system cycle time          | Tcycr  | ACCESS_SIZE_# | predefined value in DI REGISTER                   | ns   |

| IP28a | Address Write system cycle time | Tcycwa | ACCESS_SIZE_# | predefined value in DI REGISTER                   | ns   |

| IP28d | Data Write system cycle time    | Tcycwd | ACCESS_SIZE_# | predefined value in DI REGISTER                   | ns   |

| IP29  | RS start                        | Tdcsrr | UP#           | RS strobe switch, predefined value in DI REGISTER | ns   |

| IP30  | CS start                        | Tdcsc  | UP#           | CS strobe switch, predefined value in DI REGISTER | ns   |

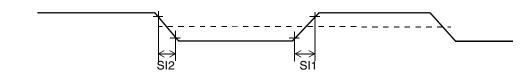

Table 90 and Figure 73 define the AC characteristics of all the P-ATA interface signals on all data transfer modes.

ATA Interface Signals

Figure 73. P-ATA Interface Signals Timing Diagram

| ID                                                                      | D Parameter                                                           |                   | Min | Max  | Unit |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------|-----|------|------|

| SI1 Rising edge slew rate for any signal on ATA interface. <sup>1</sup> |                                                                       | S <sub>rise</sub> |     | 1.25 | V/ns |

| SI2                                                                     | SI2 Falling edge slew rate for any signal on ATA interface (see note) |                   | _   | 1.25 | V/ns |

| SI3                                                                     | SI3 Host interface signal capacitance at the host connector           |                   |     | 20   | pF   |

<sup>1</sup> SRISE and SFALL shall meet this requirement when measured at the sender's connector from 10–90% of full signal amplitude with all capacitive loads from 15–40 pF where all signals have the same capacitive load value.

The user needs to use level shifters for 5.0 V compatibility on the ATA interface. The i.MX51 P-ATA interface is 3.3 V compatible.

The use of bus buffers introduces delay on the bus and introduces skew between signal lines. These factors make it difficult to operate the bus at the highest speed (UDMA-4) when bus buffers are used. If fast UDMA mode operation is needed, this may not be compatible with bus buffers.

Another area of attention is the slew rate limit imposed by the ATA specification on the ATA bus. According to this limit, any signal driven on the bus should have a slew rate between 0.4 and 1.2 V/ns with a 40 pF load. Not many vendors of bus buffers specify slew rate of the outgoing signals.

When bus buffers are used, the ata\_data bus buffer is special. This is a bidirectional bus buffer, so a direction control signal is needed. This direction control signal is ata\_buffer\_en. When its high, the bus should drive from host to device. When its low, the bus should drive from device to host. Steering of the signal is such that contention on the host and device tri-state busses is always avoided.

In the timing equations, some timing parameters are used. These parameters depend on the implementation of the i.MX51 P-ATA interface on silicon, the bus buffer used, the cable delay and cable skew.

## Figure 80. UDMA In Device Terminates Transfer Timing Diagram

### Table 95. UDMA In Burst Timing Parameters

| ATA<br>Parameter | Parameter<br>from<br>Figure 78,<br>Figure 79,<br>Figure 80 | Description                                                                                                      | Controlling Variable |

|------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|

| tack             | tack                                                       | tack (min) = (time_ack $\times$ T) – (tskew1 + tskew2)                                                           | time_ack             |

| tenv             | tenv                                                       | tenv (min) = (time_env $\times$ T) – (tskew1 + tskew2)<br>tenv (max) = (time_env $\times$ T) + (tskew1 + tskew2) | time_env             |

| tds              | tds1                                                       | $tds - (tskew3) - ti_ds > 0$                                                                                     | tskew3, ti_ds, ti_dh |

| tdh              | tdh1                                                       | $tdh - (tskew3) - ti_dh > 0$                                                                                     | should be low enough |

| tcyc             | tc1                                                        | (tcyc – tskew) > T                                                                                               | T big enough         |

| trp              | trp                                                        | trp (min) = time_rp $\times$ T – (tskew1 + tskew2 + tskew6)                                                      | time_rp              |

|                  | tx1 <sup>1</sup>                                           | $(time_rp \times T) - (tco + tsu + 3T + 2 \times tbuf + 2 \times tcable2) > trfs (drive)$                        | time_rp              |

| tmli             | tmli1                                                      | tmli1 (min) = (time_mlix + 0.4) $\times$ T                                                                       | time_mlix            |

| tzah             | tzah                                                       | tzah (min) = (time_zah + 0.4) $\times$ T                                                                         | time_zah             |

| tdzfs            | tdzfs                                                      | $tdzfs = (time_dzfs \times T) - (tskew1 + tskew2)$                                                               | time_dzfs            |

| tcvh             | tcvh                                                       | $tcvh = (time_cvh \times T) - (tskew1 + tskew2)$                                                                 | time_cvh             |

| —                | ton<br>toff <sup>2</sup>                                   | ton = time_on $\times$ T - tskew1<br>toff = time_off $\times$ T - tskew1                                         |                      |

<sup>1</sup> There is a special timing requirement in the ATA host that requires the internal DIOW to go only high 3 clocks after the last active edge on the DSTROBE signal. The equation given on this line tries to capture this constraint.

<sup>2</sup> Make ton and toff big enough to avoid bus contention.

| Port          | Signal Nomenclature                | Type and Access |

|---------------|------------------------------------|-----------------|

| AUDMUX port 6 | AUD6 External—EIM or DISP2 via ION |                 |

| AUDMUX port 7 | SSI 3                              | Internal        |

#### Table 101. AUDMUX Port Allocation (continued)

## NOTE

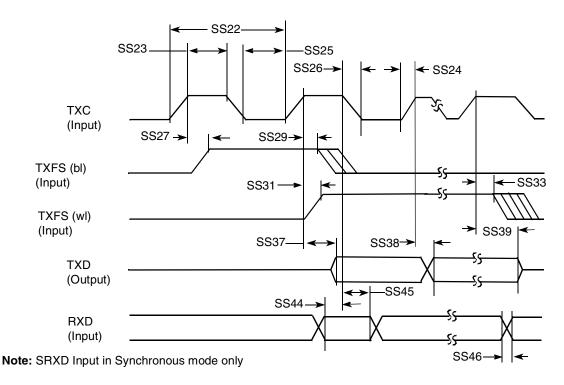

- The terms WL and BL used in the timing diagrams and tables refer to Word Length (WL) and Bit Length (BL).

- The SSI timing diagrams use generic signal names wherein the names used in the *i.MX51 Multimedia Applications Processor Reference Manual* (MCIMX51RM) are channel specific signal names. For example, a channel clock referenced in the IOMUXC chapter as AUD3\_TXC appears in the timing diagram as TXC.

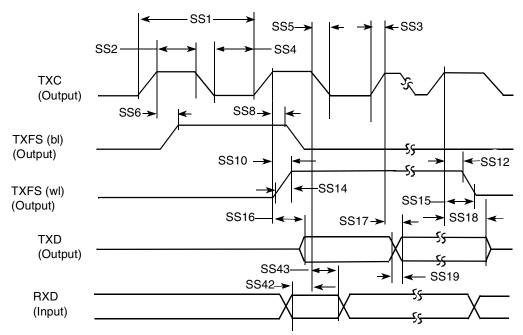

## 4.7.15.1 SSI Transmitter Timing with Internal Clock

Figure 92 depicts the SSI transmitter internal clock timing and Table 102 lists the timing parameters for the SSI transmitter internal clock.

Note: SRXD input in synchronous mode only

# 4.7.15.3 SSI Transmitter Timing with External Clock

Figure 94 depicts the SSI transmitter external clock timing and Table 104 lists the timing parameters for the SSI transmitter external clock.

### Figure 94. SSI Transmitter External Clock Timing Diagram

| ID   | Parameter                                      | Min   | Мах  | Unit |  |  |

|------|------------------------------------------------|-------|------|------|--|--|

|      | External Clock Operation                       |       |      |      |  |  |

| SS22 | (Tx/Rx) CK clock period                        | 81.4  | _    | ns   |  |  |

| SS23 | (Tx/Rx) CK clock high period                   | 36.0  | —    | ns   |  |  |

| SS24 | (Tx/Rx) CK clock rise time                     | —     | 6.0  | ns   |  |  |

| SS25 | (Tx/Rx) CK clock low period                    | 36.0  | —    | ns   |  |  |

| SS26 | (Tx/Rx) CK clock fall time                     | —     | 6.0  | ns   |  |  |

| SS27 | (Tx) CK high to FS (bl) high                   | -10.0 | 15.0 | ns   |  |  |

| SS29 | (Tx) CK high to FS (bl) low                    | 10.0  | —    | ns   |  |  |

| SS31 | (Tx) CK high to FS (wl) high                   | -10.0 | 15.0 | ns   |  |  |

| SS33 | (Tx) CK high to FS (wl) low                    | 10.0  | —    | ns   |  |  |

| SS37 | (Tx) CK high to STXD valid from high impedance | —     | 15.0 | ns   |  |  |

| SS38 | (Tx) CK high to STXD high/low                  | —     | 30   | ns   |  |  |

| Table 104. | SSI Transm | itter Timing v | with External Clock |

|------------|------------|----------------|---------------------|

|------------|------------|----------------|---------------------|

| Contact Name  | Contact Assignment                                                             |

|---------------|--------------------------------------------------------------------------------|

| NVCC_IPU7     | H22                                                                            |

| NVCC_IPU8     | V22                                                                            |

| NVCC_IPU9     | L16                                                                            |

| NVCC_NANDF_A  | J8                                                                             |

| NVCC_NANDF_B  | H8                                                                             |

| NVCC_NANDF_C  | Н9                                                                             |

| NVCC_OSC      | AD22                                                                           |

| NVCC_PER10    | H12                                                                            |

| NVCC_PER11    | H11                                                                            |

| NVCC_PER12    | H15                                                                            |

| NVCC_PER13    | H14                                                                            |

| NVCC_PER14    | V9                                                                             |

| NVCC_PER15    | H16                                                                            |

| NVCC_PER17    | J16                                                                            |

| NVCC_PER3     | V10                                                                            |

| NVCC_PER5     | D20                                                                            |

| NVCC_PER8     | J15                                                                            |

| NVCC_PER9     | H10                                                                            |

| NVCC_SRTC_POW | V12                                                                            |

| NVCC_TV_BACK  | AC22                                                                           |

| NVCC_USBPHY   | P16                                                                            |

| RREFEXT       | K18                                                                            |

| SGND          | P10                                                                            |

| SVCC          | N13                                                                            |

| SVDDGP        | M11                                                                            |

| TVDAC_DHVDD   | AB21                                                                           |

| VBUS          | L22                                                                            |

| VCC           | N12, N14, N15, P12, P13, P14, P15, R13, R14, R15, T14, T15, T16, U14, U15, U16 |

| VDD_ANA_PLL_A | AD4                                                                            |

| VDD_ANA_PLL_B | AC24                                                                           |

| VDD_DIG_PLL_A | AD3                                                                            |

| VDD_DIG_PLL_B | AB23                                                                           |

| VDD_FUSE      | P6                                                                             |

| Ball Status | Ball Assignments |

|-------------|------------------|

| NC          | AA20             |

| NC          | AA21             |

| Contact Name             | Contact<br>Assignment | Power Rail | I/O Buffer Type | Direction after<br>Reset <sup>1</sup> | Configuraton<br>after Reset <sup>1</sup> |

|--------------------------|-----------------------|------------|-----------------|---------------------------------------|------------------------------------------|

| DI1_D0_CS                | U21                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_D1_CS                | AB23                  | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_DISP_CLK             | J18                   | NVCC_IPU6  | GPIO            | Output                                | Low                                      |

| DI1_PIN11                | Y22                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN12                | AA22                  | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN13                | T20                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN15                | H20                   | NVCC_IPU6  | GPIO            | Output                                | High                                     |

| DI1_PIN2                 | G23                   | NVCC_IPU6  | GPIO            | Output                                | High                                     |

| DI1_PIN3                 | G22                   | NVCC_IPU6  | GPIO            | Output                                | High                                     |

| DI2_DISP_CLK             | J21                   | NVCC_IPU7  | GPIO            | Output                                | High                                     |

| DI2_PIN2                 | J20                   | NVCC_IPU7  | GPIO            | Output                                | High                                     |

| DI2_PIN3                 | K18                   | NVCC_IPU7  | GPIO            | Output                                | High                                     |

| DI2_PIN4                 | H23                   | NVCC_IPU7  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT0               | N20                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT1               | N21                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT10 <sup>3</sup> | D22                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT11 <sup>3</sup> | D23                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT12 <sup>3</sup> | E21                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT13 <sup>3</sup> | F20                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT14 <sup>3</sup> | E22                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT15 <sup>3</sup> | G19                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT16 <sup>3</sup> | E23                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT17 <sup>3</sup> | F21                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT18 <sup>3</sup> | G20                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT19 <sup>3</sup> | H18                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT2               | U22                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT20 <sup>3</sup> | F23                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT21 <sup>3</sup> | H19                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT22 <sup>3</sup> | F22                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT23 <sup>3</sup> | G21                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT3               | U23                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT4               | T22                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

Table 131. 19 x 19 mm Signal Assignments, Power Rails, and I/O (continued)

| Contact Name         | Contact<br>Assignment | Power Rail | I/O Buffer Type | Direction after<br>Reset <sup>1</sup> | Configuraton<br>after Reset <sup>1</sup> |

|----------------------|-----------------------|------------|-----------------|---------------------------------------|------------------------------------------|

| EIM_A17 <sup>3</sup> | AB9                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A18 <sup>3</sup> | AC8                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A19 <sup>3</sup> | AA8                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A20 <sup>3</sup> | AB8                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A21 <sup>3</sup> | AC7                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A22              | AB7                   | NVCC_EMI   | GPIO            | Output                                | High                                     |

| EIM_A23 <sup>3</sup> | AC6                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A24              | AC5                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A25              | AB6                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A26              | AC4                   | NVCC_EMI   | GPIO            | Input                                 | 100 kΩ pull-up                           |

| EIM_A27              | AB5                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_BCLK             | AA4                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_CRE              | AB2                   | NVCC_EMI   | GPIO            | Output                                | High                                     |

| EIM_CS0              | W6                    | NVCC_EMI   | GPIO            | Output                                | High                                     |

| EIM_CS1              | Y6                    | NVCC_EMI   | GPIO            | Output                                | High                                     |

| EIM_CS2              | Y7                    | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_CS3              | AC3                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_CS4              | AA6                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_CS5              | AA5                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D16              | AC12                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D17              | W10                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D18              | AA11                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D19              | Y10                   | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D20              | AB11                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D21              | W9                    | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D22              | AC11                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D23              | V8                    | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D24              | AA10                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D25              | Y9                    | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D26              | AB10                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D27              | W8                    | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

| EIM_D28              | AC10                  | NVCC_EMI   | GPIO            | Input                                 | Keeper                                   |

Table 131. 19 x 19 mm Signal Assignments, Power Rails, and I/O (continued)

# 6 Revision History

Table 135 provides a revision history for this data sheet.

| Table 135. i.MX51 | Data Sheet Documen | t Revision History |

|-------------------|--------------------|--------------------|

|-------------------|--------------------|--------------------|

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 6         | 10/2012 | <ul> <li>In Table 25, "I/O Leakage Current," on page 31, updated supply rail names for SD1 and SD2 to NVCC_PER15 and NVCC_PER17, respectively.</li> <li>Updated Section 4.6.7.3, "General WEIM Timing-Synchronous Mode."</li> <li>Updated Section 4.6.7.4, "Examples of WEIM Synchronous Accesses."</li> <li>Updated Section 4.6.7.5, "General WEIM Timing-Asynchronous Mode."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Rev. 5         | 03/2012 | <ul> <li>In Table 4, "JTAG Controller Interface Summary," on page 14, changed On-Chip Termination column value for JTAG_MOD from "100 kΩ pull-down" to "100 kΩ pull-up."</li> <li>In Section 3.7, "USB-CTG IOMUX PIN Configuration," removed the third sentence from the first paragraph and added a note after Table 9.</li> <li>In Section 4.3.4, "Ultra-High Voltage I/O (UHVIO) DC Parameters," added clarification about UHVIO I/O cell HVE bit functionality after Table 21.</li> <li>In Section 4.6.9, "DDR2 SDRAM Specific Parameters." —Updated Table 58, "DDR2 SDRAM Timing Parameter Table," on page 69 —Added a note after Table 58</li> <li>—Updated Figure 36, "DDR2 SDRAM Write Cycle Parameter Table," on page 71 —Updated Table 60, "DDR2 SDRAM Write Cycle Parameter Table," on page 71 —Updated Table 60, "DDR2 SDRAM DQ versus DQS and SDCLK Read Cycle Timing Diagram," on page 73 —Updated Table 63, "DDR2 SDRAM Read Cycle Parameter Table," on page 73 —Added a note after Table 63</li> <li>In Section 4.7.8.2, "Electrical Characteristics," changed signal name in the second sentence of the first paragraph from "SENSB_MCLK" to "SENSB_PIX_CLK."</li> <li>In Table 128, "13 x 13 mm Signal Assignments, Power Rails, and I/O," on page 157, changed Configuraton after Reset column value for contacts, DI1_D0_CS, DI1_D1_CS, DI1_PIN11, and DI1_PIN12, from "Low" to "High."</li> <li>In Table 128, "13 x 13 mm Signal Assignments, Power Rails, and I/O," on page 157, changed Configuraton after Reset column value for contact, JTAG_MOD, from "100 kΩ pull-down" to "100 kΩ pull-up."</li> <li>In Table 128, "13 x 13 mm Signal Assignments, Power Rails, and I/O," on page 157, changed Configuraton after Reset column value for contact, JTAG_MOD, from "100 kΩ pull-down" to "100 kΩ pull-up."</li> <li>In Table 128, "13 x 13 mm Signal Assignments, Power Rails, and I/O," on page 157, changed Configuraton after Reset column value for contacts, DI1_D0_CS, DI1_D1_CS, DI1_PIN11, and DI1_PIN12, from "Low" to "High."</li> <li>In Table 128, "13 x 13 mm Signal Assignments, Pow</li></ul> |

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 2         | 05/2010 | <ul> <li>Updated Case Temperature Range column in Table 1, "Ordering Information," on page 3.</li> <li>Changed the VREFOUT column in Table 3, "Special Signal Considerations," on page 12.</li> <li>Added Section 3, "IOMUX Configuration for Boot Media".</li> <li>Updated Figure 2, "Power-Up Sequence," on page 24.</li> <li>Updated the Minimum and Maximum columns in Table 13, "I.MX51 Operating Ranges," on page 19.</li> <li>Added a note in Section 4.2.1, "Power-Up Sequence."</li> <li>Updated Section 4.2.1, "Power-Up Sequence."</li> <li>Changed the Input current (47 kΩ Pull-up) column in Table 21, "UHVIO DC Electrical Characteristics," on page 27 to Input current (75 kO Pull-up).</li> <li>Added new table for parameters for DDR2 Pad output buffer Impedance. See Table 27, "DDR2 I/O Output Buffer Impedance HVE = 0," on page 32.</li> <li>Added new section under Section 4.5, "I/O AC Parameters". See Section 4.5.4, "AC Electrical Characteristics for DDR2".</li> <li>Updated Table 47, "CAMP Electrical Parameters (CKIH1, CKIH2)," on page 48. In the VIH (for square wave input) parameter, the minimum frequency was changed to NVCC_PER3 - 0.25V and the maximum frequency was changed to NVCC_PER3.</li> <li>Added a note in Section 4.6.6, "NAND Flash Controller (NFC) Parameters" after Table 49.</li> <li>Updated Asymmetric Mode Min, Symmetric Mode Min, and Max columns of Table 50.</li> <li>Removed Conditions parameters of the Full scale output voltage row in Table 82.</li> <li>Updated Section 4.7.11, "P-ATA Timing Parameters". Replaced ATIA/ATAPI-6 specification with ATA/ATAPI-5 specification.</li> <li>In Table 103, "SSI Transmitter Timing with Internal Clock," on page 136, under the Internal Clock Operation section for ID SS30, maximum frequency was changed from 10.0 to 30.</li> <li>In Table 104, "SSI Transmitter Timing with Internal Clock," on page 138, under the External Clock Operation section 4.7.1.1, "UART Electrical", under Section 4.7.1.6, "UART".</li> <li>In Table 104, "SSI Transmitter Timing with Internal Clock," on page 138,</li></ul> |

| Rev. 1         | 10/2009 | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Table 135. i.MX51 Data Sheet Document Revision History (continued)