Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                   |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                            |

| Core Processor                     | ARM® Cortex®-A8                                                                                   |

| Number of Cores/Bus Width          | 1 Core, 32-Bit                                                                                    |

| Speed                              | 600MHz                                                                                            |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                            |

| RAM Controllers                    | LPDDR, DDR2                                                                                       |

| Graphics Acceleration              | No                                                                                                |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                       |

| Ethernet                           | 10/100Mbps (1)                                                                                    |

| SATA                               | -                                                                                                 |

| USB                                | USB 2.0 (3), USB 2.0 + PHY (1)                                                                    |

| Voltage - I/O                      | 1.2V, 1.875V, 2.775V, 3.0V                                                                        |

| Operating Temperature              | -40°C ~ 95°C (TC)                                                                                 |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC |

| Package / Case                     | 529-LFBGA                                                                                         |

| Supplier Device Package            | 529-BGA (19x19)                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx513cjm6c                             |

### **Features**

Table 2. i.MX51 Digital and Analog Modules (continued)

| Block<br>Mnemonic               | Block Name                     | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|--------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IIM                             | IC<br>Identification<br>Module | Security                         | The IC Identification Module (IIM) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically programmable poly fuses (e-Fuses). The IIM also provides a set of volatile software-accessible signals that can be used for software control of hardware elements not requiring non-volatility. The IIM provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals requiring permanent non-volatility. The IIM also provides up to 28 volatile control signals. The IIM consists of a master controller, a software fuse value shadow cache, and a set of registers to hold the values of signals visible outside the module. |

| IOMUXC                          | IOMUX<br>Control               | System<br>Control<br>Peripherals | This module enables flexible I/O multiplexing. Each I/O pad has default as well as several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IPU                             | Image<br>Processing<br>Unit    | Multimedia<br>Peripherals        | IPU enables connectivity to displays and image sensors, relevant processing and synchronization. It supports two display ports and two camera ports, through the following interfaces.  • Legacy Interfaces  • Analog TV interfaces (through a TV encoder bridge)  The processing includes:  • Support for camera control  • Image enhancement: color adjustment and gamut mapping, gamma correction and contrast enhancement, sharpening and noise reduction  • Video/graphics combining  • Support for display backlight reduction  • Image conversion—resizing, rotation, inversion and color space conversion  • Synchronization and control capabilities, allowing autonomous operation.  • Hardware de-interlacing support                                                                                                                                                                                                                  |

| KPP                             | Keypad Port                    | Connectivity<br>Peripherals      | The KPP supports an 8 × 8 external keypad matrix. The KPP features are as follows:  Open drain design Glitch suppression circuit design Multiple keys detection Standby key press detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P-ATA (Muxed<br>with<br>eSDHC-4 | Parallel ATA                   | Connectivity<br>Peripherals      | The P-ATA block is an AT attachment host interface. Its main use is to interface with hard disc drives and optical disc drives. It interfaces with the ATA-5 (UDMA-4) compliant device over a number of ATA signals. It is possible to connect a bus buffer between the host side and the device side. This is muxed with eSDHC-4 interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PWM-1<br>PWM-2                  | Pulse Width<br>Modulation      | Connectivity<br>Peripherals      | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones. The PWM uses 16-bit resolution and a 4 x 16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RAM<br>128 Kbytes               | Internal RAM                   | Internal<br>Memory               | Unified RAM, can be split between Secure RAM and Non-Secure RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROM<br>36 Kbytes                | Boot ROM                       | Internal<br>Memory               | Supports secure and regular Boot Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

Table 13 shows the i.MX51 operating ranges.

Table 13. i.MX51 Operating Ranges

| Symbol                                    | Parameter                                                                                                                                                                                                                                                                                                                          | Minimum <sup>1</sup> | Nominal <sup>2</sup> | Maximum <sup>1</sup> | Unit |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| VDDGP<br>MCIMX51xD products               | ARM core supply voltage<br>0 ≤ f <sub>ARM</sub> ≤ 167 MHz                                                                                                                                                                                                                                                                          | 0.8                  | 0.85                 | 1.15                 | V    |

| (Consumer)                                | ARM core supply voltage<br>167 < f <sub>ARM</sub> ≤ 800 MHz                                                                                                                                                                                                                                                                        | 1.05                 | 1.1                  | 1.15                 | V    |

|                                           | ARM core supply voltage<br>Stop mode                                                                                                                                                                                                                                                                                               | 0.8                  | 0.85                 | 1.15                 | V    |

| VDDGP<br>MCIMX51xC products               | ARM core supply voltage<br>0 < f <sub>ARM</sub> ≤ 600 MHz                                                                                                                                                                                                                                                                          | 0.95                 | 1.0                  | 1.10                 | V    |

| (Industrial)                              | ARM core supply voltage<br>Stop mode                                                                                                                                                                                                                                                                                               | 0.90                 | 0.95                 | 1.05                 | V    |

| VCC<br>MCIMX51xD products<br>(Consumer)   | Peripheral supply voltage High Performance Mode (HPM) The clock frequencies are derived from AXI and AHB buses using 133 or 166 MHz (as needed). The DDR clock rate is 200 MHz.  Note: For detailed information about the use of 133 or 166 MHz clocks, see i.MX51 Multimedia Applications Processor Reference Manual (MCIMX51RM). | 1.175                | 1.225                | 1.275                | V    |

|                                           | Peripheral supply voltage Low Performance<br>Mode (LPM) The clock frequencies are derived<br>from AXI and AHB buses at 44 MHz and a DDR<br>clock rate of DDR Clock/3. DDR2 does not<br>support frequencies below 125 MHz per<br>JEDEC.                                                                                             | 1.00                 | 1.05                 | 1.275                | V    |

|                                           | Peripheral supply voltage—Stop mode                                                                                                                                                                                                                                                                                                | 0.9                  | 0.95                 | 1.275                | V    |

| VCC<br>MCIMX51xC products<br>(Industrial) | Peripheral supply voltage High Performance Mode (HPM) The clock frequencies are derived from AXI and AHB buses using 133 or 166 MHz (as needed). The DDR clock rate is 200 MHz.  Note: For detailed information about the use of 133 or 166 MHz clocks, see i.MX51 Multimedia Applications Processor Reference Manual (MCIMX51RM). | 1.175                | 1.225                | 1.275                | V    |

|                                           | Peripheral supply voltage—Stop mode                                                                                                                                                                                                                                                                                                | 0.90                 | 0.95                 | 1.275                | ٧    |

| VDDA                                      | Memory arrays voltage—Run Mode                                                                                                                                                                                                                                                                                                     | 1.15                 | 1.20                 | 1.275                | V    |

|                                           | Memory arrays voltage—Stop Mode                                                                                                                                                                                                                                                                                                    | 0.9                  | 0.95                 | 1.275                | ٧    |

| VDD_DIG_PLL_A<br>VDD_DIG_PLL_B            | PLL Digital supplies                                                                                                                                                                                                                                                                                                               | 1.15                 | 1.2                  | 1.35                 | V    |

| VDD_ANA_PLL_A<br>VDD_ANA_PLL_B            | PLL Analog supplies                                                                                                                                                                                                                                                                                                                | 1.75                 | 1.8                  | 1.95                 | V    |

### **NOTE**

The term OVDD in this section refers to the associated supply rail of an input or output. The association is shown in Table 128 and Table 131.

### 4.3.1 GPIO/HSGPIO DC Parameters

The parameters in Table 18 are guaranteed per the operating ranges in Table 13, unless otherwise noted.

Table 18. GPIO/HSGPIO DC Electrical Characteristics

| Parameter                                | Symbol | Test Conditions                                                         | Min                          | Тур          | Max                   | Unit |

|------------------------------------------|--------|-------------------------------------------------------------------------|------------------------------|--------------|-----------------------|------|

| High-level output voltage                | Voh    | lout = -1 mA                                                            | OVDD -0.15                   | _            | OVDD + 0.3            | V    |

| Low-level output voltage                 | Vol    | lout = 1mA                                                              | _                            | _            | 0.15                  | V    |

| High-level output current                | loh    | Vout = 0.8×OVDD<br>Low drive<br>Medium drive<br>High drive<br>Max drive | -1.9<br>-3.7<br>-5.2<br>-6.6 | _            | _                     | mA   |

| Low-level output current                 | lol    | Vout = 0.2×OVDD<br>Low drive<br>Medium drive<br>High drive<br>Max drive | 1.9<br>3.7<br>5.2<br>6.6     | _            | _                     | mA   |

| High-Level DC input voltage <sup>1</sup> | VIH    | _                                                                       | 0.7 × OVDD                   | _            | OVDD                  | V    |

| Low-Level DC input voltage <sup>1</sup>  | VIL    | _                                                                       | 0                            | _            | 0.3×OVDD              | V    |

| Input Hysteresis                         | VHYS   | OVDD = 1.875<br>OVDD = 2.775                                            | 0.25                         | 0.34<br>0.45 | _                     | V    |

| Schmitt trigger VT+1,2                   | VT+    | _                                                                       | 0.5OVDD                      | _            | _                     | V    |

| Schmitt trigger VT-1, 2                  | VT-    | _                                                                       | _                            | _            | 0.5 × OVDD            | V    |

| Input current (no pull-up/down)          | lin    | Vin = OVDD or 0                                                         | _                            | _            | See Note <sup>3</sup> | _    |

| Input current (22 kΩ Pull-up)            | lin    | Vin = 0                                                                 | _                            | _            | 161                   | μΑ   |

| Input current (47 kΩ Pull-up)            | lin    | Vin = 0                                                                 | _                            | _            | 76                    | μΑ   |

| Input current (100 kΩ Pull-up)           | lin    | Vin = 0                                                                 | _                            | _            | 36                    | μΑ   |

| Input current (100 kΩ Pull-down)         | lin    | Vin = OVDD                                                              | _                            | _            | 36                    | μΑ   |

| Keeper Circuit Resistance                | _      | OVDD = 1.875V<br>OVDD = 2.775V                                          | _                            | 22<br>17     | _<br>_                | kΩ   |

To maintain a valid level, the transition edge of the input must sustain a constant slew rate (monotonic) from the current DC level through to the target DC level, VIL or VIH. Monotonic input transition time is from 0.1 ns to 1 s.

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

<sup>&</sup>lt;sup>2</sup> Hysteresis of 250 mV is guaranteed over all operating conditions when hysteresis is enabled.

$<sup>^{3}\,</sup>$  I/O leakage currents are listed in Table 25.

Table 37. AC Electrical Characteristics of DDR2 IO Pads for Fast mode and for ovdd=1.65–1.95 V (ipp\_hve=0) (continued)

| Parameter                                                                         | Symbol | Test<br>Condition | Min<br>rise/fall | Тур         | Max<br>rise/fall | Units |

|-----------------------------------------------------------------------------------|--------|-------------------|------------------|-------------|------------------|-------|

| Output Pad di/dt <sup>1</sup>                                                     | di/dt  | _                 | 390              | 201         | 99               | mA/ns |

| Input Pad Transition Times <sup>2</sup>                                           | trfi   | 1.2 pF            | 0.09/0.09        | 0.132/0.128 | 0.212/0.213      | ns    |

| Input Pad Propagation Delay without Hysteresis (CMOS input), 50%-50% <sup>2</sup> | tpi    | 1.2 pF            | 0.45/0.93        | 0.6/0.58    | 0.9/0.88         | ns    |

| Input Pad Propagation Delay with Hysteresis (CMOS input), 50%-50% <sup>2</sup>    | tpi    | 1.2 pF            | 0.55/0.55        | 0.71/0.7    | 1.03/0.98        | ns    |

| Input Pad Propagation Delay (DDR input), 50%-50% <sup>2</sup>                     | tpi    | 1.2 pF            | 0.38/0.38        | 0.58/0.61   | 1.014/1.07       | ns    |

| Maximum Input Transition Times <sup>3</sup>                                       | trm    | _                 | _                | _           | 5                | ns    |

Max condition for tpr, tpo, tps and didt: wcs model, 1.1 V, IO 1.65 V, 105 °C and s0-s5=111111. Typ condition for tpr, tpo, tps and didt: typ model, 1.2 V, IO 1.8 V, 25 °C and s0-s5 = 101010. Min condition for tpr, tpo, tps and didt: bcs model, 1.3 V, IO 1.95 V, -40 °C and s0-s5=000000.

AC electrical characteristics in DDR2 mode for Slow mode and for ovdd=1.65 - 1.95 V, ipp\_hve = 0 are placed in Table 38:

Table 38. AC Electrical Characteristics of DDR2 IO Pads for Slow Mode and for ovdd=1.65–1.95 V (ipp\_hve=0)

| Parameter                                                                         | Symbol | Test<br>Condition | Min<br>rise/fall       | Тур                    | Max<br>rise/fall       | Units |

|-----------------------------------------------------------------------------------|--------|-------------------|------------------------|------------------------|------------------------|-------|

| Output Pad Transition Times <sup>1</sup>                                          | tpr    | 15pF<br>35pF      | 0.75/0.76<br>1.39/1.40 | 0.70/0.74<br>1.18/1.21 | 1.06/1.00<br>1.49/1.47 | ns    |

| Output Pad Propagation Delay, 50%-50% <sup>1</sup>                                | tpo    | 15pF<br>35pF      | 1.50/1.55<br>2.05/2.16 | 1.90/1.95<br>2.36/2.48 | 3.23/3.10<br>3.82/3.75 | ns    |

| Output Pad Slew Rate <sup>1</sup>                                                 | tps    | 15pF<br>35pF      | 1.56/1.54<br>0.84/0.84 | 1.54/1.46<br>0.92/0.89 | 0.93/0.99<br>0.66/0.67 | V/ns  |

| Output Pad di/dt <sup>1</sup>                                                     | di/dt  | _                 | 82                     | 40                     | 19                     | mA/ns |

| Input Pad Transition Times <sup>2</sup>                                           | trfi   | 1.2 pF            | 0.09/0.09              | 0.132/0.128            | 0.212/0.213            | ns    |

| Input Pad Propagation Delay without Hysteresis (CMOS input), 50%-50% <sup>2</sup> | tpi    | 1.2 pF            | 0.45/0.93              | 0.6/0.58               | 0.9/0.88               | ns    |

| Input Pad Propagation Delay with Hysteresis (CMOS input), 50%-50% <sup>2</sup>    | tpi    | 1.2 pF            | 0.55/0.55              | 0.71/0.7               | 1.03/0.98              | ns    |

| Input Pad Propagation Delay (DDR input), 50%-50% <sup>2</sup>                     | tpi    | 1.2 pF            | 0.38/0.38              | 0.58/0.61              | 1.014/1.07             | ns    |

| Maximum Input Transition Times <sup>3</sup>                                       | trm    | _                 | _                      | _                      | 5                      | ns    |

Max condition for trfi and tpi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Typ condition for trfi and tpi: typ model, 1.2 V, IO 1.8 V and 25 °C. Min condition for trfi and tpi: bcs model, 1.3 V, IO 1.95 V and -40 °C.

<sup>&</sup>lt;sup>3</sup> Hysteresis mode is recommended for input with transition time greater than 25 ns.

Table 43. AC Electrical Characteristics of DDR\_clk mobile IO Pads for Fast mode and ovdd=1.65 – 1.95 V (ipp\_hve=0) (continued)

| Parameter                                                     | Symbol | Test<br>Condition | Min<br>rise/fall | Тур         | Max<br>rise/fall | Units |

|---------------------------------------------------------------|--------|-------------------|------------------|-------------|------------------|-------|

| Output Pad di/dt (Low drive) <sup>1</sup>                     | di/dt  | _                 | 62               | 30          | 16               | mA/ns |

| Input Pad Transition Times <sup>2</sup>                       | trfi   | 1.2 pF            | 0.09/0.09        | 0.132/0.128 | 0.212/0.213      | ns    |

| Input Pad Propagation Delay (DDR input), 50%-50% <sup>2</sup> | tpi    | 1.2 pF            | 0.3/0.36         | 0.5/0.52    | 0.82/0.94        | _     |

| Maximum Input Transition Times <sup>3</sup>                   | trm    | _                 | _                | _           | 5                | ns    |

Max condition for tpr, tpo, tps and didt: wcs model, 1.1 V, IO 1.65 V, 105 °C and s0-s5=111111. Typ condition for tpr, tpo, tps and didt: typ model, 1.2 V, IO 1.8 V, 25 °C and s0-s5=101010. Min condition for tpr, tpo, tps and didt: bcs model, 1.3 V, IO 1.95 V, -40 °C and s0-s5=000000.

AC electrical characteristics in DDR mobile for Slow mode and ovdd=1.65-1.95V, ipp\_hve=0 are placed in Table 44.

Table 44. AC Electrical Characteristics of DDR mobile IO Pads for Slow Mode and ovdd=1.65 – 1.95 V (ipp\_hve=0)

| Parameter                                                | Symbol | Test<br>Condition | Min<br>rise/fall       | Тур                    | Max<br>rise/fall        | Units |

|----------------------------------------------------------|--------|-------------------|------------------------|------------------------|-------------------------|-------|

| Output Pad Transition Times (High Drive) <sup>1</sup>    | tpr    | 15pF<br>35pF      | 1.42/1.42<br>3.01/2.96 | 1.20/1.27<br>2.38/2.40 | 1.43/1.49<br>2.37/2.44  | ns    |

| Output Pad Transition Times (Medium Drive) <sup>1</sup>  | tpr    | 15pF<br>35pF      | 2.05/2.04<br>4.50/4.42 | 1.67/1.71<br>3.48/3.52 | 1.82/1.87<br>3.16/3.28  | ns    |

| Output Pad Transition Times (Low Drive) <sup>1</sup>     | tpr    | 15pF<br>35pF      | 4.06/3.98<br>8.94/8.86 | 3.15/3.17<br>6.92/6.93 | 2.92/ 3.02<br>5.69/5.96 | ns    |

| Output Pad Propagation Delay (High Drive) <sup>1</sup>   | tpo    | 15pF<br>35pF      | 2.07/2.23<br>3.21/3.48 | 2.46/2.62<br>3.35/3.63 | 3.92/3.93<br>4.84/4.97  | ns    |

| Output Pad Propagation Delay (Medium Drive) <sup>1</sup> | tpo    | 15pF<br>35pF      | 2.53/2.74<br>4.26/4.58 | 2.83/3.04<br>4.12/4.49 | 4.32/4.35<br>5.55/5.76  | ns    |

| Output Pad Propagation Delay (Low Drive) <sup>1</sup>    | tpo    | 15pF<br>35pF      | 3.93/4.23<br>7.38/7.91 | 3.89/4.21<br>6.43/7.01 | 5.37/5.51<br>7.45/7.94  | ns    |

| Output Pad Slew Rate (High Drive) <sup>1</sup>           | tps    | 15pF<br>35pF      | 0.82/0.82<br>0.39/0.40 | 0.90/0.85<br>0.45/0.45 | 0.69/0.66<br>0.42/0.41  | V/ns  |

| Output Pad Slew Rate (Medium Drive) <sup>1</sup>         | tps    | 15pF<br>35pF      | 0.57/0.57<br>0.26/0.26 | 0.65/0.63<br>0.31/0.31 | 0.54/0.53<br>0.31/0.30  | V/ns  |

| Output Pad Slew Rate (Low Drive) <sup>1</sup>            | tps    | 15pF<br>35pF      | 0.29/0.29<br>0.13/0.13 | 0.34/0.34<br>0.16/0.16 | 0.34/0.33<br>0.17/0.17  | V/ns  |

| Output Pad di/dt (High Drive) <sup>1</sup>               | di/dt  | _                 | 47                     | 14                     | 9                       | mA/ns |

| Output Pad di/dt (Medium drive) <sup>1</sup>             | di/dt  | _                 | 27                     | 9                      | 6                       | mA/ns |

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

<sup>&</sup>lt;sup>2</sup> Max condition for trfi and tpi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Typ condition for trfi and tpi: typ model, 1.2 V, IO 1.8 V and 25 °C. Min condition for trfi and tpi: bcs model, 1.3 V, IO 1.95 V and –40 °C.

<sup>&</sup>lt;sup>3</sup> Hysteresis mode is recommended for input with transition time greater than 25 ns.

| Table 50. NFC- | -Timing | <b>Characteristics</b> | (continued) | ) |

|----------------|---------|------------------------|-------------|---|

|----------------|---------|------------------------|-------------|---|

| ID   | Parameter         | Symbol | Asymmetric<br>Mode Min | Symmetric<br>Mode Min | Max |

|------|-------------------|--------|------------------------|-----------------------|-----|

| NF21 | WE high to RE low | tWHR   | 14T-5.45               | 14T-5.45              | _   |

| NF22 | WE high to busy   | tWB    | _                      | _                     | 6T  |

tosk is calculated by the following formula:

Asymmetric mode:  $tDSR = tREpd + tDpd + \frac{1}{2}T - Tdl^2$

Symmetric mode: tDSR = tREpd + tDpd - Tdl<sup>2</sup>

tREpd + tDpd = 11.2 ns (including clock skew)

where tREpd is RE propogation delay in the chip including IO pad delay, and tDpd is Data propogation delay from IO pad to EMI including IO pad delay.

tDSR can be used to determine tREA max parameter with the following formula: tREA = 1.5T - tDSR.

- <sup>2</sup> Tdl is composed of 4 delay-line units each generates an equal delay with min 1.25 ns and max 1 aclk period (Tack). Default is 1/4 aclk period for each delay-line unit, so all 4 delay lines together generates a total of 1 aclk period. Tack is "emi\_slow\_clk" of the system, which default value is 7.5 ns (133 MHz).

- <sup>3</sup> NF17 is defined only in asymmetric operation mode.

NF17 max value is equivalent to max tRHZ value that can be used with NFC.

Taclk is "emi\_slow\_clk" of the system.

<sup>4</sup> NF18 is defined only in Symmetric operation mode.

$\mathsf{TDHR}$  (MIN) is calculated by the following formula:  $\mathsf{Tdl}^2 - (\mathsf{tREpd} + \mathsf{tDpd})$

where tREpd is RE propogation delay in the chip including IO pad delay, and tDpd is Data propogation delay from IO pad to EMI including IO pad delay.

NF18 max value is equivalent to max tRHZ value that can be used with NFC.

Taclk is "emi\_slow\_clk" of the system.

# 4.6.7 External Interface Module (WEIM)

The following sections provide information on the WEIM.

# 4.6.7.1 WEIM Signal Cross Reference

Table 51 is a guide to help the user identify signals in the WEIM Chapter of the *i.MX51 Multimedia Applications Processor Reference Manual* (MCIMX51RM) that are the same as those mentioned in this data sheet.

Table 51. WEIM Signal Cross Reference

| Reference Manual<br>WEIM Chapter Nomenclature | Data Sheet Nomenclature, Reference Manual External Signals and Pin Multiplexing Chapter, and IOMUX Controller Chapter Nomenclature |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| BCLK                                          | EIM_BCLK                                                                                                                           |

| CSx                                           | EIM_CSx                                                                                                                            |

| WE_B                                          | EIM_RW                                                                                                                             |

| OE_B                                          | EIM_OE                                                                                                                             |

| BEy_B                                         | EIM_EBx                                                                                                                            |

| ADV                                           | EIM_LBA                                                                                                                            |

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

Table 54. WEIM Asynchronous Timing Parameters Table Relative Chip Select

| Ref No. | Parameter                                                                                            | Determination by<br>Synchronous measured<br>parameters <sup>12</sup> | Min                           | Max<br>(If 133 MHz is<br>supported by SOC) | Unit |

|---------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|--------------------------------------------|------|

| WE43    | Input Data Valid to CSx_B<br>Invalid                                                                 | MAXCO - MAXCSO + MAXDI                                               | MAXCO -<br>MAXCSO +<br>MAXDI  | _                                          | ns   |

| WE44    | CSx_B Invalid to Input Data invalid                                                                  | 0                                                                    | 0                             | _                                          | ns   |

| WE45    | CSx_B Valid to BEy_B Valid<br>(Write access)                                                         | WE12 - WE6 + (WBEA - CSA)                                            | _                             | 3 + (WBEA - CSA)                           | ns   |

| WE46    | BEy_B Invalid to CSx_B Invalid<br>(Write access)                                                     | WE7 - WE13 + (WBEN - CSN)                                            | _                             | -3 + (WBEN - CSN)                          | ns   |

| MAXDTI  | DTACK MAXIMUM delay from<br>chip dtack input to its internal<br>FF + 2 cycles for<br>synchronization |                                                                      | _                             | _                                          | _    |

| WE47    | Dtack Active to CSx_B Invalid                                                                        | MAXCO - MAXCSO + MAXDTI                                              | MAXCO -<br>MAXCSO +<br>MAXDTI | _                                          | ns   |

| WE48    | CSx_B Invalid to Dtack invalid                                                                       | 0                                                                    | 0                             | _                                          | ns   |

Parameters WE4... WE21 value see column BCD = 0 in Table 53.

$<sup>^2\,</sup>$  All config. parameters (CSA,CSN,WBEA,WBEN,ADVA,ADVN,OEN,OEA,RBEA & RBEN) are in cycle units.

<sup>&</sup>lt;sup>3</sup> CS Assertion. This bit field determines when CS signal is asserted during read/write cycles.

$<sup>^{4}\,</sup>$  CS Negation. This bit field determines when CS signal is negated during read/write cycles.

<sup>&</sup>lt;sup>5</sup> t is axi\_clk cycle time.

<sup>&</sup>lt;sup>6</sup> BE Assertion. This bit field determines when BE signal is asserted during read cycles.

<sup>&</sup>lt;sup>7</sup> BE Negation. This bit field determines when BE signal is negated during read cycles.

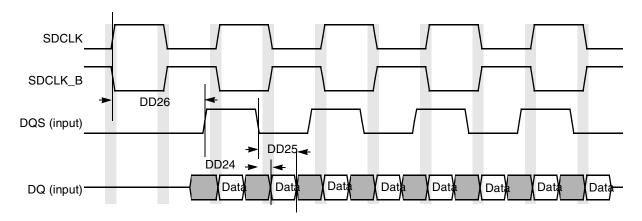

Figure 34 shows the timing diagram for mDDR SDRAM DQ versus DQS and SDCLK read cycle. The timing parameters for this diagram is shown in Table 57.

Figure 34. mDDR SDRAM DQ vs. DQS and SDCLK READ Cycle Timing Diagram

Table 57. mDDR SDRAM Read Cycle Parameter Table<sup>1</sup>

| ID   | PARAMETER                                                                   | Symbol | 200 I | MHz <sup>2</sup> | 166  | MHz  | 133 | MHz  | Unit  |

|------|-----------------------------------------------------------------------------|--------|-------|------------------|------|------|-----|------|-------|

|      | TATIANLETEN                                                                 | Symbol | Min   | Max              | Min  | Max  | Min | Max  | Oilit |

| DD24 | DQS - DQ Skew (defines the Data valid window in read cycles related to DQS) | tDQSQ  | _     | 0.4              | _    | 0.75 | _   | 0.85 | ns    |

| DD25 | DQS DQ in HOLD time from DQS                                                | tQH    | 1.75  | _                | 2.05 | _    | 2.6 | _    | ns    |

| DD26 | DQS output access time from SDCLK posedge tDQSCK 2 5 2                      |        | 2     | 5.5              | 2    | 6.5  | ns  |      |       |

Test conditions are: Capacitance 15 pF for DDR PADS. Recommended drive strengths is medium for SDCLK and high for address and controls

SDRAM CLK and DQS related parameters are being measured from the 50% point. that is, high is defined as 50% of signal value and low is defined as 50% as signal value. DDR SDRAM CLK parameters are measured at the crossing point of SDCLK and SDCLK (inverted clock)

## 4.7.6.1 Standard and Fast Mode Timing Parameters

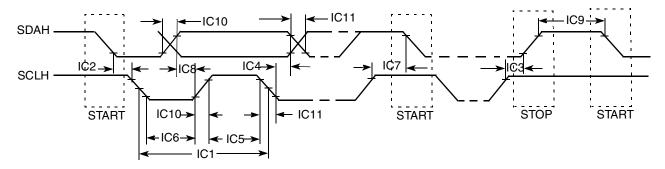

Figure 47 depicts the standard and fast mode timings of HS-I<sup>2</sup>C module, and Table 75 lists the timing characteristics.

Figure 47. HS-I<sup>2</sup>C Standard and Fast Mode Bus Timing

| ID   | Parameter                                           | Standa | rd Mode           | Fast Mode                         |                  | Unit  |  |  |

|------|-----------------------------------------------------|--------|-------------------|-----------------------------------|------------------|-------|--|--|

|      | raiametei                                           | Min    | Max               | Min                               | Max              | Oilit |  |  |

| IC1  | SCLH cycle time                                     | 10     | _                 | 2.5                               | _                | μs    |  |  |

| IC2  | Hold time (repeated) START condition                | 4.0    | _                 | 0.6                               | _                | μs    |  |  |

| IC3  | Set-up time for STOP condition                      | 4.0    | _                 | 0.6                               | _                | μs    |  |  |

| IC4  | Data hold time                                      | 01     | 3.45 <sup>2</sup> | 01                                | 0.9 <sup>2</sup> | μs    |  |  |

| IC5  | HIGH Period of SCLH Clock                           | 4.0    | _                 | 0.6                               | _                | μs    |  |  |

| IC6  | LOW Period of the SCLH Clock                        | 4.7    | _                 | 1.3                               | _                | μs    |  |  |

| IC7  | Set-up time for a repeated START condition          | 4.7    | _                 | 0.6                               | _                | μs    |  |  |

| IC8  | Data set-up time                                    | 250    | _                 | 100 <sup>3</sup>                  | _                | ns    |  |  |

| IC9  | Bus free time between a STOP and START condition    | 4.7    | _                 | 1.3                               | _                | μs    |  |  |

| IC10 | Rise time of both SDAH and SCLH signals             | _      | 1000              | 20+0.1C <sub>b</sub> <sup>4</sup> | 300              | ns    |  |  |

| IC11 | Fall time of both SDAH and SCLH signals             | _      | 300               | 20+0.1C <sub>b</sub> <sup>4</sup> | 300              | ns    |  |  |

| IC12 | Capacitive load for each bus line (C <sub>b</sub> ) | _      | 100               | _                                 | 100              | pF    |  |  |

A device must internally provide a hold time of at least 300 ns for SDAH signal in order to bridge the undefined region of the falling edge of SCLH.

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

<sup>&</sup>lt;sup>2</sup> The maximum hold time has only to be met if the device does not stretch the LOW period (ID no IC6) of the SCLH signal

A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement of Set-up time (ID No IC8) of 250 ns must then be met. This automatically is the case if the device does not stretch the LOW period of the SCLH signal.

If such a device does stretch the LOW period of the SCLH signal, it must output the next data bit to the SDAH line max\_rise\_time (ID No IC10) + data\_setup\_time (ID No IC8) = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCLH line is released.

$<sup>^4</sup>$   $C_h$  = total capacitance of one bus line in pF.

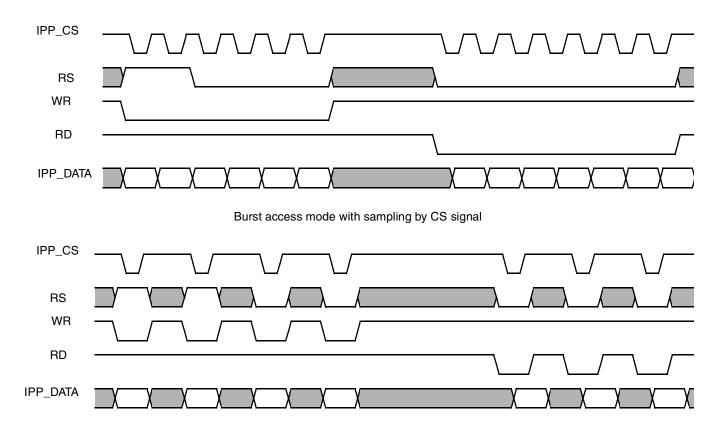

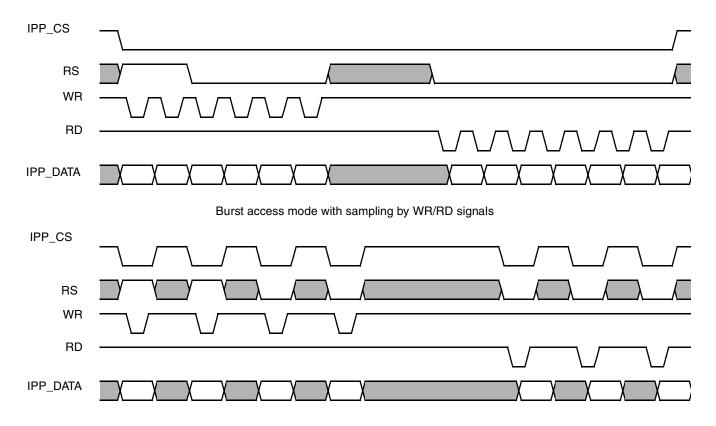

Single access mode (all control signals are not active for one display interface clock after each display access)

Figure 58. Asynchronous Parallel System 80 Interface (Type 1) Timing Diagram

Single access mode (all control signals are not active for one display interface clock after each display access)

Figure 59. Asynchronous Parallel System 80 Interface (Type 2) Timing Diagram

109

<sup>9</sup>Display control up for read

$$Tdicur = \frac{1}{2} \left( T_{DI\_CLK} \times ceil \left[ \frac{2 \times DISP\_UP\_\#}{DI\_CLK} \right] \right)$$

DISP\_UP is predefined in REGISTER

<sup>10</sup>Display control down for read

$$Tdicdrw = \frac{1}{2} \left( T_{DI\_CLK} \times ceil \left[ \frac{2 \times DISP\_DOWN\_\#}{DI\_CLK\_PERIOD} \right] \right)$$

DISP\_DOWN is predefined in REGISTER

<sup>11</sup>Display control up for write

$$Tdicuw = \frac{1}{2} \left( T_{DI\_CLK} \times ceil \left[ \frac{2 \times DISP\_UP\_\#}{DI\_CLK\_PERIOD} \right] \right)$$

DISP\_UP is predefined in REGISTER

<sup>12</sup>This parameter is a requirement to the display connected to the IPU

13Data read point

$$\mathsf{Tdrp} = \mathsf{T}_{\mathsf{DI\_CLK}} \times \mathsf{ceil} \left[ \frac{\mathsf{DISP\#\_READ\_EN}}{\mathsf{DI\_CLK\_PERIOD}} \right]$$

Note: DISP#\_READ\_EN—operand of DC's MICROCDE READ command to sample incoming data

<sup>14</sup>Loop back delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a chip-level output delay, board delays, a chip-level input delay, an IPU input delay. This value is chip specific.

### 4.7.8.8 Standard Serial Interfaces

The IPU supports the following types of asynchronous serial interfaces:

- 1. 3-wire (with bidirectional data line).

- 2. 4-wire (with separate data input and output lines).

- 3. 5-wire type 1 (with sampling RS by the serial clock).

- 4. 5-wire type 2 (with sampling RS by the chip select signal).

The IPU has four independent outputs and one input. The port can be configured to provide 3, 4, or 5-wire interfaces.

Figure 64 depicts the timing diagram of the 3-wire serial interface. The timing diagrams correspond to active-low IPP# CS signal and the straight polarity of the IPP CLK signal.

For this interface, a bidirectional data line is used outside the chip. The IPU still uses separate input and output data lines (IPP\_IND\_DISPB\_SD\_D and IPP\_DO\_DISPB\_SD\_D). The I/O mux should provide

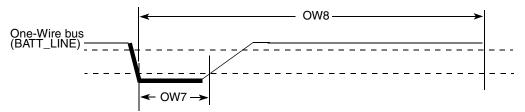

Figure 70 depicts Write 1 Sequence timing, Figure 71 depicts the Read Sequence timing, and Table 88 lists the timing parameters.

Figure 70. Write 1 Sequence Timing Diagram

Figure 71. Read Sequence Timing Diagram

Table 88. WR1 /RD Timing Parameters

| ID  | Parameter              | Symbol               | Min | Тур | Max | Unit |

|-----|------------------------|----------------------|-----|-----|-----|------|

| OW7 | Write /Read Low Time   | t <sub>LOW1</sub>    | 1   | 5   | 15  | μs   |

| OW8 | Transmission Time Slot | t <sub>SLOT</sub>    | 60  | 117 | 120 | μs   |

| OW9 | Release Time           | t <sub>RELEASE</sub> | 15  | _   | 45  | μs   |

# 4.7.10 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 75 shows timing for PIO write and Table 93 lists the timing parameters for PIO write.

### Figure 75. Multi-word DMA (MDMA) Timing

### **Table 93. PIO Write Timing Parameters**

| ATA<br>Parameter | Parameter from Figure 75 | Value                                                                       | Controlling<br>Variable      |

|------------------|--------------------------|-----------------------------------------------------------------------------|------------------------------|

| t1               | t1                       | t1 (min) = time_1 × T - (tskew1 + tskew2 + tskew5)                          | time_1                       |

| t2               | t2w                      | t2 (min) = time_2w × T - (tskew1 + tskew2 + tskew5)                         | time_2w                      |

| t9               | t9                       | t9 (min) = time_9 × T - (tskew1 + tskew2 + tskew6)                          | time_9                       |

| t3               | _                        | t3 (min) = (time_2w - time_on)×T - (tskew1 + tskew2 +tskew5)                | If not met, increase time_2w |

| t4               | t4                       | t4 (min) = time_4 × T - tskew1                                              | time_4                       |

| tA               | tA                       | $tA = (1.5 + time_ax) \times T - (tco + tsui + tcable2 + tcable2 + 2×tbuf)$ | time_ax                      |

| tO               | _                        | $t0(min) = (time_1 + time_2 + time_9) \times T$                             | time_1, time_2r,<br>time_9   |

| _                | _                        | Avoid bus contention when switching buffer on by making ton long enough     | _                            |

| _                | _                        | Avoid bus contention when switching buffer off by making toff long enough   | _                            |

Figure 80. UDMA In Device Terminates Transfer Timing Diagram

### Table 95. UDMA In Burst Timing Parameters

| ATA<br>Parameter | Parameter<br>from<br>Figure 78,<br>Figure 79,<br>Figure 80 | Description                                                                                                      | Controlling Variable |

|------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|

| tack             | tack                                                       | $tack (min) = (time_ack \times T) - (tskew1 + tskew2)$                                                           | time_ack             |

| tenv             | tenv                                                       | tenv (min) = (time_env $\times$ T) - (tskew1 + tskew2)<br>tenv (max) = (time_env $\times$ T) + (tskew1 + tskew2) | time_env             |

| tds              | tds1                                                       | tds - (tskew3) - ti_ds > 0                                                                                       | tskew3, ti_ds, ti_dh |

| tdh              | tdh1                                                       | tdh - (tskew3) - ti_dh > 0                                                                                       | should be low enough |

| tcyc             | tc1                                                        | (tcyc – tskew) > T                                                                                               | T big enough         |

| trp              | trp                                                        | trp (min) = time_rp × T - (tskew1 + tskew2 + tskew6)                                                             | time_rp              |

| _                | tx1 <sup>1</sup>                                           | $(time\_rp \times T) - (tco + tsu + 3T + 2 \times tbuf + 2 \times tcable2) > trfs (drive)$                       | time_rp              |

| tmli             | tmli1                                                      | tmli1 (min) = (time_mlix + 0.4) × T                                                                              | time_mlix            |

| tzah             | tzah                                                       | tzah (min) = (time_zah + 0.4) × T                                                                                | time_zah             |

| tdzfs            | tdzfs                                                      |                                                                                                                  | time_dzfs            |

| tcvh             | tcvh                                                       | $tcvh = (time\_cvh \times T) - (tskew1 + tskew2)$                                                                | time_cvh             |

| _                | ton<br>toff <sup>2</sup>                                   | ton = time_on $\times$ T - tskew1<br>toff = time_off $\times$ T - tskew1                                         | _                    |

<sup>&</sup>lt;sup>1</sup> There is a special timing requirement in the ATA host that requires the internal DIOW to go only high 3 clocks after the last active edge on the DSTROBE signal. The equation given on this line tries to capture this constraint.

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

<sup>&</sup>lt;sup>2</sup> Make ton and toff big enough to avoid bus contention.

### 4.7.11.3 UDMA Output Timing

Figure 81 shows timing when the UDMA out transfer starts, Figure 82 shows timing when the UDMA out host terminates transfer, Figure 83 shows timing when the UDMA out device terminates transfer, and Table 96 lists the timing parameters for UDMA out burst.

Figure 81. UDMA Out Transfer Starts Timing Diagram

Figure 82. UDMA Out Host Terminates Transfer Timing Diagram

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

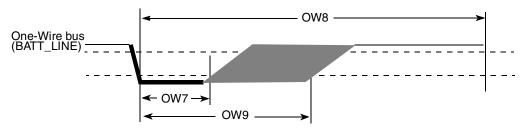

## 4.7.15.3 SSI Transmitter Timing with External Clock

Figure 94 depicts the SSI transmitter external clock timing and Table 104 lists the timing parameters for the SSI transmitter external clock.

Figure 94. SSI Transmitter External Clock Timing Diagram

Table 104. SSI Transmitter Timing with External Clock

| ID   | Parameter                                      | Min   | Max  | Unit |  |  |  |

|------|------------------------------------------------|-------|------|------|--|--|--|

|      | External Clock Operation                       |       |      |      |  |  |  |

| SS22 | (Tx/Rx) CK clock period                        | 81.4  | _    | ns   |  |  |  |

| SS23 | (Tx/Rx) CK clock high period                   | 36.0  | _    | ns   |  |  |  |

| SS24 | (Tx/Rx) CK clock rise time                     | _     | 6.0  | ns   |  |  |  |

| SS25 | (Tx/Rx) CK clock low period                    | 36.0  | _    | ns   |  |  |  |

| SS26 | (Tx/Rx) CK clock fall time                     | _     | 6.0  | ns   |  |  |  |

| SS27 | (Tx) CK high to FS (bl) high                   | -10.0 | 15.0 | ns   |  |  |  |

| SS29 | (Tx) CK high to FS (bl) low                    | 10.0  | _    | ns   |  |  |  |

| SS31 | (Tx) CK high to FS (wl) high                   | -10.0 | 15.0 | ns   |  |  |  |

| SS33 | (Tx) CK high to FS (wl) low                    | 10.0  | _    | ns   |  |  |  |

| SS37 | (Tx) CK high to STXD valid from high impedance | _     | 15.0 | ns   |  |  |  |

| SS38 | (Tx) CK high to STXD high/low                  | _     | 30   | ns   |  |  |  |

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

Table 125. USB PHY System Clocking Parameters (continued)

| Parameter          | Conditions | Min | Тур | Max | Unit |

|--------------------|------------|-----|-----|-----|------|

| Jitter (peak-peak) | <1.2 MHz   | 0   | _   | 50  | ps   |

| Jitter (peak-peak) | >1.2 MHz   | 0   | _   | 100 | ps   |

| Duty-cycle         | _          | 40  | _   | 60  | %    |

# 4.7.19.4 USB PHY Voltage Thresholds

Table 126 lists the USB PHY voltage thresholds.

**Table 126. VBUS Comparators Thresholds**

| Parameter                                    | Conditions | Min | Тур  | Max  | Unit |

|----------------------------------------------|------------|-----|------|------|------|

| A-Device Session Valid                       | _          | 0.8 | 1.4  | 2.0  | V    |

| B-Device Session Valid                       | _          | 0.8 | 1.4  | 4.0  | V    |

| B-Device Session End                         | _          | 0.2 | 0.45 | 0.8  | V    |

| VBUS Valid Comparator Threshold <sup>1</sup> | _          | 4.4 | 4.6  | 4.75 | V    |

<sup>&</sup>lt;sup>1</sup> For VBUS maximum rating, see Table 11 on page 18

# 5 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

# 5.1 13 x 13 mm Package Information

This section contains the outline drawing, signal assignment map, ground/power/reference ID (by ball grid location) for the  $13 \times 13$  mm, 0.5 mm pitch package.

### **Package Information and Contact Assignments**

Table 131. 19 x 19 mm Signal Assignments, Power Rails, and I/O (continued)

| Contact Name             | Contact<br>Assignment | Power Rail | I/O Buffer Type | Direction after<br>Reset <sup>1</sup> | Configuraton<br>after Reset <sup>1</sup> |

|--------------------------|-----------------------|------------|-----------------|---------------------------------------|------------------------------------------|

| DI1_D0_CS                | U21                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_D1_CS                | AB23                  | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_DISP_CLK             | J18                   | NVCC_IPU6  | GPIO            | Output                                | Low                                      |

| DI1_PIN11                | Y22                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN12                | AA22                  | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN13                | T20                   | NVCC_IPU2  | GPIO            | Output                                | High                                     |

| DI1_PIN15                | H20                   | NVCC_IPU6  | GPIO            | Output                                | High                                     |

| DI1_PIN2                 | G23                   | NVCC_IPU6  | GPIO            | Output                                | High                                     |

| DI1_PIN3                 | G22                   | NVCC_IPU6  | GPIO            | Output                                | High                                     |

| DI2_DISP_CLK             | J21                   | NVCC_IPU7  | GPIO            | Output                                | High                                     |

| DI2_PIN2                 | J20                   | NVCC_IPU7  | GPIO            | Output                                | High                                     |

| DI2_PIN3                 | K18                   | NVCC_IPU7  | GPIO            | Output                                | High                                     |

| DI2_PIN4                 | H23                   | NVCC_IPU7  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT0               | N20                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT1               | N21                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT10 <sup>3</sup> | D22                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT11 <sup>3</sup> | D23                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT12 <sup>3</sup> | E21                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT13 <sup>3</sup> | F20                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT14 <sup>3</sup> | E22                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT15 <sup>3</sup> | G19                   | NVCC_IPU4  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT16 <sup>3</sup> | E23                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT17 <sup>3</sup> | F21                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT18 <sup>3</sup> | G20                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT19 <sup>3</sup> | H18                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT2               | U22                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT20 <sup>3</sup> | F23                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT21 <sup>3</sup> | H19                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT22 <sup>3</sup> | F22                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT23 <sup>3</sup> | G21                   | NVCC_IPU5  | GPIO            | Input                                 | Keeper                                   |

| DISP1_DAT3               | U23                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

| DISP1_DAT4               | T22                   | NVCC_HS6   | HSGPIO          | Input                                 | Keeper                                   |

i.MX51 Applications Processors for Consumer and Industrial Products, Rev. 6

### Table 135. i.MX51 Data Sheet Document Revision History (continued)

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 2         | 05/2010 | <ul> <li>Updated CaseTemperature Range column in Table 1, "Ordering Information," on page 3.</li> <li>Changed the VREFOUT column in Table 3, "Special Signal Considerations," on page 12.</li> <li>Added Section 3, "IOMUX Configuration for Boot Media".</li> <li>Updated Figure 2, "Power-Up Sequence," on page 24.</li> <li>Updated the Minimum and Maximum columns in Table 13, "i.MX51 Operating Ranges," on page 19.</li> <li>Added a note in Section 4.2.1, "Power-Up Sequence."</li> <li>Updated Section 4.2.1, "Power-Up Sequence."</li> <li>Changed the Input current (47 kΩ Pull-up) column in Table 21, "UHVIO DC Electrical Characteristics," on page 27 to Input current (75 kO Pull-up).</li> <li>Added new table for parameters for DDR2 Pad output buffer Impedance. See Table 27, "DDR2 I/O Output Buffer Impedance HVE = 0," on page 32.</li> <li>Added new section under Section 4.5, "I/O AC Parameters". See Section 4.5.4, "AC Electrical Characteristics for DDR2".</li> <li>Updated Table 47, "CAMP Electrical Parameters (CKIH1, CKIH2)," on page 48. In the VIH (for square wave input) parameter, the minimum frequency was changed to NVCC_PER3 - 0.25V and the maximum frequency was changed to NVCC_PER3.</li> <li>Added a note in Section 4.6.6, "NAND Flash Controller (NFC) Parameters" after Table 49.</li> <li>Updated Asymmetric Mode Min, Symmetric Mode Min, and Max columns of Table 50.</li> <li>Removed Conditions parameters of the Full scale output voltage row in Table 82.</li> <li>Updated Section 4.7.11, "P-ATA Timing Parameters". Replaced ATA/ATAPI-6 specification with ATA/ATAPI-5 specification.</li> <li>In Table 102, "SSI Transmitter Timing with Internal Clock," on page 135, under the Synchronous Internal Clock Operation section for ID SS20, minimum frequency was changed from 10.0 to 30.</li> <li>In Table 104, "SSI Transmitter Timing with Internal Clock," on page 136, under the Internal Clock Operation section for ID SS20, minimum frequency was changed from 10.0 to 30.</li> <li>In Table 104, "SSI Transmitter Timing with Internal Clock," on</li></ul> |

| Rev. 1         | 10/2009 | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |