# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 64                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                |                                                                |

| RAM Size                   | 4.25К х 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b, 8x12b; D/A 2x12b                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 100-TQFP                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f020-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 18.3. SMBus Transfer Modes                              | 187 |

|----|---------------------------------------------------------|-----|

|    | 18.3.1. Master Transmitter Mode                         | 187 |

|    | 18.3.2. Master Receiver Mode                            |     |

|    | 18.3.3. Slave Transmitter Mode                          | 188 |

|    | 18.3.4. Slave Receiver Mode                             |     |

|    | 18.4. SMBus Special Function Registers                  |     |

|    | 18.4.1. Control Register                                |     |

|    | 18.4.2. Clock Rate Register                             |     |

|    | 18.4.3. Data Register                                   |     |

|    | 18.4.4. Address Register                                |     |

|    | 18.4.5. Status Register                                 |     |

| 19 | SERIAL PERIPHERAL INTERFACE BUS (SPI0)                  |     |

|    | 19.1. Signal Descriptions                               |     |

|    | 19.1.1. Master Out, Slave In (MOSI)                     |     |

|    | 19.1.2. Master In, Slave Out (MISO)                     |     |

|    | 19.1.3. Serial Clock (SCK)                              |     |

|    | 19.1.4. Slave Select (NSS)                              |     |

|    | 19.2. SPI0 Operation                                    |     |

|    | 19.3. Serial Clock Timing                               |     |

|    | 19.4. SPI Special Function Registers                    |     |

| 20 | . UART0                                                 |     |

|    | 20.1. UART0 Operational Modes                           | 206 |

|    | 20.1.1. Mode 0: Synchronous Mode                        |     |

|    | 20.1.2. Mode 1: 8-Bit UART, Variable Baud Rate          |     |

|    | 20.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate             | 208 |

|    | 20.1.4. Mode 3: 9-Bit UART, Variable Baud Rate          | 209 |

|    | 20.2. Multiprocessor Communications                     | 210 |

|    | 20.3. Frame and Transmission Error Detection            |     |

| 21 | . UART1                                                 | 215 |

|    | 21.1. UART1 Operational Modes                           | 216 |

|    | 21.1.1. Mode 0: Synchronous Mode                        | 216 |

|    | 21.1.2. Mode 1: 8-Bit UART, Variable Baud Rate          | 217 |

|    | 21.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate             | 218 |

|    | 21.1.4. Mode 3: 9-Bit UART, Variable Baud Rate          | 219 |

|    | 21.2. Multiprocessor Communications                     | 220 |

|    | 21.3. Frame and Transmission Error Detection            | 221 |

| 22 | TIMERS                                                  | 225 |

|    | 22.1. Timer 0 and Timer 1                               | 227 |

|    | 22.1.1. Mode 0: 13-bit Counter/Timer                    | 227 |

|    | 22.1.2. Mode 1: 16-bit Counter/Timer                    |     |

|    | 22.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload    | 229 |

|    | 22.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) | 230 |

|    | 22.2. Timer 2                                           | 234 |

|    | 22.2.1. Mode 0: 16-bit Counter/Timer with Capture       | 235 |

|    | 22.2.2. Mode 1: 16-bit Counter/Timer with Auto-Reload   | 236 |

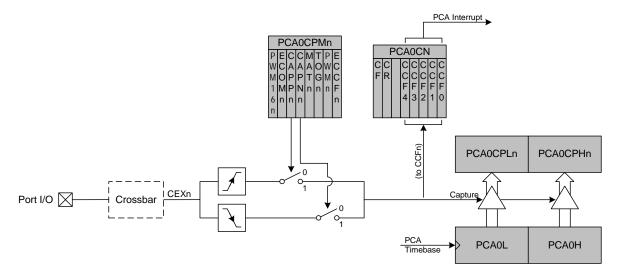

### **1.5. Programmable Counter Array**

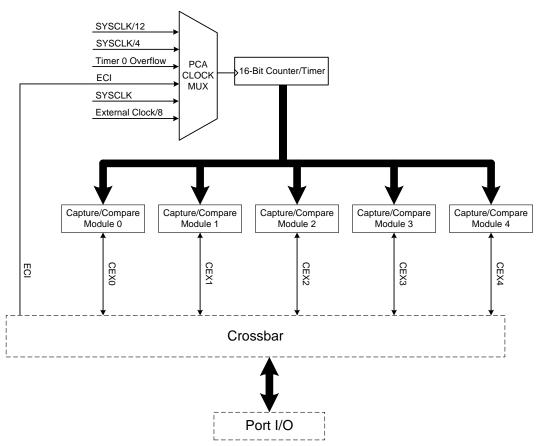

The C8051F020 MCU family includes an on-board Programmable Counter/Timer Array (PCA) in addition to the five 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with 5 programmable capture/compare modules. The timebase is clocked from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflow, an External Clock Input (ECI pin), the system clock, or the external oscillator source divided by 8.

Each capture/compare module can be configured to operate in one of six modes: Edge-Triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. The PCA Capture/Compare Module I/O and External Clock Input are routed to the MCU Port I/O via the Digital Crossbar.

#### 1.6. Serial Ports

The C8051F020 MCU Family includes two Enhanced Full-Duplex UARTs, SPI Bus, and SMBus/I<sup>2</sup>C. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little intervention by the CPU. The serial buses do not "share" resources such as timers, interrupts, or Port I/O, so any or all of the serial buses may be used together with any other.

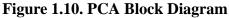

### **1.9.** Comparators and DACs

Each C8051F020/1/2/3 MCU has two 12-bit DACs and two comparators on chip. The MCU data and control interface to each comparator and DAC is via the Special Function Registers. The MCU can place any DAC or comparator in low power shutdown mode.

The comparators have software programmable hysteresis. Each comparator can generate an interrupt on its rising edge, falling edge, or both; these interrupts are capable of waking up the MCU from sleep mode. The comparators' output state can also be polled in software. The comparator outputs can be programmed to appear on the Port I/O pins via the Crossbar.

The DACs are voltage output mode, and include a flexible output scheduling mechanism. This scheduling mechanism allows DAC output updates to be forced by a software write or a Timer 2, 3, or 4 overflow. The DAC voltage reference is supplied via the dedicated VREFD input pin on C8051F020/2 devices or via the internal voltage reference on C8051F021/3 devices. The DACs are especially useful as references for the comparators or offsets for the differential inputs of the ADC.

### Figure 1.13. ComparatorandDA@iagram

VDD = 3.0 V, AV+ = 3.0 V,  $-40^{\circ}C$  to  $+85^{\circ}C$  unless otherwise specified

| PARAMETER                                         | CONDITIONS                             | MIN   | ТҮР   | MAX             | UNITS |

|---------------------------------------------------|----------------------------------------|-------|-------|-----------------|-------|

| Response Time 1                                   | CP+ - CP- = 100 mV                     |       | 4     |                 | μs    |

| Response Time 2                                   | CP+ - CP- = 10 mV                      |       | 12    |                 | μs    |

| Common-Mode Rejection Ratio                       |                                        |       | 1.5   | 4               | mV/V  |

| Positive Hysteresis 1                             | CPnHYP1-0 = 00                         |       | 0     | 1               | mV    |

| Positive Hysteresis 2                             | CPnHYP1-0 = 01                         | 2     | 4.5   | 7               | mV    |

| Positive Hysteresis 3                             | CPnHYP1-0 = 10                         | 4     | 9     | 13              | mV    |

| Positive Hysteresis 4                             | CPnHYP1-0 = 11                         | 10    | 17    | 25              | mV    |

| Negative Hysteresis 1                             | CPnHYN1-0 = 00                         |       | 0     | 1               | mV    |

| Negative Hysteresis 2                             | CPnHYN1-0 = 01                         | 2     | 4.5   | 7               | mV    |

| Negative Hysteresis 3                             | CPnHYN1-0 = 10                         | 4     | 9     | 13              | mV    |

| Negative Hysteresis 4                             | CPnHYN1-0 = 11                         | 10    | 17    | 25              | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                                        | -0.25 |       | (AV+)<br>+ 0.25 | V     |

| Input Capacitance                                 |                                        |       | 7     |                 | pF    |

| Input Bias Current                                |                                        | -5    | 0.001 | +5              | nA    |

| Input Offset Voltage                              |                                        | -10   |       | +10             | mV    |

| POWER SUPPLY                                      |                                        |       | •     |                 |       |

| Power-up Time                                     | CPnEN from 0 to 1                      |       | 20    |                 | μs    |

| Power Supply Rejection                            |                                        |       | 0.1   | 1               | mV/V  |

| Supply Current                                    | Operating Mode (each comparator) at DC |       | 1.5   | 10              | μA    |

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 12.2.2. Data Memory

The CIP-51 implements 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 12.2 illustrates the data memory organization of the CIP-51.

#### 12.2.3. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in Figure 12.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 12.2.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>TM</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 12.2.5. Stack

A programmer's stack can be located anywhere in the 256 byte data memory. The stack area is designated using the Stack Pointer (SP, address 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07; therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

The MCUs also have built-in hardware for a stack record. The stack record is a 32-bit shift register, where each PUSH or increment SP pushes one record bit onto the register, and each CALL pushes two record bits onto the register. (A POP or decrement SP pops one record bit, and a RET pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the 32-bit shift register, and can notify the debug software even with the MCU running at speed.

| R/W         | R/W                             | R/W            | R/W           | R/W           | R/W          | R/W                                     | R/W  | Reset Value |

|-------------|---------------------------------|----------------|---------------|---------------|--------------|-----------------------------------------|------|-------------|

| EXVLD       |                                 | EX7            | EX6           | EADC1         | ET4          | EADC0                                   | ET3  | 00000000    |

| Bit7        | Bit6                            | Bit5           | Bit4          | Bit3          | Bit2         | Bit1                                    | Bit0 | SFR Address |

|             |                                 |                |               |               |              |                                         |      | 0xE7        |

| Bit7:       | EVVI D. Eng                     | hla Erstannal  | Cleak Sau     | a Valid (VTI  | VID) Inton   | mat                                     |      |             |

| DII/.       | EXVLD: Ena<br>This bit sets the |                |               |               | vLD) Inter   | rupi.                                   |      |             |

|             | 0: Disable XT                   | -              |               | LD micrupi.   |              |                                         |      |             |

|             | 1: Enable inte                  |                | 1             | by the XTLV   | LD flag (OS  | SCXCN.7)                                |      |             |

| Bit6:       | ES1: Enable U                   |                |               |               | 22 mg (01    | , , , , , , , , , , , , , , , , , , , , |      |             |

|             | This bit sets the               |                | -             | 1 interrupt.  |              |                                         |      |             |

|             | 0: Disable UA                   | U              |               |               |              |                                         |      |             |

|             | 1: Enable UA                    |                |               |               |              |                                         |      |             |

| Bit5:       | EX7: Enable                     | 1              |               |               |              |                                         |      |             |

|             | This bit sets the               |                | -             | nterrupt 7.   |              |                                         |      |             |

|             | 0: Disable Ex                   | ternal Interru | ıpt 7.        | -             |              |                                         |      |             |

|             | 1: Enable inte                  | rrupt reques   | ts generated  | by the Extern | al Interrupt | 7 input pin.                            |      |             |

| Bit4:       | EX6: Enable                     | External Inte  | errupt 6.     |               |              |                                         |      |             |

|             | This bit sets the               | he masking o   | of External I | nterrupt 6.   |              |                                         |      |             |

|             | 0: Disable Ex                   | ternal Interru | ıpt 6.        |               |              |                                         |      |             |

|             | 1: Enable inte                  |                |               |               |              | 6 input pin.                            |      |             |

| Bit3:       | EADC1: Enal                     |                |               | -             |              |                                         |      |             |

|             | This bit sets the               |                |               |               | ersion inter | rupt.                                   |      |             |

|             | 0: Disable AI                   |                |               | -             |              |                                         |      |             |

|             |                                 | <b>1</b> 1     | 0             | by the ADC1   | End of Cor   | version Interr                          | upt. |             |

| Bit2:       | ET4: Enable                     |                | -             |               |              |                                         |      |             |

|             | This bit sets the               |                |               | 4 interrupt.  |              |                                         |      |             |

|             | 0: Disable Tir                  |                | L             |               | -            | _                                       |      |             |

| <b>D</b> 14 | 1: Enable inte                  |                | -             | •             | -            | .7).                                    |      |             |

| Bit1:       | EADC0: Enal                     |                |               |               |              |                                         |      |             |

|             | This bit sets the               | U              |               |               | ersion Inter | rupt.                                   |      |             |

|             | 0: Disable AL                   |                | 1             |               | а ·          | T, I, I                                 |      |             |

| D:40.       | 1: Enable inte                  |                |               | by the ADCO   | Conversion   | i interrupt.                            |      |             |

| Bit0:       | ET3: Enable 7                   |                | 1             | 2 intomat     |              |                                         |      |             |

|             | This bit sets the               |                |               | 5 interrupt.  |              |                                         |      |             |

|             | 0: Disable all                  |                |               | by the TE2 fl |              | <b>N</b> 7)                             |      |             |

|             | 1: Enable inte                  | mupt reques    | is generated  | by the 1F3 fl | ag (TMR3C    | .1 <b>N</b> ./).                        |      |             |

Figure 12.12. EIE2: Extended Interrupt Enable 2

### 14.1. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be as shown in Figure 14.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in Figure 14.3 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

The Crystal Oscillator Valid Flag (XTLVLD in register OSCXCN) is set to logic 1 by hardware when the external crystal oscillator is running and stable. The XTLVLD detection circuit requires a startup time of at least 1 ms between enabling the oscillator and checking the XTLVLD bit. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

Step 1. Enable the external oscillator.

Step 2. Wait at least 1 ms.

Step 3. Poll for XTLVLD => '1'.

Step 4. Switch the system clock to the external oscillator.

**Important Note:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device, as should the loading capacitors on the crystal pins. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

### 14.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be as shown in Figure 14.1, Option 2. The capacitor must be no greater than 100 pF; however for small capacitors (less than ~20 pF), the total capacitance may be dominated by PWB parasitic capacitance. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let  $R = 246 \text{ k}\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 * 50] = 0.1 MHz = 100 kHz$

$XFCN \ge \log_2 (f / 25 \text{ kHz})$   $XFCN \ge \log_2 (100 \text{ kHz} / 25 \text{ kHz}) = \log_2 (4)$  $XFCN \ge 2, \text{ or code } 010b$

### 14.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be as shown in Figure 14.1, Option 3. The capacitor must be no greater than 100 pF; however for small capacitors (less than ~20 pF), the total capacitance may be dominated by PWB parasitic capacitance. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume VDD = 3.0 V and C = 50 pF:

f = KF / (C \* VDD) = KF / (50 \* 3)f = KF / 150

If a frequency of roughly 90 kHz is desired, select the K Factor from the table in Figure 14.3 as KF = 13:

f = 13 / 150 = 0.087 MHz, or 87 kHz

Therefore, the XFCN value to use in this example is 011b.

| R/W      | R/W                                                                                       | R/W                                        | R/W           | R/W           | R/W           | R/W            | R/W           | Reset Value         |  |  |

|----------|-------------------------------------------------------------------------------------------|--------------------------------------------|---------------|---------------|---------------|----------------|---------------|---------------------|--|--|

| -        | -                                                                                         | -                                          | -             | -             | SFLE          | PSEE           | PSWE          | 00000000            |  |  |

| Bit7     | Bit6                                                                                      | Bit5                                       | Bit4          | Bit3          | Bit2          | Bit1           | Bit0          | SFR Address<br>0x8F |  |  |

| Bits7-3: | UNUSED. Re                                                                                | ad = 00000t                                | o, Write = do | n't care.     |               |                |               |                     |  |  |

| Bit2:    | SFLE: Scratch                                                                             | npad FLASH                                 | I Memory A    | ccess Enable  | e.            |                |               |                     |  |  |

|          | When this bit                                                                             | is set, FLAS                               | H reads and   | writes from   | user software | e are directed | to the 128-   | -byte Scratch       |  |  |

|          | pad FLASH s                                                                               | ector. When                                | SFLE is set   | to logic 1, F | LASH access   | ses out of the | e address rai | nge 0x00-           |  |  |

|          | 0x7F should n                                                                             | not be attemp                              | ted. Reads/V  | Vrites out of | this range w  | ill yield unp  | redictable re | esults.             |  |  |

|          | 0: FLASH acc                                                                              | cess from use                              | er software d | irected to th | e 64k byte Pi | rogram/Data    | FLASH see     | ctor.               |  |  |

|          | 1: FLASH acc                                                                              | cess from use                              | er software d | irected to th | e 128 byte So | cratchpad se   | ctor.         |                     |  |  |

| Bit1:    | PSEE: Program                                                                             | m Store Eras                               | se Enable.    |               |               |                |               |                     |  |  |

|          | Setting this bi                                                                           |                                            |               |               |               |                |               |                     |  |  |

|          | PSWE bit is a                                                                             |                                            |               |               |               |                |               |                     |  |  |

|          | will erase the                                                                            |                                            |               | the location  | addressed by  | the MOVX       | instruction.  | The value o         |  |  |

|          | the data byte v                                                                           |                                            |               |               |               |                |               |                     |  |  |

|          | 0: FLASH pro                                                                              | -                                          | •             |               |               |                |               |                     |  |  |

|          | 1: FLASH pro                                                                              | 0                                          | •             | nabled.       |               |                |               |                     |  |  |

| Bit0:    | PSWE: Progra                                                                              |                                            |               |               |               |                |               |                     |  |  |

|          | Setting this bit allows writing a byte of data to the FLASH program memory using the MOVX |                                            |               |               |               |                |               |                     |  |  |

|          | instruction. The location must be erased before writing data.                             |                                            |               |               |               |                |               |                     |  |  |

|          |                                                                                           | 0: Write to FLASH program memory disabled. |               |               |               |                |               |                     |  |  |

|          |                                                                                           |                                            |               |               |               |                |               |                     |  |  |

### Figure 15.4. PSCTL: Program Store Read/Write Control

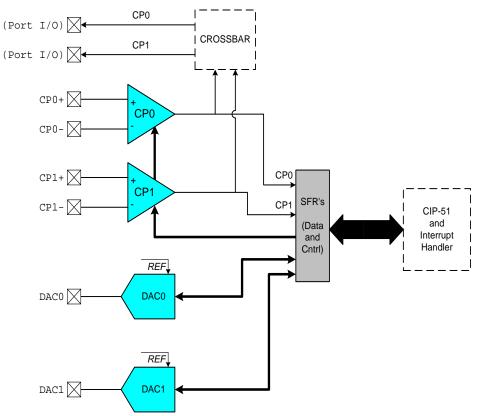

### **16.4.2.** Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Non-multiplexed Configuration is shown in Figure 16.4. See Section "16.6.1. Non-multiplexed Mode" on page 153 for more information about Non-multiplexed operation.

### Figure 16.4. Non-multiplexed Configuration Example

### 16.6.2. Multiplexed Mode

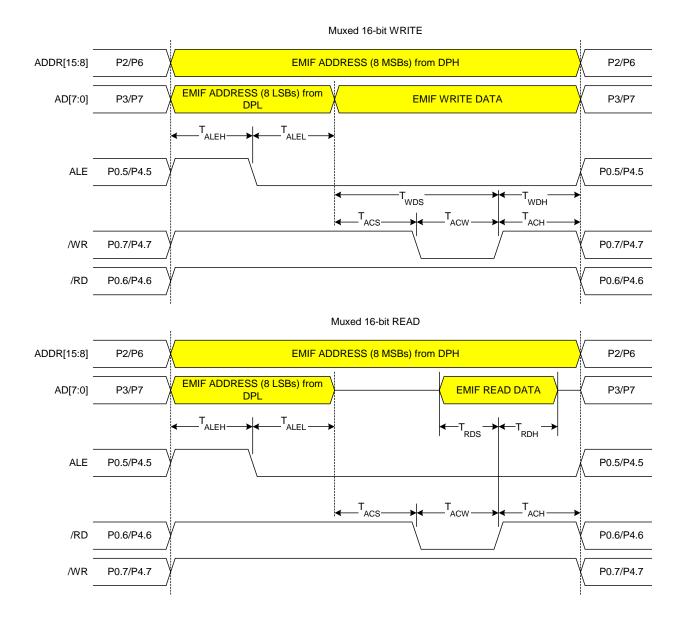

### 16.6.2.1.16-bit MOVX: EMI0CF[4:2] = '001', '010', or '011'.

### Figure 16.10. Multiplexed 16-bit MOVX Timing

#### 17.1.7. External Memory Interface Pin Assignments

If the External Memory Interface (EMIF) is enabled on the Low ports (Ports 0 through 3), EMIFLE (XBR2.1) should be set to a logic 1 so that the Crossbar will not assign peripherals to P0.7 (/WR), P0.6 (/RD), and if the External Memory Interface is in Multiplexed mode, P0.5 (ALE). Figure 17.4 shows an example Crossbar Decode Table with EMIFLE=1 and the EMIF in Multiplexed mode. Figure 17.5 shows an example Crossbar Decode Table with EMIFLE=1 and the EMIF in Non-multiplexed mode.

If the External Memory Interface is enabled on the Low ports and an off-chip MOVX operation occurs, the External Memory Interface will control the output states of the affected Port pins during the execution phase of the MOVX instruction, regardless of the settings of the Crossbar registers or the Port Data registers. The output configuration of the Port pins is not affected by the EMIF operation, except that Read operations will explicitly disable the output drivers on the Data Bus. See Section "16. EXTERNAL DATA MEMORY INTERFACE AND ON-CHIP XRAM" on page 145 for more information about the External Memory Interface.

#### P0 **P1 P2** P3 Crossbar Register Bits PIN I/O 0 2 3 4 5 7 0 3 4 5 0 3 4 1 6 1 2 6 1 2 -5 6 7 тхо UARTOEN: XBR0.2 RX0 SCK MISO SPI0EN: XBR0.1 MOSI NSS SDA . • SMB0EN: XBR0.0 SCI TX1 • UART1EN: XBR2.2 RX1 CEX0 CEX1 CEX2 PCA0ME: XBR0.[5:3] CEX3 CEX4 ECI ECIOE: XBR0.6 • ۰ ٠ ٠ ٠ • • ٠ • • • ٠ • • CP0 CP0E: XBR0.7 • • • • • • • • . • . • • • • CP1 CP1E: XBR1.0 ٠ • • • • • • • • • • • • ٠ то T0E: XBR1.1 • ٠ • • • ٠ • • • • ٠ • ٠ ٠ • /INTO INTOE: XBR1.2 ٠ • . ٠ ٠ • • • ٠ • • ٠ ٠ • • Т1 T1E: XBR1.3 • ٠ • • • • • • • • • ٠ • • • • /INT1 INT1E: XBR1.4 • . • • ٠ • • • • • • • • • • Т2 T2E: XBR1.5 • • . • • • • • • • • T2EX • ٠ • • • ٠ ٠ • • ٠ ٠ • T2EXE: XBR1.6 T4E: XBR2.3 • • • ٠ ٠ • ٠ ٠ • • • . . ٠ • • • T4EX T4EXE: XBR2.4 • • • ٠ • ٠ • ٠ ٠ • ٠ ٠ • • • . • • • ٠ ٠ • • • /SYSCLK SYSCKE: XBR1.7 . . . . . • • • • CNVSTR CNVSTE: XBR2.0 • • • • • • • • • • • • • . AIN1.7/A1 10m/A2 13m/A5 AIN1.1/A9 v11m/A3 12m/A4 15m/A7 0/A8 AIN1.2/A 3/A` .4/A 5/A .6/A 8m/A0 14m/A6 A9m/A1 A DO/DO **VD1/D1** D2/D2 D3/D3 ND4/D4 **D5/D5** D6/D6 70/70 Į, AIN1 AIN1. AIN1. AIN1 ALE ŴR AIN1 Inputs/Non-muxed Addr H Muxed Addr H/Non-muxed Addr L Muxed Data/Non-muxed Data

### Figure 17.4. Priority Crossbar Decode Table EMIFLE = 1; EMIF in Multiplexed Mode; P1MDIN = 0xFF)

| R/W    | R/W                            | R/W           | R/W      | R/W  | R/W   | R/W  | R/W  | Reset Value |

|--------|--------------------------------|---------------|----------|------|-------|------|------|-------------|

| SYSCKI | E T2EXE                        | T2E           | INT1E    | T1E  | INT0E | T0E  | CP1E | 00000000    |

| Bit7   | Bit6                           | Bit5          | Bit4     | Bit3 | Bit2  | Bit1 | Bit0 | SFR Address |

|        |                                |               |          |      |       |      |      | 0xE2        |

| Bit7:  | SYSCKE: /SY                    |               | -        | t.   |       |      |      |             |

|        | 0: /SYSCLK u                   |               | -        |      |       |      |      |             |

|        | 1: /SYSCLK 1                   |               | -        |      |       |      |      |             |

| Bit6:  | T2EXE: T2EX                    | -             |          |      |       |      |      |             |

|        | 0: T2EX unav                   | ailable at P  | ort pin. |      |       |      |      |             |

|        | 1: T2EX route                  | ed to Port pi | n.       |      |       |      |      |             |

| Bit5:  | T2E: T2 Input                  | Enable Bit    |          |      |       |      |      |             |

|        | 0: T2 unavaila                 |               | pin.     |      |       |      |      |             |

|        | 1: T2 routed to                | o Port pin.   |          |      |       |      |      |             |

| Bit4:  | INT1E: /INT1                   | Input Enab    | ole Bit. |      |       |      |      |             |

|        | 0: /INT1 unav                  | ailable at P  | ort pin. |      |       |      |      |             |

|        | 1: /INT1 route                 | ed to Port pi | n.       |      |       |      |      |             |

| Bit3:  | T1E: T1 Input                  | Enable Bit    | •        |      |       |      |      |             |

|        | 0: T1 unavaila                 |               | pin.     |      |       |      |      |             |

|        | 1: T1 routed to                | o Port pin.   |          |      |       |      |      |             |

| Bit2:  | INTOE: /INTO                   | Input Enab    | ole Bit. |      |       |      |      |             |

|        | 0: /INT0 unav                  | ailable at P  | ort pin. |      |       |      |      |             |

|        | 1: /INT1 route                 | ed to Port pi | n.       |      |       |      |      |             |

| Bit1:  | T0E: T0 Input                  | Enable Bit    |          |      |       |      |      |             |

|        | 0: T0 unavailable at Port pin. |               |          |      |       |      |      |             |

|        | 1: T0 routed to                | o Port pin.   |          |      |       |      |      |             |

| Bit0:  | CP1E: CP1 O                    | utput Enabl   | e Bit.   |      |       |      |      |             |

|        | 0: CP1 unavai                  | lable at Por  | t pin.   |      |       |      |      |             |

|        | 1: CP1 routed                  | to Port pin.  |          |      |       |      |      |             |

### Figure 17.8. XBR1: Port I/O Crossbar Register 1

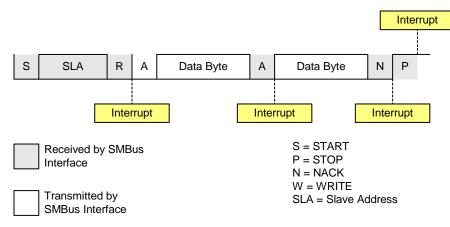

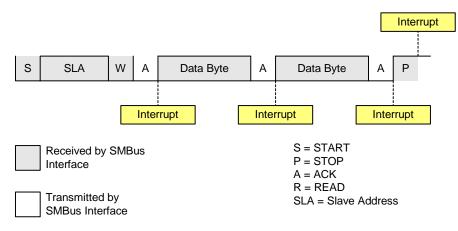

### 18.3.3. Slave Transmitter Mode

Serial data is transmitted on SDA while the serial clock is received on SCL. The SMBus0 interface receives a START followed by data byte containing the slave address and direction bit. If the received slave address matches the address held in register SMB0ADR, the SMBus0 interface generates an ACK. SMBus0 will also ACK if the general call address (0x00) is received and the General Call Address Enable bit (SMB0ADR.0) is set to logic 1. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives the clock on SCL and transmits one or more bytes of serial data, waiting for an ACK from the master after each byte. SMBus0 exits slave mode after receiving a STOP condition from the master.

#### **18.3.4.** Slave Receiver Mode

Serial data is received on SDA while the serial clock is received on SCL. The SMBus0 interface receives a START followed by data byte containing the slave address and direction bit. If the received slave address matches the address held in register SMB0ADR, the interface generates an ACK. SMBus0 will also ACK if the general call address (0x00) is received and the General Call Address Enable bit (SMB0ADR.0) is set to logic 1. In this case the data direction bit (R/W) will be logic 0 to indicate a "WRITE" operation. The SMBus0 interface receives one or more bytes of serial data; after each byte is received, the interface transmits an ACK or NACK depending on the state of the AA bit in SMB0CN. SMBus0 exits Slave Receiver Mode after receiving a STOP condition from the master.

| R/W  | R/W                                                                                                                                                                                                                                                                                                                                                                                          | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value 00000000 |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|----------------------|--|

| Bit7 | Bit6                                                                                                                                                                                                                                                                                                                                                                                         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0x99 |  |

|      | Bits7-0: SBUF0.[7:0]: UART0 Buffer Bits 7-0 (MSB-LSB)<br>This SFR accesses two registers; a transmit shift register and a receive latch register. When data is<br>written to SBUF0, it goes to the transmit shift register and is held for serial transmission. Writing a<br>byte to SBUF0 is what initiates the transmission. A read of SBUF0 returns the contents of the receive<br>latch. |      |      |      |      |      |      |                      |  |

### Figure 20.9. SBUF0: UART0 Data Buffer Register

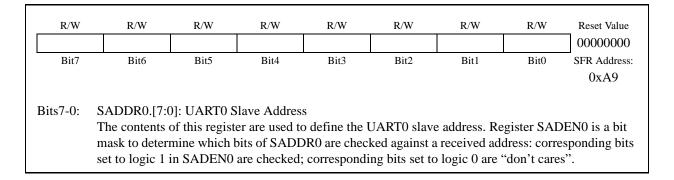

### Figure 20.10. SADDR0: UART0 Slave Address Register

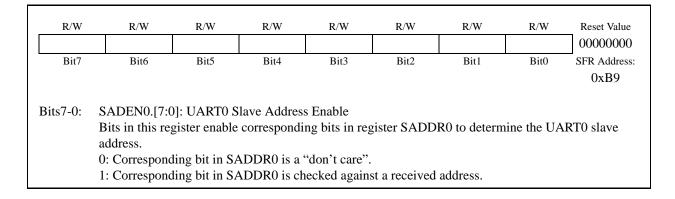

### Figure 20.11. SADEN0: UARTO Slave Address Enable Register

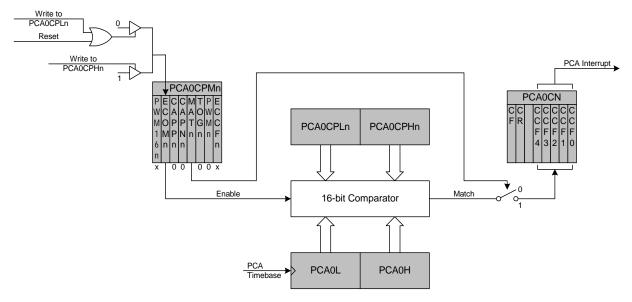

### 23.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes PCA0 to capture the value of the PCA0 counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software.

### Figure 23.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles in order to be valid.

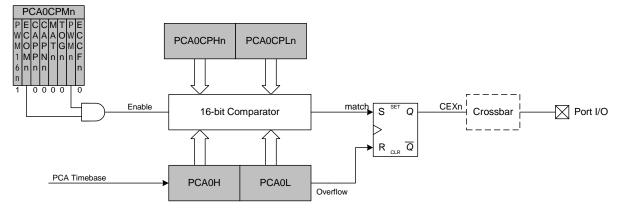

### 23.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA0 counter/timer is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 23.5. PCA Software Timer Mode Diagram

#### 23.2.6. 16-Bit Pulse Width Modulator Mode

Each PCA0 module may also be operated in 16-Bit PWM mode. In this mode, the 16-bit capture/compare module defines the number of PCA0 clocks for the low time of the PWM signal. When the PCA0 counter matches the module contents, the output on CEXn is asserted high; when the counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA0 CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, CCFn should also be set to logic 1 to enable match interrupts. The duty cycle for 16-Bit PWM Mode is given by Equation 23.3.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'

### Equation 23.3. 16-Bit PWM Duty Cycle

$DutyCycle = \frac{(65536 - PCA0CPn)}{65536}$

Using Equation 23.3, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

#### Figure 23.9. PCA 16-Bit PWM Mode

| R/W                                                                                                                            | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000 |

|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|-------------------------|

| Bit7                                                                                                                           | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:            |

|                                                                                                                                |      |      |      |      |      |      |      | 0xE9                    |

| Bits 7-0: PCA0L: PCA0 Counter/Timer Low Byte.<br>The PCA0L register holds the low byte (LSB) of the 16-bit PCA0 Counter/Timer. |      |      |      |      |      |      |      |                         |

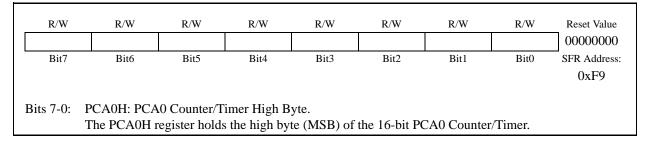

### Figure 23.13. PCA0L: PCA0 Counter/Timer Low Byte

### Figure 23.14. PCA0H: PCA0 Counter/Timer High Byte

### 24.2. Flash Programming Commands

The Flash memory can be programmed directly over the JTAG interface using the Flash Control, Flash Data, Flash Address, and Flash Scale registers. These Indirect Data Registers are accessed via the JTAG Instruction Register. Read and write operations on indirect data registers are performed by first setting the appropriate DR address in the IR register. Each read or write is then initiated by writing the appropriate Indirect Operation Code (IndOpCode) to the selected data register. Incoming commands to this register have the following format:

| 19:18     | 17:0      |

|-----------|-----------|

| IndOpCode | WriteData |

IndOpCode: These bit set the operation to perform according to the following table:

| IndOpCode | Operation |

|-----------|-----------|

| 0x        | Poll      |

| 10        | Read      |

| 11        | Write     |

The Poll operation is used to check the Busy bit as described below. Although a Capture-DR is performed, no Update-DR is allowed for the Poll operation. Since updates are disabled, polling can be accomplished by shifting in/ out a single bit.

The Read operation initiates a read from the register addressed by the DRAddress. Reads can be initiated by shifting only 2 bits into the indirect register. After the read operation is initiated, polling of the Busy bit must be performed to determine when the operation is complete.

The write operation initiates a write of WriteData to the register addressed by DRAddress. Registers of any width up to 18 bits can be written. If the register to be written contains fewer than 18 bits, the data in WriteData should be left-justified, i.e. its MSB should occupy bit 17 above. This allows shorter registers to be written in fewer JTAG clock cycles. For example, an 8-bit register could be written by shifting only 10 bits. After a Write is initiated, the Busy bit should be polled to determine when the next operation can be initiated. The contents of the Instruction Register should not be altered while either a read or write operation is busy.

Outgoing data from the indirect Data Register has the following format:

| 19 | 18:1     | 0    |  |

|----|----------|------|--|

| 0  | ReadData | Busy |  |

The Busy bit indicates that the current operation is not complete. It goes high when an operation is initiated and returns low when complete. Read and Write commands are ignored while Busy is high. In fact, if polling for Busy to be low will be followed by another read or write operation, JTAG writes of the next operation can be made while checking for Busy to be low. They will be ignored until Busy is read low, at which time the new operation will initiate. This bit is placed ate bit 0 to allow polling by single-bit shifts. When waiting for a Read to complete and Busy is 0, the following 18 bits can be shifted out to obtain the resulting data. ReadData is always right-justified. This allows registers shorter than 18 bits to be read using a reduced number of shifts. For example, the results from a byte-read requires 9 bit shifts (Busy + 8 bits).