Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT             |

| Number of I/O              | 32                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 4.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b, 8x12b; D/A 2x12b                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 64-TQFP                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f021-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Notes

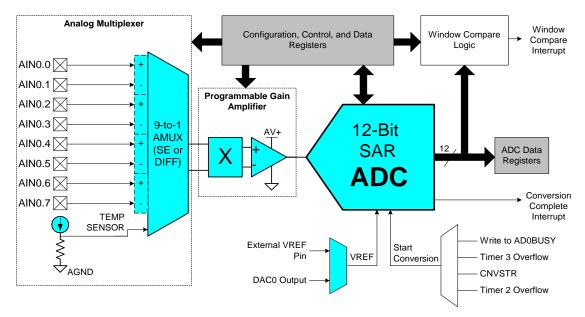

### 1.7. 12-Bit Analog to Digital Converter

The C8051F020/1 has an on-chip 12-bit SAR ADC (ADC0) with a 9-channel input multiplexer and programmable gain amplifier. With a maximum throughput of 100 ksps, the ADC offers true 12-bit accuracy with an INL of  $\pm$ 1LSB. C8051F022/3 devices include a 10-bit SAR ADC with similar specifications and configuration options. The ADC0 voltage reference is selected between the DAC0 output and an external VREF pin. On C8051F020/2 devices, ADC0 has its own dedicated VREF0 input pin; on C8051F021/3 devices, the ADC0 shares the VREFA input pin with the 8-bit ADC1. The on-chip 15 ppm/°C voltage reference may generate the voltage reference for other system components or the on-chip ADCs via the VREF output pin.

The ADC is under full control of the CIP-51 microcontroller via its associated Special Function Registers. One input channel is tied to an internal temperature sensor, while the other eight channels are available externally. Each pair of the eight external input channels can be configured as either two single-ended inputs or a single differential input. The system controller can also put the ADC into shutdown mode to save power.

A programmable gain amplifier follows the analog multiplexer. The gain can be set in software from 0.5 to 16 in powers of 2. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset (in differential mode, a DAC could be used to provide the DC offset).

Conversions can be started in four ways; a software command, an overflow of Timer 2, an overflow of Timer 3, or an external signal input. This flexibility allows the start of conversion to be triggered by software events, external HW signals, or a periodic timer overflow signal. Conversion completions are indicated by a status bit and an interrupt (if enabled). The resulting 10 or 12-bit data word is latched into two SFRs upon completion of a conversion. The data can be right or left justified in these registers under software control.

Window Compare registers for the ADC data can be configured to interrupt the controller when ADC data is within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within the specified window.

### Figure 1.11. 12-Bit ADC Block Diagram

# Notes

## Figure 5.11. ADC0 Data Word Example (C8051F020/1)

| <b>12-bit ADC0 Data Word appears in the ADC0 Data Word Registers as follows:</b><br>ADC0H[3:0]:ADC0L[7:0], if AD0LJST = 0<br>(ADC0H[7:4] will be sign-extension of ADC0H.3 for a differential reading, otherwise = 0000b). |                                                                       |                                                        |            |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|------------|--|--|--|--|--|--|--|--|

| ADC0H[7:0]:ADC0L[<br>(ADC0L[3:0]                                                                                                                                                                                           |                                                                       |                                                        |            |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                          | Word Conversion Map,<br>0x00, AMX0SL = 0x00)                          | AIN0 Input in Single-En                                | ded Mode   |  |  |  |  |  |  |  |  |

| AIN0-AGND (Volts)ADC0H:ADC0L<br>(AD0LJST = 0)ADC0H:ADC0L<br>(AD0LJST = 1)                                                                                                                                                  |                                                                       |                                                        |            |  |  |  |  |  |  |  |  |

| VREF * (4095/4096)                                                                                                                                                                                                         | 0x0FFF                                                                | 0xFFF0                                                 |            |  |  |  |  |  |  |  |  |

| VREF / 2                                                                                                                                                                                                                   | 0x0800                                                                | 0x8000                                                 |            |  |  |  |  |  |  |  |  |

| VREF * (2047/4096)                                                                                                                                                                                                         |                                                                       |                                                        |            |  |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                          |                                                                       |                                                        |            |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                          | Word Conversion Map,<br>0x01, AMX0SL = $0x00ADC0H:ADC0L(AD0LJST = 0)$ | AIN0-AIN1 Differential<br>ADC0H:ADC0L<br>(AD0LJST = 1) | Input Pair |  |  |  |  |  |  |  |  |

| VREF * (2047/2048)                                                                                                                                                                                                         | 0x07FF                                                                | 0x7FF0                                                 |            |  |  |  |  |  |  |  |  |

| VREF / 2                                                                                                                                                                                                                   | 0x0400                                                                | 0x4000                                                 |            |  |  |  |  |  |  |  |  |

| VREF * (1/2048)                                                                                                                                                                                                            | 0x0001                                                                | 0x0010                                                 | ]          |  |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                          | 0x0000                                                                | 0x0000                                                 | 1          |  |  |  |  |  |  |  |  |

| -VREF * (1/2048)                                                                                                                                                                                                           | 0xFFFF (-1d)                                                          | 0xFFF0                                                 | ]          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                            | 0 = EC00 (10244)                                                      | 0xC000                                                 | 1          |  |  |  |  |  |  |  |  |

| -VREF / 2                                                                                                                                                                                                                  | 0xFC00 (-1024d)                                                       | 0xC000                                                 |            |  |  |  |  |  |  |  |  |

For AD0LJST = 0:

$Code = Vin \times \frac{Gain}{VREF} \times 2^n$ ; 'n' = 12 for Single-Ended; 'n'=11 for Differential.

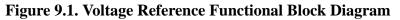

## 9. VOLTAGE REFERENCE (C8051F020/2)

The voltage reference circuit offers full flexibility in operating the ADC and DAC modules. Three voltage reference input pins allow each ADC and the two DACs to reference an external voltage reference or the on-chip voltage reference output. ADC0 may also reference the DAC0 output internally, and ADC1 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.1.

The internal voltage reference circuit consists of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins shown in Figure 9.1. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND, as shown in Figure 9.1. See Table 9.1 for voltage reference specifications.

The Reference Control Register, REF0CN (defined in Figure 9.2) enables/disables the internal reference generator and selects the reference inputs for ADC0 and ADC1. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if either DAC or ADC is used, regardless of whether the voltage reference is derived from the on-chip reference or supplied by an off-chip source. If neither the ADC nor the DAC are being used, both of these bits can be set to logic 0 to conserve power. Bits AD0VRS and AD1VRS select the ADC0 and ADC1 voltage reference sources, respectively. The electrical specifications for the Voltage Reference circuit are given in Table 9.1.

#### **12.2.7. Register Descriptions**

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic l. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

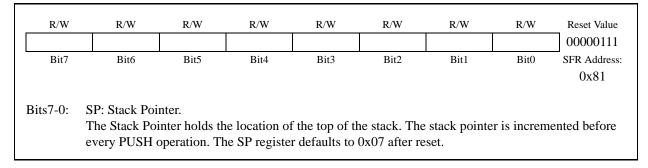

#### Figure 12.3. SP: Stack Pointer

### Figure 12.4. DPL: Data Pointer Low Byte

| R/W      | R/W                                        | R/W            | R/W  | R/W          | R/W          | R/W           | R/W           | Reset Value<br>00000000 |

|----------|--------------------------------------------|----------------|------|--------------|--------------|---------------|---------------|-------------------------|

| Bit7     | Bit6                                       | Bit5           | Bit4 | Bit3         | Bit2         | Bit1          | Bit0          | SFR Address:<br>0x82    |

| Bits7-0: | DPL: Data Po<br>The DPL regi<br>XRAM and F | ster is the lo | •    | e 16-bit DPT | R. DPTR is u | used to acces | ss indirectly | v addressed             |

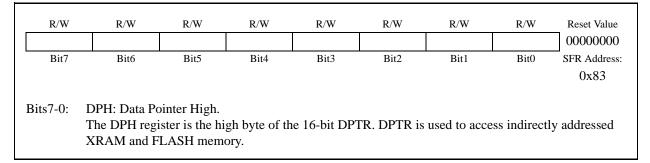

#### Figure 12.5. DPH: Data Pointer High Byte

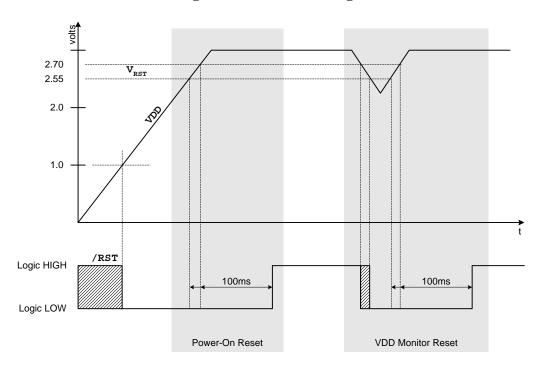

#### 13.1. Power-on Reset

The C8051F020/1/2/3 family incorporates a power supply monitor that holds the MCU in the reset state until VDD rises above the  $V_{RST}$  level during power-up. See Figure 13.2 for timing diagram, and refer to Table 13.1 for the Electrical Characteristics of the power supply monitor circuit. The /RST pin is asserted low until the end of the 100 ms VDD Monitor timeout in order to allow the VDD supply to stabilize.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. All of the other reset flags in the RSTSRC Register are indeterminate. PORSF is cleared by all other resets. Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The contents of internal data memory should be assumed to be undefined after a power-on reset.

# The VDD monitor function is enabled by tying the MONEN pin directly to VDD. This is the recommended configuration for the MONEN pin.

#### Figure 13.2. Reset Timing

#### 13.2. Power-fail Reset

When a power-down transition or power irregularity causes VDD to drop below  $V_{RST}$ , the power supply monitor will drive the /RST pin low and return the CIP-51 to the reset state. When VDD returns to a level above VRST, the CIP-51 will leave the reset state in the same manner as that for the power-on reset (see Figure 13.2). Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if VDD dropped below the level required for data retention. If the PORSF flag is set to logic 1, the data may no longer be valid.

MCU with proprietary value-added firmware before distribution. The value-added firmware can be protected while allowing additional code to be programmed in remaining program memory space later.

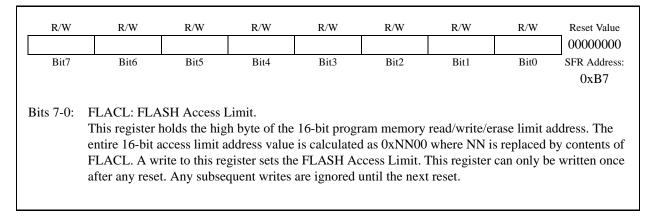

The Software Read Limit (SRL) is a 16-bit address that establishes two logical partitions in the program memory space. The first is an upper partition consisting of all the program memory locations at or above the SRL address, and the second is a lower partition consisting of all the program memory locations starting at 0x0000 up to (but excluding) the SRL address. Software in the upper partition can execute code in the lower partition, but is prohibited from reading locations in the lower partition using the MOVC instruction. (Executing a MOVC instruction from the upper partition with a source address in the lower partition will always return a data value of 0x00.) Software running in the lower partition can access locations in both the upper and lower partition without restriction.

The Value-added firmware should be placed in the lower partition. On reset, control is passed to the value-added firmware via the reset vector. Once the value-added firmware completes its initial execution, it branches to a predetermined location in the upper partition. If entry points are published, software running in the upper partition may execute program code in the lower partition, but it cannot read the contents of the lower partition. Parameters may be passed to the program code running in the lower partition either through the typical method of placing them on the stack or in registers before the call or by placing them in prescribed memory locations in the upper partition.

The SRL address is specified using the contents of the FLASH Access Register. The 16-bit SRL address is calculated as 0xNN00, where NN is the contents of the SRL Security Register. Thus, the SRL can be located on 256-byte boundaries anywhere in program memory space. However, the 512-byte erase sector size essentially requires that a 512 boundary be used. The contents of a non-initialized SRL security byte is 0x00, thereby setting the SRL address to 0x0000 and allowing read access to all locations in program memory space by default.

#### Figure 15.2. FLACL: FLASH Access Limit

| R/W      | R/W                              | R/W           | R/W           | R/W           | R/W           | R/W            | R/W           | Reset Value         |

|----------|----------------------------------|---------------|---------------|---------------|---------------|----------------|---------------|---------------------|

| -        | -                                | -             | -             | -             | SFLE          | PSEE           | PSWE          | 00000000            |

| Bit7     | Bit6                             | Bit5          | Bit4          | Bit3          | Bit2          | Bit1           | Bit0          | SFR Address<br>0x8F |

| Bits7-3: | UNUSED. Re                       | ad = 00000t   | o, Write = do | n't care.     |               |                |               |                     |

| Bit2:    | SFLE: Scratch                    | npad FLASH    | I Memory A    | ccess Enable  | e.            |                |               |                     |

|          | When this bit                    | is set, FLAS  | H reads and   | writes from   | user software | e are directed | to the 128-   | -byte Scratch       |

|          | pad FLASH s                      | ector. When   | SFLE is set   | to logic 1, F | LASH access   | ses out of the | e address rai | nge 0x00-           |

|          | 0x7F should n                    | not be attemp | ted. Reads/V  | Vrites out of | this range w  | ill yield unp  | redictable re | esults.             |

|          | 0: FLASH acc                     | cess from use | er software d | irected to th | e 64k byte Pi | rogram/Data    | FLASH see     | ctor.               |

|          | 1: FLASH acc                     | cess from use | er software d | irected to th | e 128 byte So | cratchpad se   | ctor.         |                     |

| Bit1:    | PSEE: Program                    | m Store Eras  | se Enable.    |               |               |                |               |                     |

|          | Setting this bi                  |               |               |               |               |                |               |                     |

|          | PSWE bit is a                    |               |               |               |               |                |               |                     |

|          | will erase the                   |               |               | the location  | addressed by  | the MOVX       | instruction.  | The value o         |

|          | the data byte v                  |               |               |               |               |                |               |                     |

|          | 0: FLASH pro                     | -             | •             |               |               |                |               |                     |

|          | 1: FLASH pro                     | 0             | •             | nabled.       |               |                |               |                     |

| Bit0:    | PSWE: Progra                     |               |               |               |               |                |               |                     |

|          | Setting this bi                  |               |               |               |               | ram memory     | y using the N | MOVX                |

|          | instruction. Th                  | he location n | nust be erase | d before wr   | iting data.   |                |               |                     |

|          |                                  |               |               |               |               |                |               |                     |

|          | 0: Write to FL<br>1: Write to FL |               |               |               |               |                |               |                     |

## Figure 15.4. PSCTL: Program Store Read/Write Control

| R/W      | R/W                                                                                                             | R/W                                                                | R/W                           | R/W          | R/W    | R/W    | R/W    | Reset Value  |

|----------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------|--------------|--------|--------|--------|--------------|

| PGSEL    | PGSEL6                                                                                                          | PGSEL5                                                             | PGSEL4                        | PGSEL3       | PGSEL2 | PGSEL1 | PGSEL0 | 0000000      |

| Bit7     | Bit6                                                                                                            | Bit5                                                               | Bit4                          | Bit3         | Bit2   | Bit1   | Bit0   | SFR Address: |

|          |                                                                                                                 |                                                                    |                               |              |        |        |        | 0xAF         |

| Bits7-0: | PGSEL[7:0]:<br>The XRAM F<br>using an 8-bit<br>0x00: 0x0000<br>0x01: 0x0100<br><br>0xFE: 0xFE00<br>0xFF: 0xFF00 | Page Select E<br>MOVX con<br>to 0x00FF<br>to 0x01FF<br>0 to 0xFEFF | its provide t<br>nmand, effec | he high byte |        |        | •      | ddress when  |

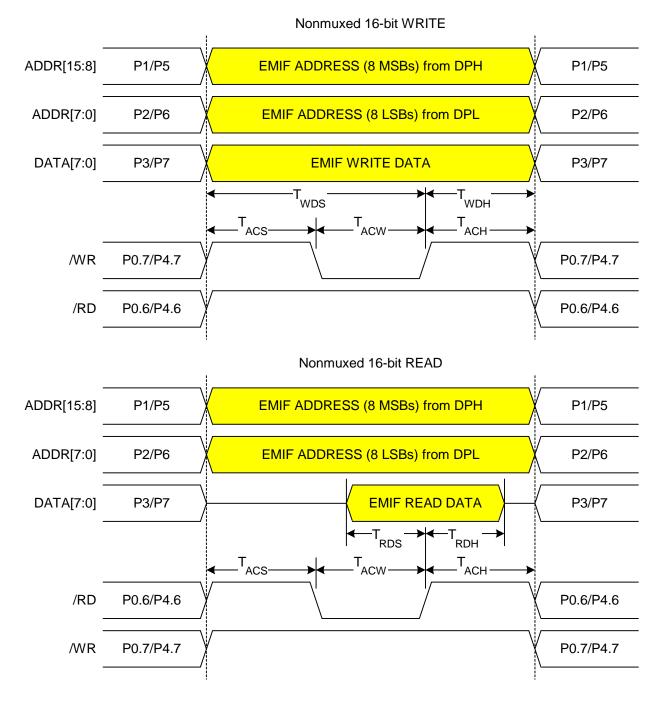

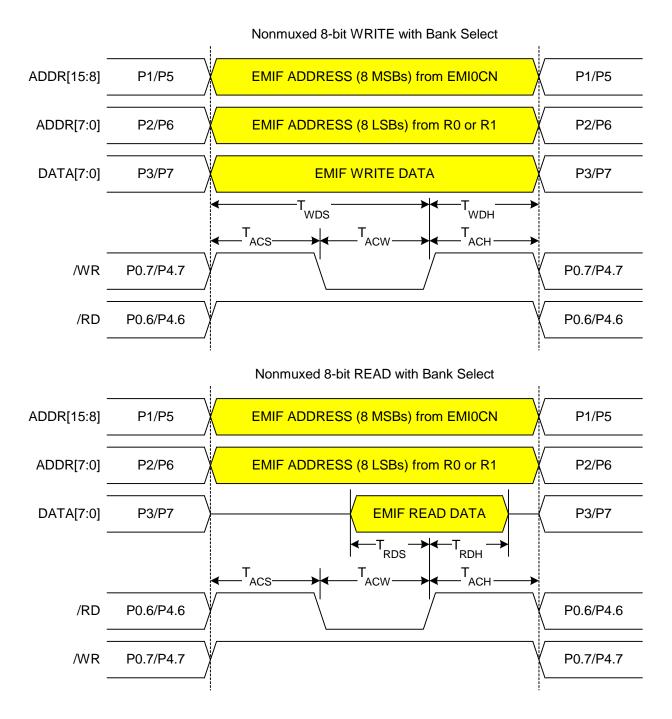

## Figure 16.1. EMIOCN: External Memory Interface Control

## Figure 16.2. EMI0CF: External Memory Configuration

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reset Value  |  |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|--|--|--|--|--|

| <ul> <li>Bits7-6: Unused. Read = 00b. Write = don't care.</li> <li>Bit5: PRTSEL: EMIF Port Select.</li> <li>0: EMIF active on P0-P3.</li> <li>1: EMIF active on P4-P7.</li> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context and the specific chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                          | 00000011     |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Bit5: PRTSEL: EMIF Port Select.</li> <li>0: EMIF active on P0-P3.</li> <li>1: EMIF active on P4-P7.</li> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMIOCN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context space.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SFR Address: |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Bit5: PRTSEL: EMIF Port Select.</li> <li>0: EMIF active on P0-P3.</li> <li>1: EMIF active on P4-P7.</li> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMIOCN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context space.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0xA3         |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Bit5: PRTSEL: EMIF Port Select.</li> <li>0: EMIF active on P0-P3.</li> <li>1: EMIF active on P4-P7.</li> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMIOCN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Adabove the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context space.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>0: EMIF active on P0-P3.</li> <li>1: EMIF active on P4-P7.</li> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Address to a page that is not contained in the on-chip address space.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>1: EMIF active on P4-P7.</li> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMIOCN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Active address the function of the Address and the set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Active address are address and the set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Active address the function of the address and the set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Active address the function of the function of the set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Active address the function of the function of the function of the set to a page that is not contained in the on-chip address space.</li> </ul> |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Bit4: EMD2: EMIF Multiplex Mode Select.</li> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.</li> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context of the 4k boundary are directed off-chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>0: EMIF operates in multiplexed address/data mode.</li> <li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.<br/>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context of the Address and the bank Select: Accesses below the 4k boundary are directed on-chip. Address byte with Bank Select: Accesses below the 4k boundary are directed on-chip. Address byte with Bank Select: Accesses below the 4k boundary are directed on-chip. Address byte with Bank Select: Accesses below the 4k boundary are directed on-chip. Address byte with Bank Select: Accesses below the 4k boundary are directed on-chip. Address byte with Bank Select: Accesses below the 4k boundary are directed on-chip. Address byte with Bank Select: Accesses below the 4k boundary are directed on-chip. Address byte byte byte byte byte byte byte byte</li></ul>                                                                                                                                                                                                                                                                                                                         |              |  |  |  |  |  |  |  |  |  |  |  |

| <ol> <li>EMIF operates in non-multiplexed mode (separate address and data pins).</li> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.<br/>These bits control the operating mode of the External Memory Interface.<br/>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.<br/>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip.<br/>above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip.</li> </ol>                                                                                                                                                                                                                                                 |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>Bits3-2: EMD1-0: EMIF Operating Mode Select.<br/>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the curren of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed on-chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>These bits control the operating mode of the External Memory Interface.</li> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the curren of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context of the address space.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to or memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the curren of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Accesses below the 4k boundary are directed on-chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>memory space.</li> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip.</li> <li>above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Address below the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context above the 4k boundary are directed off-chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | n shin       |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>01: Split Mode without Bank Select: Accesses below the 4k boundary are directed on-chip. above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the curren of the Address High port latches to resolve upper address byte. Note that in order to access space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Ad above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context off-chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | n-emp        |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the current of the Address High port latches to resolve upper address byte. Note that in order to access space, EMIOCN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Address the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the context off-chip.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |  |  |  |  |  |  |  |  |  |  |  |

| of the Address High port latches to resolve upper address byte. Note that in order to access<br>space, EMIOCN must be set to a page that is not contained in the on-chip address space.<br>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Ac<br>above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the conte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |  |  |  |  |  |  |  |  |  |  |  |

| space, EMI0CN must be set to a page that is not contained in the on-chip address space.<br>10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Ac<br>above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the conte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |  |  |  |  |  |  |  |  |  |  |  |

| 10: Split Mode with Bank Select: Accesses below the 4k boundary are directed on-chip. Ac above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the conte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |  |  |  |  |  |  |  |  |  |  |  |

| above the 4k boundary are directed off-chip. 8-bit off-chip MOVX operations use the conte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | accesses     |  |  |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |  |  |  |  |  |  |  |  |  |  |  |

| Entricer, to determine the men byte of the dualoos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |  |  |  |  |  |  |  |  |  |  |  |

| 11: External Only: MOVX accesses off-chip XRAM only. On-chip XRAM is not visible to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | o the CPU.   |  |  |  |  |  |  |  |  |  |  |  |

| Bits1-0: EALE1-0: ALE Pulse-Width Select Bits (only has effect when $EMD2 = 0$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |  |  |  |  |  |  |  |  |  |  |  |

| 00: ALE high and ALE low pulse width = 1 SYSCLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |  |  |  |  |  |  |  |  |  |  |  |

| 01: ALE high and ALE low pulse width = 2 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |  |  |  |  |  |  |  |  |  |  |  |