Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 4.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 8x8b, 8x12b; D/A 2x12b                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 64-TQFP                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f021 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **1.1.** CIP-51<sup>TM</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F020 family utilizes Silicon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The core has all the peripherals included with a standard 8052, including five 16-bit counter/timers, two full-duplex UARTs, 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and 8/4 byte-wide I/O Ports.

#### **1.1.2.** Improved Throughput

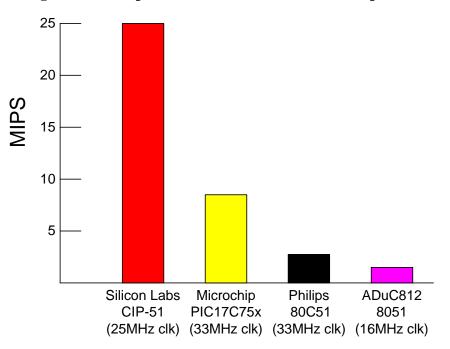

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.5 shows a comparison of peak throughputs of various 8-bit microcontroller cores with their maximum system clocks.

## Figure 1.5. Comparison of Peak MCU Execution Speeds

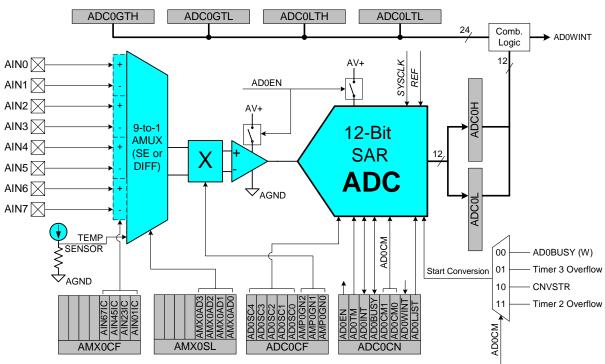

## 5. ADC0 (12-BIT ADC, C8051F020/1 ONLY)

The ADC0 subsystem for the C8051F020/1 consists of a 9-channel, configurable analog multiplexer (AMUX0), a programmable gain amplifier (PGA0), and a 100 ksps, 12-bit successive-approximation-register ADC with integrated track-and-hold and Programmable Window Detector (see block diagram in Figure 5.1). The AMUX0, PGA0, Data Conversion Modes, and Window Detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. The voltage reference used by ADC0 is selected as described in Section "9. VOLTAGE REFERENCE (C8051F020/2)" on page 91 for C8051F020/2 devices, or Section "10. VOLTAGE REFERENCE (C8051F021/3)" on page 93 for C8051F021/3 devices. The ADC0 subsystem (ADC0, track-and-hold and PGA0) is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

## 5.1. Analog Multiplexer and PGA

Eight of the AMUX channels are available for external measurements while the ninth channel is internally connected to an on-chip temperature sensor (temperature transfer function is shown in Figure 5.2). AMUX input pairs can be programmed to operate in either differential or single-ended mode. This allows the user to select the best measurement technique for each input channel, and even accommodates mode changes "on-the-fly". The AMUX defaults to all single-ended inputs upon reset. There are two registers associated with the AMUX: the Channel Selection register AMX0SL (Figure 5.6), and the Configuration register AMX0CF (Figure 5.7). The table in Figure 5.6 shows AMUX functionality by channel, for each possible configuration. The PGA amplifies the AMUX output signal by an amount determined by the states of the AMP0GN2-0 bits in the ADC0 Configuration register, ADC0CF (Figure 5.7). The PGA can be software-programmed for gains of 0.5, 2, 4, 8 or 16. Gain defaults to unity on reset.

| R/W      | R/W                                                    | R/W                   | R/W          | R/W  | R/W  | R/W  | R/W  | Reset Value  |

|----------|--------------------------------------------------------|-----------------------|--------------|------|------|------|------|--------------|

|          |                                                        |                       |              |      |      |      |      | 00000000     |

| Bit7     | Bit6                                                   | Bit5                  | Bit4         | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|          |                                                        |                       |              |      |      |      |      | 0xBF         |

| Bits7-0: | ADC Data Wo<br>For ADLJST<br>ADC Data Wo<br>For ADLJST | = 0: Bits 7-2<br>ord. | are the sign |      |      |      | -    | f the 10-bit |

## Figure 6.10. ADC0L: ADC0 Data Word LSB Register (C8051F022/3)

| R/W      | R/W                                   | R/W           | R/W          | R/W  | R/W  | R/W  | R/W  | Reset Value          |

|----------|---------------------------------------|---------------|--------------|------|------|------|------|----------------------|

| Bit7     | Bit6                                  | Bit5          | Bit4         | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xBE |

| Bits7-0: | ADC Data Wo                           | ord Low-Ord   | ler Bits.    |      |      |      |      | UXBE                 |

| 2107 01  | For ADLJST<br>For ADLJST<br>read '0'. | = 0: Bits 7-0 | are the lowe |      |      |      | -    | vill always          |

The temperature sensor connects to the highest order input of the ADC0 input multiplexer (see Section "5.1. Analog Multiplexer and PGA" on page 43 for C8051F020/1 devices, or Section "6.1. Analog Multiplexer and PGA" on page 59 for C8051F022/3 devices). The TEMPE bit within REF0CN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any A/D measurements performed on the sensor while disabled result in undefined data.

| R/W      | R/W                                          | R/W                                         | R/W           | R/W          | R/W             | R/W         | R/W      | Reset Value |  |  |  |

|----------|----------------------------------------------|---------------------------------------------|---------------|--------------|-----------------|-------------|----------|-------------|--|--|--|

| -        | -                                            | -                                           | AD0VRS        | AD1VRS       | TEMPE           | BIASE       | REFBE    | 00000000    |  |  |  |

| Bit7     | Bit6                                         | Bit5                                        | Bit4          | Bit3         | Bit2            | Bit1        | Bit0     | SFR Address |  |  |  |

|          |                                              |                                             |               |              |                 |             |          | 0xD1        |  |  |  |

| Bits7-5: | UNUSED. R                                    | ead = 000b;                                 | Write = don'  | t care.      |                 |             |          |             |  |  |  |

| Bit4:    | AD0VRS: Al                                   | OC0 Voltage                                 | e Reference S | elect        |                 |             |          |             |  |  |  |

|          | 0: ADC0 voltage reference from VREF0 pin.    |                                             |               |              |                 |             |          |             |  |  |  |

|          | 1: ADC0 volt                                 | 1: ADC0 voltage reference from DAC0 output. |               |              |                 |             |          |             |  |  |  |

| Bit3:    | AD1VRS: ADC1 Voltage Reference Select        |                                             |               |              |                 |             |          |             |  |  |  |

|          | 0: ADC1 voltage reference from VREF1 pin.    |                                             |               |              |                 |             |          |             |  |  |  |

|          | 1: ADC1 voltage reference from AV+.          |                                             |               |              |                 |             |          |             |  |  |  |

| Bit2:    | TEMPE: Temperature Sensor Enable Bit.        |                                             |               |              |                 |             |          |             |  |  |  |

|          | 0: Internal Temperature Sensor Off.          |                                             |               |              |                 |             |          |             |  |  |  |

|          | 1: Internal Te                               | 1: Internal Temperature Sensor On.          |               |              |                 |             |          |             |  |  |  |

| Bit1:    | BIASE: ADC                                   | /DAC Bias                                   | Generator En  | able Bit. (M | ust be '1' if u | using ADC o | or DAC). |             |  |  |  |

|          | 0: Internal Bi                               | as Generato                                 | r Off.        |              |                 |             |          |             |  |  |  |

|          | 1: Internal Bias Generator On.               |                                             |               |              |                 |             |          |             |  |  |  |

| Bit0:    | REFBE: Internal Reference Buffer Enable Bit. |                                             |               |              |                 |             |          |             |  |  |  |

|          | 0: Internal Re                               | ference Buf                                 | fer Off.      |              |                 |             |          |             |  |  |  |

|          | 1: Internal Re                               | C                                           |               | 1 1          | c · 1           |             |          |             |  |  |  |

#### Figure 9.2. REF0CN: Reference Control Register

#### Table 9.1. Voltage Reference Electrical Characteristics

VDD = 3.0 V, AV+ = 3.0 V,  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  unless otherwise specified

| PARAMETER                      | CONDITIONS                           | MIN  | ТҮР  | MAX     | UNITS  |  |  |  |  |

|--------------------------------|--------------------------------------|------|------|---------|--------|--|--|--|--|

| INTERNAL REFERENCE (REFBE = 1) |                                      |      |      |         |        |  |  |  |  |

| Output Voltage                 | 25°C ambient                         | 2.36 | 2.43 | 2.48    | V      |  |  |  |  |

| VREF Short-Circuit Current     |                                      |      |      | 30      | mA     |  |  |  |  |

| VREF Temperature Coefficient   |                                      |      | 15   |         | ppm/°C |  |  |  |  |

| Load Regulation                | Load = 0 to 200 $\mu$ A to AGND      |      | 0.5  |         | ppm/µA |  |  |  |  |

| VREF Turn-on Time 1            | 4.7µF tantalum, 0.1µF ceramic bypass |      | 2    |         | ms     |  |  |  |  |

| VREF Turn-on Time 2            | 0.1µF ceramic bypass                 |      | 20   |         | μs     |  |  |  |  |

| VREF Turn-on Time 3            | no bypass cap                        |      | 10   |         | μs     |  |  |  |  |

| EXTERNAL REFERENCE (RI         | $\mathbf{FBE} = 0$                   | •    | •    |         |        |  |  |  |  |

| Input Voltage Range            |                                      | 1.00 |      | (AV+) - | V      |  |  |  |  |

|                                |                                      |      |      | 0.3     |        |  |  |  |  |

| Input Current                  |                                      |      | 0    | 1       | μA     |  |  |  |  |

#### **12.2.7. Register Descriptions**

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic l. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

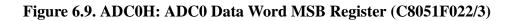

#### Figure 12.3. SP: Stack Pointer

### Figure 12.4. DPL: Data Pointer Low Byte

| R/W      | R/W                                        | R/W            | R/W  | R/W          | R/W          | R/W           | R/W           | Reset Value<br>00000000 |

|----------|--------------------------------------------|----------------|------|--------------|--------------|---------------|---------------|-------------------------|

| Bit7     | Bit6                                       | Bit5           | Bit4 | Bit3         | Bit2         | Bit1          | Bit0          | SFR Address:<br>0x82    |

| Bits7-0: | DPL: Data Po<br>The DPL regi<br>XRAM and F | ster is the lo | •    | e 16-bit DPT | R. DPTR is u | used to acces | ss indirectly | v addressed             |

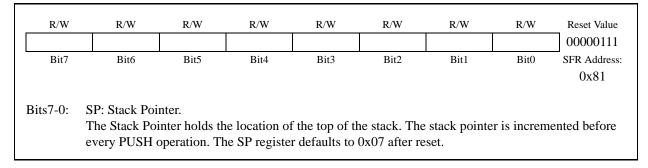

#### Figure 12.5. DPH: Data Pointer High Byte

### 14.1. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be as shown in Figure 14.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in Figure 14.3 (OSCXCN register). For example, an 11.0592 MHz crystal requires an XFCN setting of 111b.

The Crystal Oscillator Valid Flag (XTLVLD in register OSCXCN) is set to logic 1 by hardware when the external crystal oscillator is running and stable. The XTLVLD detection circuit requires a startup time of at least 1 ms between enabling the oscillator and checking the XTLVLD bit. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

Step 1. Enable the external oscillator.

Step 2. Wait at least 1 ms.

Step 3. Poll for XTLVLD => '1'.

Step 4. Switch the system clock to the external oscillator.

**Important Note:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device, as should the loading capacitors on the crystal pins. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

#### 14.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be as shown in Figure 14.1, Option 2. The capacitor must be no greater than 100 pF; however for small capacitors (less than ~20 pF), the total capacitance may be dominated by PWB parasitic capacitance. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let  $R = 246 \text{ k}\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 * 50] = 0.1 MHz = 100 kHz$

$XFCN \ge \log_2 (f / 25 \text{ kHz})$   $XFCN \ge \log_2 (100 \text{ kHz} / 25 \text{ kHz}) = \log_2 (4)$  $XFCN \ge 2, \text{ or code } 010b$

#### 14.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be as shown in Figure 14.1, Option 3. The capacitor must be no greater than 100 pF; however for small capacitors (less than ~20 pF), the total capacitance may be dominated by PWB parasitic capacitance. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume VDD = 3.0 V and C = 50 pF:

f = KF / (C \* VDD) = KF / (50 \* 3)f = KF / 150

If a frequency of roughly 90 kHz is desired, select the K Factor from the table in Figure 14.3 as KF = 13:

f = 13 / 150 = 0.087 MHz, or 87 kHz

Therefore, the XFCN value to use in this example is 011b.

| R/W                                     | R/W                                                                 | R/W            | R/W         | R/W           | R/W           | R/W      | R/W  | Reset Value  |  |  |

|-----------------------------------------|---------------------------------------------------------------------|----------------|-------------|---------------|---------------|----------|------|--------------|--|--|

| FOSE                                    | FRAE                                                                | Reserved       | Reserved    | Reserved      | Reserved      | Reserved | FLWE | 1000000      |  |  |

| Bit7                                    | Bit6                                                                | Bit5           | Bit4        | Bit3          | Bit2          | Bit1     | Bit0 | SFR Address: |  |  |

|                                         |                                                                     |                |             |               |               |          |      | 0xB6         |  |  |

| Bit7: FOSE: FLASH One-Shot Timer Enable |                                                                     |                |             |               |               |          |      |              |  |  |

|                                         | This is the timer that turns off the sense amps after a FLASH read. |                |             |               |               |          |      |              |  |  |

|                                         | 0: FLASH One-Shot Timer disabled.                                   |                |             |               |               |          |      |              |  |  |

|                                         | 1: FLASH Or                                                         | e-Shot Time    | r enabled.  |               |               |          |      |              |  |  |

| Bit6:                                   | FRAE: FLAS                                                          | H Read Alw     | ays Enable  |               |               |          |      |              |  |  |

|                                         | 0: FLASH rea                                                        | ds per One-    | Shot Timer. |               |               |          |      |              |  |  |

|                                         | 1: FLASH alv                                                        | vays in read   | mode.       |               |               |          |      |              |  |  |

| Bits5-1:                                | RESERVED.                                                           | Read $= 0000$  | 00b. Must W | rite 00000b.  |               |          |      |              |  |  |

| Bit0:                                   | FLWE: FLAS                                                          | H Read/Wri     | te Enable   |               |               |          |      |              |  |  |

|                                         | This bit must                                                       | be set to allo | w FLASH w   | vrites from u | ser software. |          |      |              |  |  |

|                                         | 0: FLASH wr                                                         | ites disabled  |             |               |               |          |      |              |  |  |

|                                         | 1: FLASH wr                                                         | itan anahlad   |             |               |               |          |      |              |  |  |

## Figure 15.3. FLSCL: FLASH Memory Control

## 16. EXTERNAL DATA MEMORY INTERFACE AND ON-CHIP XRAM

The C8051F020/1/2/3 MCUs include 4k bytes of on-chip RAM mapped into the external data memory space (XRAM), as well as an External Data Memory Interface which can be used to access off-chip memories and memorymapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN, shown in Figure 16.1). Note: the MOVX instruction can also be used for writing to the FLASH memory. See Section "15. FLASH MEMORY" on page 139 for details. The MOVX instruction accesses XRAM by default. The EMIF can be configured to appear on the lower I/O ports (P0-P3) or the upper I/O ports (P4-P7).

#### 16.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read or written. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 16.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

| MOV  | DPTR, #1234h | ; load DPTR with 16-bit address to read (0x1234) |

|------|--------------|--------------------------------------------------|

| MOVX | A, @DPTR     | ; load contents of 0x1234 into accumulator A     |

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 16.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |

|------|--------------|----------------------------------------------|

| MOV  | R0, #34h     | ; load low byte of address into R0 (or R1)   |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |

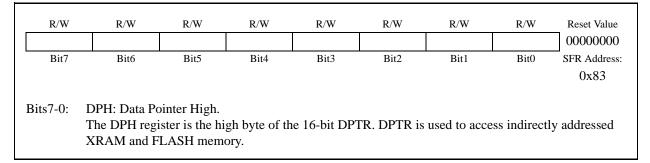

#### **16.5.** Memory Mode Selection

The external data memory space can be configured in one of four modes, shown in Figure 16.5, based on the EMIF Mode bits in the EMIOCF register (Figure 16.2). These modes are summarized below. More information about the different modes can be found in Section "." on page 152.

#### 16.5.1. Internal XRAM Only

When EMIOCF.[3:2] are set to '00', all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 4k boundaries. As an example, the addresses 0x1000 and 0x2000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMI0CN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

#### 16.5.2. Split Mode without Bank Select

When EMIOCF.[3:2] are set to '01', the XRAM memory map is split into two areas, on-chip space and off-chip space.

- Effective addresses below the 4k boundary will access on-chip XRAM space.

- Effective addresses beyond the 4k boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is on-chip or offchip. The lower 8-bits of the Address Bus A[7:0] are driven as defined by R0 or R1. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate the upper address bits at will by setting the Port state directly. This behavior is in contrast with "Split Mode with Bank Select" described below.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or offchip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the offchip transaction.

## Figure 16.5. EMIF Operating Modes

| PARAMETER           | DESCRIPTION                    | MIN                   | MAX                    | UNITS |

|---------------------|--------------------------------|-----------------------|------------------------|-------|

| T <sub>SYSCLK</sub> | System Clock Period            | 40                    |                        | ns    |

| T <sub>ACS</sub>    | Address / Control Setup Time   | 0                     | 3*T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>    | Address / Control Pulse Width  | 1*T <sub>SYSCLK</sub> | 16*T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>    | Address / Control Hold Time    | 0                     | 3*T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>   | Address Latch Enable High Time | 1*T <sub>SYSCLK</sub> | 4*T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>   | Address Latch Enable Low Time  | 1*T <sub>SYSCLK</sub> | 4*T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>    | Write Data Setup Time          | 1*T <sub>SYSCLK</sub> | 19*T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>    | Write Data Hold Time           | 0                     | 3*T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>    | Read Data Setup Time           | 20                    |                        | ns    |

| T <sub>RDH</sub>    | Read Data Hold Time            | 0                     |                        | ns    |

Table 16.1. AC Parameters for External Memory Interface

#### 18.2. SMBus Protocol

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. Note: multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the master in a system; any device who transmits a START and a slave address becomes the master for that transfer.

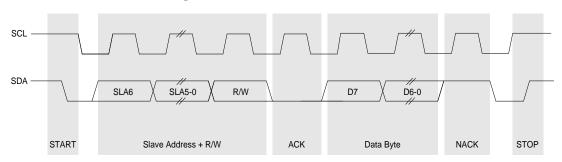

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7-1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 18.3). If the receiving device does not ACK, the transmitting device will read a "not acknowledge" (NACK), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 18.3 illustrates a typical SMBus transaction.

Figure 18.3. SMBus Transaction

#### 18.2.1. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see **Section 18.2.4**). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is opendrain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and give up the bus. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### **18.2.2.** Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to  $I^2C$ , which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

Multiple masters may reside on the same bus. A Mode Fault flag (MODF, SPI0CN.5) is set to logic 1 when SPI0 is configured as a master (MSTEN = 1) and its slave select signal NSS is pulled low. When the Mode Fault flag is set, the MSTEN and SPIEN bits of the SPI control register are cleared by hardware, thereby placing the SPI0 module in an "off-line" state. In a multiple-master environment, the system controller should check the state of the SLVSEL flag (SPI0CN.2) to ensure the bus is free before setting the MSTEN bit and initiating a data transfer.

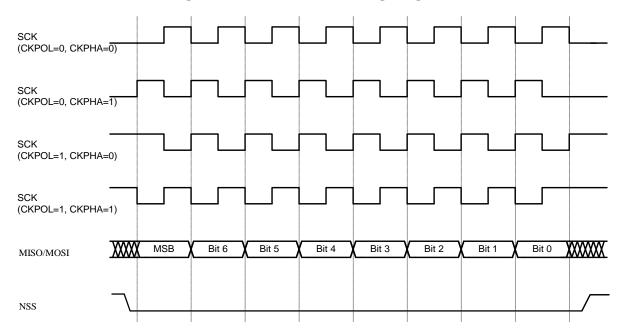

### 19.3. Serial Clock Timing

As shown in Figure 19.4, four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.7) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.6) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. Note: SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) while changing the clock phase and polarity.

The SPI0 Clock Rate Register (SPI0CKR) as shown in Figure 19.7 controls the master mode serial clock frequency. This register is ignored when operating in slave mode.

Figure 19.4. Data/Clock Timing Diagram

| R/W   | R/W                                                                                                       | R/W         | R/W       | R             | R            | R/W            | R/W             | Reset Value    |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------|-------------|-----------|---------------|--------------|----------------|-----------------|----------------|--|--|--|--|

| SPIF  | WCOL                                                                                                      | MODF        | RXOVRN    | TXBSY         | SLVSEL       | MSTEN          | SPIEN           | 00000000       |  |  |  |  |

| Bit7  | Bit6                                                                                                      | Bit5        | Bit4      | Bit3          | Bit2         | Bit1           | Bit0            | SFR Address:   |  |  |  |  |

|       |                                                                                                           |             |           |               |              | (              | bit addressable | ) 0xF8         |  |  |  |  |

|       |                                                                                                           |             |           |               |              |                |                 |                |  |  |  |  |

| Bit7: | SPIF: SPI0 In                                                                                             |             |           |               |              |                |                 |                |  |  |  |  |

|       | This bit is set                                                                                           |             |           |               |              |                |                 |                |  |  |  |  |

|       | bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared |             |           |               |              |                |                 |                |  |  |  |  |

|       | by hardware.                                                                                              |             | •         | tware.        |              |                |                 |                |  |  |  |  |

| Bit6: | WCOL: Write                                                                                               |             | U         |               | CDIO 1       |                |                 |                |  |  |  |  |

|       | This bit is set                                                                                           |             |           |               |              |                |                 |                |  |  |  |  |

|       | data register v<br>bit causes the                                                                         |             |           |               |              |                |                 |                |  |  |  |  |

|       | by hardware.                                                                                              |             |           |               |              | 2. THIS DIUS   | lot automati    | cally cleared  |  |  |  |  |

| Bit5: | MODF: Mode                                                                                                |             | •         | iware.        |              |                |                 |                |  |  |  |  |

| Dito. | This bit is set                                                                                           | 0           |           | nd generates  | a SPI0 inter | rupt) when a   | master mod      | e collision is |  |  |  |  |

|       | detected (NSS                                                                                             |             |           |               |              |                |                 |                |  |  |  |  |

|       | vector to the S                                                                                           |             |           |               |              |                |                 |                |  |  |  |  |

|       | be cleared by                                                                                             | -           |           |               |              | •              | •               |                |  |  |  |  |

| Bit4: | RXOVRN: R                                                                                                 | eceive Over | run Flag. |               |              |                |                 |                |  |  |  |  |

|       | This bit is set                                                                                           |             |           |               |              |                |                 |                |  |  |  |  |

|       | holds unread                                                                                              |             |           |               |              |                |                 |                |  |  |  |  |

|       | SPI0 shift reg                                                                                            |             |           |               |              |                |                 |                |  |  |  |  |

| DUO   | rupt service ro                                                                                           |             |           | omatically cl | eared by har | dware. It mu   | st be cleared   | by software.   |  |  |  |  |

| Bit3: | TXBSY: Tran                                                                                               |             |           | 1.:1          |              |                |                 |                |  |  |  |  |

|       | This bit is set<br>ware at the en                                                                         |             |           | nne a master  | mode transi  | er is in progi | ress. It is cle | ared by nard-  |  |  |  |  |

| Bit2: | SLVSEL: Slav                                                                                              |             |           |               |              |                |                 |                |  |  |  |  |

| DILZ. | This bit is set                                                                                           |             |           | JSS nin is lo | v indicating | it is enabled  | as a slave. It  | is cleared to  |  |  |  |  |

|       | logic 0 when                                                                                              |             |           |               | w maleating  | it is chabled  | as a siave. It  | is cleared to  |  |  |  |  |

| Bit1: | MSTEN: Mas                                                                                                |             |           | •••)          |              |                |                 |                |  |  |  |  |

|       | 0: Disable ma                                                                                             |             |           | ve mode.      |              |                |                 |                |  |  |  |  |

|       | 1: Enable mas                                                                                             |             | -         |               |              |                |                 |                |  |  |  |  |

| Bit0: | SPIEN: SPI0                                                                                               | Enable.     |           |               |              |                |                 |                |  |  |  |  |

|       | This bit enabl                                                                                            |             | he SPI.   |               |              |                |                 |                |  |  |  |  |

|       | 0: SPI disable                                                                                            | ed.         |           |               |              |                |                 |                |  |  |  |  |

| L     |                                                                                                           |             |           |               |              |                |                 |                |  |  |  |  |

## Figure 19.6. SPI0CN: SPI0 Control Register

| R/W      | R/W                                                                       | R/W                           | R/W                              | R/W                                | R/W            | R/W             | R/W        | Reset Value 00000000 |

|----------|---------------------------------------------------------------------------|-------------------------------|----------------------------------|------------------------------------|----------------|-----------------|------------|----------------------|

| Bit7     | Bit6                                                                      | Bit5                          | Bit4                             | Bit3                               | Bit2           | Bit1            | Bit0       | SFR Address:<br>0xF2 |

| Bits7-0: | SBUF1.[7:0]:<br>This SFR acco<br>written to SBU<br>byte to SBUF<br>latch. | esses two reg<br>UF1, it goes | gisters; a tran<br>to the transn | ismit shift reg<br>nit shift regis | ter and is hel | ld for serial t | ransmissio | n. Writing a         |

### Figure 21.9. SBUF1: UART1 Data Buffer Register

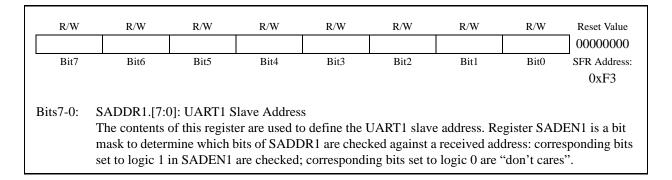

#### Figure 21.10. SADDR1: UART1 Slave Address Register

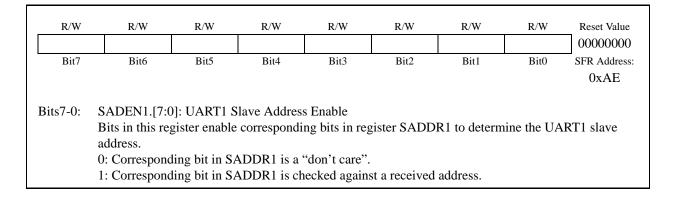

#### Figure 21.11. SADEN1: UART1 Slave Address Enable Register

## 22. TIMERS

The C8051F020/1/2/3 devices contain 5 counter/timers: three are 16-bit counter/timers compatible with those found in the standard 8051, and two are 16-bit auto-reload timers for use with the ADCs, SMBus, UART1, or for general purpose use. These can be used to measure time intervals, count external events and generate periodic interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation. Timer 2 offers additional capabilities not available in Timers 0 and 1. Timer 3 is similar to Timer 2, but without the capture or Baud Rate Generator modes. Timer 4 is identical to Timer 2, and can supply baud-rate generation capabilities to UART1.

| Timer 0 and Timer 1:     | Timer 2:                  | Timer 3:                | Timer 4                   |

|--------------------------|---------------------------|-------------------------|---------------------------|

| 13-bit counter/timer     | 16-bit counter/timer with | 16-bit timer with auto- | 16-bit counter/timer with |

| 13-bit counter/timer     | auto-reload               | reload                  | auto-reload               |

| 16-bit counter/timer     | 16-bit counter/timer with |                         | 16-bit counter/timer with |

| 10-bit counter/timer     | capture                   |                         | capture                   |

| 8-bit counter/timer with | Baud rate generator for   |                         | Baud rate generator for   |

| auto-reload              | UART0                     |                         | UART1                     |

| Two 8-bit counter/timers |                           |                         |                           |

| (Timer 0 only)           |                           |                         |                           |

When functioning as a timer, the counter/timer registers are incremented on each clock tick. Clock ticks are derived from the system clock divided by either one or twelve as specified by the Timer Clock Select bits (T4M-T0M) in CKCON, shown in Figure 22.1. The twelve-clocks-per-tick option provides compatibility with the older generation of the 8051 family. Applications that require a faster timer can use the one-clock-per-tick option.

When functioning as a counter, a counter/timer register is incremented on each high-to-low transition at the selected input pin. Events with a frequency of up to one-fourth the system clock's frequency can be counted. The input signal need not be periodic, but it should be held at a given level for at least two full system clock cycles to ensure the level is sampled.

| R/W      | R/W                       | R/W                                       | R/W           | R/W            | R/W            | R/W          | R/W            | Reset Value   |  |  |  |

|----------|---------------------------|-------------------------------------------|---------------|----------------|----------------|--------------|----------------|---------------|--|--|--|

| TF3      | -                         | -                                         | -             | -              | TR3            | T3M          | T3XCLK         | 00000000      |  |  |  |

| Bit7     | Bit6                      | Bit5                                      | Bit4          | Bit3           | Bit2           | Bit1         | Bit0           | SFR Address:  |  |  |  |

|          |                           |                                           |               |                |                |              |                | 0x91          |  |  |  |

| Bit7:    | TF3: Timer3               | Overflow Fl                               | ag.           |                |                |              |                |               |  |  |  |

|          | Set by hardwa             | are when Tir                              | ner 3 overflo | ows from 0x1   | FFFF to 0x00   | 00. When th  | ne Timer 3 in  | terrupt is    |  |  |  |

|          | enabled, settin           | ng this bit ca                            | uses the CPU  | U to vector to | o the Timer 3  | Interrupt se | ervice routine | . This bit is |  |  |  |

|          | not automatic             | ally cleared                              | by hardware   | and must be    | e cleared by s | oftware.     |                |               |  |  |  |

| Bits6-3: | UNUSED. Re                | UNUSED. Read = 0000b, Write = don't care. |               |                |                |              |                |               |  |  |  |

| Bit2:    | TR3: Timer 3 Run Control. |                                           |               |                |                |              |                |               |  |  |  |

|          | This bit enabl            | This bit enables/disables Timer 3.        |               |                |                |              |                |               |  |  |  |

|          | 0: Timer 3 dis            | sabled.                                   |               |                |                |              |                |               |  |  |  |

|          | 1: Timer 3 en             | abled.                                    |               |                |                |              |                |               |  |  |  |

| Bit1:    | T3M: Timer 3              |                                           |               |                |                |              |                |               |  |  |  |

|          | This bit contr            |                                           |               |                |                | ounter/Timer | r 3.           |               |  |  |  |

|          | 0: Counter/Ti             |                                           | •             |                | oy 12.         |              |                |               |  |  |  |

|          | 1: Counter/Ti             | mer 3 uses tl                             | ne system clo | ock.           |                |              |                |               |  |  |  |

| Bit0:    | T3XCLK: Tii               |                                           |               |                |                |              |                |               |  |  |  |

|          | This bit select           |                                           |               | -              | by 8 as the T  | imer 3 clocl | k source. Wh   | en T3XCLk     |  |  |  |

|          | is logic 1, bit           | •                                         | , 0           |                |                |              |                |               |  |  |  |

|          | 0: Timer 3 clo            | ock source de                             | •             |                |                |              |                |               |  |  |  |

|          | 1: Timer 3 clo            |                                           |               |                |                |              |                |               |  |  |  |

## Figure 22.20. TMR3CN: Timer 3 Control Register

## Figure 22.21. TMR3RLL: Timer 3 Reload Register Low Byte

| R/W       | R/W            | R/W         | R/W           | R/W       | R/W           | R/W           | R/W          | Reset Value          |

|-----------|----------------|-------------|---------------|-----------|---------------|---------------|--------------|----------------------|

|           |                |             |               |           |               |               |              | 00000000             |

| Bit7      | Bit6           | Bit5        | Bit4          | Bit3      | Bit2          | Bit1          | Bit0         | SFR Address:<br>0x92 |

|           |                |             |               |           |               |               |              | 07/2                 |

| Bits 7-0: | TMR3RLL: T     | imer 3 Relo | ad Register I | Low Byte. |               |               |              |                      |

|           | Timer 3 is con |             | -             | •         | register hold | le the low by | to of the re | auley heal           |

|           | 8                           |      |      | Timer 3    |               | 8              |              |             |

|-----------|-----------------------------|------|------|------------|---------------|----------------|--------------|-------------|

| R/W       | R/W                         | R/W  | R/W  | R/W        | R/W           | R/W            | R/W          | Reset Value |

|           |                             |      |      |            |               |                |              | 00000000    |

| Bit7      | Bit6                        | Bit5 | Bit4 | Bit3       | Bit2          | Bit1           | Bit0         | SFR Address |

|           |                             |      |      |            |               |                |              | 0x93        |

| Bits 7-0: | TMR3RLH: 7<br>Timer 3 is co |      | 0    | <b>U</b> . | register hold | ls the high by | vte of the r |             |

--

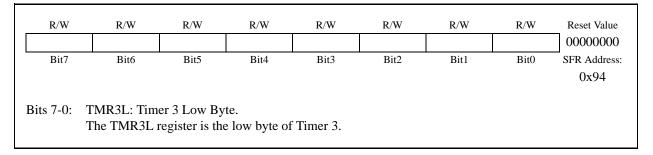

Figure 22.23. TMR3L: Timer 3 Low Byte

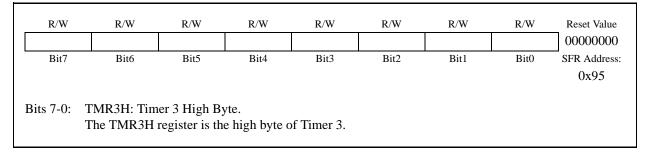

Figure 22.24. TMR3H: Timer 3 High Byte

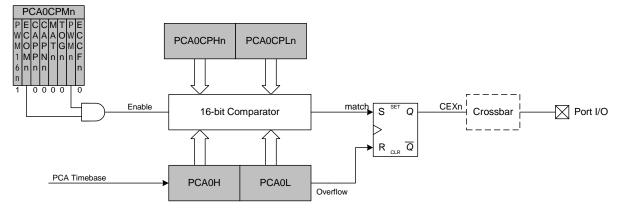

#### 23.2.6. 16-Bit Pulse Width Modulator Mode

Each PCA0 module may also be operated in 16-Bit PWM mode. In this mode, the 16-bit capture/compare module defines the number of PCA0 clocks for the low time of the PWM signal. When the PCA0 counter matches the module contents, the output on CEXn is asserted high; when the counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA0 CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, CCFn should also be set to logic 1 to enable match interrupts. The duty cycle for 16-Bit PWM Mode is given by Equation 23.3.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'

#### Equation 23.3. 16-Bit PWM Duty Cycle

$DutyCycle = \frac{(65536 - PCA0CPn)}{65536}$

Using Equation 23.3, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

#### Figure 23.9. PCA 16-Bit PWM Mode

| R/W       | R/W                        | R/W  | R/W  | R/W  | R/W          | R/W          | R/W    | Reset Value<br>00000000 |

|-----------|----------------------------|------|------|------|--------------|--------------|--------|-------------------------|

| Bit7      | Bit6                       | Bit5 | Bit4 | Bit3 | Bit2         | Bit1         | Bit0   | SFR Address:            |

|           |                            |      |      |      |              |              |        | 0xE9                    |

| Bits 7-0: | PCA0L: PCA<br>The PCA0L re |      | •    |      | e 16-bit PCA | A0 Counter/1 | Timer. |                         |

### Figure 23.13. PCA0L: PCA0 Counter/Timer Low Byte

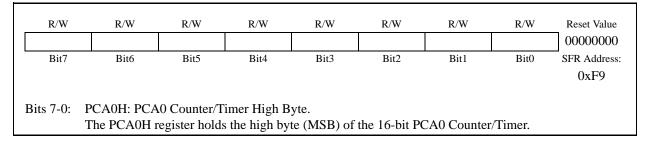

## Figure 23.14. PCA0H: PCA0 Counter/Timer High Byte

#### 24.2. Flash Programming Commands

The Flash memory can be programmed directly over the JTAG interface using the Flash Control, Flash Data, Flash Address, and Flash Scale registers. These Indirect Data Registers are accessed via the JTAG Instruction Register. Read and write operations on indirect data registers are performed by first setting the appropriate DR address in the IR register. Each read or write is then initiated by writing the appropriate Indirect Operation Code (IndOpCode) to the selected data register. Incoming commands to this register have the following format:

| 19:18     | 17:0      |

|-----------|-----------|

| IndOpCode | WriteData |

IndOpCode: These bit set the operation to perform according to the following table:

| IndOpCode | Operation |

|-----------|-----------|

| 0x        | Poll      |

| 10        | Read      |

| 11        | Write     |

The Poll operation is used to check the Busy bit as described below. Although a Capture-DR is performed, no Update-DR is allowed for the Poll operation. Since updates are disabled, polling can be accomplished by shifting in/ out a single bit.

The Read operation initiates a read from the register addressed by the DRAddress. Reads can be initiated by shifting only 2 bits into the indirect register. After the read operation is initiated, polling of the Busy bit must be performed to determine when the operation is complete.

The write operation initiates a write of WriteData to the register addressed by DRAddress. Registers of any width up to 18 bits can be written. If the register to be written contains fewer than 18 bits, the data in WriteData should be left-justified, i.e. its MSB should occupy bit 17 above. This allows shorter registers to be written in fewer JTAG clock cycles. For example, an 8-bit register could be written by shifting only 10 bits. After a Write is initiated, the Busy bit should be polled to determine when the next operation can be initiated. The contents of the Instruction Register should not be altered while either a read or write operation is busy.

Outgoing data from the indirect Data Register has the following format:

| 19 | 18:1     | 0    |  |

|----|----------|------|--|

| 0  | ReadData | Busy |  |

The Busy bit indicates that the current operation is not complete. It goes high when an operation is initiated and returns low when complete. Read and Write commands are ignored while Busy is high. In fact, if polling for Busy to be low will be followed by another read or write operation, JTAG writes of the next operation can be made while checking for Busy to be low. They will be ignored until Busy is read low, at which time the new operation will initiate. This bit is placed ate bit 0 to allow polling by single-bit shifts. When waiting for a Read to complete and Busy is 0, the following 18 bits can be shifted out to obtain the resulting data. ReadData is always right-justified. This allows registers shorter than 18 bits to be read using a reduced number of shifts. For example, the results from a byte-read requires 9 bit shifts (Busy + 8 bits).