# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 64                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 100-TQFP                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f022-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Notes

|     | Figure 9.1. Voltage Reference Functional Block Diagram                                                                       | 91  |

|-----|------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Figure 9.2. REF0CN: Reference Control Register                                                                               |     |

|     | Table 9.1.       Voltage Reference Electrical Characteristics                                                                |     |

| 10. | VOLTAGE REFERENCE (C8051F021/3)                                                                                              |     |

|     | Figure 10.1. Voltage Reference Functional Block Diagram                                                                      |     |

|     | Figure 10.2. REFOCN: Reference Control Register                                                                              |     |

|     | Table 10.1. Voltage Reference Electrical Characteristics                                                                     |     |

| 11. | COMPARATORS                                                                                                                  |     |

|     | Figure 11.1. Comparator Functional Block Diagram                                                                             | 95  |

|     | Figure 11.2. Comparator Hysteresis Plot                                                                                      |     |

|     | Figure 11.3. CPT0CN: Comparator0 Control Register                                                                            |     |

|     | Figure 11.4. CPT1CN: Comparator1 Control Register                                                                            | 98  |

|     | Table 11.1. Comparator Electrical Characteristics                                                                            | 99  |

| 12. | CIP-51 MICROCONTROLLER                                                                                                       | 101 |

|     | Figure 12.1. CIP-51 Block Diagram                                                                                            | 101 |

|     | Table 12.1. CIP-51 Instruction Set Summary                                                                                   | 103 |

|     | Figure 12.2. Memory Map                                                                                                      |     |

|     | Table 12.2. Special Function Register (SFR) Memory Map                                                                       | 109 |

|     | Table 12.3. Special Function Registers                                                                                       | 109 |

|     | Figure 12.3. SP: Stack Pointer                                                                                               |     |

|     | Figure 12.4. DPL: Data Pointer Low Byte                                                                                      |     |

|     | Figure 12.5. DPH: Data Pointer High Byte                                                                                     | 113 |

|     | Figure 12.6. PSW: Program Status Word                                                                                        |     |

|     | Figure 12.7. ACC: Accumulator                                                                                                |     |

|     | Figure 12.8. B: B Register                                                                                                   |     |

|     | Table 12.4. Interrupt Summary                                                                                                |     |

|     | Figure 12.9. IE: Interrupt Enable                                                                                            |     |

|     | Figure 12.10. IP: Interrupt Priority                                                                                         |     |

|     | Figure 12.11. EIE1: Extended Interrupt Enable 1                                                                              |     |

|     | Figure 12.12. EIE2: Extended Interrupt Enable 2                                                                              |     |

|     | Figure 12.13. EIP1: Extended Interrupt Priority 1                                                                            |     |

|     | Figure 12.14. EIP2: Extended Interrupt Priority 2                                                                            |     |

|     | Figure 12.15. PCON: Power Control                                                                                            |     |

| 13. | RESET SOURCES                                                                                                                |     |

|     | Figure 13.1. Reset Sources                                                                                                   |     |

|     | Figure 13.2. Reset Timing                                                                                                    |     |

|     | Figure 13.3. WDTCN: Watchdog Timer Control Register                                                                          |     |

|     | Figure 13.4. RSTSRC: Reset Source Register                                                                                   |     |

| 14  | Table 13.1. Reset Electrical Characteristics                                                                                 |     |

| 14. | OSCILLATORS                                                                                                                  |     |

|     | Figure 14.1. Oscillator Diagram                                                                                              |     |

|     | Figure 14.2. OSCICN: Internal Oscillator Control Register                                                                    |     |

|     | Table 14.1. Internal Oscillator Electrical Characteristics         Eigure 14.2. OSCNCN: External Oscillator Control Register |     |

| 15  | Figure 14.3. OSCXCN: External Oscillator Control Register                                                                    |     |

| 15. | FLASH MEMORY                                                                                                                 | 139 |

# **1.1.** CIP-51<sup>TM</sup> Microcontroller Core

### 1.1.1. Fully 8051 Compatible

The C8051F020 family utilizes Silicon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The core has all the peripherals included with a standard 8052, including five 16-bit counter/timers, two full-duplex UARTs, 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space, and 8/4 byte-wide I/O Ports.

### **1.1.2.** Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12-to-24 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

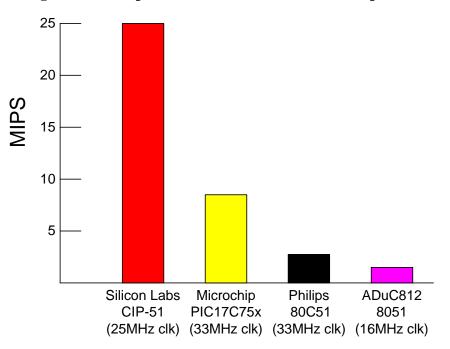

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.5 shows a comparison of peak throughputs of various 8-bit microcontroller cores with their maximum system clocks.

# Figure 1.5. Comparison of Peak MCU Execution Speeds

| R/W     | R/W          | R/W            | R/W                       | R/W            | R/W              | R/W                                     | R/W             | Reset Value  |

|---------|--------------|----------------|---------------------------|----------------|------------------|-----------------------------------------|-----------------|--------------|

| AD0EN   | AD0TM        | AD0INT         | AD0BUSY                   | AD0CM1         | AD0CM0           | AD0WINT                                 | AD0LJS7         | 00000000     |

| Bit7    | Bit6         | Bit5           | Bit4                      | Bit3           | Bit2             | Bit1                                    | Bit0            | SFR Address: |

|         |              |                |                           |                |                  | (                                       | (bit addressabl | e) 0xE8      |

|         |              |                |                           |                |                  |                                         |                 |              |

| Bit7:   | AD0EN: AI    | DC0 Enable     | Bit.                      |                |                  |                                         |                 |              |

|         |              |                | C0 is in low-p            |                |                  |                                         |                 |              |

|         |              |                |                           | d ready for    | data conversi    | ons.                                    |                 |              |

| Bit6:   | AD0TM: Al    |                |                           |                |                  |                                         |                 |              |

|         |              |                |                           |                | ous unless a c   | onversion is in                         | n process       |              |

| Bit5:   | U            |                | ADSTM1-0 t<br>sion Comple |                | Flog             |                                         |                 |              |

| DILJ.   |              |                | d by software             | -              | riag.            |                                         |                 |              |

|         | -            |                | •                         |                | ce the last tin  | ne this flag wa                         | s cleared       |              |

|         |              |                | a data conve              |                | ee the fust this | ie uns nug wu                           | is creared.     |              |

| Bit4:   | AD0BUSY:     | -              |                           |                |                  |                                         |                 |              |

|         | Read:        | •              |                           |                |                  |                                         |                 |              |

|         | 0: ADC0 Co   | onversion is   | complete or a             | conversion     | is not current   | tly in progress                         | . AD0INT i      | s set to     |

|         |              |                | ge of AD0BU               | JSY.           |                  |                                         |                 |              |

|         | 1: ADC0 Co   | onversion is   | in progress.              |                |                  |                                         |                 |              |

|         | Write:       |                |                           |                |                  |                                         |                 |              |

|         | 0: No Effect |                | ersion if AD0             | STM1 = 0       | )0b              |                                         |                 |              |

| Bit3-2: |              |                | t of Conversi             |                |                  |                                         |                 |              |

| DI13-2. | If AD0TM =   |                | t of Conversi             |                | leet.            |                                         |                 |              |

|         |              |                | itiated on eve            | ery write of   | '1' to AD0BU     | JSY.                                    |                 |              |

|         |              |                | itiated on ove            |                |                  |                                         |                 |              |

|         | 10: ADC0 c   | onversion in   | itiated on risi           | ing edge of e  | external CNV     | STR.                                    |                 |              |

|         |              |                | itiated on ove            | erflow of Tir  | mer 2.           |                                         |                 |              |

|         | If AD0TM =   |                |                           |                |                  |                                         |                 |              |

|         | -            | g starts with  | the write of .            | 1' to AD0B     | USY and last     | s for 3 SAR cl                          | ocks, follov    | ved by con-  |

|         | version.     | r storted by t | he overflow               | of Timor 2 o   | nd last for 2 (  | SAR clocks, fo                          | llowed by       | onversion    |

|         |              |                |                           |                |                  | ersion starts of                        |                 |              |

|         |              |                |                           |                |                  | SAR clocks, fo                          |                 |              |

| Bit1:   |              |                | low Compare               |                |                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 |              |

|         |              |                | by software.              | 1              | 8                |                                         |                 |              |

|         | 0: ADC0 W    | indow Comp     | arison Data               | match has no   | ot occurred si   | nce this flag w                         | as last clear   | red.         |

|         |              | -              | parison Data              |                | ccurred.         |                                         |                 |              |

| Bit0:   |              |                | ustify Select.            |                |                  |                                         |                 |              |

|         |              |                | OL registers              |                |                  |                                         |                 |              |

|         | 1: Data in A | DCUH:ADC       | OL registers              | are left-justi | nea.             |                                         |                 |              |

# Figure 5.8. ADC0CN: ADC0 Control Register (C8051F020/1)

# Figure 5.11. ADC0 Data Word Example (C8051F020/1)

| <b>12-bit ADC0 Data Word appears in the ADC0 Data Word Registers as follows:</b><br>ADC0H[3:0]:ADC0L[7:0], if AD0LJST = 0<br>(ADC0H[7:4] will be sign-extension of ADC0H.3 for a differential reading, otherwise = 0000b). |                                                                       |                                                        |            |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|------------|--|--|--|--|--|--|--|

| ADC0H[7:0]:ADC0L[<br>(ADC0L[3:0]                                                                                                                                                                                           |                                                                       |                                                        |            |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                          | Word Conversion Map,<br>0x00, AMX0SL = 0x00                           | AIN0 Input in Single-En                                | ded Mode   |  |  |  |  |  |  |  |

| AIN0-AGND (Volts)                                                                                                                                                                                                          | ADC0H:ADC0L (AD0LJST = 0)                                             | ADC0H:ADC0L $(AD0LJST = 1)$                            |            |  |  |  |  |  |  |  |

| VREF * (4095/4096)                                                                                                                                                                                                         | 0x0FFF                                                                | 0xFFF0                                                 |            |  |  |  |  |  |  |  |

| VREF / 2                                                                                                                                                                                                                   | 0x0800                                                                | 0x8000                                                 |            |  |  |  |  |  |  |  |

| VREF * (2047/4096)                                                                                                                                                                                                         | 0x07FF                                                                | 0x7FF0                                                 |            |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                          | 0x0000                                                                | 0x0000                                                 |            |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                          | Word Conversion Map,<br>0x01, AMX0SL = $0x00ADC0H:ADC0L(AD0LJST = 0)$ | AIN0-AIN1 Differential<br>ADC0H:ADC0L<br>(AD0LJST = 1) | Input Pair |  |  |  |  |  |  |  |

| VREF * (2047/2048)                                                                                                                                                                                                         | 0x07FF                                                                | 0x7FF0                                                 |            |  |  |  |  |  |  |  |

| VREF / 2                                                                                                                                                                                                                   | 0x0400                                                                | 0x4000                                                 |            |  |  |  |  |  |  |  |

| VREF * (1/2048)                                                                                                                                                                                                            | 0x0001                                                                | 0x0010                                                 | ]          |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                                          | 0x0000                                                                | 0x0000                                                 | 1          |  |  |  |  |  |  |  |

| -VREF * (1/2048)                                                                                                                                                                                                           | 0xFFFF (-1d)                                                          | 0xFFF0                                                 | ]          |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                            | 0 = EC00 (10244)                                                      | 0xC000                                                 | 1          |  |  |  |  |  |  |  |

| -VREF / 2                                                                                                                                                                                                                  | 0xFC00 (-1024d)                                                       | 0xC000                                                 |            |  |  |  |  |  |  |  |

For AD0LJST = 0:

$Code = Vin \times \frac{Gain}{VREF} \times 2^n$ ; 'n' = 12 for Single-Ended; 'n'=11 for Differential.

| R/W               | R/W                                                           | R/W                                                  | R/W             | R/W             | R/W          | R/W          | R/W           | Reset Value  |  |  |  |  |

|-------------------|---------------------------------------------------------------|------------------------------------------------------|-----------------|-----------------|--------------|--------------|---------------|--------------|--|--|--|--|

| -                 | -                                                             | -                                                    | -               | AIN67IC         | AIN45IC      | AIN23IC      | AIN01IC       | 00000000     |  |  |  |  |

| Bit7              | Bit6                                                          | Bit5                                                 | Bit4            | Bit3            | Bit2         | Bit1         | Bit0          | SFR Address: |  |  |  |  |

|                   |                                                               |                                                      |                 |                 |              |              |               | 0xBA         |  |  |  |  |

| Bits7-4:<br>Bit3: | UNUSED. Re<br>AIN67IC: AI                                     | ,                                                    |                 |                 | it           |              |               |              |  |  |  |  |

|                   |                                                               | 0: AIN6 and AIN7 are independent single-ended inputs |                 |                 |              |              |               |              |  |  |  |  |

|                   | 1: AIN6, AIN7 are (respectively) +, - differential input pair |                                                      |                 |                 |              |              |               |              |  |  |  |  |

| Bit2:             | AIN45IC: AIN4, AIN5 Input Pair Configuration Bit              |                                                      |                 |                 |              |              |               |              |  |  |  |  |

|                   | 0: AIN4 and AIN5 are independent single-ended inputs          |                                                      |                 |                 |              |              |               |              |  |  |  |  |

|                   | 1: AIN4, AIN                                                  | · 1                                                  | •               |                 |              |              |               |              |  |  |  |  |

| Bit1:             | AIN23IC: AI                                                   |                                                      |                 | U               |              |              |               |              |  |  |  |  |

|                   | 0: AIN2 and A                                                 |                                                      | -               | 0               | •            |              |               |              |  |  |  |  |

|                   | 1: AIN2, AIN                                                  | · 1                                                  | •               |                 |              |              |               |              |  |  |  |  |

| Bit0:             | AIN01IC: AI                                                   |                                                      |                 | U               |              |              |               |              |  |  |  |  |

|                   | 0: AIN0 and AIN1 are independent single-ended inputs          |                                                      |                 |                 |              |              |               |              |  |  |  |  |

|                   | 1: AIN0, AIN                                                  | 1 are (respec                                        | ctively) +, - a | differential ir | iput pair    |              |               |              |  |  |  |  |

| NOTE:             | The ADC0 D                                                    | ata Word is i                                        | n 2's comple    | ement format    | for channels | s configured | as differenti | al.          |  |  |  |  |

# Figure 6.5. AMX0CF: AMUX0 Configuration Register (C8051F022/3)

| R/W    | R/W                                                                                                             | R/W                                            | R/W                                        | R/W                                          | R/W                              | R/W     | R/W     | Reset Value  |

|--------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|----------------------------------------------|----------------------------------|---------|---------|--------------|

| AD0SC4 | AD0SC3                                                                                                          | AD0SC2                                         | AD0SC1                                     | AD0SC0                                       | AMP0GN2                          | AMP0GN1 | AMP0GN0 | 11111000     |

| Bit7   | Bit6                                                                                                            | Bit5                                           | Bit4                                       | Bit3                                         | Bit2                             | Bit1    | Bit0    | SFR Address: |

|        |                                                                                                                 |                                                |                                            |                                              |                                  |         |         | 0xBC         |

|        | AD0SC4-0: A<br>SAR Convers<br>to the 5-bit va<br>Table 6.1 on p<br>AD0SC =                                      | ion clock is<br>lue held in A<br>page 74 for S | derived from<br>AD0SC4-0, a<br>AR clock se | system cloc<br>and <i>CLK<sub>SAR0</sub></i> | k by the follor<br>refers to the |         |         |              |

|        | AMP0GN2-0<br>000: Gain = 1<br>001: Gain = 2<br>010: Gain = 4<br>011: Gain = 8<br>10x: Gain = 1<br>11x: Gain = 0 | 6                                              | rnal Amplifi                               | er Gain (PG₄                                 | A)                               |         |         |              |

# Figure 6.7. ADC0CF: ADC0 Configuration Register (C8051F022/3)

| Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         | R/W   | R/W          | R/W       | R/W           | R/W          | R/W            | R/W           | Reset Value  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|--------------|-----------|---------------|--------------|----------------|---------------|--------------|--|--|

| <ul> <li>Bit7: CP0EN: Comparator0 Enable Bit.</li> <li>0: Comparator0 Disabled.</li> <li>1: Comparator0 Enabled.</li> <li>Bit6: CP0OUT: Comparator0 Output State Flag.</li> <li>0: Voltage on CP0+ &lt; CP0</li> <li>1: Voltage on CP0+ &gt; CP0</li> <li>Bit5: CP0RIF: Comparator0 Rising-Edge Interrupt Flag.</li> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag.</li> <li>0: No Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bit3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis = 10 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UT      | CP0EN | CPORIF       | CP0FIF    | CP0HYP1       | CP0HYP0      | CP0HYN1        | CP0HYN0       | 00000000     |  |  |

| <ul> <li>Bit7: CP0EN: Comparator0 Enable Bit.<br/>0: Comparator0 Disabled.<br/>1: Comparator0 Enabled.</li> <li>Bit6: CP0OUT: Comparator0 Output State Flag.<br/>0: Voltage on CP0+ &lt; CP0<br/>1: Voltage on CP0+ &gt; CP0</li> <li>Bit5: CP0RIF: Comparator0 Rising-Edge Interrupt Flag.<br/>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.<br/>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag.<br/>0: No Comparator0 Falling-Edge Interrupt Has occurred since this flag was last cleared.<br/>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Palling-Edge Interrupt has occurred.</li> <li>Bit5-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.<br/>00: Positive Hysteresis = 2 mV.<br/>10: Positive Hysteresis = 4 mV.<br/>11: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br/>00: Negative Hysteresis Disabled.<br/>01: Negative Hysteresis</li></ul> |         | Bit7  | Bit5         | Bit4      | Bit3          | Bit2         | Bit1           | Bit0          | SFR Address: |  |  |

| 0: Comparator0 Disabled.1: Comparator0 Enabled.Bit6:CP0OUT: Comparator0 Output State Flag.<br>0: Voltage on CP0+ < CP0<br>1: Voltage on CP0+ > CP0Bit5:CP0RIF: Comparator0 Rising-Edge Interrupt Flag.<br>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.<br>1: Comparator0 Rising Edge Interrupt has occurred.Bit4:CP0FIF: Comparator0 Falling-Edge Interrupt Flag.<br>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.<br>1: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.<br>1: Comparator0 Falling-Edge Interrupt has occurred.Bits3-2:CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.<br>00: Positive Hysteresis = 2 mV.<br>10: Positive Hysteresis = 10 mV.Bits1-0:CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br>00: Negative Hysteresis Disabled.<br>01: Negative Hysteresis Disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |       |              |           |               |              |                |               | 0x9E         |  |  |

| <ul> <li>1: Comparator0 Enabled.</li> <li>Bit6: CP0OUT: Comparator0 Output State Flag.</li> <li>0: Voltage on CP0+ &lt; CP0</li> <li>1: Voltage on CP0+ &gt; CP0</li> <li>Bit5: CP0RIF: Comparator0 Rising-Edge Interrupt Flag.</li> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Positive Hysteresis = 10 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |       |              |           |               |              |                |               |              |  |  |

| <ul> <li>Bit6: CPOOUT: Comparator0 Output State Flag.</li> <li>0: Voltage on CP0+ &lt; CP0</li> <li>1: Voltage on CP0+ &gt; CP0</li> <li>Bit5: CP0RIF: Comparator0 Rising-Edge Interrupt Flag.</li> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bit3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |       |              |           |               |              |                |               |              |  |  |

| <ul> <li>0: Voltage on CP0+ &lt; CP0</li> <li>1: Voltage on CP0+ &gt; CP0</li> <li>Bit5: CP0RIF: Comparator0 Rising-Edge Interrupt Flag.</li> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |       |              |           |               |              |                |               |              |  |  |

| <ul> <li>1: Voltage on CP0+ &gt; CP0</li> <li>Bit5: CP0RIF: Comparator0 Rising-Edge Interrupt Flag.</li> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag.</li> <li>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>11: Negative Hysteresis Disabled.</li> <li>12: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>13: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>14: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>15: Negative Hysteresis Disabled.</li> <li>16: Negative Hysteresis Disabled.</li> <li>17: Negative Hysteresis Disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -       |       | -            | -         | Flag.         |              |                |               |              |  |  |

| <ul> <li>Bit5: CPORIF: Comparator0 Rising-Edge Interrupt Flag.</li> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag.</li> <li>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |       |              |           |               |              |                |               |              |  |  |

| <ul> <li>0: No Comparator0 Rising Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag.</li> <li>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 4 mV.</li> <li>11: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |       |              |           |               |              |                |               |              |  |  |

| <ul> <li>1: Comparator0 Rising Edge Interrupt has occurred.</li> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag. <ul> <li>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> </ul> </li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits. <ul> <li>00: Positive Hysteresis Disabled.</li> <li>01: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> </ul> </li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits. <ul> <li>00: Negative Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis = 2 mV.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |       |              |           |               |              |                |               |              |  |  |

| <ul> <li>Bit4: CP0FIF: Comparator0 Falling-Edge Interrupt Flag.</li> <li>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis Disabled.</li> <li>01: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis Disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |       |              |           |               |              | is flag was la | ast cleared.  |              |  |  |

| <ul> <li>0: No Comparator0 Falling-Edge Interrupt has occurred since this flag was last cleared.</li> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.</li> <li>00: Positive Hysteresis Disabled.</li> <li>01: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |       | -            |           |               |              |                |               |              |  |  |

| <ul> <li>1: Comparator0 Falling-Edge Interrupt has occurred.</li> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.<br/>00: Positive Hysteresis Disabled.<br/>01: Positive Hysteresis = 2 mV.<br/>10: Positive Hysteresis = 4 mV.<br/>11: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br/>00: Negative Hysteresis Disabled.<br/>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -       |       | -            |           |               |              |                |               |              |  |  |

| <ul> <li>Bits3-2: CP0HYP1-0: Comparator0 Positive Hysteresis Control Bits.<br/>00: Positive Hysteresis Disabled.<br/>01: Positive Hysteresis = 2 mV.<br/>10: Positive Hysteresis = 4 mV.<br/>11: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br/>00: Negative Hysteresis Disabled.<br/>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -       |       |              |           | -             |              | nis flag was l | last cleared. |              |  |  |

| <ul> <li>00: Positive Hysteresis Disabled.</li> <li>01: Positive Hysteresis = 2 mV.</li> <li>10: Positive Hysteresis = 4 mV.</li> <li>11: Positive Hysteresis = 10 mV.</li> <li>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.</li> <li>00: Negative Hysteresis Disabled.</li> <li>01: Negative Hysteresis = 2 mV.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |       | -            |           |               |              |                |               |              |  |  |

| 01: Positive Hysteresis = 2 mV.<br>10: Positive Hysteresis = 4 mV.<br>11: Positive Hysteresis = 10 mV.<br>Bits1-0: CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br>00: Negative Hysteresis Disabled.<br>01: Negative Hysteresis = 2 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |       | -            |           | ysteresis Coi | trol Bits.   |                |               |              |  |  |

| 10: Positive Hysteresis = 4 mV.11: Positive Hysteresis = 10 mV.Bits1-0:CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br>00: Negative Hysteresis Disabled.<br>01: Negative Hysteresis = 2 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |       |              |           |               |              |                |               |              |  |  |

| 11: Positive Hysteresis = 10 mV.Bits1-0:CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br>00: Negative Hysteresis Disabled.<br>01: Negative Hysteresis = 2 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •       |       | •            |           |               |              |                |               |              |  |  |

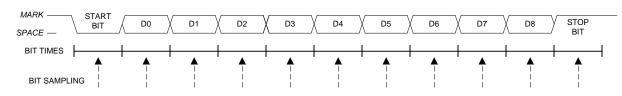

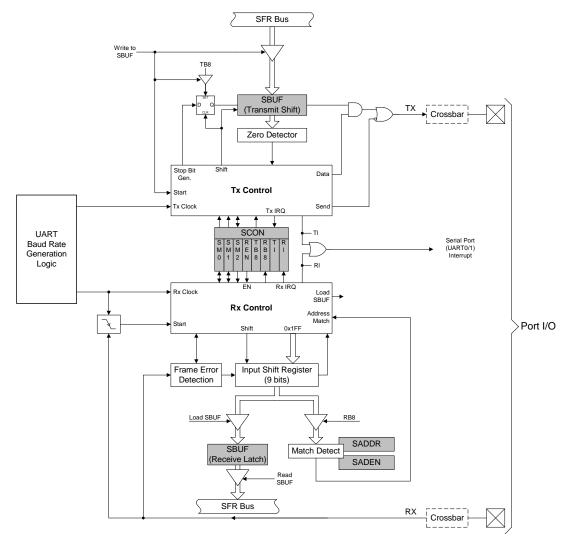

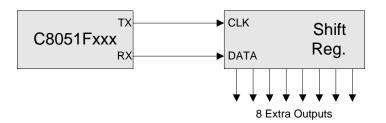

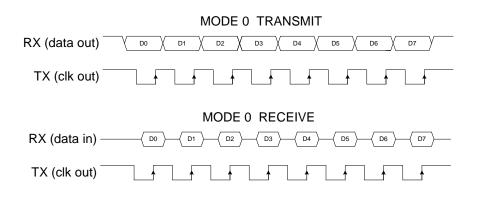

| Bits1-0:CP0HYN1-0: Comparator0 Negative Hysteresis Control Bits.<br>00: Negative Hysteresis Disabled.<br>01: Negative Hysteresis = 2 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •       |       | •            |           |               |              |                |               |              |  |  |