Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 4.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f023-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 23.4. PCA Capture Mode Diagram                       |  |

|-------------------------------------------------------------|--|

| Figure 23.5. PCA Software Timer Mode Diagram                |  |

| Figure 23.6. PCA High Speed Output Mode Diagram             |  |

| Figure 23.7. PCA Frequency Output Mode                      |  |

| Figure 23.8. PCA 8-Bit PWM Mode Diagram                     |  |

| Figure 23.9. PCA 16-Bit PWM Mode                            |  |

| Figure 23.10. PCA0CN: PCA Control Register                  |  |

| Figure 23.11. PCA0MD: PCA0 Mode Register                    |  |

| Figure 23.12. PCA0CPMn: PCA0 Capture/Compare Mode Registers |  |

| Figure 23.13. PCA0L: PCA0 Counter/Timer Low Byte            |  |

| Figure 23.14. PCA0H: PCA0 Counter/Timer High Byte           |  |

| Figure 23.15. PCA0CPLn: PCA0 Capture Module Low Byte        |  |

| Figure 23.16. PCA0CPHn: PCA0 Capture Module High Byte       |  |

| 24. JTAG (IEEE 1149.1)                                      |  |

| Figure 24.1. IR: JTAG Instruction Register                  |  |

| Table 24.1.    Boundary Data Register Bit Definitions       |  |

| Figure 24.2. DEVICEID: JTAG Device ID Register              |  |

| Figure 24.3. FLASHCON: JTAG Flash Control Register          |  |

| Figure 24.4. FLASHADR: JTAG Flash Address Register          |  |

| Figure 24.5. FLASHDAT: JTAG Flash Data Register             |  |

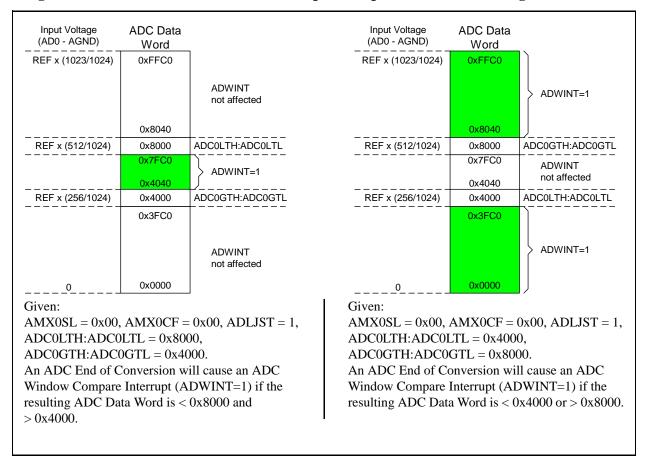

| Input Voltage<br>(AD0 - AGND) | ADC Data<br>Word                                        |                         | Input Voltage<br>(AD0 - AGND)                                                                                                                                                                                                                                                 | ADC Data<br>Word |                 |  |

|-------------------------------|---------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--|

| REF x (4095/4096)             | 0x0FFF                                                  | AD0WINT<br>not affected | REF x (4095/4096)                                                                                                                                                                                                                                                             | 0x0FFF           | AD0WINT=1       |  |

|                               | 0x0201                                                  |                         |                                                                                                                                                                                                                                                                               | 0x0201           | <u> </u>        |  |

| REF x (512/4096)              | 0x0200                                                  | ADC0LTH:ADC0LTL         | REF x (512/4096)                                                                                                                                                                                                                                                              | 0x0200           | ADC0GTH:ADC0GTL |  |

|                               | 0x01FF                                                  | AD0WINT=1               |                                                                                                                                                                                                                                                                               | 0x01FF           | ADOWINT         |  |

|                               | 0x0101                                                  | ADOWINT=1               |                                                                                                                                                                                                                                                                               | 0x0101           | not affected    |  |

| REF x (256/4096)              | 0x0100                                                  | ADC0GTH:ADC0GTL         | REF x (256/4096)                                                                                                                                                                                                                                                              | 0x0100           | ADC0LTH:ADC0LTL |  |

| 0                             | 0x0000                                                  | AD0WINT<br>not affected | 0                                                                                                                                                                                                                                                                             | 0x0000           | AD0WINT=1       |  |

| Window Compare                | DLTL = 0x02<br>DGTL = 0x0<br>Conversion<br>Interrupt (A | 00,                     | Given:<br>AMX0SL = 0x00, AMX0CF = 0x00,<br>AD0LJST = '0',<br>ADC0LTH:ADC0LTL = 0x0100,<br>ADC0GTH:ADC0GTL = 0x0200.<br>An ADC0 End of Conversion will cause an ADC<br>Window Compare Interrupt (AD0WINT = '1') if<br>the resulting ADC0 Data Word is > 0x0200 or<br>< 0x0100. |                  |                 |  |

## Figure 5.16. 12-Bit ADC0 Window Interrupt Example: Right Justified Single-Ended Data

| Input Voltage<br>(AD0 - AD1) | ADC Data<br>Word                                                          |                                                                                 | Input Voltage<br>(AD0 - AD1)                                                                                                                                                                                                                                                                       | ADC Data<br>Word |                 |  |

|------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--|

| REF x (2047/2048)            | 0x7FF0                                                                    | AD0WINT<br>not affected                                                         | REF x (2047/2048)                                                                                                                                                                                                                                                                                  | 0x7FF0<br>0x1010 | ADOWINT=1       |  |

| REF x (256/2048)             | 0x1010                                                                    | ADC0LTH:ADC0LTL                                                                 | REF x (256/2048)                                                                                                                                                                                                                                                                                   | 0x1010           | ADC0GTH:ADC0GTI |  |

|                              | 0x0FF0                                                                    | <u> </u>                                                                        |                                                                                                                                                                                                                                                                                                    | 0x0FF0           | ADOWINT         |  |

|                              | 0x0000                                                                    | AD0WINT=1                                                                       |                                                                                                                                                                                                                                                                                                    | 0x0000           | not affected    |  |

| REF x (-1/2048)              | 0xFFF0                                                                    | ADC0GTH:ADC0GTL                                                                 | REF x (-1/2048)                                                                                                                                                                                                                                                                                    | 0xFFF0           | ADC0LTH:ADC0LTL |  |

| -REF                         | 0x8000                                                                    | AD0WINT<br>not affected                                                         | -REF                                                                                                                                                                                                                                                                                               | 0x8000           | ADOWINT=1       |  |

| Vindow Compare               | OLTL = 0x100<br>OGTL = 0xFl<br>Conversion<br>Interrupt (A<br>20 Data Word | 00,<br>FF0.<br>will cause an ADC0<br>D0WINT = '1') if<br>1  is  < 0 x 1000  and | Given:<br>AMX0SL = 0x00, AMX0CF = 0x01,<br>AD0LJST = '1',<br>ADC0LTH:ADC0LTL = 0xFFF0,<br>ADC0GTH:ADC0GTL = 0x1000.<br>An ADC0 End of Conversion will cause an AI<br>Window Compare Interrupt (AD0WINT = '1')<br>the resulting ADC0 Data Word is < 0xFFF0 or<br>> 0x1000. (Two's-complement math.) |                  |                 |  |

## Figure 5.19. 12-Bit ADC0 Window Interrupt Example: Left Justified Differential Data

### Figure 6.18. 10-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

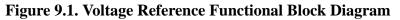

## 9. VOLTAGE REFERENCE (C8051F020/2)

The voltage reference circuit offers full flexibility in operating the ADC and DAC modules. Three voltage reference input pins allow each ADC and the two DACs to reference an external voltage reference or the on-chip voltage reference output. ADC0 may also reference the DAC0 output internally, and ADC1 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.1.

The internal voltage reference circuit consists of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins shown in Figure 9.1. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND, as shown in Figure 9.1. See Table 9.1 for voltage reference specifications.

The Reference Control Register, REF0CN (defined in Figure 9.2) enables/disables the internal reference generator and selects the reference inputs for ADC0 and ADC1. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if either DAC or ADC is used, regardless of whether the voltage reference is derived from the on-chip reference or supplied by an off-chip source. If neither the ADC nor the DAC are being used, both of these bits can be set to logic 0 to conserve power. Bits AD0VRS and AD1VRS select the ADC0 and ADC1 voltage reference sources, respectively. The electrical specifications for the Voltage Reference circuit are given in Table 9.1.

The temperature sensor connects to the highest order input of the ADC0 input multiplexer (see Section "5.1. Analog Multiplexer and PGA" on page 43 for C8051F020/1 devices, or Section "6.1. Analog Multiplexer and PGA" on page 59 for C8051F022/3 devices). The TEMPE bit within REF0CN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any A/D measurements performed on the sensor while disabled result in undefined data.

| R/W      | R/W                 | R/W          | R/W           | R/W          | R/W             | R/W         | R/W      | Reset Value |

|----------|---------------------|--------------|---------------|--------------|-----------------|-------------|----------|-------------|

| -        | -                   | -            | AD0VRS        | AD1VRS       | TEMPE           | BIASE       | REFBE    | 00000000    |

| Bit7     | Bit6                | Bit5         | Bit4          | Bit3         | Bit2            | Bit1        | Bit0     | SFR Address |

|          |                     |              |               |              |                 |             |          | 0xD1        |

| Bits7-5: | UNUSED. R           | ead = 000b;  | Write = don'  | t care.      |                 |             |          |             |

| Bit4:    | AD0VRS: Al          | OC0 Voltage  | e Reference S | elect        |                 |             |          |             |

|          | 0: ADC0 volt        | age referend | ce from VRE   | F0 pin.      |                 |             |          |             |

|          | 1: ADC0 volt        | age referend | ce from DAC   | 0 output.    |                 |             |          |             |

| Bit3:    | AD1VRS: Al          | DC1 Voltage  | e Reference S | elect        |                 |             |          |             |

|          | 0: ADC1 volt        | age referend | ce from VRE   | F1 pin.      |                 |             |          |             |

|          | 1: ADC1 volt        | age referend | ce from AV+.  |              |                 |             |          |             |

| Bit2:    | TEMPE: Tem          | perature Se  | nsor Enable H | Bit.         |                 |             |          |             |

|          | 0: Internal Te      | mperature S  | ensor Off.    |              |                 |             |          |             |

|          | 1: Internal Te      | mperature S  | ensor On.     |              |                 |             |          |             |

| Bit1:    | BIASE: ADC          | /DAC Bias    | Generator En  | able Bit. (M | ust be '1' if u | using ADC o | or DAC). |             |

|          | 0: Internal Bi      | as Generato  | r Off.        |              |                 |             |          |             |

|          | 1: Internal Bi      | as Generato  | r On.         |              |                 |             |          |             |

| Bit0:    | <b>REFBE:</b> Inter | nal Referen  | ce Buffer Ena | able Bit.    |                 |             |          |             |

|          | 0: Internal Re      | ference Buf  | fer Off.      |              |                 |             |          |             |

|          | 1: Internal Re      | C            |               | 1 1          | c · 1           |             |          |             |

## Figure 9.2. REF0CN: Reference Control Register

## Table 9.1. Voltage Reference Electrical Characteristics

VDD = 3.0 V, AV+ = 3.0 V,  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  unless otherwise specified

| PARAMETER                      | CONDITIONS                           | MIN  | ТҮР  | MAX     | UNITS  |  |  |  |  |

|--------------------------------|--------------------------------------|------|------|---------|--------|--|--|--|--|

| INTERNAL REFERENCE (REFBE = 1) |                                      |      |      |         |        |  |  |  |  |

| Output Voltage                 | 25°C ambient                         | 2.36 | 2.43 | 2.48    | V      |  |  |  |  |

| VREF Short-Circuit Current     |                                      |      |      | 30      | mA     |  |  |  |  |

| VREF Temperature Coefficient   |                                      |      | 15   |         | ppm/°C |  |  |  |  |

| Load Regulation                | Load = 0 to 200 $\mu$ A to AGND      |      | 0.5  |         | ppm/µA |  |  |  |  |

| VREF Turn-on Time 1            | 4.7µF tantalum, 0.1µF ceramic bypass |      | 2    |         | ms     |  |  |  |  |

| VREF Turn-on Time 2            | 0.1µF ceramic bypass                 |      | 20   |         | μs     |  |  |  |  |

| VREF Turn-on Time 3            | no bypass cap                        |      | 10   |         | μs     |  |  |  |  |

| EXTERNAL REFERENCE (RI         | $\mathbf{FBE} = 0$                   |      | •    |         |        |  |  |  |  |

| Input Voltage Range            |                                      | 1.00 |      | (AV+) - | V      |  |  |  |  |

|                                |                                      |      |      | 0.3     |        |  |  |  |  |

| Input Current                  |                                      |      | 0    | 1       | μA     |  |  |  |  |

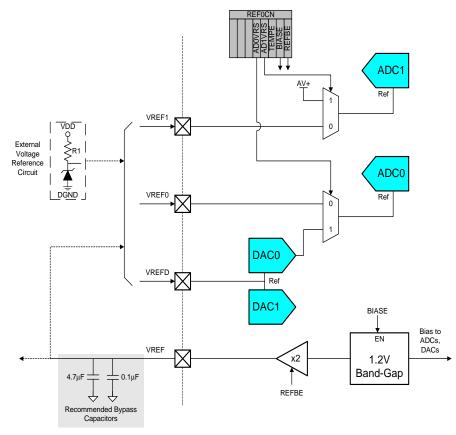

## 10. VOLTAGE REFERENCE (C8051F021/3)

The internal voltage reference circuit consists of a 1.2 V, 15 ppm/°C (typical) bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the VREFA input pin shown in Figure 10.1. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND, as shown in Figure 10.1. See Table 10.1 for voltage reference specifications.

The VREFA pin provides a voltage reference input for ADC0 and ADC1. ADC0 may also reference the DAC0 output internally, and ADC1 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 10.1.

The Reference Control Register, REF0CN (defined in Figure 10.2) enables/disables the internal reference generator and selects the reference inputs for ADC0 and ADC1. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to 1 (this includes any time a DAC is used). If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if either ADC is used, regardless of whether the voltage reference is derived from the on-chip reference or supplied by an off-chip source. If neither the ADC nor the DAC are being used, both of these bits can be set to logic 0 to conserve power. Bits AD0VRS and AD1VRS select the ADC0 and ADC1 voltage reference sources, respectively. The electrical specifications for the Voltage Reference are given in Table 10.1.

### Figure 10.1. Voltage Reference Functional Block Diagram

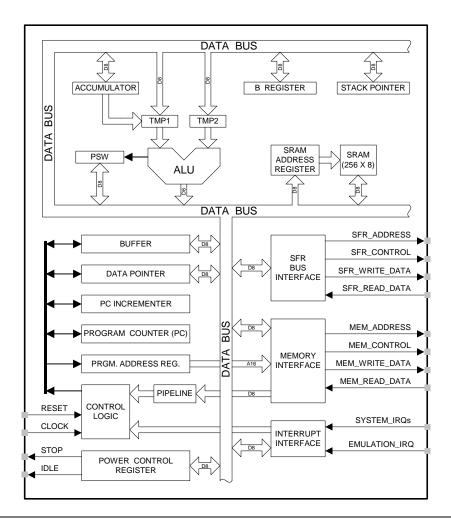

## 12. CIP-51 MICROCONTROLLER

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are five 16-bit counter/timers (see description in Section 22), two full-duplex UARTs (see description in Section 20 and Section 21), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (see Section 12.2.6), and 8/4 byte-wide I/O Ports (see description in Section 17). The CIP-51 also includes on-chip debug hardware (see description in Section 24), and interfaces directly with the MCUs' analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 12.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- 256 Bytes of Internal RAM

- 8/4 Byte-Wide I/O Ports

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

### Figure 12.1. CIP-51 Block Diagram

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### Programming and Debugging Support

A JTAG-based serial interface is provided for in-system programming of the FLASH program memory and communication with on-chip debug support logic. The re-programmable FLASH can also be read and changed a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints and watch points, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debug is completely non-intrusive and non-invasive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, macro assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via its JTAG interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

### 12.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>TM</sup> instruction set; standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>TM</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 12.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 12.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 12.1.2. MOVX Instruction and Program Memory

In the CIP-51, the MOVX instruction serves three purposes: accessing on-chip XRAM, accessing off-chip XRAM, and accessing on-chip program FLASH memory. The FLASH access feature provides a mechanism for user software to update program code and use the program memory space for non-volatile data storage (see Section "15. FLASH

**MEMORY" on page 139**). The External Memory Interface provides a fast access to off-chip XRAM (or memorymapped peripherals) via the MOVX instruction. Refer to **Section "16. EXTERNAL DATA MEMORY INTER-FACE AND ON-CHIP XRAM" on page 145** for details.

| Mnemonic          | Description                              | Bytes | Clock<br>Cycles |

|-------------------|------------------------------------------|-------|-----------------|

|                   | ARITHMETIC OPERATIONS                    |       |                 |

| ADD A, Rn         | Add register to A                        | 1     | 1               |

| ADD A, direct     | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri        | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data      | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn        | Add register to A with carry             | 1     | 1               |

| ADDC A, direct    | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri       | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data     | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn        | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct    | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri       | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data     | Subtract immediate from A with borrow    | 2     | 2               |

| INC A             | Increment A                              | 1     | 1               |

| INC Rn            | Increment register                       | 1     | 1               |

| INC direct        | Increment direct byte                    | 2     | 2               |

| INC @Ri           | Increment indirect RAM                   | 1     | 2               |

| DEC A             | Decrement A                              | 1     | 1               |

| DEC Rn            | Decrement register                       | 1     | 1               |

| DEC direct        | Decrement direct byte                    | 2     | 2               |

| DEC @Ri           | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR          | Increment Data Pointer                   | 1     | 1               |

| MUL AB            | Multiply A and B                         | 1     | 4               |

| DIV AB            | Divide A by B                            | 1     | 8               |

| DA A              | Decimal adjust A                         | 1     | 1               |

|                   | LOGICAL OPERATIONS                       |       |                 |

| ANL A, Rn         | AND Register to A                        | 1     | 1               |

| ANL A, direct     | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri        | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data      | AND immediate to A                       | 2     | 2               |

| ANL direct, A     | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn         | OR Register to A                         | 1     | 1               |

| ORL A, direct     | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri        | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data      | OR immediate to A                        | 2     | 2               |

| ORL direct, A     | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn         | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct     | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri        | Exclusive-OR indirect RAM to A           | 1     | 2               |

## Table 12.1. CIP-51 Instruction Set Summary

## **Table 12.3. Special Function Registers**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register       | Address      | Description                                                  | Page No.             |

|----------------|--------------|--------------------------------------------------------------|----------------------|

| ADC0LTH        | 0xC7         | ADC0 Less-Than High                                          | page 53*, page 69**  |

| ADC0LTL        | 0xC6         | ADC0 Less-Than Low                                           | page 53*, page 69**  |

| ADC1CF         | 0xAB         | ADC1 Analog Multiplexer Configuration                        | page 79              |

| ADC1CN         | 0xAA         | ADC1 Control                                                 | page 80              |

| ADC1           | 0x9C         | ADC1 Data Word                                               | page 81              |

| AMX0CF         | 0xBA         | ADC0 Multiplexer Configuration                               | page 47*, page 63**  |

| AMX0SL         | 0xBB         | ADC0 Multiplexer Channel Select                              | page 48*, page 64**  |

| AMX1SL         | 0xAC         | ADC1 Analog Multiplexer Channel Select                       | page 79              |

| В              | 0xF0         | B Register                                                   | page 115             |

| CKCON          | 0x8E         | Clock Control                                                | page 226             |

| CPT0CN         | 0x9E         | Comparator 0 Control                                         | page 97              |

| CPT1CN         | 0x9F         | Comparator 1 Control                                         | page 98              |

| DACOCN         | 0xD4         | DAC0 Control                                                 | page 86              |

| DAC0H          | 0xD3         | DAC0 High                                                    | page 85              |

| DACOL          | 0xD2         | DAC0 Low                                                     | page 85              |

| DACICN         | 0xD2<br>0xD7 | DAC1 Control                                                 | page 88              |

| DAC1H          | 0xD6         | DAC1 High Byte                                               | page 87              |

| DAC1L          | 0xD5         | DAC1 Low Byte                                                | page 87              |

| DPH            | 0x83         | Data Pointer High                                            | page 113             |

| DPL            | 0x82         | Data Pointer Low                                             | page 113             |

| EIE1           | 0xE6         | Extended Interrupt Enable 1                                  | page 113<br>page 121 |

| EIE1<br>EIE2   | 0xE0         | Extended Interrupt Enable 1<br>Extended Interrupt Enable 2   | page 121<br>page 122 |

| EIE2<br>EIP1   | 0xE7         | Extended Interrupt Enable 2<br>External Interrupt Priority 1 | page 122<br>page 123 |

| EIP1<br>EIP2   | 0xF7         | External Interrupt Priority 2                                | page 123             |

| EIF2<br>EMI0CN | 0xF7<br>0xAF | External Memory Interface Control                            |                      |

| EMIOCK         | 0xAF<br>0xA3 |                                                              | page 147             |

| EMIOCF         |              | EMIF Configuration                                           | page 147             |

| FLACL          | 0xA1<br>0xB7 | EMIF Timing Control<br>FLASH Access Limit                    | page 152             |

| FLACL          |              | FLASH Access Linit<br>FLASH Scale                            | page 142             |

|                | 0xB6         |                                                              | page 143             |

| IE             | 0xA8         | Interrupt Enable                                             | page 119             |

| IP             | 0xB8         | Interrupt Priority                                           | page 120             |

| OSCICN         | 0xB2         | Internal Oscillator Control                                  | page 136             |

| OSCXCN         | 0xB1         | External Oscillator Control                                  | page 137             |

| P0             | 0x80         | Port 0 Latch                                                 | page 173             |

| POMDOUT        | 0xA4         | Port 0 Output Mode Configuration                             | page 173             |

| P1             | 0x90         | Port 1 Latch                                                 | page 174             |

| P1MDIN         | 0xBD         | Port 1 Input Mode                                            | page 174             |

| P1MDOUT        | 0xA5         | Port 1 Output Mode Configuration                             | page 175             |

| P2             | 0xA0         | Port 2 Latch                                                 | page 175             |

| P2MDOUT        | 0xA6         | Port 2 Output Mode Configuration                             | page 175             |

| P3             | 0xB0         | Port 3 Latch                                                 | page 176             |

| P3IF           | 0xAD         | Port 3 Interrupt Flags                                       | page 177             |

| P3MDOUT        | 0xA7         | Port 3 Output Mode Configuration                             | page 176             |

| †P4            | 0x84         | Port 4 Latch                                                 | page 180†            |

| †P5            | 0x85         | Port 5 Latch                                                 | page 180†            |

| R/W   | R/W                           | R/W   | R/W             | R/W          | R/W     | R/W   | R/W              | Reset Value  |

|-------|-------------------------------|-------|-----------------|--------------|---------|-------|------------------|--------------|

| ACC.7 | ACC.6                         | ACC.5 | ACC.4           | ACC.3        | ACC.2   | ACC.1 | ACC.0            | 00000000     |

| Bit7  | Bit6                          | Bit5  | Bit4            | Bit3         | Bit2    | Bit1  | Bit0             | SFR Address: |

|       |                               |       |                 |              |         | (     | bit addressable) | ) 0xE0       |

|       | ACC: Accum<br>This register i |       | ulator for arit | hmetic opera | ations. |       |                  |              |

## Figure 12.7. ACC: Accumulator

Figure 12.8. B: B Register

| R/W                                                                                                        | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W               | Reset Value  |  |  |

|------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------------|--------------|--|--|

| B.7                                                                                                        | B.6  | B.5  | B.4  | B.3  | B.2  | B.1  | B.0               | 00000000     |  |  |

| Bit7                                                                                                       | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0              | SFR Address: |  |  |

|                                                                                                            |      |      |      |      |      |      | (bit addressable) | ) 0xF0       |  |  |

| Bits7-0: B: B Register.<br>This register serves as a second accumulator for certain arithmetic operations. |      |      |      |      |      |      |                   |              |  |  |

| Interrupt Source             | Interrupt<br>Vector | Priority<br>Order | Pending Flag                        | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|------------------------------|---------------------|-------------------|-------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                        | 0x0000              | Тор               | None                                | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (/INT0) | 0x0003              | 0                 | IE0 (TCON.1)                        | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow             | 0x000B              | 1                 | TF0 (TCON.5)                        | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (/INT1) | 0x0013              | 2                 | IE1 (TCON.3)                        | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow             | 0x001B              | 3                 | TF1 (TCON.7)                        | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                        | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)      | Y                |                | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow (or EXF2)   | 0x002B              | 5                 | TF2 (T2CON.7)                       | Y                |                | ET2 (IE.5)         | PT2 (IP.5)          |

| Serial Peripheral Interface  | 0x0033              | 6                 | SPIF (SPI0CN.7)                     | Y                |                | ESPI0<br>(EIE1.0)  | PSPI0<br>(EIP1.0)   |

| SMBus Interface              | 0x003B              | 7                 | SI (SMB0CN.3)                       | Y                |                | ESMB0<br>(EIE1.1)  | PSMB0<br>(EIP1.1)   |

| ADC0 Window Comparator       | 0x0043              | 8                 | AD0WINT<br>(ADC0CN.2)               | Y                |                | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| Programmable Counter Array   | 0x004B              | 9                 | CF (PCA0CN.7)<br>CCFn<br>(PCA0CN.n) | Y                |                | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator 0 Falling Edge    | 0x0053              | 10                | CP0FIF<br>(CPT0CN.4)                |                  |                | ECP0F<br>(EIE1.4)  | PCP0F<br>(EIP1.4)   |

| Comparator 0 Rising Edge     | 0x005B              | 11                | CPORIF<br>(CPT0CN.5)                |                  |                | ECP0R<br>(EIE1.5)  | PCP0R<br>(EIP1.5)   |

| Comparator 1 Falling Edge    | 0x0063              | 12                | CP1FIF<br>(CPT1CN.4)                |                  |                | ECP1F<br>(EIE1.6)  | PCP1F<br>(EIP1.6)   |

| Comparator 1 Rising Edge     | 0x006B              | 13                | CP1RIF<br>(CPT1CN.5)                |                  |                | ECP1R<br>(EIE1.7)  | PCP1F<br>(EIP1.7)   |

| Timer 3 Overflow             | 0x0073              | 14                | TF3 (TMR3CN.7)                      |                  |                | ET3<br>(EIE2.0)    | PT3<br>(EIP2.0)     |

| ADC0 End of Conversion       | 0x007B              | 15                | AD0INT<br>(ADC0CN.5)                | Y                |                | EADC0<br>(EIE2.1)  | PADC0<br>(EIP2.1)   |

| Timer 4 Overflow             | 0x0083              | 16                | TF4 (T4CON.7)                       |                  |                | ET4<br>(EIE2.2)    | PT4<br>(EIP2.2)     |

| ADC1 End of Conversion       | 0x008B              | 17                | AD1INT<br>(ADC1CN.5)                |                  |                | EADC1<br>(EIE2.3)  | PADC1<br>(EIP2.3)   |

| External Interrupt 6         | 0x0093              | 18                | IE6 (P3IF.5)                        |                  |                | EX6<br>(EIE2.4)    | PX6<br>(EIP2.4)     |

| External Interrupt 7         | 0x009B              | 19                | IE7 (P3IF.6)                        |                  |                | EX7<br>(EIE2.5)    | PX7<br>(EIP2.5)     |

| UART1                        | 0x00A3              | 20                | RI1 (SCON1.0)<br>TI1 (SCON1.1)      |                  |                | ES1                | PS1                 |

| External Crystal OSC Ready   | 0x00AB              | 21                | XTLVLD<br>(OSCXCN.7)                |                  |                | EXVLD<br>(EIE2.7)  | PXVLD<br>(EIP2.7)   |

| R/W   | R/W                                              | R/W            | R/W           | R/W             | R/W           | R/W             | R/W  | Reset Value          |

|-------|--------------------------------------------------|----------------|---------------|-----------------|---------------|-----------------|------|----------------------|

| PXVLD | EP1                                              | PX7            | PX6           | PADC1           | PT4           | PADC0           | PT3  | 00000000             |

| Bit7  | Bit6                                             | Bit5           | Bit4          | Bit3            | Bit2          | Bit1            | Bit0 | SFR Address:<br>0xF7 |

| Bit7: | PXVLD: Exte                                      | ernal Clock S  | Source Valid  | (XTLVLD) I      | nterrupt Pri  | iority Control. |      |                      |

|       | This bit sets the                                | he priority of | f the XTLVI   | D interrupt.    | -             | -               |      |                      |

|       | 0: XTLVLD i                                      | nterrupt set t | o low priori  | ty level.       |               |                 |      |                      |

|       | 1: XTLVLD i                                      | nterrupt set t | o high prior  | ity level.      |               |                 |      |                      |

| Bit6: | EP1: UART1                                       | Interrupt Pri  | ority Contro  | ol.             |               |                 |      |                      |

|       | This bit sets the                                | he priority of | f the UART    | interrupt.      |               |                 |      |                      |

|       | 0: UART1 int                                     | errupt set to  | low priority  |                 |               |                 |      |                      |

|       | 1: UART1 int                                     | errupt set to  | high priority | /.              |               |                 |      |                      |

| Bit5: | PX7: External                                    | l Interrupt 7  | Priority Cor  | trol.           |               |                 |      |                      |

|       | This bit sets the                                |                |               |                 |               |                 |      |                      |

|       | 0: External In                                   | terrupt 7 set  | to low prior  | ity level.      |               |                 |      |                      |

|       | 1: External In                                   | terrupt 7 set  | to high prio  | rity level.     |               |                 |      |                      |

| Bit4: | PX6: External                                    | l Interrupt 6  | Priority Cor  | trol.           |               |                 |      |                      |

|       | This bit sets the                                | he priority of | f the Externa | al Interrupt 6. |               |                 |      |                      |

|       | 0: External In                                   | terrupt 6 set  | to low prior  | ity level.      |               |                 |      |                      |

|       | 1: External In                                   | terrupt 6 set  | to high prio  | rity level.     |               |                 |      |                      |

| Bit3: | PADC1: ADC                                       | C1 End Of C    | onversion In  | terrupt Priori  | y Control.    |                 |      |                      |

|       | This bit sets the                                | he priority of | f the ADC1    | End of Conve    | rsion interr  | upt.            |      |                      |

|       | 0: ADC1 End                                      | of Conversi    | on interrupt  | set to low pri  | ority.        |                 |      |                      |

|       | 1: ADC1 End                                      | of Conversi    | on interrupt  | set to low pri  | ority.        |                 |      |                      |

| Bit2: | PT4: Timer 4                                     | Interrupt Pri  | ority Contro  | ol.             |               |                 |      |                      |

|       | This bit sets the                                | he priority of | f the Timer 4 | l interrupt.    |               |                 |      |                      |

|       | 0: Timer 4 int                                   | errupt set to  | low priority  |                 |               |                 |      |                      |

|       | 1: Timer 4 int                                   | errupt set to  | low priority  |                 |               |                 |      |                      |

| Bit1: | PADC0: ADC                                       | End of Cor     | version Inte  | rrupt Priority  | Control.      |                 |      |                      |

|       | This bit sets the                                | he priority of | f the ADC0    | End of Conve    | rsion Intern  | rupt.           |      |                      |

|       | 0: ADC0 End                                      | of Conversi    | on interrupt  | set to low pri  | ority level.  |                 |      |                      |

|       | 1: ADC0 End                                      | of Conversi    | on interrupt  | set to high pr  | iority level. |                 |      |                      |

| Bit0: | PT3: Timer 3                                     |                | -             |                 | -             |                 |      |                      |

|       | This bit sets the                                | -              | •             |                 |               |                 |      |                      |

|       | 0: Timer 3 int                                   |                |               |                 | oriority orde | er.             |      |                      |

|       | 1: Timer 3 interrupt set to high priority level. |                |               |                 |               |                 |      |                      |

Figure 12.14. EIP2: Extended Interrupt Priority 2

| R/W              | R/W                                                                                                                                              | R/W                                                            | R/W                                     | R/W                          | R/W               | R/W        | R/W        | Reset Value  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------|------------------------------|-------------------|------------|------------|--------------|--|--|

| XTLVLI           |                                                                                                                                                  | XOSCMD1                                                        |                                         | -                            | XFCN2             | XFCN1      | XFCN0      | 00000000     |  |  |

| Bit7             | Bit6                                                                                                                                             | Bit5                                                           | Bit4                                    | Bit3                         | Bit2              | Bit1       | Bit0       | SFR Address: |  |  |

|                  |                                                                                                                                                  |                                                                |                                         |                              |                   |            |            | 0xB1         |  |  |

|                  |                                                                                                                                                  |                                                                |                                         |                              |                   |            |            |              |  |  |

| Bit7:            | XTLVLD: Ci                                                                                                                                       | ystal Oscillat                                                 | or Valid Flag                           | z                            |                   |            |            |              |  |  |

|                  | (Valid only when XOSCMD = 11x.)                                                                                                                  |                                                                |                                         |                              |                   |            |            |              |  |  |

|                  | 0: Crystal Os                                                                                                                                    | 0: Crystal Oscillator is unused or not yet stable              |                                         |                              |                   |            |            |              |  |  |

|                  |                                                                                                                                                  | cillator is run                                                |                                         |                              |                   |            |            |              |  |  |

| Bits6-4:         | XOSCMD2-0                                                                                                                                        |                                                                |                                         |                              |                   |            |            |              |  |  |

|                  | 00x: Off. XT.                                                                                                                                    |                                                                |                                         | •                            |                   |            |            |              |  |  |

|                  | 010: System                                                                                                                                      |                                                                |                                         |                              |                   |            | •          |              |  |  |

|                  | 011: System                                                                                                                                      |                                                                |                                         |                              | XTALI pin         | divided by | 2.         |              |  |  |

|                  |                                                                                                                                                  | scillator Mod                                                  |                                         | e by 2 stage.                |                   |            |            |              |  |  |

|                  |                                                                                                                                                  | Oscillator Mo                                                  |                                         | do by 2 store                |                   |            |            |              |  |  |

| Bit3:            | RESERVED.                                                                                                                                        | Oscillator Mo<br>Read – under                                  |                                         |                              | •                 |            |            |              |  |  |

| Bits2-0:         | XFCN2-0: E                                                                                                                                       |                                                                |                                         |                              | Rits              |            |            |              |  |  |

| <b>D</b> 1132 0. | 000-111:                                                                                                                                         | Kiernar Oberna                                                 | ator i requen                           | cy control I                 | 105               |            |            |              |  |  |

|                  | XFCN                                                                                                                                             | Crystal (XO                                                    | SCMD = 112                              | $\mathbf{x}$ ) RC (2         | KOSCMD =          | 10x) C     | (XOSCMD =  | = 10x)       |  |  |

|                  | 000                                                                                                                                              |                                                                | 12 kHz                                  |                              | f < 25 kHz        |            | K Factor = | = 0.44       |  |  |

|                  | 001                                                                                                                                              | 12 kHz                                                         | $< f \le 30 \text{ kHz}$                | z 25                         | $kHz < f \le 50$  | kHz        | K Factor   | = 1.4        |  |  |

|                  | 010                                                                                                                                              | 30 kHz                                                         | < f ≤ 95 kHz                            | z 50 l                       | $Hz < f \le 10$   | ) kHz      | K Factor   | = 4.4        |  |  |

|                  | 011                                                                                                                                              | 95 kHz <                                                       | < f ≤ 270 kH                            | z 100                        | $kHz < f \le 20$  | 0 kHz      | K Factor   | = 13         |  |  |

|                  | 100                                                                                                                                              | 270 kHz                                                        | $< f \le 720 \text{ kH}$                | Iz 200                       | $kHz < f \le 40$  | 0 kHz      | K Factor   | = 38         |  |  |

|                  | 101                                                                                                                                              | 720 kHz                                                        | $< f \le 2.2 MH$                        | Iz 400                       | $kHz < f \le 80$  | 0 kHz      | K Factor = | = 100        |  |  |

|                  | 110                                                                                                                                              | 2.2 MHz                                                        | $< f \le 6.7 MF$                        | Hz 800                       | $kHz < f \le 1.0$ | 5 MHz      | K Factor = | = 420        |  |  |

|                  | 111                                                                                                                                              | f >                                                            | 6.7 MHz                                 | 1.6 N                        | $MHz < f \le 3.2$ | 2 MHz      | K Factor = | : 1400       |  |  |

| CRYSTA           | <b>CRYSTAL MODE</b> (Circuit from Figure 14.1, Option 1; XOSCMD = 11x)<br>Choose XFCN value to match the crystal or ceramic resonator frequency. |                                                                |                                         |                              |                   |            |            |              |  |  |

| RC MOD           | E (Circuit from                                                                                                                                  | n Figure 14.1                                                  | , Option 2; X                           | KOSCMD =                     | 10x)              |            |            |              |  |  |

|                  | Choose oscill                                                                                                                                    | ation frequen                                                  | cy range wh                             | ere:                         |                   |            |            |              |  |  |

|                  | $f = 1.23(10^3)$                                                                                                                                 | / (R * C), wh                                                  | ere                                     |                              |                   |            |            |              |  |  |

|                  | f = frequency of oscillation in MHz                                                                                                              |                                                                |                                         |                              |                   |            |            |              |  |  |

|                  | C = capacitor value in pF                                                                                                                        |                                                                |                                         |                              |                   |            |            |              |  |  |

|                  | $R = Pull-up$ resistor value in k $\Omega$                                                                                                       |                                                                |                                         |                              |                   |            |            |              |  |  |

| C MODE           | C (Circuit from<br>Choose K Fa<br>f = KF / (C *<br>f = frequency<br>C = capaciton<br>AV+ = Analo                                                 | ctor (KF) for<br>AV+), where<br>of oscillation<br>value on XT. | the oscillation<br>in MHz<br>AL1, XTAL2 | on frequency<br>2 pins in pF |                   |            |            |              |  |  |

## Figure 14.3. OSCXCN: External Oscillator Control Register

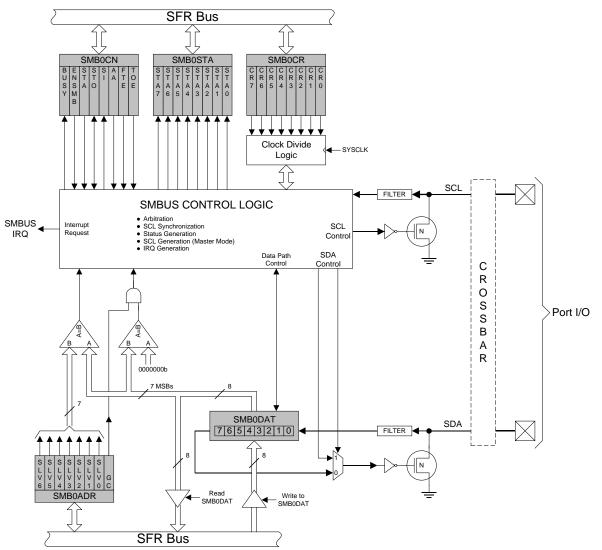

## **18.** SYSTEM MANAGEMENT BUS / I<sup>2</sup>C BUS (SMBUS0)

The SMBus0 I/O interface is a two-wire, bi-directional serial bus. SMBus0 is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus0 interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/8th of the system clock if desired (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

SMBus0 may operate as a master and/or slave, and may function on a bus with multiple masters. SMBus0 provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. SMBus0 is controlled by SFRs as described in Section 18.4 on page 189.

## Figure 18.1. SMBus0 Block Diagram

|           | rigur                                                                                                                                                                                                                                                  | e 22.15. K | CAP2L: | limer 2 Ca | apture Re | gister Lov | v Byte |                      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------|-----------|------------|--------|----------------------|

| R/W       | R/W                                                                                                                                                                                                                                                    | R/W        | R/W    | R/W        | R/W       | R/W        | R/W    | Reset Value 00000000 |

| Bit7      | Bit6                                                                                                                                                                                                                                                   | Bit5       | Bit4   | Bit3       | Bit2      | Bit1       | Bit0   | SFR Address:<br>0xCA |

| Bits 7-0: | Bits 7-0: RCAP2L: Timer 2 Capture Register Low Byte.<br>The RCAP2L register captures the low byte of Timer 2 when Timer 2 is configured in capture mode.<br>When Timer 2 is configured in auto-reload mode, it holds the low byte of the reload value. |            |        |            |           |            |        |                      |

## Figure 22.15. RCAP2L: Timer 2 Capture Register Low Byte

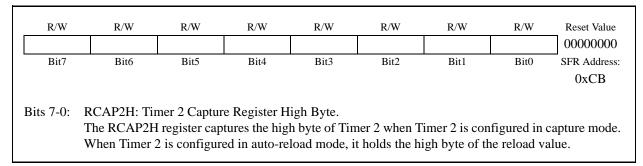

## Figure 22.16. RCAP2H: Timer 2 Capture Register High Byte

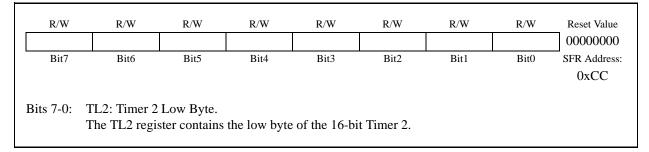

## Figure 22.17. TL2: Timer 2 Low Byte

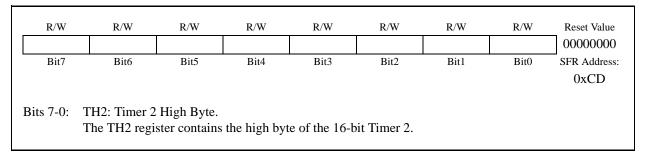

## Figure 22.18. TH2 Timer 2 High Byte

| R/W     | R/W                        | R/W            | R/W            | R/W           | R/W            | R/W            | R/W             | Reset Value   |

|---------|----------------------------|----------------|----------------|---------------|----------------|----------------|-----------------|---------------|

| PWM16   | n ECOMn                    | CAPPn          | CAPNn          | MATn          | TOGn           | PWMn           | ECCFn           | 00000000      |

| Bit7    | Bit6                       | Bit5           | Bit4           | Bit3          | Bit2           | Bit1           | Bit0            | SFR Address:  |

|         |                            |                |                |               |                |                |                 | 0xDA-0xDE     |

|         |                            |                |                |               |                |                |                 |               |

| PCA0CPN | In Address:                | PCA0C          | PM0 = 0xDA     | A(n = 0)      |                |                |                 |               |

|         |                            |                | PM1 = 0xDE     | · /           |                |                |                 |               |

|         |                            | PCA0C          | PM2 = 0xDC     | C(n = 2)      |                |                |                 |               |

|         |                            |                | PM3 = 0xDI     | . ,           |                |                |                 |               |

|         |                            | PCA0C          | PM4 = 0xDB     | E(n = 4)      |                |                |                 |               |

| Bit7:   | PWM16n: 16                 | hit Dulso W    | idth Modula    | tion Enable   |                |                |                 |               |

| DII/.   | This bit select            |                |                |               | fulation mod   | le is enabled  | (PWMn - 1)      | )             |

|         | 0: 8-bit PWM               |                | ie when i uis  |               |                | ie is chabled  | (1 ** 1*111 = 1 | .).           |

|         | 1: 16-bit PWN              |                |                |               |                |                |                 |               |

| Bit6:   | ECOMn: Con                 |                | ction Enable   |               |                |                |                 |               |

| Dito.   | This bit enabl             | -              |                |               | or PCA0 mo     | dule n.        |                 |               |

|         | 0: Disabled.               |                |                |               |                |                |                 |               |

|         | 1: Enabled.                |                |                |               |                |                |                 |               |

| Bit5:   | CAPPn: Capt                | ure Positive   | Function En    | able.         |                |                |                 |               |

|         | This bit enabl             |                |                |               | for PCA0 mo    | odule n.       |                 |               |

|         | 0: Disabled.               |                | 1              | 0 1           |                |                |                 |               |

|         | 1: Enabled.                |                |                |               |                |                |                 |               |

| Bit4:   | CAPNn: Capt                | ure Negative   | e Function E   | nable.        |                |                |                 |               |

|         | This bit enabl             | es/disables t  | he negative e  | edge capture  | for PCA0 m     | odule n.       |                 |               |

|         | 0: Disabled.               |                |                |               |                |                |                 |               |

|         | 1: Enabled.                |                |                |               |                |                |                 |               |

| Bit3:   | MATn: Match                |                |                |               |                |                |                 |               |

|         | This bit enabl             |                |                |               |                |                |                 |               |

|         | PCA0 counter               |                | ule's capture  | /compare reg  | gister cause t | he CCFn bit    | in PCA0MI       | O register to |

|         | be set to logic            | : 1.           |                |               |                |                |                 |               |

|         | 0: Disabled.               |                |                |               |                |                |                 |               |

|         | 1: Enabled.                |                |                |               |                |                |                 |               |

| Bit2:   | TOGn: Toggl                |                |                |               |                | ****           |                 | 0.1           |

|         | This bit enabl             |                | 00             |               |                |                |                 |               |

|         | PCA0 counter               |                | -              |               |                | -              |                 |               |

|         | gle. If the PW             | Mn bit is als  | so set to logi | c 1, the modi | ile operates i | in Frequency   | Output Mo       | de.           |

|         | 0: Disabled.               |                |                |               |                |                |                 |               |

| Bit1:   | 1: Enabled.<br>PWMn: Pulse | Width Mod      | ulation Mod    | a Enabla      |                |                |                 |               |

| DILI.   | This bit enabl             |                |                |               | 10 modulo r    | Whon onch      | lad a pulsa     | width modu    |

|         | lated signal is            |                |                |               |                |                | · 1             |               |

|         | if PWM16n lo               | -              | -              |               |                | -              |                 |               |

|         | 0: Disabled.               | 5510 1. 11 UIC | 10011 UIL IS   | uiso set, uit | module oper    | allos in riequ | iency Outpu     |               |

|         | 1: Enabled.                |                |                |               |                |                |                 |               |

| Bit0:   | ECCFn: Capt                | ure/Compare    | e Flag Intern  | ipt Enable    |                |                |                 |               |

| 5110.   | This bit sets the          | -              | -              | -             | ag (CCFn)      | interrupt      |                 |               |

|         | 0: Disable CC              | -              | -              | e, computer   |                |                |                 |               |

|         | 1: Enable a C              |                |                | errupt reques | t when CCF     | n is set.      |                 |               |

|         |                            | -r tare, comp  |                | reques        |                |                |                 |               |

## Figure 23.12. PCA0CPMn: PCA0 Capture/Compare Mode Registers

## 24.1. Boundary Scan

The DR in the Boundary Scan path is an 134-bit shift register. The Boundary DR provides control and observability of all the device pins as well as the SFR bus and Weak Pullup feature via the EXTEST and SAMPLE commands.

| Bit                   | Action  | Target                                                          |

|-----------------------|---------|-----------------------------------------------------------------|

| 0                     | Capture | Reset Enable from MCU (C8051F021/3 devices)                     |

|                       | Update  | Reset Enable to /RST pin (C8051F021/3 devices)                  |

| 1                     | Capture | Reset input from /RST pin (C8051F021/3 devices)                 |

|                       | Update  | Reset output to /RST pin (C8051F021/3 devices)                  |

| 2                     | Capture | Reset Enable from MCU (C8051F020/2 devices)                     |

|                       | Update  | Reset Enable to /RST pin (C8051F020/2 devices)                  |

| 3                     | Capture | Reset input from /RST pin (C8051F020/2 devices)                 |

|                       | Update  | Reset output to /RST pin (C8051F020/2 devices)                  |

| 4                     | Capture | External Clock from XTAL1 pin                                   |

|                       | Update  | Not used                                                        |