Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT          |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 4.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 8x8b, 8x10b; D/A 2x12b                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 64-TQFP                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f023 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

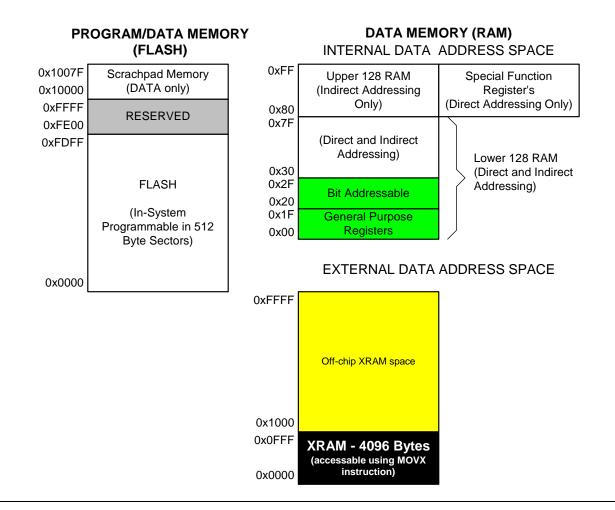

### 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The CIP-51 in the C8051F020/1/2/3 MCUs additionally has an on-chip 4k byte RAM block and an external memory interface (EMIF) for accessing off-chip data memory. The on-chip 4k byte block can be addressed over the entire 64k external data memory address range (overlapping 4k boundaries). External data memory address space can be mapped to on-chip memory only, off-chip memory only, or a combination of the two (addresses up to 4k directed to on-chip, above 4k directed to EMIF). The EMIF is also configurable for multiplexed or non-multiplexed address/data lines.

The MCU's program memory consists of 64k bytes of FLASH. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. The 512 bytes from addresses 0xFE00 to 0xFFFF are reserved for factory use. There is also a single 128 byte sector at address 0x10000 to 0x1007F, which may be useful as a small table for software constants. See Figure 1.7 for the MCU system memory map.

## Figure 1.7. On-Chip Memory Map

## 4. PINOUT AND PACKAGE DEFINITIONS

### **Table 4.1. Pin Definitions**

|       | Pin Nu        | imbers        |       |                                                                                                                                                                                                                                                                                               |

|-------|---------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name  | F020          | F021          | Туре  | Description                                                                                                                                                                                                                                                                                   |

|       | F022          | F023          |       |                                                                                                                                                                                                                                                                                               |

| VDD   | 37, 64,<br>90 | 24, 41,<br>57 |       | Digital Supply Voltage. Must be tied to +2.7 to +3.6 V.                                                                                                                                                                                                                                       |

| DGND  | 38, 63,<br>89 | 25, 40,<br>56 |       | Digital Ground. Must be tied to Ground.                                                                                                                                                                                                                                                       |

| AV+   | 11, 14        | 6             |       | Analog Supply Voltage. Must be tied to +2.7 to +3.6 V.                                                                                                                                                                                                                                        |

| AGND  | 10, 13        | 5             |       | Analog Ground. Must be tied to Ground.                                                                                                                                                                                                                                                        |

| TMS   | 1             | 58            | D In  | JTAG Test Mode Select with internal pull-up.                                                                                                                                                                                                                                                  |

| ТСК   | 2             | 59            | D In  | JTAG Test Clock with internal pull-up.                                                                                                                                                                                                                                                        |

| TDI   | 3             | 60            | D In  | JTAG Test Data Input with internal pull-up. TDI is latched on the rising edge of TCK.                                                                                                                                                                                                         |

| TDO   | 4             | 61            | D Out | JTAG Test Data Output with internal pull-up. Data is shifted out on TDO on the falling edge of TCK. TDO output is a tri-state driver.                                                                                                                                                         |

| /RST  | 5             | 62            | D I/O | Device Reset. Open-drain output of internal VDD monitor. Is driven<br>low when VDD is <2.7 V and MONEN is high. An external source<br>can initiate a system reset by driving this pin low.                                                                                                    |

| XTAL1 | 26            | 17            | A In  | Crystal Input. This pin is the return for the internal oscillator circuit<br>for a crystal or ceramic resonator. For a precision internal clock,<br>connect a crystal or ceramic resonator from XTAL1 to XTAL2. If<br>overdriven by an external CMOS clock, this becomes the system<br>clock. |

| XTAL2 | 27            | 18            | A Out | Crystal Output. This pin is the excitation driver for a crystal or ceramic resonator.                                                                                                                                                                                                         |

| MONEN | 28            | 19            | D In  | VDD Monitor Enable. When tied high, this pin enables the internal VDD monitor, which forces a system reset when VDD is < 2.7 V. When tied low, the internal VDD monitor is disabled.                                                                                                          |

| VREF  | 12            | 7             | A I/O | Bandgap Voltage Reference Output (all devices).<br>DAC Voltage Reference Input (F021/3 only).                                                                                                                                                                                                 |

| VREFA |               | 8             | A In  | ADC0 and ADC1 Voltage Reference Input.                                                                                                                                                                                                                                                        |

| VREF0 | 16            |               | A In  | ADC0 Voltage Reference Input.                                                                                                                                                                                                                                                                 |

| VREF1 | 17            |               | A In  | ADC1 Voltage Reference Input.                                                                                                                                                                                                                                                                 |

| VREFD | 15            |               | A In  | DAC Voltage Reference Input.                                                                                                                                                                                                                                                                  |

### 7.2. ADC1 Modes of Operation

ADC1 has a maximum conversion speed of 500 ksps. The ADC1 conversion clock (SAR1 clock) is a divided version of the system clock, determined by the AD1SC bits in the ADC1CF register (system clock divided by (AD1SC + 1) for  $0 \le AD1SC \le 31$ ). The maximum ADC1 conversion clock is 6 MHz.

### 7.2.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC1 Start of Conversion Mode bits (AD1CM2-0) in register ADC1CN. Conversions may be initiated by:

- 1. Writing a '1' to the AD1BUSY bit of ADC1CN;

- 2. A Timer 3 overflow (i.e. timed continuous conversions);

- 3. A rising edge detected on the external ADC convert start signal, CNVSTR;

- 4. A Timer 2 overflow (i.e. timed continuous conversions);

- 5. Writing a '1' to the AD0BUSY of register ADC0CN (initiate conversion of ADC1 and ADC0 with a single software command).

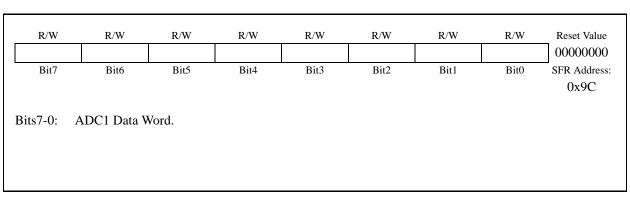

During conversion, the AD1BUSY bit is set to logic 1 and restored to 0 when conversion is complete. The falling edge of AD1BUSY triggers an interrupt (when enabled) and sets the interrupt flag in ADC1CN. Converted data is available in the ADC1 data word, ADC1.

When a conversion is initiated by writing a '1' to AD1BUSY, it is recommended to poll AD1INT to determine when the conversion is complete. The recommended procedure is:

- Step 1. Write a '0' to AD1INT;

- Step 2. Write a '1' to AD1BUSY;

- Step 3. Poll AD1INT for '1';

- Step 4. Process ADC1 data.

#### 7.2.2. Tracking Modes

The AD1TM bit in register ADC1CN controls the ADC1 track-and-hold mode. In its default state, the ADC1 input is continuously tracked, except when a conversion is in progress. When the AD1TM bit is logic 1, ADC1 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC1 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR (see Figure 7.2). Tracking can also be disabled (shutdown) when the entire chip is in low power standby or sleep modes. Low-power Track-and-Hold mode is also useful when AMUX or PGA settings are frequently changed, due to the settling time requirements described in Section "7.2.3. Settling Time Requirements" on page 78.

## Figure 7.7. ADC1: ADC1 Data Word Register

## Figure 7.8. ADC1 Data Word Example

| AIN1.0-AGND<br>(Volts) | ADC1 |  |

|------------------------|------|--|

| VREF * (255/256)       | 0xFF |  |

| VREF / 2               | 0x80 |  |

| VREF * (127/256)       | 0x7F |  |

| 0                      | 0x00 |  |

### **Table 12.3. Special Function Registers**

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register       | Address      | Description                                                | Page No.             |

|----------------|--------------|------------------------------------------------------------|----------------------|

| ADC0LTH        | 0xC7         | ADC0 Less-Than High                                        | page 53*, page 69**  |

| ADC0LTL        | 0xC6         | ADC0 Less-Than Low                                         | page 53*, page 69**  |

| ADC1CF         | 0xAB         | ADC1 Analog Multiplexer Configuration                      | page 79              |

| ADC1CN         | 0xAA         | ADC1 Control                                               | page 80              |

| ADC1           | 0x9C         | ADC1 Data Word                                             | page 81              |

| AMX0CF         | 0xBA         | ADC0 Multiplexer Configuration                             | page 47*, page 63**  |

| AMX0SL         | 0xBB         | ADC0 Multiplexer Channel Select                            | page 48*, page 64**  |

| AMX1SL         | 0xAC         | ADC1 Analog Multiplexer Channel Select                     | page 79              |

| В              | 0xF0         | B Register                                                 | page 115             |

| CKCON          | 0x8E         | Clock Control                                              | page 226             |

| CPT0CN         | 0x9E         | Comparator 0 Control                                       | page 97              |

| CPT1CN         | 0x9F         | Comparator 1 Control                                       | page 98              |

| DACOCN         | 0xD4         | DAC0 Control                                               | page 86              |

| DAC0H          | 0xD3         | DAC0 High                                                  | page 85              |

| DACOL          | 0xD2         | DAC0 Low                                                   | page 85              |

| DACICN         | 0xD2<br>0xD7 | DAC1 Control                                               | page 88              |

| DAC1H          | 0xD6         | DAC1 High Byte                                             | page 87              |

| DAC1L          | 0xD5         | DAC1 Low Byte                                              | page 87              |

| DPH            | 0x83         | Data Pointer High                                          | page 113             |

| DPL            | 0x82         | Data Pointer Low                                           | page 113             |

| EIE1           | 0xE6         | Extended Interrupt Enable 1                                | page 113<br>page 121 |

| EIE1<br>EIE2   | 0xE0         | Extended Interrupt Enable 1<br>Extended Interrupt Enable 2 | page 121<br>page 122 |

| EIE2<br>EIP1   | 0xE7         | External Interrupt Priority 1                              | page 122<br>page 123 |

| EIP1<br>EIP2   | 0xF7         | External Interrupt Priority 2                              | page 123             |

| EIF2<br>EMI0CN | 0xF7<br>0xAF | External Memory Interface Control                          |                      |

| EMIOCK         | 0xAF<br>0xA3 |                                                            | page 147             |

| EMIOCF         |              | EMIF Configuration                                         | page 147             |

| FLACL          | 0xA1<br>0xB7 | EMIF Timing Control<br>FLASH Access Limit                  | page 152             |

| FLACL          |              | FLASH Access Linit<br>FLASH Scale                          | page 142             |

|                | 0xB6         |                                                            | page 143             |

| IE             | 0xA8         | Interrupt Enable                                           | page 119             |

| IP             | 0xB8         | Interrupt Priority                                         | page 120             |

| OSCICN         | 0xB2         | Internal Oscillator Control                                | page 136             |

| OSCXCN         | 0xB1         | External Oscillator Control                                | page 137             |

| P0             | 0x80         | Port 0 Latch                                               | page 173             |

| POMDOUT        | 0xA4         | Port 0 Output Mode Configuration                           | page 173             |

| P1             | 0x90         | Port 1 Latch                                               | page 174             |

| P1MDIN         | 0xBD         | Port 1 Input Mode                                          | page 174             |

| P1MDOUT        | 0xA5         | Port 1 Output Mode Configuration                           | page 175             |

| P2             | 0xA0         | Port 2 Latch                                               | page 175             |

| P2MDOUT        | 0xA6         | Port 2 Output Mode Configuration                           | page 175             |

| P3             | 0xB0         | Port 3 Latch                                               | page 176             |

| P3IF           | 0xAD         | Port 3 Interrupt Flags                                     | page 177             |

| P3MDOUT        | 0xA7         | Port 3 Output Mode Configuration                           | page 176             |

| †P4            | 0x84         | Port 4 Latch                                               | page 180†            |

| †P5            | 0x85         | Port 5 Latch                                               | page 180†            |

| R/W      | R/W               | R/W           | R/W             | R/W        | R/W             | R/W        | R/W              | Reset Value |

|----------|-------------------|---------------|-----------------|------------|-----------------|------------|------------------|-------------|

| -        | -                 | PT2           | PS0             | PT1        | PX1             | PT0        | PX0              | 00000000    |

| Bit7     | Bit6              | Bit5          | Bit4            | Bit3       | Bit2            | Bit1       | Bit0             | SFR Address |

|          |                   |               |                 |            |                 |            | (bit addressable | e) 0xB8     |

| Bits7-6: | UNUSED. Re        | ead = 11b, W  | /rite = don't c | are.       |                 |            |                  |             |

| Bit5:    | PT2: Timer 2      | Interrupt Pr  | iority Contro   | 1.         |                 |            |                  |             |

|          | This bit sets the |               |                 | -          |                 |            |                  |             |

|          | 0: Timer 2 int    | 1 1           | •               | •          | priority order  | ſ.         |                  |             |

|          | 1: Timer 2 int    | -             | 01              | •          |                 |            |                  |             |

| Bit4:    | PS0: UART0        | 1             |                 |            |                 |            |                  |             |

|          | This bit sets t   | 1 *           |                 | 1          |                 |            |                  |             |

|          | 0: UART0 int      |               |                 |            | priority order  | ſ.         |                  |             |

|          | 1: UART0 int      | 1             | 01              | •          |                 |            |                  |             |

| Bit3:    | PT1: Timer 1      | -             | •               |            |                 |            |                  |             |

|          | This bit sets t   |               |                 | -          |                 |            |                  |             |

|          | 0: Timer 1 int    |               |                 |            | priority order  | ſ <b>.</b> |                  |             |

|          | 1: Timer 1 int    |               |                 |            |                 |            |                  |             |

| Bit2:    | PX1: Externa      | 1             | •               |            |                 |            |                  |             |

|          | This bit sets t   | 1 V           |                 | 1          | -               |            |                  |             |

|          | 0: External In    |               | •               | •          | ult priority or | der.       |                  |             |

|          | 1: External In    | 1             | 01              | •          |                 |            |                  |             |

| Bit1:    | PT0: Timer 0      |               |                 |            |                 |            |                  |             |

|          | This bit sets t   |               |                 | -          |                 |            |                  |             |

|          | 0: Timer 0 int    | 1 1           | •               | •          | priority order  | r <b>.</b> |                  |             |

|          | 1: Timer 0 int    | -             | U 1 V           |            |                 |            |                  |             |

| Bit0:    | PX0: Externa      | 1             | •               |            |                 |            |                  |             |

|          | This bit sets the |               |                 | 1          | -               |            |                  |             |

|          | 0: External In    | 1 1           | •               | •          | ult priority or | der.       |                  |             |

|          | 1: External In    | terrupt 0 set | to high prior   | ity level. |                 |            |                  |             |

## **Figure 12.10. IP: Interrupt Priority**

| R/W         | R/W                             | R/W            | R/W           | R/W           | R/W          | R/W                                     | R/W  | Reset Value |

|-------------|---------------------------------|----------------|---------------|---------------|--------------|-----------------------------------------|------|-------------|

| EXVLD       |                                 | EX7            | EX6           | EADC1         | ET4          | EADC0                                   | ET3  | 00000000    |

| Bit7        | Bit6                            | Bit5           | Bit4          | Bit3          | Bit2         | Bit1                                    | Bit0 | SFR Address |

|             |                                 |                |               |               |              |                                         |      | 0xE7        |

| Bit7:       | EVVI D. Eng                     | hla Erstannal  | Cleak Sau     | a Valid (VTI  | VID) Inton   | mat                                     |      |             |

| DII/.       | EXVLD: Ena<br>This bit sets the |                |               |               | vLD) Inter   | rupi.                                   |      |             |

|             | 0: Disable XT                   | -              |               | LD micrupi.   |              |                                         |      |             |

|             | 1: Enable inte                  |                | 1             | by the XTLV   | LD flag (OS  | SCXCN.7)                                |      |             |

| Bit6:       | ES1: Enable U                   |                |               |               | 22 mg (01    | , , , , , , , , , , , , , , , , , , , , |      |             |

|             | This bit sets the               |                | -             | 1 interrupt.  |              |                                         |      |             |

|             | 0: Disable UA                   | U              |               |               |              |                                         |      |             |

|             | 1: Enable UA                    |                |               |               |              |                                         |      |             |

| Bit5:       | EX7: Enable                     | 1              |               |               |              |                                         |      |             |

|             | This bit sets the               |                | -             | nterrupt 7.   |              |                                         |      |             |

|             | 0: Disable Ex                   | ternal Interru | ıpt 7.        | -             |              |                                         |      |             |

|             | 1: Enable inte                  | rrupt reques   | ts generated  | by the Extern | al Interrupt | 7 input pin.                            |      |             |

| Bit4:       | EX6: Enable                     | External Inte  | errupt 6.     |               |              |                                         |      |             |

|             | This bit sets the               | he masking o   | of External I | nterrupt 6.   |              |                                         |      |             |

|             | 0: Disable Ex                   | ternal Interru | ıpt 6.        |               |              |                                         |      |             |

|             | 1: Enable inte                  |                |               |               |              | 6 input pin.                            |      |             |

| Bit3:       | EADC1: Enal                     |                |               | -             |              |                                         |      |             |

|             | This bit sets the               |                |               |               | ersion inter | rupt.                                   |      |             |

|             | 0: Disable AI                   |                |               | -             |              |                                         |      |             |

|             |                                 | <b>1</b> 1     | 0             | by the ADC1   | End of Cor   | version Interr                          | upt. |             |

| Bit2:       | ET4: Enable                     |                | -             |               |              |                                         |      |             |

|             | This bit sets the               |                |               | 4 interrupt.  |              |                                         |      |             |

|             | 0: Disable Tir                  |                | L             |               | -            | _                                       |      |             |

| <b>D</b> 14 | 1: Enable inte                  |                | -             | •             | -            | .7).                                    |      |             |

| Bit1:       | EADC0: Enal                     |                |               |               |              |                                         |      |             |

|             | This bit sets the               | U              |               |               | ersion Inter | rupt.                                   |      |             |

|             | 0: Disable AL                   |                | 1             |               | а ·          | T, I, I                                 |      |             |

| D:40.       | 1: Enable inte                  |                |               | by the ADCO   | Conversion   | i interrupt.                            |      |             |

| Bit0:       | ET3: Enable 7                   |                | 1             | 2 intomat     |              |                                         |      |             |

|             | This bit sets the               |                |               | 5 interrupt.  |              |                                         |      |             |

|             | 0: Disable all                  |                |               | by the TE2 fl |              | <b>N</b> 7)                             |      |             |

|             | 1: Enable inte                  | mupt reques    | is generated  | by the 1F3 fl | ag (TMR3C    | .1 <b>N</b> ./).                        |      |             |

Figure 12.12. EIE2: Extended Interrupt Enable 2

| R/W            | R/W                            | R/W            | R/W            | R/W            | R/W           | R/W           | R/W            | Reset Value   |

|----------------|--------------------------------|----------------|----------------|----------------|---------------|---------------|----------------|---------------|

| SMOD0          | SSTAT0                         | Reserved       | SMOD1          | SSTAT1         | Reserved      | STOP          | IDLE           | 00000000      |

| Bit7           | Bit6                           | Bit5           | Bit4           | Bit3           | Bit2          | Bit1          | Bit0           | SFR Address:  |

|                |                                |                |                |                |               |               |                | 0x87          |

|                |                                |                |                |                |               |               |                |               |

| Bit7:          | SMOD0: UA                      |                |                |                |               |               |                |               |

|                | This bit enabl                 |                |                | -two function  | n of the UAR  | T0 baud rate  | e logic for co | onfigurations |

|                | described in t                 |                |                |                |               |               |                |               |

|                | 0: UARTO ba                    |                |                |                |               |               |                |               |

|                | 1: UART0 ba                    |                | •              |                |               |               |                |               |

| Bit6:          | SSTATO: UA                     |                |                |                |               |               |                |               |

|                | This bit contr                 |                |                |                | Ŭ             |               |                |               |

|                | 0: Reads/writ                  |                |                |                |               |               | 0              |               |

|                | 1: Reads/writ                  |                |                | s the Framing  | g Error (FEO) | , RX Overru   | in (RXOVO)     | ), and IX     |

| D:45.          | Collision (TX<br>Reserved. Res | · · ·          |                | :4- 0          |               |               |                |               |

| Bit5:<br>Bit4: | SMOD1: UA                      |                |                |                |               |               |                |               |

| Б114:          | This bit enabl                 |                |                |                | of the UAD    | T1 boud rote  | logic for a    | onfigurations |

|                | described in t                 |                | •              | -two function  | I OI IIIE UAK |               |                | Jingurations  |

|                | 0: UART1 ba                    |                |                | ablad          |               |               |                |               |

|                | 1: UART1 ba                    |                |                |                |               |               |                |               |

| Bit3:          | SSTAT1: UA                     |                |                |                |               |               |                |               |

| DIG.           | This bit contr                 |                |                |                | )1 bits in SC | ON1           |                |               |

|                | 0: Reads/writ                  |                |                |                |               |               | ng.            |               |

|                | 1: Reads/writ                  |                |                |                |               |               | -              | ), and TX     |

|                | Collision (TX                  |                |                | 2              | , ( /         | ,             | (              | ,,            |

| Bit2:          | Reserved. Re                   | ,              |                | ite 0.         |               |               |                |               |

| Bit1:          | STOP: STOP                     | Mode Select    | t.             |                |               |               |                |               |

|                | Writing a '1'                  | to this bit wi | ll place the ( | CIP-51 into S  | TOP mode.     | This bit will | always read    | l '0'.        |

|                | 1: CIP-51 for                  |                | -              |                |               |               | •              |               |

| Bit0:          | IDLE: IDLE                     | -              |                |                |               |               |                |               |

|                | Writing a '1'                  | to this bit wi | ll place the ( | CIP-51 into I  | DLE mode. 7   | This bit will | always read    | <b>'</b> 0'.  |

|                | 1: CIP-51 for                  | ced into idle  | mode. (Shut    | s off clock to | CPU, but cl   | ock to Time   | rs, Interrupt  | s, and all    |

|                | peripherals re                 | main active.   | )              |                |               |               |                |               |

|                |                                |                |                |                |               |               |                |               |

|                |                                |                |                |                |               |               |                |               |

Figure 12.15. PCON: Power Control

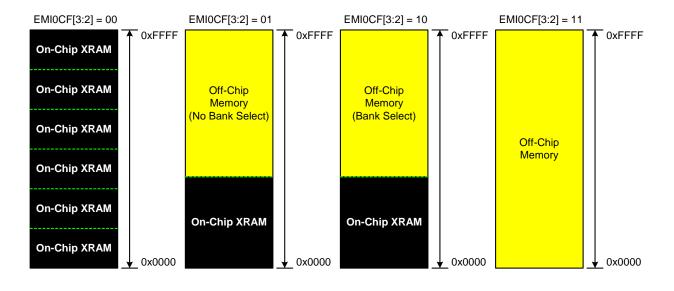

### **16.5.** Memory Mode Selection

The external data memory space can be configured in one of four modes, shown in Figure 16.5, based on the EMIF Mode bits in the EMIOCF register (Figure 16.2). These modes are summarized below. More information about the different modes can be found in Section "." on page 152.

### 16.5.1. Internal XRAM Only

When EMIOCF.[3:2] are set to '00', all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 4k boundaries. As an example, the addresses 0x1000 and 0x2000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMI0CN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

### 16.5.2. Split Mode without Bank Select

When EMIOCF.[3:2] are set to '01', the XRAM memory map is split into two areas, on-chip space and off-chip space.

- Effective addresses below the 4k boundary will access on-chip XRAM space.

- Effective addresses beyond the 4k boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is on-chip or offchip. The lower 8-bits of the Address Bus A[7:0] are driven as defined by R0 or R1. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate the upper address bits at will by setting the Port state directly. This behavior is in contrast with "Split Mode with Bank Select" described below.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or offchip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the offchip transaction.

### Figure 16.5. EMIF Operating Modes

.

| D/11/    | D /11/        | DAV            | D /11/                | D /W       | DAV     | D /11/ | D /11/ |              |

|----------|---------------|----------------|-----------------------|------------|---------|--------|--------|--------------|

| R/W      | R/W           | R/W            | R/W                   | R/W        | R/W     | R/W    | R/W    | Reset Value  |

| EAS1     | EAS0          | EWR3           | EWR2                  | EWR1       | EWR0    | EAH1   | EAH0   | 11111111     |

| Bit7     | Bit6          | Bit5           | Bit4                  | Bit3       | Bit2    | Bit1   | Bit0   | SFR Address: |

|          |               |                |                       |            |         |        |        | 0xA1         |

| Bits7-6: | EAS1-0: EMI   | F Address S    | etun Time B           | its        |         |        |        |              |

| Dits7 0. | 00: Address s |                | -                     |            |         |        |        |              |

|          | 01: Address s |                |                       |            |         |        |        |              |

|          | 10: Address s |                |                       |            |         |        |        |              |

|          | 11: Address s | 1              |                       | •          |         |        |        |              |

| Bits5-2: | EWR3-0: EM    | -              |                       | •          | l Bits. |        |        |              |

|          | 0000: /WR an  |                |                       |            |         |        |        |              |

|          | 0001: /WR an  | -              |                       | •          |         |        |        |              |

|          | 0010: /WR an  | -              |                       | •          |         |        |        |              |

|          | 0011: /WR an  | -              |                       | •          |         |        |        |              |

|          | 0100: /WR an  | d /RD pulse    | width = $5 S^{2}$     | YSCLK cycl | es.     |        |        |              |

|          | 0101: /WR an  | d /RD pulse    | width = $6 S$         | YSCLK cycl | es.     |        |        |              |

|          | 0110: /WR an  | d /RD pulse    | width $= 7 S^{2}$     | YSCLK cycl | es.     |        |        |              |

|          | 0111: /WR an  | d /RD pulse    | width $= 8 S^{2}$     | YSCLK cycl | es.     |        |        |              |

|          | 1000: /WR an  | d /RD pulse    | width = $9 S^{\circ}$ | YSCLK cycl | es.     |        |        |              |

|          | 1001: /WR an  | d /RD pulse    | width $= 10$ s        | SYSCLK cy  | cles.   |        |        |              |

|          | 1010: /WR an  | -              |                       | •          |         |        |        |              |

|          | 1011: /WR an  | -              |                       | •          |         |        |        |              |

|          | 1100: /WR an  | -              |                       | •          |         |        |        |              |

|          | 1101: /WR an  |                |                       |            |         |        |        |              |

|          | 1110: /WR an  |                |                       |            |         |        |        |              |

|          | 1111: /WR an  |                |                       |            | eles.   |        |        |              |

| Bits1-0: | EAH1-0: EM    |                |                       |            |         |        |        |              |

|          | 00: Address h |                | •                     |            |         |        |        |              |

|          | 01: Address h |                |                       |            |         |        |        |              |

|          | 10: Address h |                | •                     |            |         |        |        |              |

|          | 11: Address h | old time $= 3$ | SYSCLK cy             | cles.      |         |        |        |              |

## Figure 16.6. EMI0TC: External Memory Timing Control

to a Port pin without assigning RX0 as well. Each combination of enabled peripherals results in a unique device pinout.

All Port pins on Ports 0 through 3 that are not allocated by the Crossbar can be accessed as General-Purpose I/O (GPIO) pins by reading and writing the associated Port Data registers (See Figure 17.10, Figure 17.12, Figure 17.15, and Figure 17.17), a set of SFRs which are both byte- and bit-addressable. The output states of Port pins that are allocated by the Crossbar are controlled by the digital peripheral that is mapped to those pins. Writes to the Port Data registers (or associated Port bits) will have no effect on the states of these pins.

A Read of a Port Data register (or Port bit) will always return the logic state present at the pin itself, regardless of whether the Crossbar has allocated the pin for peripheral use or not. An exception to this occurs during the execution of a *read-modify-write* instruction (ANL, ORL, XRL, CPL, INC, DEC, DJNZ, JBC, CLR, SET, and the bitwise MOV operation). During the *read* cycle of the *read-modify-write* instruction, it is the contents of the Port Data register, not the state of the Port pins themselves, which is read.

Because the Crossbar registers affect the pinout of the peripherals of the device, they are typically configured in the initialization code of the system before the peripherals themselves are configured. Once configured, the Crossbar registers are typically left alone.

Once the Crossbar registers have been properly configured, the Crossbar is enabled by setting XBARE (XBR2.6) to a logic 1. Until XBARE is set to a logic 1, the output drivers on Ports 0 through 3 are explicitly disabled in order to prevent possible contention on the Port pins while the Crossbar registers and other registers which can affect the device pinout are being written.

The output drivers on Crossbar-assigned input signals (like RX0, for example) are explicitly disabled; thus the values of the Port Data registers and the PnMDOUT registers have no effect on the states of these pins.

### 17.1.2. Configuring the Output Modes of the Port Pins

The output drivers on Ports 0 through 3 remain disabled until the Crossbar is enabled by setting XBARE (XBR2.6) to a logic 1.

The output mode of each port pin can be configured as either Open-Drain or Push-Pull; the default state is Open-Drain. In the Push-Pull configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to GND, and writing a logic 1 will cause the Port pin to be driven to VDD. In the Open-Drain configuration, writing a logic 0 to the associated bit in the Port Data register will cause the Port pin to be driven to KDD. In the Open-Drain configuration, writing a logic 1 will cause the Port Data register will cause the Port pin to be driven to GND, and a logic 1 will cause the Port pin to assume a high-impedance state. The Open-Drain configuration is useful to prevent contention between devices in systems where the Port pin participates in a shared interconnection in which multiple outputs are connected to the same physical wire (like the SDA signal on an SMBus connection).

The output modes of the Port pins on Ports 0 through 3 are determined by the bits in the associated PnMDOUT registers (See Figure 17.11, Figure 17.14, Figure 17.16, and Figure 17.18). For example, a logic 1 in P3MDOUT.7 will configure the output mode of P3.7 to Push-Pull; a logic 0 in P3MDOUT.7 will configure the output mode of P3.7 to Open-Drain. All Port pins default to Open-Drain output.

The PnMDOUT registers control the output modes of the port pins regardless of whether the Crossbar has allocated the Port pin for a digital peripheral or not. The exceptions to this rule are: the Port pins connected to SDA, SCL, RX0 (if UART0 is in Mode 0), and RX1 (if UART1 is in Mode 0) are always configured as Open-Drain outputs, regardless of the settings of the associated bits in the PnMDOUT registers.

Port Data register will cause the Port pin to be driven to GND, and a logic 1 will cause the Port pin to assume a highimpedance state. The Open-Drain configuration is useful to prevent contention between devices in systems where the Port pin participates in a shared interconnection in which multiple outputs are connected to the same physical wire.

The output modes of the Port pins on Ports 4 through 7 are determined by the bits in the P74OUT register (see Figure 17.20). Each bit in P74OUT controls the output mode of a 4-bit bank of Port pins on Ports 4, 5, 6, and 7. A logic 1 in P74OUT.7 will configure the output modes of 4 most-significant bits of Port 7, P7.[7:4], to Push-Pull; a logic 0 in P74OUT.7 will configure the output modes of P7.[7:4] to Open-Drain.

### 17.2.3. Configuring Port Pins as Digital Inputs

A Port pin is configured as a digital input by setting its output mode to "Open-Drain" and writing a logic 1 to the associated bit in the Port Data register. For example, P7.7 is configured as a digital input by setting P74OUT.7 to a logic 0 and P7.7 to a logic 1.

### 17.2.4. Weak Pull-ups

By default, each Port pin has an internal weak pull-up device enabled which provides a resistive connection (about 100 k $\Omega$ ) between the pin and VDD. The weak pull-up devices can be globally disabled by writing a logic 1 to the Weak Pull-up Disable bit, (WEAKPUD, XBR2.7). The weak pull-up is automatically deactivated on any pin that is driving a logic 0; that is, an output pin will not contend with its own pull-up device.

### **17.2.5. External Memory Interface**

If the External Memory Interface (EMIF) is enabled on the High ports (Ports 4 through 7), EMIFLE (XBR2.1) should be set to a logic 0.

If the External Memory Interface is enabled on the High ports and an off-chip MOVX operation occurs, the External Memory Interface will control the output states of the affected Port pins during the execution phase of the MOVX instruction, regardless of the settings of the Port Data registers. The output configuration of the Port pins is not affected by the EMIF operation, except that Read operations will explicitly disable the output drivers on the Data Bus during the MOVX execution. See Section "16. EXTERNAL DATA MEMORY INTERFACE AND ON-CHIP XRAM" on page 145 for more information about the External Memory Interface.

| R/W   | R/W             | R/W          | R/W         | R/W  | R/W  | R/W  | R/W  | Reset Value  |

|-------|-----------------|--------------|-------------|------|------|------|------|--------------|

| P7H   | P7L             | P6H          | P6L         | P5H  | P5L  | P4H  | P4L  | 00000000     |

| Bit7  | Bit6            | Bit5         | Bit4        | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|       |                 |              |             |      |      |      |      | 0xB5         |

| Bit7: | P7H: Port7 Ou   |              | 0           |      |      |      |      |              |

|       | 0: P7.[7:4] con | 0            | 1           |      |      |      |      |              |

|       | 1: P7.[7:4] con | 0            |             |      |      |      |      |              |

| Bit6: | P7L: Port7 Ou   | •            |             |      |      |      |      |              |

|       | 0: P7.[3:0] con | 0            |             |      |      |      |      |              |

|       | 1: P7.[3:0] con | 0            |             |      |      |      |      |              |

| Bit5: | P6H: Port6 Ou   | 1            | 0           |      |      |      |      |              |

|       | 0: P6.[7:4] con | 0            | 1           |      |      |      |      |              |

|       | 1: P6.[7:4] con | 0            |             |      |      |      |      |              |

| Bit4: | P6L: Port6 Ou   | •            |             |      |      |      |      |              |

|       | 0: P6.[3:0] con | -            | -           |      |      |      |      |              |

|       | 1: P6.[3:0] con | 0            |             |      |      |      |      |              |

| Bit3: | P5H: Port5 Ou   | 1            | 0           |      |      |      |      |              |

|       | 0: P5.[7:4] con | -            | -           |      |      |      |      |              |

|       | 1: P5.[7:4] con | 0            |             |      |      |      |      |              |

| Bit2: | P5L: Port5 Ou   | •            |             |      |      |      |      |              |

|       | 0: P5.[3:0] con | 0            | 1           |      |      |      |      |              |

|       | 1: P5.[3:0] con | figured as H | ush-Pull.   |      |      |      |      |              |

| Bit1: | P4H: Port4 Ou   | tput Mode 1  | High Nibble | Bit. |      |      |      |              |

|       | 0: P4.[7:4] con | figured as ( | Open-Drain. |      |      |      |      |              |

|       | 1: P4.[7:4] con | figured as H | ush-Pull.   |      |      |      |      |              |

| Bit0: | P4L: Port4 Ou   | tput Mode I  | low Nibble  | Bit. |      |      |      |              |

|       | 0: P4.[3:0] con | figured as ( | Open-Drain. |      |      |      |      |              |

|       | 1: P4.[3:0] con | figured as H | ush-Pull.   |      |      |      |      |              |

## Figure 17.20. P74OUT: Ports 7 - 4 Output Mode Register

### **19.4.** SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following section.

| Figure 19.5 | SPI0CFG: S | SPI0 Config | uration Regis | ter |

|-------------|------------|-------------|---------------|-----|

| <b>.</b>    |            |             |               |     |

| R/W<br>CKPHA | R/W<br>CKPOL                                  | R<br>BC2                    | R<br>BC1         | R<br>BC0      | R/W<br>SPIFRS2 | R/W<br>SPIFRS1 | R/W<br>SPIFRS0 | Reset Value 00000111 |

|--------------|-----------------------------------------------|-----------------------------|------------------|---------------|----------------|----------------|----------------|----------------------|

| Bit7         | Bit6                                          | Bit5                        | Bit4             | Bit3          | Bit2           | Bit1           | Bit0           | SFR Address<br>0x9A  |

| Bit7:        | CKPHA: SPI                                    | 0 Clock Pha                 | lse.             |               |                |                |                |                      |

|              | This bit contr                                |                             |                  |               |                |                |                |                      |

|              | 0: Data samp                                  |                             |                  |               |                |                |                |                      |

|              | 1: Data samp                                  |                             | -                | •             |                |                |                |                      |

| Bit6:        | CKPOL: SPI                                    |                             |                  | 1             |                |                |                |                      |

|              | This bit contr                                |                             |                  | ty.           |                |                |                |                      |

|              | 0: SCK line l                                 | ow in idle st               | ate.             |               |                |                |                |                      |

|              | 1: SCK line h                                 | igh in idle s               | tate.            |               |                |                |                |                      |

| Bits5-3:     | BC2-BC0: SI                                   |                             |                  |               |                |                |                |                      |

|              | Indicates whi                                 | ch of the up                | to 8 bits of the | he SPI0 word  | have been t    | ransmitted.    |                |                      |

|              |                                               | BC2-BC0                     |                  | BIT Transm    | itted          |                |                |                      |

|              | 0                                             | 0                           | 0                | Bit 0 (LSI    |                |                |                |                      |

|              | 0                                             | 0                           | 1                | Bit 1         |                |                |                |                      |

|              | 0                                             | 1                           | 0                | Bit 2         |                |                |                |                      |

|              | 0                                             | 1                           | 1                | Bit 3         |                |                |                |                      |

|              | 1                                             | 0                           | 0                | Bit 4         |                |                |                |                      |

|              | 1                                             | 0                           | 1                | Bit 5         |                |                |                |                      |

|              | 1                                             | 1                           | 0                | Bit 6         |                |                |                |                      |

|              | 1                                             | 1                           | 1                | Bit 7 (MS     | B)             |                |                |                      |

| Bits2-0:     | SPIFRS2-SP<br>These three b<br>transfer in ma | its determin<br>aster mode. | e the number     | ored in slave | mode.          | he SPI0 shift  | t register dur | ing a data           |

|              |                                               | SPIFRS                      |                  | Bits Shifte   | d              |                |                |                      |

|              | 0                                             | 0                           | 0                | 1             |                |                |                |                      |

|              | 0                                             | 0                           | 1                | 2             |                |                |                |                      |

|              | 0                                             | 1                           | 0                | 3             |                |                |                |                      |

|              | 0                                             | 1                           | 1                | 4             |                |                |                |                      |

|              | 1                                             | 0                           | 0                | 5             |                |                |                |                      |

|              | 1                                             | 0                           | 1                | 6             |                |                |                |                      |

|              | 1                                             | 1                           | 0                | 7 8           |                |                |                |                      |

|              |                                               | 1                           | 1                | X             |                |                |                |                      |

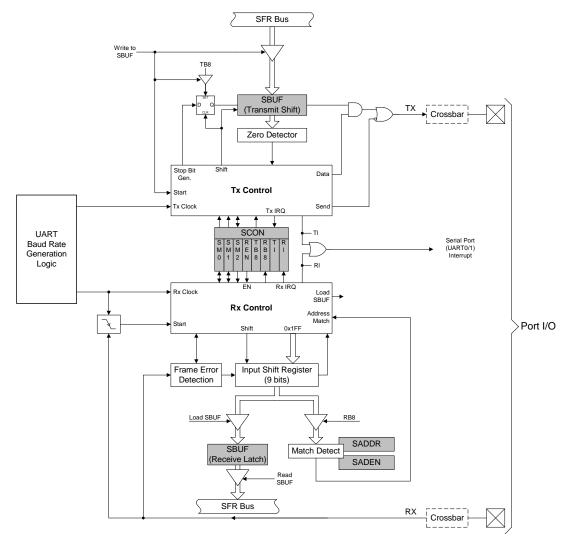

## **21. UART1**

UART1 is an enhanced serial port with frame error detection and address recognition hardware. UART1 may operate in full-duplex asynchronous or half-duplex synchronous modes, and mutiproccessor communication is fully supported. Receive data is buffered in a holding register, allowing UART1 to start reception of a second incoming data byte before software has finished reading the previous data byte. A Receive Overrun bit indicates when new received data is latched into the receive buffer before the previous received byte is read.

UART1 is accessed via its associated SFRs, Serial Control (SCON1) and Serial Data Buffer (SBUF1). The single SBUF1 location provides access to both transmit and receive registers. Reads access the Receive register and writes access the Transmit register automatically.

UART1 may be operated in polled or interrupt mode. UART1 has two sources of interrupts: a Transmit Interrupt flag, TI1 (SCON1.1) set when transmission of a data byte is complete, and a Receive Interrupt flag, RI1 (SCON1.0) set when reception of a data byte is complete. UART1 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine; they must be cleared manually by software. This allows software to determine the cause of the UART1 interrupt (transmit complete or receive complete).

| Oscillator frequency (MHz) | <b>Divide Factor</b> | Timer 1 Load Value* | Resulting Baud Rate (Hz)** |

|----------------------------|----------------------|---------------------|----------------------------|

| 25.0                       | 434                  | 0xE5                | 57600 (57870)              |

| 25.0                       | 868                  | 0xCA                | 28800                      |

| 24.576                     | 320                  | 0xEC                | 76800                      |

| 24.576                     | 848                  | 0xCB                | 28800 (28921)              |

| 24.0                       | 208                  | 0XF3                | 115200 (115384)            |

| 24.0                       | 833                  | 0xCC                | 28800 (28846)              |

| 23.592                     | 205                  | 0xF3                | 115200 (113423)            |

| 23.592                     | 819                  | 0xCD                | 28800 (28911)              |

| 22.1184                    | 192                  | 0xF4                | 115200                     |

| 22.1184                    | 768                  | 0xD0                | 28800                      |

| 18.432                     | 160                  | 0xF6                | 115200                     |

| 18.432                     | 640                  | 0xD8                | 28800                      |

| 16.5888                    | 144                  | 0xF7                | 115200                     |

| 16.5888                    | 576                  | 0xDC                | 28800                      |

| 14.7456                    | 128                  | 0xF8                | 115200                     |

| 14.7456                    | 512                  | 0xE0                | 28800                      |

| 12.9024                    | 112                  | 0xF9                | 115200                     |

| 12.9024                    | 448                  | 0xE4                | 28800                      |

| 11.0592                    | 96                   | 0xFA                | 115200                     |

| 11.0592                    | 348                  | 0xE8                | 28800                      |

| 9.216                      | 80                   | 0xFB                | 115200                     |

| 9.216                      | 320                  | 0xEC                | 28800                      |

| 7.3728                     | 64                   | 0xFC                | 115200                     |

| 7.3728                     | 256                  | 0xF0                | 28800                      |

| 5.5296                     | 48                   | 0xFD                | 115200                     |

| 5.5296                     | 192                  | 0xF4                | 28800                      |

| 3.6864                     | 32                   | 0xFE                | 115200                     |

| 3.6864                     | 128                  | 0xF8                | 28800                      |

| 1.8432                     | 16                   | 0xFF                | 115200                     |

| 1.8432                     | 64                   | 0xFC                | 28800                      |

**Table 21.2. Oscillator Frequencies for Standard Baud Rates**

\* Assumes SMOD1=1 and T1M=1. \*\* Numbers in parenthesis show the actual baud rate.

#### 22.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. The TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter value in TL0 is reloaded from TH0. If enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0. Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0.

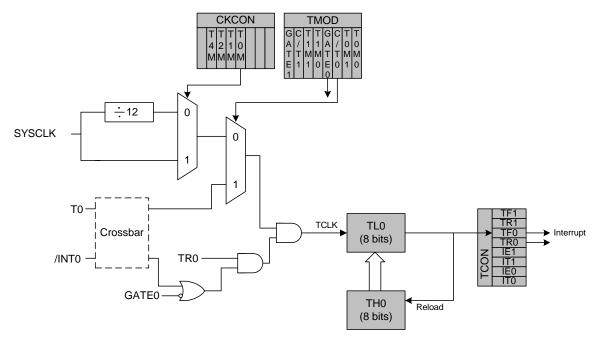

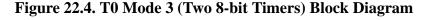

### 22.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

Timer 0 and Timer 1 behave differently in Mode 3. Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. It can use either the system clock or an external input signal as its timebase. The timer in the TH0 register is restricted to a timer function sourced by the system clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3, so with Timer 0 in Mode 3, Timer 1 can be turned off and on by switching it into and out of its Mode 3. When Timer 0 is in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate the baud clock for UART0 and/or UART1. Refer to **Section "20. UART0" on page 205** and **Section "21. UART1" on page 215** for information on configuring Timer 1 for baud rate generation.

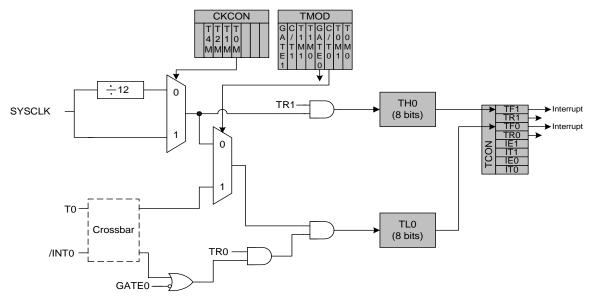

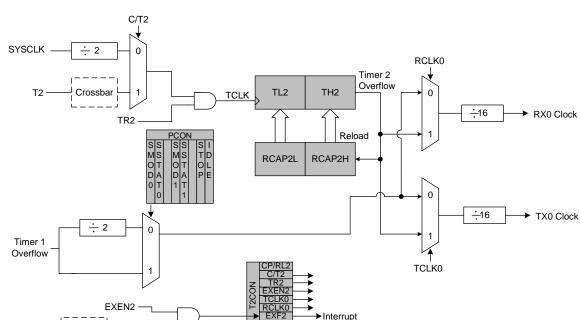

#### 22.1.3. Mode 2: Baud Rate Generator

Timer 2 can be used as a baud rate generator for UART0 when UART0 is operated in modes 1 or 3 (refer to Section "20.1. UART0 Operational Modes" on page 206 for more information on the UART0 operational modes). In Baud Rate Generator mode, Timer 2 works similarly to the auto-reload mode. On overflow, the 16-bit value held in the two capture registers (RCAP2H, RCAP2L) is automatically loaded into the counter/timer register. However, the TF2 overflow flag is not set and no interrupt is generated. Instead, the overflow event is used as the input to the UART's shift clock. Timer 2 overflows can be selected to generate baud rates for transmit and/or receive independently.

The Baud Rate Generator mode is selected by setting RCLK0 (T2CON.5) and/or TCLK0 (T2CON.2) to '1'. When RCLK0 or TCLK0 is set to logic 1, Timer 2 operates in the auto-reload mode regardless of the state of the CP/RL2 bit. Note that in Baud Rate Generator mode, the Timer 2 timebase is the system clock divided by two. When selected as the UART0 baud clock source, Timer 2 defines the UART0 baud rate as follows:

*Baud Rate* = *SYSCLK* / ((65536 - [*RCAP2H*, *RCAP2L*]) \* 32)

If a different time base is required, setting the C/T2 bit to logic 1 will allow the timebase to be derived from the external input pin T2. In this case, the baud rate for the UART is calculated as:

*Baud Rate* =  $F_{CLK}$  / ( (65536 - [*RCAP2H*, *RCAP2L*] ) \* 16)

Where  $F_{CLK}$  is the frequency of the signal (TCLK) supplied to Timer 2 and [RCAP2H, RCAP2L] is the 16-bit value held in the capture registers.

As explained above, in Baud Rate Generator mode, Timer 2 does not set the TF2 overflow flag and therefore cannot generate an interrupt. However, if EXEN2 is set to logic 1, a high-to-low transition on the T2EX input pin will set the EXF2 flag and a Timer 2 interrupt will occur if enabled. Therefore, the T2EX input may be used as an additional external interrupt source.

Figure 22.13. T2 Mode 2 Block Diagram

T2FX

Crossbar

## Figure 24.4. FLASHADR: JTAG Flash Address Register

|                                                                                                                                                                                                       | 1                                         |  | [ |  | [ | [ | [ | 1 |  |  |  |  | [ | 1    | Reset Value |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|---|--|---|---|---|---|--|--|--|--|---|------|-------------|

| D:415                                                                                                                                                                                                 |                                           |  |   |  |   |   |   |   |  |  |  |  |   | D:40 | 0x0000      |

| Bit15                                                                                                                                                                                                 |                                           |  |   |  |   |   |   |   |  |  |  |  |   | Bit0 |             |

|                                                                                                                                                                                                       |                                           |  |   |  |   |   |   |   |  |  |  |  |   |      |             |

| This register holds the address for all JTAG Flash read, write, and erase operations. This register autoincrements after each read or write, regardless of whether the operation succeeded or failed. |                                           |  |   |  |   |   |   |   |  |  |  |  |   |      |             |

| Bits15                                                                                                                                                                                                | Bits15-0: Flash Operation 16-bit Address. |  |   |  |   |   |   |   |  |  |  |  |   |      |             |

## Figure 24.5. FLASHDAT: JTAG Flash Data Register

|                       |                                                                                                                        |               |           | •         |            | •          | •         |      | Reset Value |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|---------------|-----------|-----------|------------|------------|-----------|------|-------------|--|--|--|

|                       |                                                                                                                        |               |           |           |            |            |           |      | 0000000000  |  |  |  |

| Bit9                  |                                                                                                                        |               |           |           |            |            |           | Bit0 | _           |  |  |  |

|                       |                                                                                                                        |               |           |           |            |            |           |      |             |  |  |  |

|                       |                                                                                                                        |               |           |           |            |            |           |      |             |  |  |  |

| This regis            | ster is used to read                                                                                                   | d or write da | ta to the | Flash men | nory acros | ss the JTA | G interfa | ce.  |             |  |  |  |

| <b>D</b> : 0 <b>0</b> |                                                                                                                        |               |           |           |            |            |           |      |             |  |  |  |

| Bits9-2:              | DATA7-0: Flash Data Byte.                                                                                              |               |           |           |            |            |           |      |             |  |  |  |

| Bit1:                 | FAIL: Flash Fail Bit.                                                                                                  |               |           |           |            |            |           |      |             |  |  |  |

|                       | 0: Previous Flash memory operation was successful.                                                                     |               |           |           |            |            |           |      |             |  |  |  |

|                       | 1: Previous Flash memory operation failed. Usually indicates the associated memory location                            |               |           |           |            |            |           |      |             |  |  |  |

|                       | was locked.                                                                                                            |               |           |           |            |            |           |      |             |  |  |  |

| Bit0:                 | BUSY: Flash Busy Bit.                                                                                                  |               |           |           |            |            |           |      |             |  |  |  |

| Bito.                 | 0: Flash interface logic is not busy.                                                                                  |               |           |           |            |            |           |      |             |  |  |  |

|                       |                                                                                                                        |               |           |           |            |            |           |      |             |  |  |  |

|                       | 1: Flash interface logic is processing a request. Reads or writes while $BUSY = 1$ will not initiate another operation |               |           |           |            |            |           |      |             |  |  |  |

|                       | initiate another                                                                                                       | operation     |           |           |            |            |           |      |             |  |  |  |

|                       |                                                                                                                        |               |           |           |            |            |           |      |             |  |  |  |

|                       |                                                                                                                        |               |           |           |            |            |           |      |             |  |  |  |