Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

Application enecific microcontrollers are engineered to

| Details                 |                                                                          |

|-------------------------|--------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                 |

| Applications            | Battery Monitor                                                          |

| Core Processor          | S12                                                                      |

| Program Memory Type     | FLASH (128kB)                                                            |

| Controller Series       | HCS12                                                                    |

| RAM Size                | 6K x 8                                                                   |

| Interface               | LIN, SCI, SPI                                                            |

| Number of I/O           | 8                                                                        |

| Voltage - Supply        | 2.25V ~ 5.5V                                                             |

| Operating Temperature   | -40°C ~ 105°C                                                            |

| Mounting Type           | Surface Mount                                                            |

| Package / Case          | 48-VFQFN Exposed Pad                                                     |

| Supplier Device Package | 48-QFN-EP (7x7)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/mm912j637av1epr2 |

|                         |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 |      | ering information                                     |      |

|---|------|-------------------------------------------------------|------|

| 2 | Part | Identification                                        |      |

|   | 2.1  | Description                                           | 2    |

|   | 2.2  | Format and Examples                                   | 2    |

|   |      | Fields                                                |      |

| 3 |      | Assignment                                            |      |

| J |      |                                                       |      |

|   | 3.1  | MM912_637 Pin Description                             |      |

|   |      | Recommended External Components                       |      |

|   |      | Pin Structure                                         |      |

| 4 |      | trical Characteristics                                |      |

|   | 4.1  | General                                               |      |

|   | 4.2  | Absolute Maximum Ratings                              | . 13 |

|   | 4.3  | Operating Conditions                                  |      |

|   | 4.4  | Supply Currents                                       |      |

|   | 4.5  | Static Electrical Characteristics                     |      |

|   |      | Dynamic Electrical Characteristics                    |      |

|   | 4.6  |                                                       |      |

|   | 4.7  | Thermal Protection Characteristics                    |      |

|   | 4.8  | Electromagnetic Compatibility (EMC)                   |      |

| 5 | Fund | ctional Description and Application Information       |      |

|   | 5.1  | MM912_637 - Analog Die Overview                       |      |

|   | 5.2  | Analog Die - Power, Clock and Resets - PCR            | . 63 |

|   | 5.3  | Interrupt Module - IRQ                                | . 87 |

|   | 5.4  | Current Measurement - ISENSE                          |      |

|   | 5.5  | Voltage Measurement - VSENSE                          |      |

|   | 5.6  | Temperature Measurement - TSENSE                      | . 07 |

|   |      |                                                       |      |

|   | 5.7  | Channel Acquisition                                   |      |

|   |      | Window Watchdog                                       |      |

|   | 5.9  | Basic Timer Module - TIM (TIM16B4C)                   |      |

|   | 5.10 | General Purpose I/O - GPIO                            | 163  |

|   | 5.11 | LIN                                                   | 174  |

|   | 5.12 | Serial Communication Interface (S08SCIV4)             | 181  |

|   |      | Life Time Counter (LTC)                               |      |

|   |      | Die to Die Interface - Target                         |      |

|   |      | Embedded Microcontroller - Overview                   |      |

|   |      | MCU - Port Integration Module (9S12I128PIMV1)         |      |

|   |      |                                                       |      |

|   |      | MCU - Interrupt Module (S12SINTV1)                    |      |

|   | 5.18 | Memory Map Control (S12PMMCV1)                        | 224  |

|   |      | MCU - Debug Module (S12SDBG)                          |      |

|   |      | MCU - Security (S12XS9SECV2)                          |      |

|   | 5.21 | Background Debug Module (S12SBDMV1)                   | 276  |

|   | 5.22 | S12 Clock, Reset, and Power Management Unit (S12CPMU) | 293  |

|   | 5.23 | MCU - Serial Peripheral Interface (S12SPIV5)          | 325  |

|   |      | 128 kByte Flash Module (S12FTMRC128K1V1)              | 345  |

|   |      | MCU - Die-to-Die Initiator (D2DIV1)                   | 383  |

| 6 |      | 012_637 - Trimming                                    |      |

| 6 |      | _                                                     | 395  |

|   | 6.1  | Introduction                                          | 395  |

|   | 6.2  | IFR Trimming Content and Location                     | 395  |

|   | 6.3  | Memory Map and Registers                              | 399  |

| 7 | Pack | kaging                                                | 405  |

|   | 7.1  | Package dimensions                                    | 405  |

| 8 | Revi | sion History                                          | 412  |

## Table 4. MM912\_637 Pin Description

| Pin# | Pin Name | Formal Name                           | Description                                                                                                                                                                                                                                                                                                                  |

|------|----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40   | TCLK     | Test Clock Input                      | Test mode clock input pin for Test mode only. This pin must be grounded in user mode.                                                                                                                                                                                                                                        |

| 41   | GNDSUB   | Substrate Ground                      | Substrate ground connection to improve EMC behavior.                                                                                                                                                                                                                                                                         |

| 42   | VDDL     | Low Power Voltage<br>Regulator Output | 2.5 V low power voltage regulator output pin. See Section 5.2, "Analog Die - Power, Clock and Resets - PCR".                                                                                                                                                                                                                 |

| 43   | TEST_A   | Test Mode                             | Analog die Test mode pin for Test mode only. This pin must be grounded in user mode.                                                                                                                                                                                                                                         |

| 44   | DGND     | Digital Ground                        | This pin is the device digital ground connection. See Section 5.2, "Analog Die - Power, Clock and Resets - PCR".                                                                                                                                                                                                             |

| 45   | RESET_A  | Reset I/O                             | Reset output pin of the analog die. Active low signal with internal pull-up. V <sub>DDX</sub> based. See Section 5.2, "Analog Die - Power, Clock and Resets - PCR".                                                                                                                                                          |

| 46   | RESET    | MCU Reset                             | Bidirectional reset I/O pin of the MCU die. Active low signal with internal pull-up. V <sub>DDRX</sub> based. See Section 5.2, "Analog Die - Power, Clock and Resets - PCR".                                                                                                                                                 |

| 47   | BKGD     | MCU Background Debug and Mode         | The BKGD/MODC pin is used as a pseudo-open-drain pin for the background debug communication. It is used as an MCU operating mode select pin during reset. The state of this pin is latched to the MODC bit at the rising edge of RESET. The BKGD pin has a pull-up device. See Section 5.19, "MCU - Debug Module (S12SDBG)". |

| 48   | PA7      | MCU PA7                               | General purpose port A input or output pin 7. See Section 5.16, "MCU - Port Integration Module (9S12I128PIMV1)".                                                                                                                                                                                                             |

NOTE: Not defined

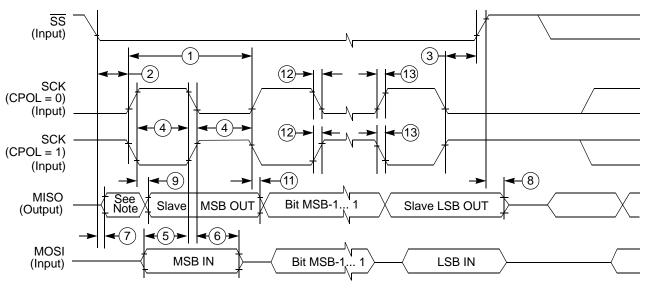

Figure 11. SPI Slave Timing (CPHA = 1)

The timing characteristics for slave mode are listed in Table 46.

**Table 46. SPI Slave Mode Timing Characteristics**

| Num | С | Characteristic                          | Symbol            | Min | Тур | Max                                         | Unit             |

|-----|---|-----------------------------------------|-------------------|-----|-----|---------------------------------------------|------------------|

| 1   | D | SCK Frequency                           | f <sub>SCK</sub>  | DC  | _   | 1/4                                         | f <sub>BUS</sub> |

| 1   | D | SCK Period                              | t <sub>SCK</sub>  | 4.0 | _   | ∞                                           | f <sub>BUS</sub> |

| 2   | D | Enable Lead Time                        | t <sub>LEAD</sub> | 4.0 | _   | _                                           | f <sub>BUS</sub> |

| 3   | D | Enable Lag Time                         | t <sub>LAG</sub>  | 4.0 | _   | _                                           | f <sub>BUS</sub> |

| 4   | D | Clock (SCK) High or Low Time            | t <sub>WSCK</sub> | 4.0 | _   | _                                           | f <sub>BUS</sub> |

| 5   | D | Data Setup Time (inputs)                | t <sub>SU</sub>   | 8.0 | _   | _                                           | ns               |

| 6   | D | Data Hold Time (inputs)                 | t <sub>HI</sub>   | 8.0 | _   | _                                           | ns               |

| 7   | D | Slave Access Time (time to data active) | t <sub>A</sub>    | _   | _   | 20                                          | ns               |

| 8   | D | Slave MISO Disable Time                 | t <sub>DIS</sub>  | _   | _   | 22                                          | ns               |

| 9   | D | Data Valid After SCK Edge               | t <sub>VSCK</sub> | _   | _   | 29 + 0.5 · t <sub>BUS</sub> (63)            | ns               |

| 10  | D | Data Valid After SS Fall                | t <sub>VSS</sub>  | _   | _   | 29 + 0.5 · t <sub>BUS</sub> <sup>(63)</sup> | ns               |

| 11  | D | Data Hold Time (outputs)                | t <sub>HO</sub>   | 20  | _   | _                                           | ns               |

| 12  | D | Rise and Fall Time Inputs               | t <sub>RFI</sub>  | _   | _   | 8.0                                         | ns               |

| 13  | D | Rise and Fall Time Outputs              | t <sub>RFO</sub>  | _   | _   | 8.0                                         | ns               |

Notes

$63.0.5\ t_{BUS}$  added due to internal synchronization delay

# 5 Functional Description and Application Information

This chapter describes the MM912\_637 dual die device functions on a block by block base. The following symbols are shown on all module cover pages to distinguish between the module location being the MCU die or the analog die:

The documented module is physically located on the Analog die. This applies to Section 5.1, "MM912\_637 - Analog Die Overview" through Section 5.14, "Die to Die Interface - Target".

The documented module is physically located on the Microcontroller die. This applies to Section 5.1, "MM912\_637 - Analog Die Overview" through Section 5.25, "MCU - Die-to-Die Initiator (D2DIV1)".

Sections concerning both die or the complete device will not have a specific indication (e.g. Section 6, "MM912\_637 - Trimming").

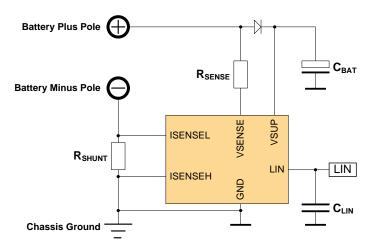

#### 5.0.1 Introduction

Many types of electronic control units (ECUs) are connected to and supplied from the main car battery in modern cars. Depending on the cars mode of operation (drive, start, stop, standby), the battery must deliver different currents to the different ECUs. The vehicle power management has several sub-functions, like control of the set-point value of the power generator, dynamic load management during drive, start, stop, and standby mode.

The Application Specific Integrated Circuit (ASIC) allows for two application circuits, depending on whether the bias current of the MM912\_637 itself shall be included into the current measurement.

Figure 12. Typical IBS Application (Device GND = Chassis GND)

## **Functional Description and Application Information**

Table 63. Analog die Registers - 0x0200-0x02FF D2D Blocking Access (D2DI) 2 of 3/ 0x0300-0x03FF D2D Non Blocking Access (D2DI) 3 of 3

| Offset <sup>(71)</sup> | Name                                                               |   | 15<br>7     | 14<br>6   | 13<br>5 | 12<br>4        | 11<br>3       | 10<br>2 | 9<br>1   | 8<br>0 |  |  |

|------------------------|--------------------------------------------------------------------|---|-------------|-----------|---------|----------------|---------------|---------|----------|--------|--|--|

| 0,406                  | LPF_A11 (hi)                                                       | R |             |           |         |                |               |         |          |        |  |  |

| 0x96                   | A11 filter coefficient                                             | W |             | A11[15:0] |         |                |               |         |          |        |  |  |

| 007                    | LPF_A11 (lo)                                                       | R |             |           |         | AII            | 15.0]         |         |          |        |  |  |

| 0x97                   | A11 filter coefficient                                             | W |             |           |         |                |               |         |          |        |  |  |

| 0,00                   | LPF_A12 (hi)                                                       | R |             |           |         |                |               |         |          |        |  |  |

| 0x98                   | A12 filter coefficient                                             | W |             |           |         | A 4 O          | 4.5.01        |         |          |        |  |  |

| 0,400                  | LPF_A12 (lo)                                                       | R |             |           |         | AIZ            | [15:0]        |         |          |        |  |  |

| 0x99                   | A12 filter coefficient                                             | W |             |           |         |                |               |         |          |        |  |  |

| 0,04                   | LPF_A13 (hi)                                                       | R |             |           |         |                |               |         |          |        |  |  |

| 0x9A                   | A13 filter coefficient                                             | W |             |           |         | A 4 2 F        | 45.01         |         |          |        |  |  |

| 0,,00                  | LPF_A13 (lo)                                                       | R |             |           |         | AIS            | [15:0]        |         |          |        |  |  |

| 0x9B                   | A13 filter coefficient                                             | W |             |           |         |                |               |         |          |        |  |  |

| 0,,00                  | LPF_A14 (hi)                                                       | R |             |           |         |                |               |         |          |        |  |  |

| UX9C                   | 0x9C  A14 filter coefficient  LPF_A14 (lo)  A14 filter coefficient |   |             |           |         | A 4 4 I        | 45.01         |         |          |        |  |  |

| 00D                    |                                                                    |   |             |           |         | A14[           | [15:0]        |         |          |        |  |  |

| UX9D                   |                                                                    |   |             |           |         |                |               |         |          |        |  |  |

| 005                    | LPF_A15 (hi)                                                       | R |             |           |         |                |               |         |          |        |  |  |

| 0x9E                   | A15 filter coefficient                                             | W |             |           |         | A 4 5          | 45.01         |         |          |        |  |  |

| 0.05                   | 0x9F                                                               |   | A15[15:0]   |           |         |                |               |         |          |        |  |  |

| 0x9F                   |                                                                    |   |             |           |         |                |               |         |          |        |  |  |

|                        |                                                                    | R | 0           | 0         | 0       | 0              | 0             | 0       |          | 0      |  |  |

| 040                    | COMP_CTL                                                           | W | BGCA        | _M[1:0]   | PGAZM   | PGAOM          | DIAGVM        | DIAGIM  |          | CALIEM |  |  |

| 0xA0                   | Compensation control register                                      | R | DOO         | 1.[4.0]   | DCA7    | DCAO           | DIACV         | DIACI   |          | CALIE  |  |  |

|                        |                                                                    | W | BGCF        | \L[1:0]   | PGAZ    | PGAO           | DIAGV         | DIAGI   |          |        |  |  |

| 040                    | COMP_SR                                                            | R | 0           | BGRF      | 0       | PGAOF          | 0             | 0       | 0        | CALF   |  |  |

| 0xA2                   | Compensation status register                                       | W |             | <u>I</u>  | 1       | Write 1 will c | lear the flag | S       | <u>I</u> |        |  |  |

| 040                    | COMP_TF                                                            | R | 0           | 0         | 0       | 0              | 0             |         | TME[0.0] |        |  |  |

| 0xA3                   | Temperature filtering period                                       | W |             |           |         |                |               | -       | TMF[2:0] |        |  |  |

|                        |                                                                    | R |             |           |         |                |               |         |          |        |  |  |

| 044                    | COMP_TMAX                                                          | W |             |           |         | TO 144         | V[4 F 0]      |         |          |        |  |  |

| 0xA4                   | Max temp before recalibration                                      | R | TCMAX[15:0] |           |         |                |               |         |          |        |  |  |

|                        |                                                                    | W |             |           |         |                |               |         |          |        |  |  |

|                        |                                                                    | R |             |           |         |                |               |         |          |        |  |  |

|                        | COMP_TMIN                                                          | W |             |           |         |                |               |         |          |        |  |  |

| 0xA6                   | Min temp before recalibration                                      | R |             |           |         | ICMI           | N[15:0]       |         |          |        |  |  |

|                        |                                                                    | W |             |           |         |                |               |         |          |        |  |  |

| 040                    | D                                                                  | R | 0           | 0         | 0       | 0              | 0             | 0       | 0        | 0      |  |  |

| 0xA8                   | Reserved                                                           | W |             |           |         |                |               |         |          |        |  |  |

| 0.15                   |                                                                    | R | 0           | 0         | 0       | 0              | 0             | 0       | 0        | 0      |  |  |

| 0xA9                   | Reserved                                                           | W |             |           |         |                |               |         |          |        |  |  |

|                        | COMP_VO                                                            | R |             |           | 1       |                | N7 01         |         |          |        |  |  |

| 0xAA                   | Offset voltage compensation                                        | W |             |           |         | VOC            | [7:0]         |         |          |        |  |  |

Table 97. Interrupt Mask Register (INT\_MSK (hi)) - Register Field Descriptions

| Field     | Description                                                                             |

|-----------|-----------------------------------------------------------------------------------------|

| 7<br>TOVM | Timer overflow interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled              |

| 6<br>CH3M | Timer channel 3 interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled             |

| 5<br>CH2M | Timer channel 2 interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled             |

| 4<br>CH1M | Timer channel 1 interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled             |

| 3<br>CH0M | Timer channel 1 interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled             |

| 2<br>LTIM | LIN driver over-temperature interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled |

| 1<br>HTIM | High temperature interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled            |

| 0<br>UVIM | Under-voltage interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled               |

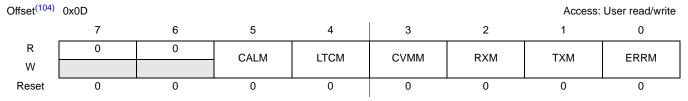

## 5.3.5.3.5 Interrupt Mask Register (INT\_MSK (Io))

#### Table 98. Interrupt mask register (INT\_MSK (lo))

#### Notes

104.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

Table 99. Interrupt Mask Register (INT\_MSK (Io)) - Register Field Descriptions

| Field     | Description                                                                               |

|-----------|-------------------------------------------------------------------------------------------|

| 5<br>CALM | Calibration request interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled           |

| 4<br>LTCM | Life time counter interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled             |

| 3<br>CVMM | Current / Voltage measurement interrupt mask 0 - Interrupt enabled 1 - Interrupt disabled |

Table 104. Offset Compensation - Temperature Channel (106)

| ITOC[7:0]<br>ETOC[7:0] | Temperature Channel Offset<br>Compensation <sup>(107)</sup> |

|------------------------|-------------------------------------------------------------|

| 0x7F                   | +9.689                                                      |

| 0x7E                   | +9.613                                                      |

| 0x7D                   | +9.537                                                      |

|                        | ·                                                           |

|                        | ·                                                           |

| 0x03                   | +0.229                                                      |

| 0x02                   | +0.153                                                      |

| 0x01                   | +0.076                                                      |

| 0x00 (default)         | 0                                                           |

| 0xFF                   | -0.076                                                      |

| 0xFE                   | -0.153                                                      |

| 0xFD                   | -0.229                                                      |

|                        | ·                                                           |

|                        | ·                                                           |

| 0x82                   | -9.613                                                      |

| 0x81                   | -9.689                                                      |

| 0x80                   | -9.766                                                      |

#### Notes

106. Typical values based on default gain setting

107.SD input related (mV)

#### NOTE

Factory trimmed compensation values are only available for the internal temperature channel.

## 5.7.5 Calibration

To ensure the maximum precision of the current and voltage sense module, several stages of calibration are implemented to compensate temperature effects. The calibration concept combines the availability of FLASH and the temperature information to guarantee the measurement accuracy under all functional conditions.

The trimming and calibration procedures are split in three different categories: Power On-, Calibration Request-, and Optional Verification Procedures.

## 5.7.5.1 System Power On Procedure

Several device parameters are guaranteed with full precision after system trimming only. During final test of the device, trim values are computed, verified, and stored into the system FLASH memory.

To ensure optimum system performance, the following power on procedure has to be performed during power on. As the device is typically constantly powered during its operation, this operation has to be performed typically one time only.

During a system power loss or low power reset condition, the application software has to ensure the procedure executes again.

## **Table 108. Module Memory Map**

| Offset | Name                                 |        | 7      | 6       | 5          | 4              | 3             | 2           | 1           | 0       |

|--------|--------------------------------------|--------|--------|---------|------------|----------------|---------------|-------------|-------------|---------|

|        |                                      | R      | 0      | 0       | 0          | 0              | 0             | 0           | 0           | 0       |

| OvEQ   | ACQ_CTL                              | W      | AHCRM  | OPTEM   | OPENEM     | CVMIEM         | ETMENM        | ITMENM      | VMENM       | CMENM   |

| 0x58   | Acquisition control register         | R      | 0      | OPTE    | OPENE      | CVMIE          | ETMEN         | ITMEN       | VMEN        | CMEN    |

|        |                                      | W      | AHCR   | OFIE    | OPENE      | CVIVILE        | ETIVIEN       | IIIVIEN     | VIVICIN     | CIVILIN |

| 0x5A   | ACQ_SR (hi)                          | R      | AVRF   | PGAG    | VMOW       | CMOW           | ETM           | ITM         | VM          | CM      |

| UXSA   | Acquisition status register          | W      |        | 1.      | V          | Write 1 will o | lear the flag | S           | 1           | I.      |

| 0x5B   | ACQ_SR (lo)                          | R      | OPEN   | 0       | 0          | VTH            | ETCHOP        | ITCHOP      | VCHOP       | CCHOP   |

| UNDD   | Acquisition status register          | W      |        |         |            |                |               |             |             |         |

|        |                                      | R      | 0      | 0       | 0          | 0              | 0             | 0           | 0           | 0       |

| 0x5C   | ACQ_ACC1 Acquisition chain control 1 | W      | ТСОМРМ | VCOMPM  | CCOMP<br>M | LPFENM         | ETCHOP<br>M   | ITCHOP<br>M | CVCHOP<br>M | AGENM   |

|        | Acquisition chain control i          | R      | TCOMP  | VCOMP   | CCOMP      | LPFEN          | ETCHOP        | ITCHOP      | CVCHOP      | AGEN    |

|        |                                      | W      | TOOM   | VOOIVII | OOOWII     | LITEIN         | LIGHO         | 1101101     | OVOITOI     | AGEN    |

|        |                                      | R      | 0      | 0       | 0          | 0              | 0             | 0           | 0           | 0       |

| 0x5E   | ACQ_ACC0                             | W      | ZEROM  | ECAPM   | TADCGM     | VADCGM         | CADCGM        | TDENM       | VDENM       | CDENM   |

| UXUL   | Acquisition chain control 0          | R<br>W | ZERO   | ECAP    | TADCG      | VADCG          | CADCG         | TDEN        | VDEN        | CDEN    |

| 0x60   | ACQ_DEC R                            |        | 0      | 0       | 0          | 0              | 0             | DEC[2:0]    |             |         |

| 0,000  | Decimation Rate V                    |        |        |         |            |                |               |             |             |         |

| 0x61   | ACQ_BGC                              | R      | 0      | 0       | BC A D     | C[1:0]         | BGLDO         | BG3EN       | BG2EN       | BG1EN   |

| UXOI   | BandGap control                      | W      |        |         | BGAL       | /C[1.0]        | BGLDO         |             |             |         |

| 0x62   | ACQ_GAIN                             | R      | 0      | 0       | 0          | 0              | 0             |             | IGAIN[2:0]  | •       |

| 0.02   | PGA gain                             | W      |        |         |            |                |               |             | IGAIN[2.0]  |         |

| 0x63   | ACQ_GCB                              | R      |        |         |            | DI.            | 7.∩1          |             |             |         |

| 0,000  | GCB threshold                        | W      | D[7:0] |         |            |                |               |             |             |         |

|        | ACQ_ITEMP (hi)                       | R      |        |         |            | ITEMI          | P[15:8]       |             |             |         |

| 0x64   | Internal temp. measurement result    | W      |        |         |            |                |               |             |             |         |

|        | ACQ_ITEMP (Io)                       | R      |        |         |            | ITEM           | P[7:0]        |             |             |         |

| 0x65   | Internal temp. measurement result    | W      |        |         |            |                |               |             |             |         |

|        | ACQ_ETEMP (hi)                       | R      |        |         |            | EEMF           | P[15:8]       |             |             |         |

| 0x66   | External temp. measurement result    | W      |        |         |            |                |               |             |             |         |

|        | ACQ_ETEMP (lo)                       | R      |        | 1       |            | EEM            | P[7:0]        |             |             |         |

| 0x67   | External temp. measurement result    | W      |        |         |            |                |               |             |             |         |

| 0x68   | Reserved                             | R      | 0      | 0       | 0          | 0              | 0             | 0           | 0           | 0       |

| 0,00   | NESCIVEU                             | W      |        |         |            |                |               |             |             |         |

| 0x69   | ACQ_CURR1                            | R      |        |         |            | CURR           | [23:16]       |             |             |         |

| 0,03   | Current measurement result           | W      |        |         |            |                |               |             |             |         |

#### 5.9.4.2 Prescaler

The prescaler divides the bus clock by 1, 2, 4, 8,16, 32, 64, or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in the timer system control register 2 (TSCR2).

## 5.9.4.3 Input Capture

Clearing the I/O (input/output) select bit, IOSn, configures channel n as an input capture channel. The input capture function captures the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the timer transfers the value in the timer counter into the timer channel registers, TCn.

The minimum pulse width for the input capture input is greater than two bus clocks. An input capture on channel n sets the CnF flag. The CnI bit enables the CnF flag to generate interrupt requests.

## 5.9.4.4 Output Compare

Setting the I/O select bit, IOSn, configures channel n as an output compare channel. The output compare function can generate a periodic pulse with a programmable polarity, duration, and frequency. When the timer counter reaches the value in the channel registers of an output compare channel, the timer can set, clear, or toggle the channel pin. An output compare on channel n sets the CnF flag. The CnI bit enables the CnF flag to generate interrupt requests.

The output mode and level bits, OMn and OLn, select set, clear, toggle on output compare. Clearing both OMn and OLn disconnects the pin from the output logic. Setting a force output compare bit, FOCn, causes an output compare on channel n. A forced output compare does not set the channel flag.

A successful output compare on channel 3 overrides output compares on all other output compare channels. The output compare 3 mask register masks the bits in the output compare 3 data register. The timer counter reset enable bit, TCRE, enables channel 3 output compares to reset the timer counter. Writing to the timer port bit of an output compare pin does not affect the pin state. The value written is stored in an internal latch. When the pin becomes available for general-purpose output, the last value written to the bit appears at the pin.

#### **5.9.5** Resets

#### 5.9.5.1 General

The reset state of each individual bit is listed within the Register Description Section 5.9.3, "Memory Map and Registers", which details the registers and their bit-fields.

## 5.9.6 Interrupts

#### 5.9.6.1 General

This section describes interrupts originated by the TIM16B4C block. Table 225 lists the interrupts generated by the TIM16B4C to communicate with the MCU.

#### Table 225. TIM16B4C Interrupts

| Interrupt | Offset | Vector | Priority | Source            | Description                              |

|-----------|--------|--------|----------|-------------------|------------------------------------------|

| C[3:0]F   | -      | -      | -        | Timer Channel 3-0 | Active high timer channel interrupts 3-0 |

| TOF       | -      | -      | -        | Timer Overflow    | Timer Overflow interrupt                 |

## 5.9.6.2 Description of Interrupt Operation

The TIM16B4C uses a total of 5 interrupt vectors. The interrupt vector offsets and interrupt numbers are chip dependent. More information on interrupt vector offsets and interrupt numbers can be found in Section 5.3, "Interrupt Module - IRQ".

## 5.10.5.3.3 GPIO Port Data Register (GPIO\_DATA)

#### Table 231. GPIO Port Data Register (GPIO\_DATA)

| Offset <sup>(199)</sup> 0x43 Access: User rea |   |   |   |   |                      |     | cess: User read |     |

|-----------------------------------------------|---|---|---|---|----------------------|-----|-----------------|-----|

|                                               | 7 | 6 | 5 | 4 | 3                    | 2   | 1               | 0   |

| R                                             | 0 | 0 | 0 | 0 | PD3 <sup>(200)</sup> | PD2 | PD1             | PD0 |

| W                                             |   |   |   |   |                      |     |                 |     |

#### Notes

199.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

200. Due the different implementation of the L0/PTB3, PTWU needs to be set in the GPIO\_IN3 to read the PD3 port status during normal mode.

#### Table 232. GPIO Port Data Register (GPIO\_DATA)

| Field | Description                                  |

|-------|----------------------------------------------|

| 3     | PTB3 Data Register                           |

| PD3   | A read returns the value of the PTB3 buffer. |

| 2     | PTB2 Data Register                           |

| PD2   | A read returns the value of the PTB2 buffer. |

| 1     | PTB1 Data Register                           |

| PD1   | A read returns the value of the PTB1 buffer. |

| 0     | PTB0 Data Register                           |

| PD0   | A read returns the value of the PTB0 buffer. |

## 5.10.5.3.4 Port 0 Input Configuration (GPIO\_IN0)

#### Table 233. Port 0 Input Configuration (GPIO\_IN0)

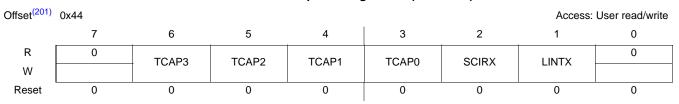

#### Notes

201.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

#### Table 234. Port 0 input configuration (GPIO\_IN0)

| Field      | Description                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>TCAP3 | PTB0 - Timer Input Capture Channel 3 0 - PTB0 Input buffer disconnected from Timer Channel 3 - Input Capture 1 - PTB0 Input buffer routed to Timer Channel 3 - Input Capture |

| 5<br>TCAP2 | PTB0 - Timer Input Capture Channel 2 0 - PTB0 Input buffer disconnected from Timer Channel 2 - Input Capture 1 - PTB0 Input buffer routed to Timer Channel 2 - Input Capture |

| 4<br>TCAP1 | PTB0 - Timer Input Capture Channel 1 0 - PTB0 Input buffer disconnected from Timer Channel 1 - Input Capture 1 - PTB0 Input buffer routed to Timer Channel 1 - Input Capture |

| 3<br>TCAP0 | PTB0 - Timer Input Capture Channel 0 0 - PTB0 Input buffer disconnected from Timer Channel 0 - Input Capture 1 - PTB0 Input buffer routed to Timer Channel 0 - Input Capture |

## 5.12 Serial Communication Interface (S08SCIV4)

# MCU ANALOG

## 5.12.1 Introduction

#### 5.12.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Active edge on receive pin

- Break detect supporting LIN

- · Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- · Receiver wake-up by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

## 5.12.1.2 Modes of Operation

See Section 5.12.3, "Functional Description", for details concerning SCI operation in these modes:

- 8- and 9-bit data modes

- Loop mode

- · Single-wire mode

## 5.12.1.3 Block Diagram

Figure 46 shows the transmitter portion of the SCI.

## 5.15.8.2 Low Power Operation

The MM912\_637 has two static low-power modes Pseudo Stop and Stop mode. For a detailed description refer to the S12CPMU section.

## 5.15.9 Security

The MCU security mechanism prevents unauthorized access to the Flash memory. Refer to Section 5.20, "MCU - Security (S12XS9SECV2)", Section 5.21.4.1, "Security", and Section 5.24.5, "Security". Resets and Interrupts

Consult the S12 CPU manual and the S12SINT section for information on exception processing.

#### 5.15.9.1 Resets

Table 287 lists all Reset sources and the vector locations. Resets are explained in detail in Section 5.22, "S12 Clock, Reset, and Power Management Unit (S12CPMU)".

| Vector Address | Reset Source            | CCR<br>Mask | Local Enable                 |

|----------------|-------------------------|-------------|------------------------------|

| \$FFFE         | Power-On Reset (POR)    | None        | None                         |

| \$FFFE         | Low Voltage Reset (LVR) | None        | None                         |

| \$FFFE         | External pin RESET      | None        | None                         |

| \$FFFE         | Illegal Address Reset   | None        | None                         |

| \$FFFC         | Clock monitor reset     | None        | OSCE Bit in CPMUOSC register |

| \$FFFA         | COP watchdog reset      | None        | CR[2:0] in CPMUCOP register  |

**Table 287. Reset Sources and Vector Locations**

## 5.15.9.2 Interrupt Vectors

Table 288 lists all interrupt sources and vectors in the default order of priority. The interrupt module (see Section 5.17, "MCU - Interrupt Module (S12SINTV1)") provides an interrupt vector base register (IVBR) to relocate the vectors.

| Vector Address <sup>(236)</sup>                | Interrupt Source                  | CCR<br>Mask | Local Enable     | Wake-up from STOP | Wake-up<br>from WAIT |

|------------------------------------------------|-----------------------------------|-------------|------------------|-------------------|----------------------|

| Vector base + \$F8                             | Unimplemented instruction trap    | None        | None             | -                 | -                    |

| Vector base+ \$F6                              | SWI                               | None        | None             | -                 | -                    |

| Vector base+ \$F4                              | D2DI Error Interrupt              | X Bit       | None             | Yes               | Yes                  |

| Vector base+ \$F2                              | D2DI External Interrupt           | I bit       | D2DCTL (D2DIE)   | Yes               | Yes                  |

| Vector base+ \$F0                              | RTI timeout interrupt             | 3.22.6 lr   | nterrupts        |                   |                      |

| Vector base + \$EE<br>to<br>Vector base + \$DA |                                   |             | Reserved         | •                 |                      |

| Vector base + \$D8                             | SPI I bit SPICR1 (SPIE, SPTIE) No |             |                  |                   |                      |

| Vector base + \$D6<br>to<br>Vector base + \$CA |                                   |             | Reserved         | -                 |                      |

| Vector base + \$C8                             | Oscillator status interrupt       | I bit       | CPMUINT (OSCIE)  | No                | No                   |

| Vector base + \$C6                             | PLL lock interrupt                | I bit       | CPMUINT (LOCKIE) | No                | No                   |

| Vector base + \$C4<br>to<br>Vector base + \$BC |                                   |             | Reserved         | ,                 |                      |

Table 288. Interrupt Vector Locations (Sheet 1 of 2)

MM912\_637, Rev. 3.0

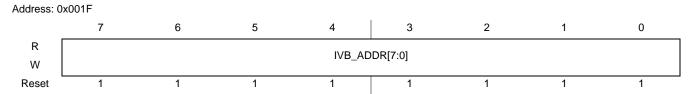

#### Table 310. Interrupt Vector Base Register (IVBR)

Read: Anytime. Write: Anytime.

**Table 311. IVBR Field Descriptions**

| Field                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>IVB_ADDR[7:0] | Interrupt Vector Base Address Bits — These bits represent the upper byte of all vector addresses. Out of reset, these bits are set to 0xFF (i.e., vectors are located at 0xFF80–0xFFFE) to ensure compatibility to HCS12.  Note: A system reset will initialize the interrupt vector base register with "0xFF" before it is used to determine the reset vector address. Therefore, changing the IVBR has no effect on the location of the three reset vectors (0xFFFA–0xFFFE).  Note: If the BDM is active (i.e., the CPU is in the process of executing BDM firmware code), the contents of IVBR are ignored and the upper byte of the vector address is fixed as "0xFF". This is done to enable handling of all non-maskable interrupts in the BDM firmware. |

## 5.17.4 Functional Description

The INT module processes all exception requests to be serviced by the CPU module. These exceptions include interrupt vector requests and reset vector requests. Each of these exception types and their overall priority level is discussed in the following subsections.

## 5.17.4.1 S12S Exception Requests

The CPU handles both reset requests and interrupt requests. A priority decoder is used to evaluate the priority of pending interrupt requests.

## 5.17.4.2 Interrupt Prioritization

The INT module contains a priority decoder to determine the priority for all interrupt requests pending for the CPU. If more than one interrupt request is pending, the interrupt request with the higher vector address wins the prioritization.

The following conditions must be met for an I bit maskable interrupt request to be processed.

- 1. The local interrupt enabled bit in the peripheral module must be set.

- The I bit in the condition code register (CCR) of the CPU must be cleared.

- 3. There is no SWI, TRAP, or X bit maskable request pending.

#### **NOTE**

All non I bit maskable interrupt requests always have higher priority than the I bit maskable interrupt requests. If the X bit in the CCR is cleared, it is possible to interrupt an I bit maskable interrupt by an X bit maskable interrupt. It is possible to nest non maskable interrupt requests, e.g., by nesting SWI or TRAP calls.

Since an interrupt vector is only supplied at the time when the CPU requests it, it is possible that a higher priority interrupt request could override the original interrupt request that caused the CPU to request the vector. In this case, the CPU will receive the highest priority vector and the system will process this interrupt request first, before the original interrupt request is processed.

If the interrupt source is unknown (for example, in the case where an interrupt request becomes inactive after the interrupt has been recognized, but prior to the CPU vector request), the vector address supplied to the CPU will default to that of the spurious interrupt vector.

#### NOTE

Care must be taken to ensure that all interrupt requests remain active until the system begins execution of the applicable service routine; otherwise, the exception request may not get processed at all or the result may be a spurious interrupt request (vector at address (vector base + 0x0080)).

## 5.17.4.3 Reset Exception Requests

The INT module supports three system reset exception request types (Refer to the Clock and Reset generator module for details):

- 1. Pin reset, power-on reset or illegal address reset, low voltage reset (if applicable)

- 2. Clock monitor reset request

- COP watchdog reset request

## 5.17.4.4 Exception Priority

The priority (from highest to lowest) and address of all exception vectors issued by the INT module upon request by the CPU is shown in Table 312.

**Table 312. Exception Vector Map and Priority**

| Vector Address <sup>(240)</sup> | Source                                                                                                                            |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0xFFFE                          | Pin reset, power-on reset, illegal address reset, low voltage reset (if applicable)                                               |

| 0xFFFC                          | Clock monitor reset                                                                                                               |

| 0xFFFA                          | COP watchdog reset                                                                                                                |

| (Vector base + 0x00F8)          | Unimplemented opcode trap                                                                                                         |

| (Vector base + 0x00F6)          | Software interrupt instruction (SWI) or BDM vector request                                                                        |

| (Vector base + 0x00F4)          | X bit maskable interrupt request (XIRQ or D2D error interrupt) <sup>(241)</sup>                                                   |

| (Vector base + 0x00F2)          | IRQ or D2D interrupt request <sup>(242)</sup>                                                                                     |

| (Vector base + 0x00F0-0x0082)   | Device specific I bit maskable interrupt sources (priority determined by the low byte of the vector address, in descending order) |

| (Vector base + 0x0080)          | Spurious interrupt                                                                                                                |

#### Notes

240.16-bit vector address based

241.D2D error interrupt on MCUs featuring a D2D initiator module, otherwise XIRQ pin interrupt

242.D2D interrupt on MCUs featuring a D2D initiator module, otherwise IRQ pin interrupt

# 5.17.5 Initialization/Application Information

#### 5.17.5.1 Initialization

After a system reset, the software should:

- Initialize the interrupt vector base register, if the interrupt vector table is not located at the default location (0xFF80–0xFFF9).

- 2. Enable I bit maskable interrupts by clearing the I bit in the CCR.

- 3. Enable the X bit maskable interrupt by clearing the X bit in the CCR.

## 5.18.5.1 Chip Bus Control

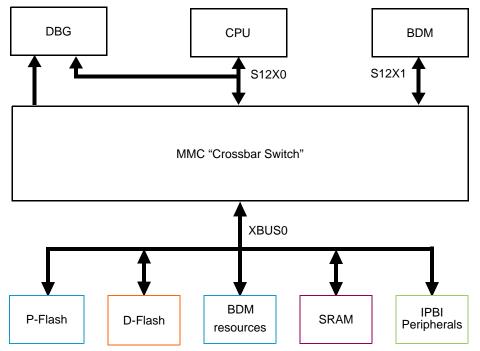

The S12PMMC controls the address buses and the data buses that interface the bus masters (CPU12, S12SBDM) with the rest of the system (master buses). In addition, the MMC handles all CPU read data bus swapping operations. All internal resources are connected to specific target buses (see Figure 62).

Figure 62. S12I platform

## 5.18.5.1.1 Master Bus Prioritization Regarding Access Conflicts on Target Buses

The arbitration scheme allows only one master to be connected to a target at any given time. The following rules apply when prioritizing accesses from different masters to the same target bus:

- CPU12 always has priority over BDM.

- BDM has priority over CPU12 when its access is stalled for more than 128 cycles. In the later case the CPU will be stalled after finishing the current operation and the BDM will gain access to the bus.

## **5.18.5.2** Interrupts

The MMC does not generate any interrupts.

# 5.18.6 Initialization/Application Information

## 5.18.6.1 CALL and RTC Instructions

CALL and RTC instructions are uninterruptable CPU instructions that automate page switching in the program page window. The CALL instruction is similar to the JSR instruction, but the subroutine that is called can be located anywhere in the local address space or in any Flash or ROM page visible through the program page window. The CALL instruction calculates and stacks a return address, stacks the current PPAGE value and writes a new instruction-supplied value to the PPAGE register. The PPAGE value controls which of the 256 possible pages is visible through the 16 kbyte program page window in the 64 kbyte local CPU memory map. Execution then begins at the address of the called subroutine.

4. COPOSCSEL: In Normal mode (if PROT=0) until CPMUCOP write once is taken. If COPOSCSEL was cleared by UPOSC=0 (entering Full Stop mode with COPOSCSEL=1 or insufficient OSCCLK quality), then COPOSCSEL can be set again once.

#### **NOTE**

After writing CPMUCLKS register, it is strongly recommended to read back CPMUCLKS register to make sure that write of PLLSEL, RTIOSCSEL and COPOSCSEL was successful.

**Table 412. CPMUCLKS Descriptions**

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PLLSEL    | PLL Select Bit This bit selects the PLLCLK as source of the system clocks (core clock and bus clock). PLLSEL can only be set to 0, if UPOSC=1. UPOSC= 0 sets the PLLSEL bit. Entering Full Stop mode sets the PLLSEL bit. 0 System clocks are derived from OSCCLK if oscillator is up (UPOSC=1, f <sub>BUS</sub> = f <sub>OSC</sub> / 2. 1 System clocks are derived from PLLCLK, f <sub>BUS</sub> = f <sub>PLL</sub> / 2.                                                                                                                                                                                                                                                                                                                                            |

| 6<br>PSTP      | Pseudo Stop Bit This bit controls the functionality of the oscillator during Stop mode.  O Oscillator is disabled in Stop mode (Full Stop mode).  Oscillator continues to run in Stop mode (Pseudo Stop mode), option to run RTI and COP.  Note: Pseudo Stop mode allows for faster STOP recovery and reduces the mechanical stress and aging of the resonator in case of frequent STOP conditions at the expense of a slightly increased power consumption.  Note: When starting up the external oscillator (either by programming OSCE bit to 1 or on exit from Full Stop mode with OSCE bit is already 1) the software must wait for a minimum time equivalent to the startup time of the external oscillator t <sub>UPOSC</sub> before entering Pseudo Stop mode. |

| 3<br>PRE       | RTI Enable During Pseudo Stop Bit — PRE enables the RTI during Pseudo Stop mode.  0 RTI stops running during Pseudo Stop mode.  1 RTI continues running during Pseudo Stop mode if RTIOSCSEL=1.  Note: If PRE=0 or RTIOSCSEL=0 then the RTI will go static while Stop mode is active. The RTI counter will not be reset.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2<br>PCE       | COP Enable During Pseudo Stop Bit — PCE enables the COP during Pseudo Stop mode.  0 COP stops running during Pseudo Stop mode  1 COP continues running during Pseudo Stop mode if COPOSCSEL=1  Note: If PCE=0 or COPOSCSEL=0 then the COP will go static while Stop mode is active. The COP counter will not be reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1<br>RTIOSCSEL | RTI Clock Select— RTIOSCSEL selects the clock source to the RTI. Either IRCCLK or OSCCLK. Changing the RTIOSCSEL bit re-starts the RTI timeout period.  RTIOSCSEL can only be set to 1, if UPOSC=1.  UPOSC= 0 clears the RTIOSCSEL bit.  0 RTI clock source is IRCCLK.  1 RTI clock source is OSCCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0<br>COPOSCSEL | COP Clock Select— COPOSCSEL selects the clock source to the COP. Either IRCCLK or OSCCLK. Changing the COPOSCSEL bit re-starts the COP timeout period.  COPOSCSEL can only be set to 1, if UPOSC=1.  UPOSC= 0 clears the COPOSCSEL bit.  0 COP clock source is IRCCLK.  1 COP clock source is OSCCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 5.24.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

Table 499. Flash Reserved3 Register (FRSV3)

Address: 0x010E R W Reset = Unimplemented or Reserved

All bits in the FRSV3 register read 0 and are not writable.

## 5.24.3.2.15 Flash Reserved4 Register (FRSV4)

This Flash register is reserved for factory testing.

Table 500. Flash Reserved4 Register (FRSV4)

Address: 0x010F R W Reset n = Unimplemented or Reserved

All bits in the FRSV4 register read 0 and are not writable.

## 5.24.3.2.16 Flash Option Register (FOPT)

The FOPT register is the Flash option register.

Table 501. Flash Option Register (FOPT)

All bits in the FOPT register are readable but are not writable.

During the reset sequence, the FOPT register is loaded from the Flash nonvolatile byte in the Flash configuration field, at global address 0x3\_FF0E located in P-Flash memory (see Table 463), as indicated by reset condition F in Figure 501. If a double bit fault is detected while reading the P-Flash phrase containing the Flash nonvolatile byte during the reset sequence, all bits in the FOPT register will be set.

**Table 502. FOPT Field Descriptions**

| Field          | Description                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>NV[7:0] | Nonvolatile Bits — The NV[7:0] bits are available as nonvolatile bits. Refer to the device user guide for proper use of the NV bits. |

MM912\_637, Rev. 3.0

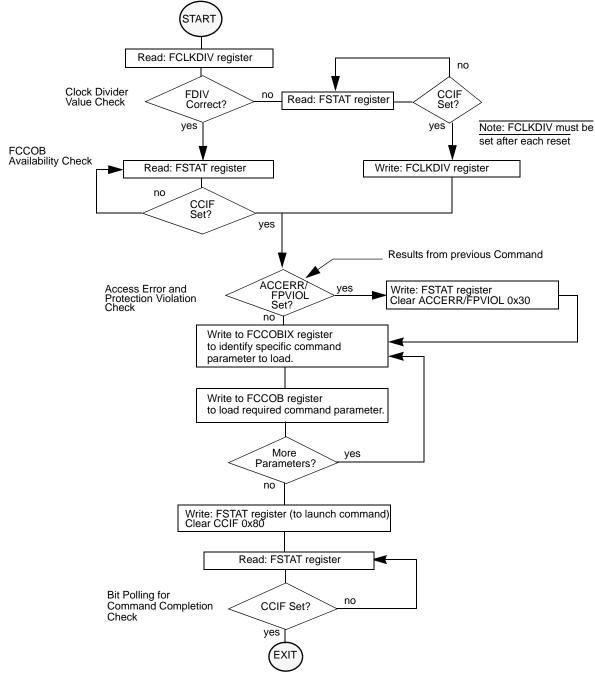

#### 5.24.4.3.2.1 Define FCCOB Contents

The FCCOB parameter fields must be loaded with all required parameters for the Flash command being executed. Access to the FCCOB parameter fields is controlled via the CCOBIX bits in the FCCOBIX register (see Section 5.24.3.2.3, "Flash CCOB Index Register (FCCOBIX)").

The contents of the FCCOB parameter fields are transferred to the Memory Controller when the user clears the CCIF command completion flag in the FSTAT register (writing 1 clears the CCIF to 0). The CCIF flag will remain clear until the Flash command has completed. Upon completion, the Memory Controller will return CCIF to 1 and the FCCOB register will be used to communicate any results. The flow for a generic command write sequence is shown in Figure 113.

Figure 113. Generic Flash Command Write Sequence Flowchart

MM912\_637, Rev. 3.0

#### Table 565. Module Memory Map

| Offset <sup>(308)</sup> | Name                       |   | 7 | 6 | 5 | 4            | 3 | 2 | 1 | 0   |

|-------------------------|----------------------------|---|---|---|---|--------------|---|---|---|-----|

| 0xE7                    | TRIM_LVT                   | R | 0 | 0 | 0 | 0            | 0 | 0 | 0 | LVT |

| OXL1                    | Trim low voltage threshold | W |   |   |   |              |   |   |   |     |

| 0xE8                    | TRIM_OSC (hi)              | R |   |   |   |              |   |   |   |     |

| UXLO                    | Trim LP oscillator         | W |   |   |   | LPOSC[12:0]  |   |   |   |     |

| 0xE9                    | TRIM_OSC (lo)              | R |   |   |   | 21 000[12.0] |   |   |   |     |

| UXLS                    | Trim LP oscillator         | W |   |   |   |              |   |   |   |     |

| 0xEA-                   | Reserved                   | R | 0 | 0 | 0 | 0            | 0 | 0 | 0 | 0   |

| 0xEF                    | Reserved                   |   |   |   |   |              |   |   |   |     |

#### Notes

308.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

## 6.3.2.1 Trim Bandgap 0 (TRIM\_BG0 (hi))

#### Table 566. Trim Bandgap 0 (TRIM\_BG0 (hi))

| Offset <sup>(309)</sup> | 0xE0 |   |             |             |   |   | Access:     | User read/write |

|-------------------------|------|---|-------------|-------------|---|---|-------------|-----------------|

|                         | 7    | 6 | 5           | 4           | 3 | 2 | 1           | 0               |

| R                       | 0    | 0 |             | TCIBG2[2:0] |   |   | TCIBG1[2:0] |                 |

| W                       |      |   | 161562[2.0] |             |   |   |             |                 |

| Reset                   | 0    | 0 | 0           | 0           | 0 | 0 | 0           | 0               |

#### Notes

309.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

#### Table 567. Trim Bandgap 0 (TRIM\_BG0 (hi)) - Register Field Descriptions

| Field       | Description                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-3         | The optimal content of this register is determined during final test and stored in the microcontroller IFR. For proper operation                                    |

| TCIBG2[2:0] | of the MM912_637, the content has to be copied to this location. See Section 6.2.1, "IFR - Trimming Content for Analog Die Functionality" for location information. |

| 2-0         | 1 discionality for location information.                                                                                                                            |

| TCIBG1[2:0] |                                                                                                                                                                     |

## 6.3.2.2 Trim Bandgap 0 (TRIM\_BG0 (lo))

#### Table 568. Trim Bandgap 0 (TRIM\_BG0 (lo))

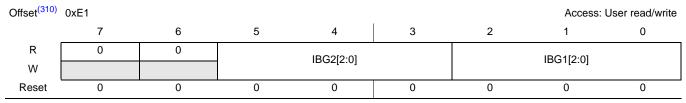

#### Notes

310.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

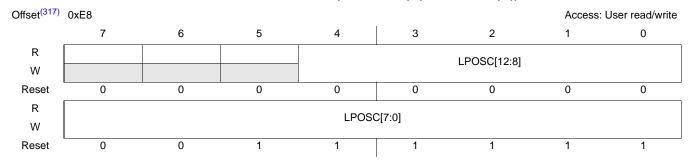

## 6.3.2.9 Trim LP Oscillator (TRIM\_OSC (hi), TRIM\_OSC (lo))

#### Table 582. Trim LP Oscillator (TRIM\_OSC (hi), TRIM\_OSC (lo))

#### Notes

317.Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

Table 583. Trim LP Oscillator (TRIM\_OSC (hi), TRIM\_OSC (lo)) - Register Field Descriptions

| Field               | Description                                                                                                                                                                                                                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-0<br>LPOSC[12:0] | The optimal content of this register is determined during final test and stored in the microcontroller IFR. For proper operation of the MM912_637, the content has to be copied to this location. See Section 6.2.1, "IFR - Trimming Content for Analog Die Functionality" for location information. |