Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f492pmc-ge1 |

|----------------------------|----------------------------------------------------------------------------|

| Supplier Device Package    | 64-LQFP (12×12)                                                            |

| Package / Case             | 64-LQFP                                                                    |

| Mounting Type              | Surface Mount                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Oscillator Type            | External                                                                   |

| Data Converters            | A/D 12x8/10b                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| RAM Size                   | 12K x 8                                                                    |

| EEPROM Size                | -                                                                          |

| Program Memory Type        | FLASH                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Number of I/O              | 49                                                                         |

| Peripherals                | DMA, LVD, PWM, WDT                                                         |

| Connectivity               | I <sup>2</sup> C                                                           |

| Speed                      | 80MHz                                                                      |

| Core Size                  | 32-Bit Single-Core                                                         |

| Core Processor             | FR60 RISC                                                                  |

| Product Status             | Obsolete                                                                   |

| Details                    |                                                                            |

## 32-bit Microcontrollers

**CMOS**

# FR60 MB91490 Series

# MB91F492 / FV470

#### **■ DESCRIPTION**

The MB91490 series is Fujitsu's general-purpose 32-bit RISC microcontroller, which is designed for embedded control applications that require high-speed processing performance.

This series uses the FR60 CPU, which is compatible with the FR\* family of CPUs.

\*: FR, the abbreviation of FUJITSU RISC controller, is a line of products of Fujitsu Microelectronics Limited.

#### **■ FEATURES**

- FR60 CPU

- 32-bit RISC, load/store architecture, five-stage pipeline

- Operating frequency of 80 MHz (PLL clock multiplied)

- 16-bit fixed-length instructions (basic instructions)

- Instruction execution speed : one instruction per cycle

- Memory-to-memory transfer, bit processing, barrel shift instructions, etc. : instructions suitable for embedded applications

- Function entry and exit instructions, multi load/store instructions of register contents : instructions compatible with C language.

- · Register interlock function to facilitate assembly-language coding

- Built-in multiplier/instruction-level support

- Signed 32-bit multiplication : 5 cycles

- Signed 16-bit multiplication : 3 cycles

- Interrupts (save PC and PS): 6 cycles, 16 priority levels

- Harvard architecture allowing program access and data access to be executed simultaneously

- · Instructions compatible with the FR family

(Continued)

For the information for microcontroller supports, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

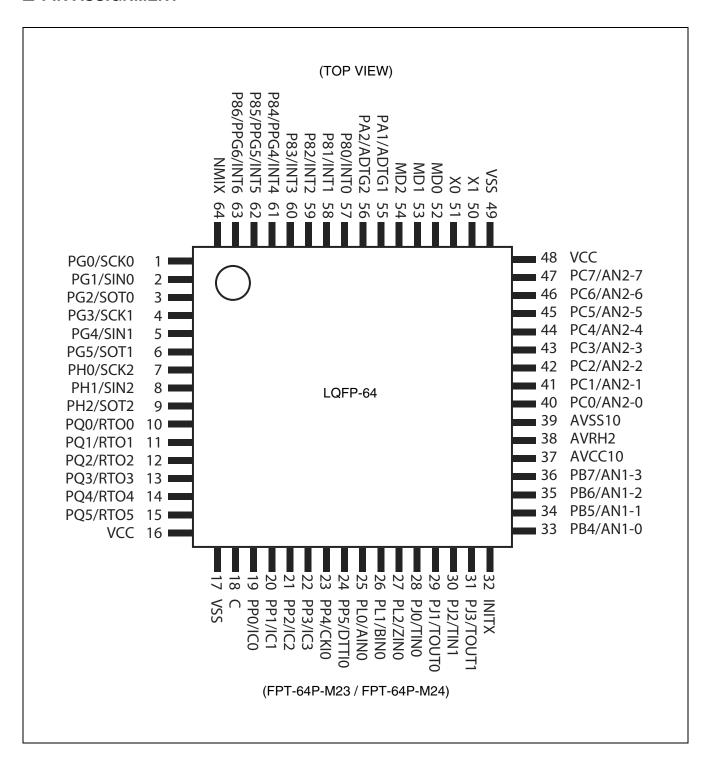

#### **■ PIN ASSIGNMENT**

| Pin no. | Pin<br>name    | I/O<br>circuit<br>type* | Function                                                                               |

|---------|----------------|-------------------------|----------------------------------------------------------------------------------------|

| 4       | SCK1<br>(SCL1) | D                       | Clock I/O of multi-function serial interface 1 (used in I <sup>2</sup> C mode, SCL1)   |

|         | PG3            |                         | General-purpose I/O port                                                               |

| 5       | SIN1           | D                       | Data input of multi-function serial interface 1 (not used in I <sup>2</sup> C mode)    |

| 5       | PG4            |                         | General-purpose I/O port                                                               |

| 6       | SOT1<br>(SDA1) | D                       | Data output of multi-function serial interface 1 (used in I <sup>2</sup> C mode, SDA1) |

|         | PG5            |                         | General-purpose I/O port                                                               |

| 7       | SCK2<br>(SCL2) | D                       | Clock I/O of multi-function serial interface 2 (used in I <sup>2</sup> C mode, SCL2)   |

|         | PH0            |                         | General-purpose I/O port                                                               |

| 8       | SIN2           | D                       | Data input of multi-function serial interface 2 (not used in I <sup>2</sup> C mode)    |

| 0       | PH1            |                         | General-purpose I/O port                                                               |

| 9       | SOT2<br>(SDA2) | D                       | Data output of multi-function serial interface 2 (used in I <sup>2</sup> C mode, SDA2) |

|         | PH2            |                         | General-purpose I/O port                                                               |

| 28      | TIN0           | D                       | Base timer 0 input                                                                     |

| 20      | PJ0            |                         | General-purpose I/O port                                                               |

| 29      | TOUT0          | D                       | Base timer 0 output                                                                    |

| 29      | PJ1            |                         | General-purpose I/O port                                                               |

| 30      | TIN1           | D                       | Base timer 1 input                                                                     |

| 30      | PJ2            |                         | General-purpose I/O port                                                               |

| 31      | TOUT1          | D                       | Base timer 1 output                                                                    |

| 01      | PJ3            |                         | General-purpose I/O port                                                               |

| 25      | AIN0           | D                       | 8/16-bit up count input pin for up/down counter 0                                      |

| 25      | PL0            |                         | General-purpose I/O port                                                               |

| 26      | BIN0           | D                       | 8/16-bit down count input pin for up/down counter 0                                    |

| 20      | PL1            |                         | General-purpose I/O port                                                               |

| 27      | ZIN0           | D                       | 8/16-bit reset input pin for up/down counter 0                                         |

|         | PL2            |                         | General-purpose I/O port                                                               |

| 19      | IC0            | D                       | Trigger input of input capture 0                                                       |

|         | PP0            |                         | General-purpose I/O port                                                               |

| 20      | IC1            | D                       | Trigger input of input capture 1                                                       |

|         | PP1            |                         | General-purpose I/O port                                                               |

#### Order of power turning ON/OFF

Use the following procedure for turning the power on or off. If not using the A/D converter, connect AVcc = Vcc and AVss = Vss. Turn on the power supply in the sequence  $Vcc \to AVcc \to AVRH2$ , and turn off the power in the reverse sequence.

• Source oscillation input when turning on the power

When turning the power on, maintain the clock input until the device is released from the oscillation stabilization wait state.

• Cautions for operation during PLL clock mode

Even if the oscillator comes off or the clock input stops with the PLL clock selected for MB91490 series, MB91490 series may continue to operate at the free-run frequency of the PLL's internal self-oscillating oscillator circuit.

Performance of this operation, however, cannot be guaranteed.

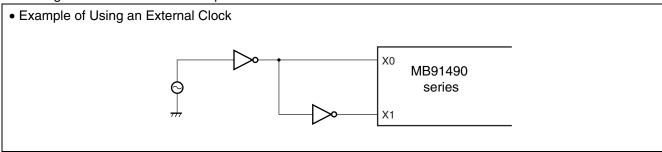

#### Using an external clock

When using an external clock, you must always input clock signals with opposite phase from X0 pin to X1 pin simultaneously. However, as the X1 pin halts with an output at the "H" level during stop mode, insert a resistor of approximately 1  $k\Omega$  externally to prevent a conflict between the two outputs if using stop mode (oscillation stop mode).

The figure below shows an example of how to use an external clock.

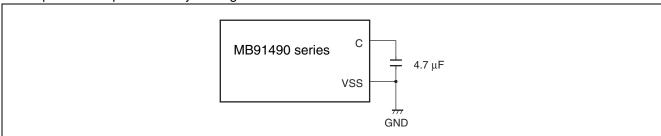

#### • C pin

As MB91490 series includes an internal regulator, always connect a bypass capacitor of approximately  $4.7 \mu F$  to the C pin for use by the regulator.

Software reset on the synchronous mode

Be sure to meet the following two conditions before setting 0 to the SRST bit of STCR (standby control register) when the software reset is used on the synchronous mode.

- Set the interrupt enable flag (I-Flag) to interrupts disabled (I-Flag=0).

- Not used NMI

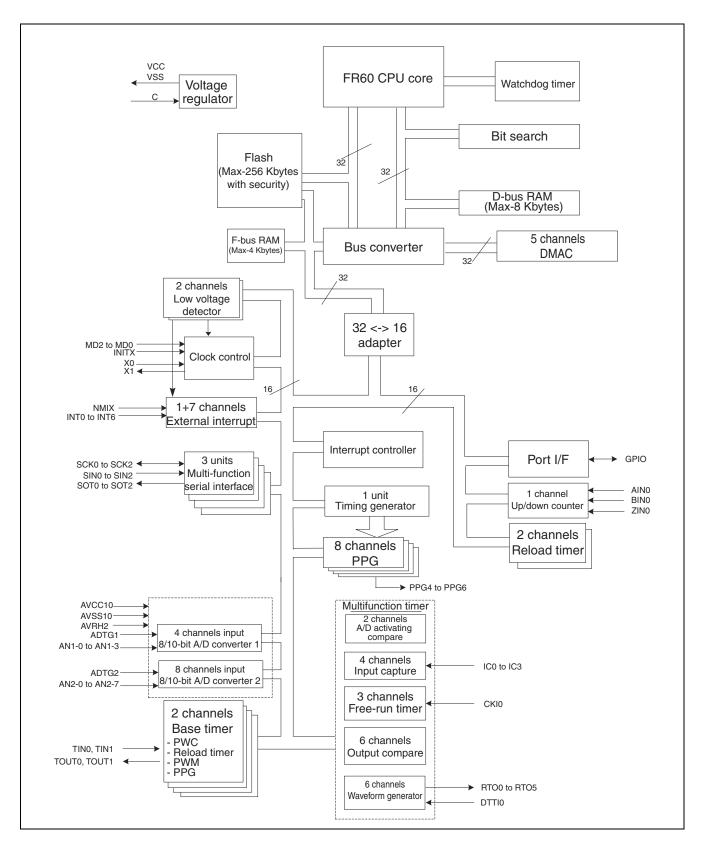

#### **■ BLOCK DIAGRAM**

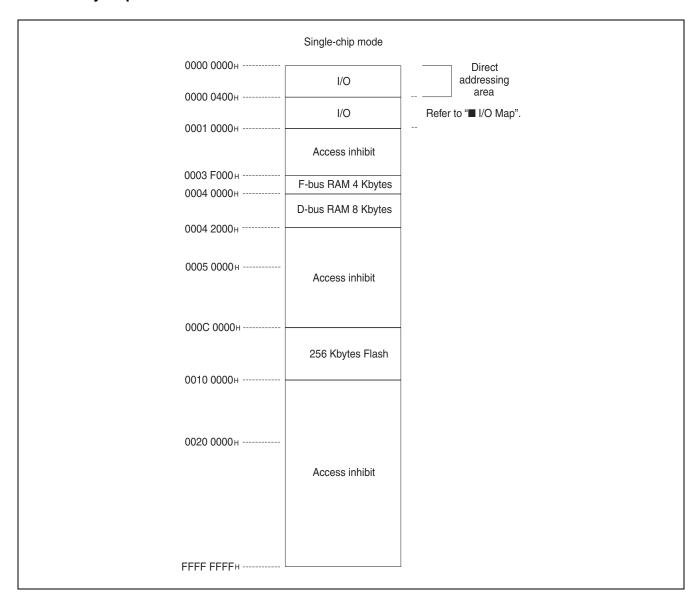

#### **■ MEMORY SPACE**

#### 1. Memory Space

The FR family has 4 Gbytes of logical address space (232 addresses) available to the CPU by linear access.

#### • Direct Addressing Areas

The following address space areas are used as I/O areas.

These areas are called direct addressing areas, in which the address of an operand can be specified directly by the instruction. The size of directly addressable areas depends on the length of the data being accessed as shown below.

ightarrow byte data access : 000 $\rm H$  to 0FFH ightarrow half word data access : 000 $\rm H$  to 1FFH ightarrow word data access : 000 $\rm H$  to 3FFH

#### 2. Memory Map

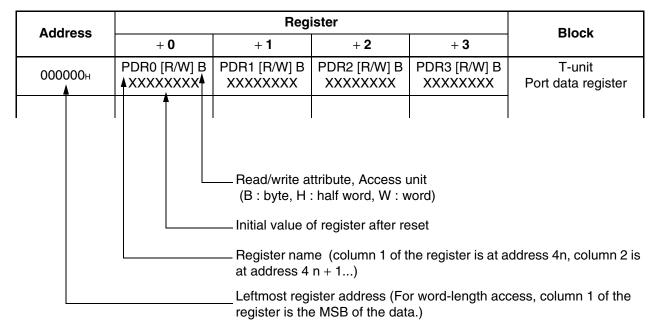

#### ■ I/O MAP

[How to read the table]

Note: Initial values of register bits are represented as follows:

"1": Initial Value "1"

"0": Initial Value "0"

"X": Initial Value "undefined"

" - " : No physical register at this location

Access to addresses where the data access properties have not been documented is prohibited.

| Address |                                      | Reg                                                   | ister                                                 |                                   | Block                             |

|---------|--------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------|-----------------------------------|

| Address | +0                                   | +1                                                    | +2                                                    | +3                                | Block                             |

| 000060н | SSR0 [R/W, R]<br>B, H, W<br>00000011 | ESCR0 [R/W]/<br>IBSR0 [R/W, R]<br>B, H, W<br>00000000 | SCR0 [R/W] /<br>IBCR0 [R/W, R]<br>B, H, W<br>00000000 | SMR0 [R/W]<br>B, H, W<br>000-0000 | Multi-                            |

| 000064н | BGR01[R/W]<br>B, H, W<br>00000000    | BGR00 [R/W]<br>B, H, W<br>00000000                    | RDR(<br>TDR0 [\<br>0 0                                | W] H, W                           | function<br>serial<br>interface 0 |

| 000068н | -                                    | _                                                     | ISMK0 [R/W]<br>B, H<br>01111111                       | ISBA0 [R/W]<br>B, H<br>00000000   |                                   |

| 00006Сн |                                      | _                                                     | _                                                     |                                   | (Reserved)                        |

| 000070н | SSR1 [R/W, R]<br>B, H, W<br>00000011 | ESCR1 [R/W]/<br>IBSR1 [R/W, R]<br>B, H, W<br>00000000 | SCR1 [R/W] /<br>IBCR1 [R/W, R]<br>B, H, W<br>00000000 | SMR1 [R/W]<br>B, H, W<br>000-0000 | Multi-                            |

| 000074н | BGR11 [R/W]<br>B, H, W<br>00000000   | BGR10 [R/W]<br>B, H, W<br>00000000                    | RDR1 [R]/<br>TDR1 [W] H, W<br>0 00000000              |                                   | function<br>serial<br>interface 1 |

| 000078н | _                                    | _                                                     | ISMK1 [R/W]<br>B, H<br>01111111                       | ISBA1 [R/W]<br>B, H<br>00000000   |                                   |

| 00007Сн |                                      | _                                                     | _                                                     |                                   | (Reserved)                        |

| 000080н | SSR2 [R/W, R]<br>B, H, W<br>00000011 | ESCR2 [R/W]/<br>IBSR2 [R/W, R]<br>B, H, W<br>00000000 | SCR2 [R/W] /<br>IBCR2 [R/W, R]<br>B, H, W<br>00000000 | SMR2 [R/W]<br>B, H, W<br>000-0000 | Multi-                            |

| 000084н | BGR21 [R/W]<br>B, H, W<br>00000000   | BGR20 [R/W]<br>B, H, W<br>00000000                    | RDR:<br>TDR2 [\<br>0 0                                | - 1                               | function<br>serial<br>interface 2 |

| 000088н | _                                    | _                                                     | ISMK2 [R/W]<br>B, H<br>01111111                       | ISBA2 [R/W]<br>B, H<br>00000000   |                                   |

| 00008Сн |                                      |                                                       |                                                       |                                   | (Reserved)                        |

| Addyooo                  |                                  | Reg                                | ister                            |                                | Black                                      |  |

|--------------------------|----------------------------------|------------------------------------|----------------------------------|--------------------------------|--------------------------------------------|--|

| Address                  | +0                               | +1                                 | +2                               | +3                             | Block                                      |  |

| 000520н<br>to<br>00053Сн | _                                |                                    |                                  |                                |                                            |  |

| 000540н                  | RCR10 [W]<br>B, H, W<br>XXXXXXXX | W B, H, W B, H, W B, H, W          |                                  |                                |                                            |  |

| 000544н                  | CCRH0 [R/W]<br>B, H<br>00000000  | CCRL0 [R/W, R]<br>B, H<br>-0001000 | _                                | CSR0 [R/W, R]<br>B<br>00000000 | counter 0                                  |  |

| 000548н<br>to<br>00057Сн |                                  | (Reserved)                         |                                  |                                |                                            |  |

| 000580н                  |                                  | R] B, H, W<br>00000000             |                                  | R/W] B, H, W<br>00000000       |                                            |  |

| 000584н                  | _                                | BT1STC [R/W] B<br>00000000         | _                                |                                | Base timer 1                               |  |

| 000588н                  | H,                               | T1PRLL [R/W]<br>W<br>XXXXXXXX      | BT1PDUT/BT1PRI<br>H,<br>XXXXXXXX |                                |                                            |  |

| 00058Сн<br>to<br>000600н |                                  | _                                  | _                                |                                | (Reserved)                                 |  |

| 000604н                  | -                                | _                                  | PCR8 [R/W]<br>B<br>-0000000      | _                              |                                            |  |

| 000608н                  | PCRA [R/W]<br>B, H<br>00-        | PCRB [R/W]<br>B, H<br>0000         | PCRC [R/W]<br>B<br>00000000      | _                              |                                            |  |

| 00060Сн                  | _                                | _                                  | PCRG [R/W]<br>B, H<br>000000     | PCRH [R/W]<br>B, H<br>000      | Pull-up<br>resistor<br>control<br>register |  |

| 000610н                  | PCRJ [R/W]<br>B<br>0000          | _                                  | PCRL [R/W]<br>B<br>000           | _                              | . register                                 |  |

| 000614н                  | PCRP [R/W]<br>B, H<br>000000     | PCRQ [R/W]<br>B, H<br>000000       | _                                |                                |                                            |  |

| 000618н<br>to<br>000FFCн |                                  | -                                  | _                                |                                | (Reserved)                                 |  |

| Address   |       | Reg                                     | jister                      |     | Dlask |  |  |  |  |

|-----------|-------|-----------------------------------------|-----------------------------|-----|-------|--|--|--|--|

| Address — | +0    | +1                                      | +2                          | +3  | Block |  |  |  |  |

| 007030н   |       |                                         |                             |     |       |  |  |  |  |

| 007038н   |       |                                         |                             |     |       |  |  |  |  |

| 00703Сн   | XXX   | WD01 [R/W] W XXXXXXXX XXXXXXXX XXXXXXXX |                             |     |       |  |  |  |  |

| 007040н   |       |                                         | [R/W] W<br>XXXXXX XXXXXX    |     |       |  |  |  |  |

| 007044н   | XXX   |                                         | [R/W] W<br>XXXXXXXXX XXXXX  | «хх |       |  |  |  |  |

| 007048н   |       |                                         | [R/W] W<br>XXXXXX XXXXXX    |     |       |  |  |  |  |

| 00704Сн   | 704CH |                                         |                             |     |       |  |  |  |  |

| 007050н   |       | WA04 [R/W] W<br>XXXX XXXXXXXX XXXXXX    |                             |     |       |  |  |  |  |

| 007054н   | XXX   | WD04 [R/W] W XXXXXXXX XXXXXXXX XXXXXXXX |                             |     |       |  |  |  |  |

| 007058н   |       |                                         | [R/W] W<br>XXXXXX XXXXXX    |     |       |  |  |  |  |

| 00705Сн   | XXX   |                                         | [R/W] W<br>XXXXXXXXX XXXXX  | «хх |       |  |  |  |  |

| 007060н   |       |                                         | [R/W] W<br>XXXXXX XXXXXX    |     |       |  |  |  |  |

| 007064н   | XXX   |                                         | [R/W] W<br>XXXXXXXX XXXXX   | «хх |       |  |  |  |  |

| 007068н   |       |                                         | [R/W] W<br>XXXXXX XXXXXX    |     |       |  |  |  |  |

| 00706Сн   | XXX   |                                         | [R/W] W<br>XXXXXXXXX XXXXX  | «хх |       |  |  |  |  |

| 007070н   |       |                                         | [R/W] W<br>XXXXXX XXXXXX    |     |       |  |  |  |  |

| 007074н   | XXX   |                                         | [R/W] W<br>X XXXXXXXX XXXXX | КХХ |       |  |  |  |  |

#### (Continued)

| Address                                              |     |                                                                          |                             |     |           |  |  |  |  |

|------------------------------------------------------|-----|--------------------------------------------------------------------------|-----------------------------|-----|-----------|--|--|--|--|

| Address                                              | +0  | +1                                                                       | +2                          | +3  | Block     |  |  |  |  |

| 007078н WA09 [R/W] WXXXX XXXXXXX XXXXXX WD09 [R/W] W |     |                                                                          |                             |     |           |  |  |  |  |

| 00707Сн                                              | XXX |                                                                          |                             |     |           |  |  |  |  |

| 007080н                                              |     |                                                                          | [R/W] W<br>XXXXXXX XXXXXX   |     |           |  |  |  |  |

| 007084н                                              | XXX |                                                                          | [R/W] W<br>X XXXXXXXX XXXXX | xxx |           |  |  |  |  |

| 007088н                                              |     |                                                                          | [R/W] W<br>XXXXXXX XXXXXX   |     |           |  |  |  |  |

| 00708Сн                                              | XXX |                                                                          | [R/W] W<br>X XXXXXXXX XXXXX | xxx |           |  |  |  |  |

| 007090н                                              |     | WA12 [R/W] WXXXX XXXXXXXX XXXXXX WD12 [R/W] W XXXXXXXX XXXXXXXX XXXXXXXX |                             |     |           |  |  |  |  |

| 007094н                                              | XXX |                                                                          |                             |     |           |  |  |  |  |

| 007098н                                              |     | WA13 [R/W] W<br>XXXX XXXXXXXX XXXXXX                                     |                             |     |           |  |  |  |  |

| 00709Сн                                              | XXX |                                                                          | [R/W] W<br>X XXXXXXXX XXXXX | xxx |           |  |  |  |  |

| 0070А0н                                              |     |                                                                          | [R/W] W<br>XXXXXXX XXXXXX   |     |           |  |  |  |  |

| 0070А4н                                              | XXX |                                                                          | [R/W] W<br>X XXXXXXXX XXXXX | xxx |           |  |  |  |  |

| 0070А8н                                              |     |                                                                          | [R/W] W<br>XXXXXXX XXXXXX   |     |           |  |  |  |  |

| 0070АСн                                              | XXX |                                                                          | [R/W] W<br>X XXXXXXXX XXXXX | xxx |           |  |  |  |  |

| 0070В0н<br>to<br>0FFFFCн                             |     |                                                                          | _                           |     | (Reserved |  |  |  |  |

<sup>\*:</sup> The lower 16 bits (DTC15 to DTC0) of DMACA0 to DMACA4 cannot be accessed as bytes.

Notes: • Data is undefined in reserved or (—) area.

- Do not execute read modify write (RMW) instruction on registers having a write-only bit.

- The initial values are varied depending on the product series. Please refer to the hardware manual of MB91490 series for more details.

|                                  | Interrup        | number           | Interrupt          |                    | TBR default                  |  |

|----------------------------------|-----------------|------------------|--------------------|--------------------|------------------------------|--|

| Interrupt source                 | Decimal         | Hexa-<br>decimal | Interrupt<br>level | Offset             | address                      |  |

| OCU2/OCU3 (match)                | 61              | 3D               | ICR45              | 308н               | 000FFF08н                    |  |

| OCU4/OCU5 (match)                | 62              | 3E               | ICR46              | 304н               | 000FFF04н                    |  |

| Interrupt delay source bit       | 63              | 3F               | ICR47              | 300н               | 000FFF00н                    |  |

| System reserved (Used by REALOS) | 64              | 40               | _                  | 2FСн               | 000FFEFCн                    |  |

| System reserved (Used by REALOS) | 65              | 41               | _                  | 2F8н               | 000FFEF8н                    |  |

| System reserved                  | 66              | 42               | _                  | 2F4н               | 000FFEF4н                    |  |

| System reserved                  | 67              | 43               | _                  | 2F0н               | 000FFEF0н                    |  |

| System reserved                  | 68              | 44               | _                  | 2ЕСн               | 000FFEECн                    |  |

| System reserved                  | 69              | 45               | _                  | 2Е8н               | 000FFEE8н                    |  |

| System reserved                  | 70              | 46               | _                  | 2Е4н               | 000FFEE4н                    |  |

| System reserved                  | 71              | 47               | _                  | 2Е0н               | 000FFEE0н                    |  |

| System reserved                  | 72              | 48               | _                  | 2DC <sub>H</sub>   | 000FFEDCн                    |  |

| System reserved                  | 73              | 49               | _                  | 2D8н               | 000FFED8н                    |  |

| System reserved                  | 74              | 4A               | _                  | 2D4н               | 000FFED4н                    |  |

| System reserved                  | 75              | 4B               | _                  | 2D0н               | 000FFED0н                    |  |

| System reserved                  | 76              | 4C               | _                  | 2ССн               | 000FFECCн                    |  |

| System reserved                  | 77              | 4D               | _                  | 2С8н               | 000FFEC8н                    |  |

| System reserved                  | 78              | 4E               | _                  | 2С4н               | 000FFEC4н                    |  |

| System reserved                  | 79              | 4F               | _                  | 2С0н               | 000FFEC0н                    |  |

| Used by INT instruction          | 80<br>to<br>255 | 50<br>to<br>FF   | _                  | 2ВСн<br>to<br>000н | 000FFEBCн<br>to<br>000FFC00н |  |

#### **■ PIN STATUS IN EACH CPU STATE**

Terms used as the status of pins mean as follows.

- Input enabled

Means that the input function can be used.

- Input disabled Indicates that the input function cannot be used.

- Input fixed to "0"

A state of a pin, in which "0" is transmitted to internal circuitry, with the external input shut off by the input gate adjacent to the pin.

- Output Hi-Z

Means to place a pin in a high impedance state by disabling the pin driving transistor from driving.

- Preserving the previous state

Means to output the state existing immediately prior to entering this mode.

That is, to output according to an internal resource with an output when it is operating or to preserve an output when the output is provided, for example, as a port.

- Input enabled when external interrupt function selected and enabled Inputs are allowed only when the pin is configured as an external interrupt request input pin and the external interrupt request is enabled.

### • List of pin status

| • List of pin st |                 | During ini                                               | tialization                                                                  |                                          | In stop                                  | mode                                                  |

|------------------|-----------------|----------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------------------|

| Pin name         | Function        | INITX = "L"*1 or when Low voltage detection reset occurs | INITX = "H"*2<br>or when Low<br>voltage<br>detection<br>reset is<br>released | In sleep mode                            | HIZ = 0                                  | HIZ = 1                                               |

| NMIX             | NMIX            | Input enabled                                            | Input enabled                                                                | Input enabled                            | Input enabled                            | Input enabled                                         |

| P80 to P83       | INT0 to INT3    |                                                          |                                                                              |                                          |                                          | Output Hi-Z/                                          |

| P84              | INT4/PPG4       |                                                          |                                                                              |                                          |                                          | Input "0" fixed                                       |

| P85              | INT5/PPG5       | Output Hi-Z/                                             | Output Hi-Z/                                                                 | Innut anablad                            | Innut anablad                            | Input enabled                                         |

| P86              | INT6/PPG6       | Input disabled                                           | Input enabled                                                                | Input enabled                            | Input enabled                            | when interrupt<br>function<br>selected and<br>enabled |

| PA1, PA2         | ADTG1,<br>ADTG2 | Output Hi-Z/<br>Input disabled                           | Output Hi-Z/<br>Input enabled                                                | Retention of the immediately prior state | Retention of the immediately prior state | Output Hi-Z/<br>Input "0" fixed                       |

| PB4 to PB7       | AN1-0 to AN1-3  | Output Hi-Z/                                             | Output Hi-Z/<br>Input "0" fixed                                              | Retention of the immediately prior state | Retention of the                         | Output Hi-Z/                                          |

| PC0 to PC7       | AN2-0 to AN2-7  | Input disabled                                           |                                                                              |                                          | immediately prior state                  | Input "0" fixed                                       |

| PG0, PG3         | SCK0, SCK1      |                                                          |                                                                              | Retention of the immediately             | Retention of the immediately prior state |                                                       |

| PG1, PG4         | SIN0, SIN1      |                                                          |                                                                              |                                          |                                          |                                                       |

| PG2, PG5         | SOT0, SOT1      | Output Hi-Z/                                             | Output Hi-Z/                                                                 |                                          |                                          | Output Hi-Z/In-                                       |

| PH0              | SCK2            | Input disabled                                           | Input enabled                                                                | prior state                              |                                          | put "0" fixed                                         |

| PH1              | SIN2            |                                                          |                                                                              |                                          |                                          |                                                       |

| PH2              | SOT2            |                                                          |                                                                              |                                          |                                          |                                                       |

| PJ0, PJ2         | TINO, TIN1      | Output Hi-Z/                                             | Output Hi-Z/                                                                 | Retention of the                         | Retention of the                         | Output Hi-Z/In-                                       |

| PJ1, PJ3         | TOUT0,<br>TOUT1 | Input disabled                                           | Input enabled                                                                | immediately prior state                  | immediately prior state                  | put "0" fixed                                         |

| PL0              | AIN0            | 0                                                        | 0                                                                            | Retention of the                         | Retention of the                         | 0                                                     |

| PL1              | BIN0            | Output Hi-Z/<br>Input disabled                           | Output Hi-Z/<br>Input enabled                                                | immediately                              | immediately                              | Output Hi-Z/In-<br>put "0" fixed                      |

| PL2              | ZIN0            | par aloablod                                             |                                                                              | prior state                              | prior state                              | F31 0 111.00                                          |

| PP0 to PP3       | IC0 to IC3      |                                                          |                                                                              |                                          |                                          |                                                       |

| PP4              | CKI0            | Output Hi-Z/                                             | Output Hi-Z/                                                                 | Retention of the immediately             | Retention of the immediately             | Output Hi-Z/In-                                       |

| PP5              | DTTI0           | Input disabled                                           | Input enabled                                                                | prior state                              | prior state                              | put "0" fixed                                         |

| PQ0 to PQ5       | RTO0 to RTO5    |                                                          |                                                                              | -                                        | -                                        |                                                       |

<sup>\*1 :</sup> INITX = "L" : Indicates the pin status with INITX remaining at the "L" level.

$<sup>^*2</sup>$ : INITX = "H": Indicates the pin status existing immediately after INITX transition from "L" to "H" level.

### 4. Flash Memory Write/Erase Characteristics

| Parameter                               | Condition                                                   | Value |     |      | Unit  | Remarks                                                  |

|-----------------------------------------|-------------------------------------------------------------|-------|-----|------|-------|----------------------------------------------------------|

|                                         | Condition                                                   | Min   | Тур | Max  | Offic | neiliaiks                                                |

| Sector erase time<br>(8 Kbytes sectors) | $V_{CC} = 5.0 \text{ V},$ $T_{A} = +25 ^{\circ}\text{C}$    | _     | 0.5 | 2.0  | s     | Not including time for internal writing before deletion. |

| Word write time                         | $V_{CC} = 5.0 \text{ V},$ $T_A = +25 \text{ °C}$            | _     | 6   | 100  | μs    | Not including system-level overhead time.                |

| Chip erase time                         | $V_{CC} = 5.0 \text{ V},$<br>$T_{A} = +25 ^{\circ}\text{C}$ | _     | 1.8 | 29.5 | s     | Not including system-level overhead time.                |

| Erase/write cycle                       | _                                                           | 10000 |     | _    | cycle |                                                          |

| Flash memory data hold time             | _                                                           | 10    | _   | _    | year  |                                                          |

#### (2) PLL Oscillation stabilization time (LOCK UP TIME)

$(Vcc = 2.7 \text{ V to } 5.5 \text{ V}, Vss = AVSS10 = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter                                              | Symbol   | Pin Name | Condition | Va  | lue | Unit  |

|--------------------------------------------------------|----------|----------|-----------|-----|-----|-------|

| Parameter                                              | Syllibol | Pin Name | Condition | Min | Max | Ollit |

| PLL Oscillation stabilization wait time (LOCK UP TIME) | tLOCK*   | _        |           | 600 | _   | μs    |

<sup>\*:</sup> The length of time to wait for the PLL oscillations to stabilize.

#### (3) Reset Input Ratings

$(Vcc = 2.7 \text{ V to } 5.5 \text{ V}, Vss = AVSS10 = 0.0 \text{ V}, T_A = -40 \,^{\circ}\text{C to } +85 \,^{\circ}\text{C})$

|                                         |                                     |       |     | Value                                                                |      |    |

|-----------------------------------------|-------------------------------------|-------|-----|----------------------------------------------------------------------|------|----|

| Parameter                               | Parameter Symbol Pin Name Condition |       | Min | Max                                                                  | Unit |    |

| INITX input time<br>(at power-on)       |                                     |       |     | tpon + tstbl + Oscillation time of oscillator + tc × 2 <sup>13</sup> | _    | ns |

| INITX input time (at STOP)              | tintl                               | INITX | _   | Oscillation time of oscillator + tc × 10                             | _    | ns |

| INITX input time (other than the above) |                                     |       |     | tc×10                                                                | _    | ns |

Notes: • For tc (clock cycle time), refer to "(1) Clock Timing".

• For tpon and tstbl, refer to "(4) Power on Rise Time /Power-on Stabilization Time Ratings".

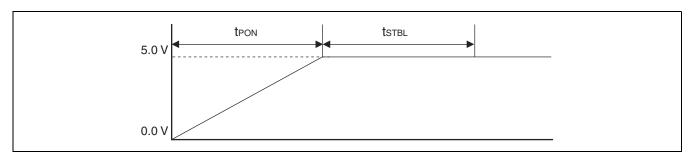

#### (4) Power on Rise Time /Power-on Stabilization Time Ratings

$(V_{SS} = AVSS10 = 0.0 \text{ V}, T_{A} = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C})$

| Parameter                   | Symbol Pin Name Co |     | Condition | Value |     | Unit  |

|-----------------------------|--------------------|-----|-----------|-------|-----|-------|

| raiametei                   |                    |     | Condition | Min   | Max | Ollit |

| Power on rise time          | <b>t</b> PON       | VCC |           | 600   |     | μs    |

| power-on stabilization time | <b>t</b> stbl      | VCC |           | 600   | _   | μs    |

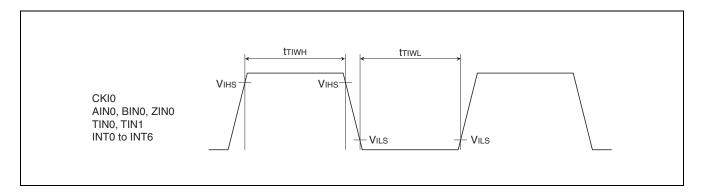

### (6) Free-run Timer Clock, Up/Down Counter, Base Timer, and External Interrupt Input Timing

(Vcc = 2.7 V to 5.5 V, Vss = AVSS10 = 0.0 V,  $T_A = -40$  °C to +85 °C)

| Parameter                              | Symbol | Pin Name             | Condition | Va        | Unit |    |

|----------------------------------------|--------|----------------------|-----------|-----------|------|----|

| Parameter                              |        |                      | Condition | Min       | Max  |    |

| Free-run timer input clock pulse width |        | CKI0                 |           | 4 × tcycp | _    | ns |

| Up-down counter input pulse width      | tтıwн  | AIN0<br>BIN0<br>ZIN0 |           | 4 × tcycp | _    | ns |

| Base timer input pulse width           | ttiwL  | TINO, TIN1           |           | 4 × tcycp | _    | ns |

| External interrupt                     |        | INT0 to INT6         |           | 4 × tcycp | _    | ns |

| input pulse width                      |        |                      |           | 1.0*      | _    | μs |

<sup>\*:</sup> In stop mode

Note: tcycp indicates the peripheral clock cycle time.

#### b. Slave Mode

$(Vcc = 2.7 \text{ V to } 5.5 \text{ V}, Vss = AVSS10 = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Parameter                                                                              | Sym-<br>bol    | Pin<br>name         | Condition                        | Standard Mode |              | Fast Mode*3  |              | Unit | Damanta                                        |

|----------------------------------------------------------------------------------------|----------------|---------------------|----------------------------------|---------------|--------------|--------------|--------------|------|------------------------------------------------|

|                                                                                        |                |                     |                                  | Min           | Max          | Min          | Max          | Unit | Remarks                                        |

| SCL clock frequency                                                                    | fscL           | SDAn, R=<br>SCLn C= | R=1 kΩ,<br>C=50 pF* <sup>4</sup> | 0             | 100          | 0            | 400          | kHz  |                                                |

| "L" width of the SCL clock                                                             | tLOW           |                     |                                  | 4.7           | _            | 1.3          | _            | μs   |                                                |

| "H" width of the SCL clock                                                             | <b>t</b> HIGH  |                     |                                  | 4.0           | _            | 0.6          | _            | μs   |                                                |

| Bus free time<br>between STOP<br>and START<br>conditions                               | tвиs           |                     |                                  | 4.7           | _            | 1.3          | _            | μs   |                                                |

| $\begin{array}{c} SCL \downarrow \to SDA \\ output \ delay \ time \end{array}$         | <b>t</b> DLDAT |                     |                                  | _             | 5 × tcycp *1 | _            | 5 × tcycp *1 | ns   |                                                |

| Setup time for a repeated START condition SCL $\uparrow \rightarrow$ SDA $\downarrow$  | <b>t</b> susta |                     |                                  | 4.7           | _            | 0.6          | _            | μs   |                                                |

| Hold time for a repeated START condition SDA $\downarrow \rightarrow$ SCL $\downarrow$ | <b>t</b> hdsta |                     |                                  | 4.0           | _            | 0.6          | _            | μs   | The first clock pulse is generated after this. |

| Setup time for STOP condition SCL $\uparrow \rightarrow$ SDA $\uparrow$                | <b>t</b> susto |                     |                                  | 4.0           | _            | 0.6          |              | μs   |                                                |

| SDA Data input<br>hold time<br>(vs. SCL ↓)                                             | <b>t</b> hddat |                     |                                  | 2 × tcycp *1  | _            | 2 × tcycp *1 | _            | μs   |                                                |

| SDA Data input<br>setup time<br>(vs. SCL ↑)                                            | <b>t</b> sudat |                     |                                  | 250           | _            | 100 *2       |              | ns   |                                                |

<sup>\*1:</sup> toycp indicates the peripheral clock cycle time.

<sup>\*2 :</sup> A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement  $t_{SUDAT} \ge 250$  ns must then be met.

If a device does not extend the "L" period of the SCL signal, it is necessary to output the next piece of data to the SDA line 1250 ns (SDA and SCL rising Max time + tsudat) before the SCL line is released.

<sup>\*3:</sup> For use at over 100 kHz, set the peripheral clock to at least 6 MHz.

<sup>\*4:</sup> R and C are pull-up resistance and load capacitance of the SCL and SDA lines.

#### (Continued)

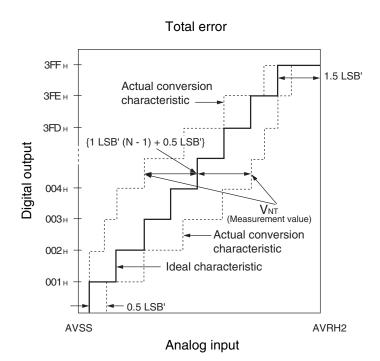

$$1 LSB' (ideal value) = \frac{AVRH2 - AVSS}{1024} [V]$$

$$Total error of digital output N = \frac{V_{NT} - \{1 LSB' \times (N-1) + 0.5 LSB'\}}{1 LSB'}$$

N : A/D converter digital output value

$V_{NT}$ : Voltage at which digital output changes from (N + 1)  $_{H}$  to N $_{H}$ .

Vor' (ideal value) = AVSS + 0.5 LSB' [V] VFST' (ideal value) = AVRH2 - 1.5 LSB' [V]