Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 10-Core                                                |

| Speed                      | 2000MIPS                                                      |

| Connectivity               | USB                                                           |

| Peripherals                | -                                                             |

| Number of I/O              | 81                                                            |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | -                                                             |

| RAM Size                   | 512K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xu210-512-tq128-c20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

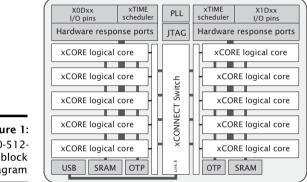

# 1 xCORE Multicore Microcontrollers

The xCORE-200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

Figure 1: XU210-512-TQ128 block diagram

Key features of the XU210-512-TQ128 include:

- ► **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 6.2

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 6.5

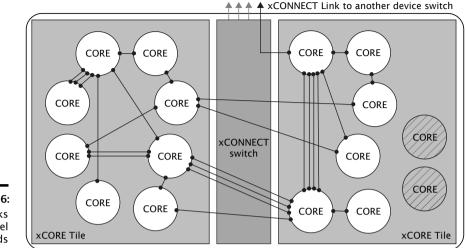

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 6.6

-XM()S

Figure 6: Switch, links and channel ends

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-U Link Performance and Design Guide, X2999.

# 7 PLL

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock. The initial PLL multiplication value is shown in Figure 7:

Figure 7: The initial PLL multiplier values

| Z.<br>LL | Oscillator | Tile Boot   | PLL Ratio | PLL : | settin | gs |

|----------|------------|-------------|-----------|-------|--------|----|

| er       | Frequency  | Frequency   |           | OD    | F      | R  |

| es       | 9-25 MHz   | 144-400 MHz | 16        | 1     | 63     | 0  |

Figure 7 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

*OD*, *F* and *R* must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The *OD*, *F*, and *R* values can be modified by writing to the digital node PLL configuration register.

If the USB PHY is used, then either a 24 MHz or 12 MHz oscillator must be used.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

#### 8.1 Boot from QSPI master

If set to boot from QSPI master, the processor enables the six pins specified in Figure 10, and drives the SPI clock at 50 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

|            | Pin        | Signal | Description  |

|------------|------------|--------|--------------|

|            | X0D01      | SS     | Slave Select |

| Figure 10: | X0D04X0D07 | SPIO   | Data         |

| QSPI pins  | X0D10      | SCLK   | Clock        |

The xCORE Tile expects each byte to be transferred with the *least-significant nibble first*. Programmers who write bytes into an QSPI interface using the most significant nibble first may have to reverse the nibbles in each byte of the image stored in the QSPI device.

The pins used for QSPI boot are hardcoded in the boot ROM and cannot be changed. If required, an QSPI boot program can be burned into OTP that uses different pins.

#### 8.2 Boot from SPI master

If set to boot from SPI master, the processor enables the four pins specified in Figure 11, and drives the SPI clock at 2.5 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

Pin Signal Description X0D00 MISO Master In Slave Out (Data) Figure 11: X0D01 SS Slave Select SPI master X0D10 SCLK Clock pins X0D11 MOSI Master Out Slave In (Data)

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. Programmers who write bytes into an SPI interface using the most significant bit first may have to reverse the bits in each byte of the image stored in the SPI device.

If a large boot image is to be read in, it is faster to first load a small boot-loader that reads the large image using a faster SPI clock, for example 50 MHz or as fast as the flash device supports.

# 13 DC and Switching Characteristics

| Symbol     | Parameter                                     | MIN   | ТҮР  | MAX   | UNITS | Notes |

|------------|-----------------------------------------------|-------|------|-------|-------|-------|

| VDD        | Tile DC supply voltage                        | 0.95  | 1.00 | 1.05  | V     |       |

| VDDIOL     | I/O supply voltage                            | 3.135 | 3.30 | 3.465 | V     |       |

| VDDIOR     | I/O supply voltage                            | 3.135 | 3.30 | 3.465 | V     |       |

| VDDIOT 3v3 | I/O supply voltage                            | 3.135 | 3.30 | 3.465 | V     |       |

| VDDIOT 2v5 | I/O supply voltage                            | 2.375 | 2.50 | 2.625 | V     |       |

| USB_VDD    | USB tile DC supply voltage                    | 0.95  | 1.00 | 1.05  | V     |       |

| VDD33      | Peripheral supply                             | 3.135 | 3.30 | 3.465 | V     |       |

| PLL_AVDD   | PLL analog supply                             | 0.95  | 1.00 | 1.05  | V     |       |

| Cl         | xCORE Tile I/O load<br>capacitance            |       |      | 25    | pF    |       |

| Та         | Ambient operating<br>temperature (Commercial) | 0     |      | 70    | °C    |       |

|            | Ambient operating<br>temperature (Industrial) | -40   |      | 85    | °C    |       |

| Тј         | Junction temperature                          |       |      | 125   | °C    |       |

| Tstg       | Storage temperature                           | -65   |      | 150   | °C    |       |

### 13.1 Operating Conditions

Figure 21: Operating conditions

### 13.2 DC Characteristics, VDDIO=3V3

| Symbol | Parameter                                | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|------------------------------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage                       | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage                        | -0.30 |     | 0.70 | V     | А     |

| V(OH)  | Output high voltage                      | 2.20  |     |      | V     | B, C  |

| V(OL)  | Output low voltage                       |       |     | 0.40 | V     | B, C  |

| I(PU)  | Internal pull-up current (Vin=0V)        | -100  |     |      | μA    | D     |

| I(PD)  | Internal pull-down current<br>(Vin=3.3V) |       |     | 100  | μA    | D     |

| I(LC)  | Input leakage current                    | -10   |     | 10   | μA    |       |

Figure 22: DC characteristics

A All pins except power supply pins.

B Pins X1D40, X1D41, X1D42, X1D43, X1D26, and X1D27 are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry. In order to pull the pin to the opposite state, a 4K7 resistor is recommended to overome the internal pull current.

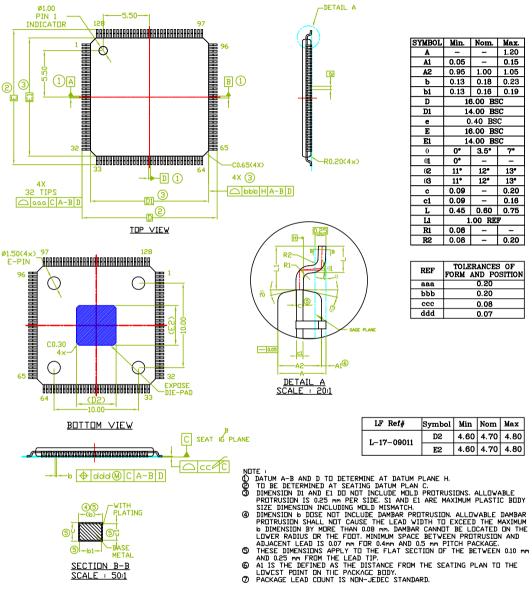

#### 14 **Package Information**

| INDOP      | Min.      | NOIL.   | max. |  |

|------------|-----------|---------|------|--|

| A          | -         | -       | 1.20 |  |

| A1         | 0.05      | -       | 0.15 |  |

| A2         | 0.95      | 1.00    | 1.05 |  |

| đ          | 0.13      | 0.18    | 0.23 |  |

| b1         | 0.13      | 0.16    | 0.19 |  |

| D          | 10        | 3.00 BS | SC   |  |

| D1         | 14        | 4.00 BS | SC . |  |

| e          | 0.40 BSC  |         |      |  |

| E          | 16.00 BSC |         |      |  |

| El         | 14.00 BSC |         |      |  |

| θ          | 0"        | 3.5°    | 7°   |  |

| <b>61</b>  | 0*        | -       | -    |  |

| 62         | 11•       | 12*     | 13*  |  |

| 6 <b>3</b> | 11*       | 12*     | 13*  |  |

| с          | 0.09      | -       | 0.20 |  |

| c1         | 0.09      | -       | 0.16 |  |

| L          | 0.45      | 0.60    | 0.75 |  |

| LI         | 1.00 REF  |         |      |  |

| R1         | 0.08      | -       | -    |  |

| R2         | 0.08      | -       | 0.20 |  |

|            |           |         |      |  |

| REF | TOLERANCES OF<br>FORM AND POSITION |

|-----|------------------------------------|

| aaa | 0.20                               |

| bbb | 0.20                               |

| ccc | 0.08                               |

| ddd | 0.07                               |

| LF Ref#    | Symbol | Min  | Nom  | Max  |

|------------|--------|------|------|------|

| L-17-09011 | D2     | 4.60 | 4.70 | 4.80 |

|            | E2     | 4.60 | 4.70 | 4.80 |

XS2-U10A-512-TQ128

-XMOS

A write message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | data | control-token |

|---------------|------------------------|-----------------|-------|------|---------------|

| 36            | channel-end identifier | register number | size  |      | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | control-token |

|---------------|------------------------|-----------------|-------|---------------|

| 37            | channel-end identifier | register number | size  | 1             |

The response to the read message comprises either control token 3, data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

### B.1 RAM base address: 0x00

This register contains the base address of the RAM. It is initialized to 0x00040000.

**0x00**: RAM base address

| 0: | Bits | Perm | Init | Description                                |

|----|------|------|------|--------------------------------------------|

| se | 31:2 | RW   |      | Most significant 16 bits of all addresses. |

| 55 | 1:0  | RO   | -    | Reserved                                   |

### B.2 Vector base address: 0x01

Base address of event vectors in each resource. On an interrupt or event, the 16 most significant bits of the destination address are provided by this register; the least significant 16 bits come from the event vector.

0x01: Vector base address

|   | Bits  | Perm | Init | Description                      |

|---|-------|------|------|----------------------------------|

| 2 | 31:18 | RW   |      | The event and interrupt vectors. |

| 5 | 17:0  | RO   | -    | Reserved                         |

### B.3 xCORE Tile control: 0x02

Register to control features in the xCORE tile

### **B.25** Data breakpoint control register: 0x70 ... 0x73

This set of registers controls each of the four data watchpoints.

|        | Bits  | Perm | Init | Description                                                                                              |

|--------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|        | 31:24 | RO   | -    | Reserved                                                                                                 |

| _      | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| :      | 15:3  | RO   | -    | Reserved                                                                                                 |

| a<br>t | 2     | DRW  | 0    | When 1 the breakpoints will be be triggered on loads.                                                    |

| l      | 1     | DRW  | 0    | Determines the break condition: $0 = A AND B$ , $1 = A OR B$ .                                           |

| r      | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

0x70 .. 0x73: Data breakpoint control register

### B.26 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

0x80 .. 0x83: Resources breakpoint mask

| burces<br>kpoint | Bits | Perm | Init | Description |

|------------------|------|------|------|-------------|

| mask             | 31:0 | DRW  |      | Value.      |

### B.27 Resources breakpoint value: 0x90 .. 0x93

This set of registers contains the value for the four resource watchpoints.

0x90 .. 0x93: Resources breakpoint value

| urces<br>point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| /alue          | 31:0 | DRW  |      | Value.      |

### B.28 Resources breakpoint control register: 0x9C .. 0x9F

This set of registers controls each of the four resource watchpoints.

-XMOS

XS2-U10A-512-TQ128

|                | Bits  | Perm | Init | Description                                        |

|----------------|-------|------|------|----------------------------------------------------|

|                | 31:24 | CRO  |      | Processor ID of this XCore.                        |

| 0x00:          | 23:16 | CRO  |      | Number of the node in which this XCore is located. |

| Device         | 15:8  | CRO  |      | XCore revision.                                    |

| identification | 7:0   | CRO  |      | XCore version.                                     |

### C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | CRO  |      | Number of channel ends.  |

| 23:16 | CRO  |      | Number of the locks.     |

| 15:8  | CRO  |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

0x01: xCORE Tile description 1

### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

|      | Bits  | Perm | Init | Description             |

|------|-------|------|------|-------------------------|

| :02: | 31:16 | RO   | -    | Reserved                |

| Tile | 15:8  | CRO  |      | Number of clock blocks. |

| n 2  | 7:0   | CRO  |      | Number of timers.       |

### C.4 Control PSwitch permissions to debug registers: 0x04

-XMOS-

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

### C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

| Bits | Perm | Init | Description                                 |

|------|------|------|---------------------------------------------|

| 31:2 | RO   | -    | Reserved                                    |

| 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

| 0    | CRW  | 0    | Request a debug interrupt on the processor. |

### C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |  |

|-------|------|------|---------------------------------------------------------------|--|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |  |

| 30:16 | RO   | -    | Reserved                                                      |  |

| 15:0  | CRW  | 0    | Clock divider.                                                |  |

### C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

-XMOS

48

# **D** Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RO   | Device identification                 |

| 0x01      | RO   | System switch description             |

| 0x04      | RW   | Switch configuration                  |

| 0x05      | RW   | Switch node identifier                |

| 0x06      | RW   | PLL settings                          |

| 0x07      | RW   | System switch clock divider           |

| 0x08      | RW   | Reference clock                       |

| 0x09      | R    | System JTAG device ID register        |

| 0x0A      | R    | System USERCODE register              |

| 0x0C      | RW   | Directions 0-7                        |

| 0x0D      | RW   | Directions 8-15                       |

| 0x10      | RW   | Reserved                              |

| 0x11      | RW   | Reserved.                             |

| 0x1F      | RO   | Debug source                          |

| 0x20 0x28 | RW   | Link status, direction, and network   |

| 0x40 0x47 | RO   | PLink status and network              |

| 0x80 0x88 | RW   | Link configuration and initialization |

| 0xA0 0xA7 | RW   | Static link configuration             |

Figure 36: Summary

### D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|             | Bits  | Perm | Init | Description                                       |

|-------------|-------|------|------|---------------------------------------------------|

|             | 31:24 | RO   | -    | Reserved                                          |

| 0x00:       | 23:16 | RO   |      | Sampled values of BootCtl pins on Power On Reset. |

| Device      | 15:8  | RO   |      | SSwitch revision.                                 |

| ntification | 7:0   | RO   |      | SSwitch version.                                  |

-XMOS<sup>®</sup>

ident

| Bits  | Perm | Init | Description                                     |

|-------|------|------|-------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose dimension is F. |

| 27:24 | RW   | 0    | The direction for packets whose dimension is E. |

| 23:20 | RW   | 0    | The direction for packets whose dimension is D. |

| 19:16 | RW   | 0    | The direction for packets whose dimension is C. |

| 15:12 | RW   | 0    | The direction for packets whose dimension is B. |

| 11:8  | RW   | 0    | The direction for packets whose dimension is A. |

| 7:4   | RW   | 0    | The direction for packets whose dimension is 9. |

| 3:0   | RW   | 0    | The direction for packets whose dimension is 8. |

0x0D: Directions 8-15

### D.12 Reserved: 0x10

Reserved.

|          | 31:2 | F |

|----------|------|---|

| 0x10:    | 1    | R |

| Reserved | 0    | F |

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:2 | RO   | -    | Reserved    |

| 1    | RW   | 0    | Reserved.   |

| 0    | RW   | 0    | Reserved.   |

## D.13 Reserved.: 0x11

Reserved.

0x11: Reserved.

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:2 | RO   | -    | Reserved    |

| 1    | RW   | 0    | Reserved.   |

| 0    | RW   | 0    | Reserved.   |

### D.14 Debug source: 0x1F

Contains the source of the most recent debug event.

### D.18 Static link configuration: 0xA0 .. 0xA7

These registers are used for static (ie, non-routed) links. When a link is made static, all traffic is forwarded to the designated channel end and no routing is attempted. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits | Perm | Init | Description                                                                                     |

|------|------|------|-------------------------------------------------------------------------------------------------|

| 31   | RW   | 0    | Enable static forwarding.                                                                       |

| 30:9 | RO   | -    | Reserved                                                                                        |

| 8    | RW   | 0    | The destination processor on this node that packets received in static mode are forwarded to.   |

| 7:5  | RO   | -    | Reserved                                                                                        |

| 4:0  | RW   | 0    | The destination channel end on this node that packets received in static mode are forwarded to. |

**0xA0 .. 0xA7:** Static link configuration

# E USB Node Configuration

The USB node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number | Perm | Description                    |

|--------|------|--------------------------------|

| 0x00   | RO   | Device identification register |

| 0x04   | RW   | Node configuration register    |

| 0x05   | RW   | Node identifier                |

| 0x51   | RW   | System clock frequency         |

| 0x80   | RW   | Link Control and Status        |

Figure 37: Summary

### E.1 Device identification register: 0x00

This register contains version information, and information on power-on behavior.

0x00: Device identification register

| Bits  | Perm | Init | Description                      |

|-------|------|------|----------------------------------|

| 31:24 | RO   | 0x0F | Chip identifier                  |

| 23:16 | RO   | -    | Reserved                         |

| 15:8  | RO   | 0x02 | Revision number of the USB block |

| 7:0   | RO   | 0x00 | Version number of the USB block  |

#### E.2 Node configuration register: 0x04

This register is used to set the communication model to use (1 or 3 byte headers), and to prevent any further updates.

0x04: Node configuration register

|           | Bits | Perm | Init | Description                                                                                          |

|-----------|------|------|------|------------------------------------------------------------------------------------------------------|

| 04:<br>de | 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |

| on        | 30:1 | RO   | -    | Reserved                                                                                             |

| er        | 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |

| Bits | Perm | Init | Description                                        |

|------|------|------|----------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                           |

| 7    | RW   | 0    | Set to 1 to switch UIFM to EXTVBUSIND mode.        |

| 6    | RW   | 0    | Set to 1 to switch UIFM to DRVVBUSEXT mode.        |

| 5    | RO   | -    | Reserved                                           |

| 4    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ CHRGVBUS mode.    |

| 3    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DISCHRGVBUS mode. |

| 2    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DMPULLDOWN mode.  |

| 1    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DPPULLDOWN mode.  |

| 0    | RW   | 0    | Set to 1 to switch UIFM to IDPULLUP mode.          |

**0x10:** UIFM on-the-go control

## F.6 UIFM on-the-go flags: 0x14

Status flags used for on-the-go negotiation

| Bits | Perm | Init | Description                  |

|------|------|------|------------------------------|

| 31:6 | RO   | -    | Reserved                     |

| 5    | RO   | 0    | Value of UTMI+ Bvalid flag.  |

| 4    | RO   | 0    | Value of UTMI+ IDGND flag.   |

| 3    | RO   | 0    | Value of UTMI+ HOSTDIS flag. |

| Ĩ    | RO   | 0    | Value of UTMI+ VBUSVLD flag. |

| 1    | RO   | 0    | Value of UTMI+ SESSVLD flag. |

| (    | RO   | 0    | Value of UTMI+ SESSEND flag. |

-XMOS°

**0x14:** UIFM on-the-go flags

| Bits | Perm | Init | Description                                       |

|------|------|------|---------------------------------------------------|

| 31:7 | RO   | -    | Reserved                                          |

| 6    | RO   | 0    | 1 if UIFM is in UTMI+ RXRCV mode.                 |

| 5    | RO   | 0    | 1 if UIFM is in UTMI+ RXDM mode.                  |

| 4    | RO   | 0    | 1 if UIFM is in UTMI+ RXDP mode.                  |

| 3    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ TXSE0 mode.      |

| 2    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ TXDATA mode.     |

| 1    | RW   | 1    | Set to 0 to switch UIFM to UTMI+ TXENABLE mode.   |

| 0    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ FSLSSERIAL mode. |

### F.7 UIFM Serial Control: 0x18

**0x18:** UIFM Serial Control

### F.8 UIFM signal flags: 0x1C

Set of flags that monitor line and error states. These flags normally clear on the next packet, but they may be made sticky by using PER\_UIFM\_FLAGS\_STICKY, in which they must be cleared explicitly.

| Bits | Perm | Init | Description                                                                                                           |

|------|------|------|-----------------------------------------------------------------------------------------------------------------------|

| 31:7 | RO   | -    | Reserved                                                                                                              |

| 6    | RW   | 0    | Set to 1 when the UIFM decodes a token successfully (e.g. it passes CRC5, PID check and has matching device address). |

| 5    | RW   | 0    | Set to 1 when linestate indicates an SEO symbol.                                                                      |

| 4    | RW   | 0    | Set to 1 when linestate indicates a K symbol.                                                                         |

| 3    | RW   | 0    | Set to 1 when linestate indicates a J symbol.                                                                         |

| 2    | RW   | 0    | Set to 1 if an incoming datapacket fails the CRC16 check.                                                             |

| 1    | RW   | 0    | Set to the value of the UTMI_RXACTIVE input signal.                                                                   |

| 0    | RW   | 0    | Set to the value of the UTMI_RXERROR input signal                                                                     |

**0x1C:** UIFM signal flags

### F.9 UIFM Sticky flags: 0x20

These bits define the sticky-ness of the bits in the UIFM IFM FLAGS register. A 1 means that bit will be sticky (hold its value until a 1 is written to that bitfield), or normal, in which case signal updates to the UIFM IFM FLAGS bits may be over-written by subsequent changes in those signals.

**0x20:** UIFM Sticky flags

| Bits | Perm | Init | Description               |

|------|------|------|---------------------------|

| 31:7 | RO   | -    | Reserved                  |

| 6:0  | RW   | 0    | Stickyness for each flag. |

### F.10 UIFM port masks: 0x24

Set of masks that identify how port 1N, port 1O and port 1P are affected by changes to the flags in FLAGS

| Bits  | Perm | Init | Description                                                                                                                                         |  |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:24 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1?. If any flag listed in this bitmask is high, port 1? will be high. |  |

| 23:16 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6: contribute to port 1P. If any flag listed in this bitmask is hig port 1P will be high.     |  |

| 15:8  | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 10. If any flag listed in this bitmask is high, port 10 will be high. |  |

| 7:0   | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1N. If any flag listed in this bitmask is high, port 1N will be high. |  |

**0x24:** UIFM port masks

### F.11 UIFM SOF value: 0x28

USB Start-Of-Frame counter

**0x28:** UIFM SOF value

| Bits  | Perm | Init | Description                             |

|-------|------|------|-----------------------------------------|

| 31:11 | RO   | -    | Reserved                                |

| 10:8  | RW   | 0    | Most significant 3 bits of SOF counter  |

| 7:0   | RW   | 0    | Least significant 8 bits of SOF counter |

-XMOS

### F.12 UIFM PID: 0x2C

The last USB packet identifier received

68

|          | Bits | Perm | Init | Description                     |

|----------|------|------|------|---------------------------------|

| 0x2C:    | 31:4 | RO   | -    | Reserved                        |

| UIFM PID | 3:0  | RO   | 0    | Value of the last received PID. |

#### F.13 UIFM Endpoint: 0x30

The last endpoint seen

**0x30:** UIFM Endpoint

|         | Bits | Perm | Init | Description                           |

|---------|------|------|------|---------------------------------------|

| 0:      | 31:5 | RO   | -    | Reserved                              |

| и.<br>И | 4    | RO   | 0    | 1 if endpoint contains a valid value. |

| t       | 3:0  | RO   | 0    | A copy of the last received endpoint. |

### F.14 UIFM Endpoint match: 0x34

This register can be used to mark UIFM endpoints as special.

**0x34:** UIFM Endpoint match

| Bits  | Perm | Init | Description                                                                                                                             |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                                |

| 15:0  | RW   | 0    | This register contains a bit for each endpoint. If its bit is set, the endpoint will be supplied on the RX port when ORed with $0x10$ . |

### F.15 OTG Flags mask: 0x38

**0x38:** OTG Flags mask

| 0x38:<br>Flags | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| mask           | 31:0 | RW   | 0    | Data        |

### F.16 UIFM power signalling: 0x3C

|                   | Bits | Perm | Init | Description |

|-------------------|------|------|------|-------------|

| 0x3C:             | 31:9 | RO   | -    | Reserved    |

| <b>UIFM</b> power | 8    | RW   | 0    | Valid       |

| signalling        | 7:0  | RW   | 0    | Data        |

# G JTAG, xSCOPE and Debugging

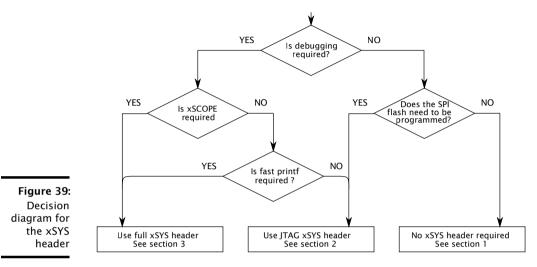

If you intend to design a board that can be used with the XMOS toolchain and xTAG debugger, you will need an xSYS header on your board. Figure 39 shows a decision diagram which explains what type of xSYS connectivity you need. The three subsections below explain the options in detail.

### G.1 No xSYS header

The use of an xSYS header is optional, and may not be required for volume production designs. However, the XMOS toolchain expects the xSYS header; if you do not have an xSYS header then you must provide your own method for writing to flash/OTP and for debugging.

### G.2 JTAG-only xSYS header

The xSYS header connects to an xTAG debugger, which has a 20-pin 0.1" female IDC header. The design will hence need a male IDC header. We advise to use a boxed header to guard against incorrect plug-ins. If you use a 90 degree angled header, make sure that pins 2, 4, 6, ..., 20 are along the edge of the PCB.

Connect pins 4, 8, 12, 16, 20 of the xSYS header to ground, and then connect:

$\mathbf{X}$  M()S

- ▶ TDI to pin 5 of the xSYS header

- TMS to pin 7 of the xSYS header

- TCK to pin 9 of the xSYS header

- TDO to pin 13 of the xSYS header

71

# J Associated Design Documentation

| Document Title                                 | Information                               | Document Number |

|------------------------------------------------|-------------------------------------------|-----------------|

| Estimating Power Consumption For XS1-U Devices | Power consumption                         |                 |

| Programming XC on XMOS Devices                 | Timers, ports, clocks, cores and channels | X9577           |

| xTIMEcomposer User Guide                       | Compilers, assembler and linker/mapper    | X3766           |

|                                                | Timing analyzer, xScope, debugger         |                 |

|                                                | Flash and OTP programming utilities       |                 |

# **K** Related Documentation

| Document Title                                  | Information                         | Document Number |

|-------------------------------------------------|-------------------------------------|-----------------|

| The XMOS XS1 Architecture                       | ISA manual                          | X7879           |

| XS1 Port I/O Timing                             | Port timings                        | X5821           |

| xCONNECT Architecture                           | Link, switch and system information | X4249           |

| XS1-U Link Performance and Design<br>Guidelines | Link timings                        |                 |

| XS1-U Clock Frequency Control                   | Advanced clock control              |                 |