# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Active                                                          |

| Core Processor             | XCore                                                           |

| Core Size                  | 32-Bit 12-Core                                                  |

| Speed                      | 800MIPS                                                         |

| Connectivity               | Configurable                                                    |

| Peripherals                | -                                                               |

| Number of I/O              | 84                                                              |

| Program Memory Size        | 128KB (32K x 32)                                                |

| Program Memory Type        | SRAM                                                            |

| EEPROM Size                | -                                                               |

| RAM Size                   | -                                                               |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | External                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 124-TFQFN Dual Rows, Exposed Pad                                |

| Supplier Device Package    | 124-QFN DualRow (10x10)                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-l12a-128-qf124-i8 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4 Signal Description

This section lists the signals and I/O pins available on the XS1-L12A-128-QF124. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

PD/PU: The IO pin a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled.

|          | Power pins (6)        |      |            |  |  |  |  |  |  |  |  |  |

|----------|-----------------------|------|------------|--|--|--|--|--|--|--|--|--|

| Signal   | Function              | Туре | Properties |  |  |  |  |  |  |  |  |  |

| GND      | Digital ground        | GND  |            |  |  |  |  |  |  |  |  |  |

| OTP_VCC  | OTP power supply      | PWR  |            |  |  |  |  |  |  |  |  |  |

| PLL_AGND | Analog ground for PLL | GND  |            |  |  |  |  |  |  |  |  |  |

| PLL_AVDD | Analog PLL power      | PWR  |            |  |  |  |  |  |  |  |  |  |

| VDD      | Digital tile power    | PWR  |            |  |  |  |  |  |  |  |  |  |

| VDDIO    | Digital I/O power     | PWR  |            |  |  |  |  |  |  |  |  |  |

ST: The IO pin has a Schmitt Trigger on its input.

| Clocks pins (2) |                     |       |            |  |  |  |  |  |  |  |

|-----------------|---------------------|-------|------------|--|--|--|--|--|--|--|

| Signal          | Function            | Туре  | Properties |  |  |  |  |  |  |  |

| CLK             | PLL reference clock | Input | PD, ST     |  |  |  |  |  |  |  |

| MODE[4:0]       | Boot mode select    | Input | PU, ST     |  |  |  |  |  |  |  |

|         | JTAG pins (7)      |        |            |

|---------|--------------------|--------|------------|

| Signal  | Function           | Туре   | Properties |

| DEBUG_N | Multi-chip debug   | I/O    | PU         |

| RST_N   | Global reset input | Input  | PU, ST     |

| тск     | Test clock         | Input  | PU, ST     |

| TDI     | Test data input    | Input  | PU, ST     |

| TDO     | Test data output   | Output | PD, OT     |

| TMS     | Test mode select   | Input  | PU, ST     |

| TRST_N  | Test reset input   | Input  | PU, ST     |

| I/O pins (84) |                 |      |                                  |  |  |  |  |  |  |

|---------------|-----------------|------|----------------------------------|--|--|--|--|--|--|

| Signal        | Function        | Туре | Properties                       |  |  |  |  |  |  |

| X0D00         | 1A <sup>0</sup> | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |  |  |  |  |  |

-XMOS<sup>®</sup>

6

*OD*, *F* and *R* must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The *OD*, *F*, and *R* values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the XS1-L Clock Frequency Control document, X1433.

## 7 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins are high impedance. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After 15-150  $\mu$ s (depending on the input clock), all GPIO pins have their internal pull-resistor enabled, and the processor boots at a clock speed that depends on MODE0 and MODE1.

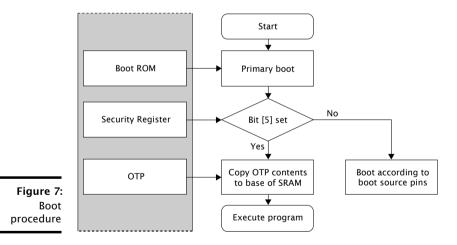

The xCORE Tile boot procedure is illustrated in Figure 7. In normal usage, MODE[4:2] controls the boot source according to the table in Figure 8. If bit 5 of the security register (*see* §8.1) is set, the device boots from OTP.

The boot image has the following format:

- A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

- A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

-XM()S

14

Figure 8: Boot source pins

| MODE | MODE | MODE | Boot Source                                                                                              |

|------|------|------|----------------------------------------------------------------------------------------------------------|

| [4]  | [3]  | [2]  |                                                                                                          |

| Х    | 0    | 0    | None: Device waits to be booted via JTAG                                                                 |

| Х    | 0    | 1    | Reserved                                                                                                 |

| 0    | 1    | 0    | Tile0 boots from link B, Tile1 from channel end 0 via Tile0                                              |

| 0    | 1    | 1    | Tile0 boots from SPI, Tile1 from channel end 0 via Tile0                                                 |

| 1    | 1    | 0    | Tile0 and Tile1 independently enable link B and internal links (E, F, G, H), and boot from channel end 0 |

| 1    | 1    | 1    | Tile0 and Tile 1 boot from SPI independently                                                             |

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

#### 7.1 Boot from SPI master

If set to boot from SPI master, the processor enables the four pins specified in Figure 9, and drives the SPI clock at 2.5 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

|            | Pin   | Signal | Description                |

|------------|-------|--------|----------------------------|

|            | X0D00 | MISO   | Master In Slave Out (Data) |

| Figure 9:  | X0D01 | SS     | Slave Select               |

| SPI master | X0D10 | SCLK   | Clock                      |

| pins       | X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. Programmers who write bytes into an SPI interface using the most significant bit first may have to reverse the bits in each byte of the image stored in the SPI device.

If a large boot image is to be read in, it is faster to first load a small boot-loader that reads the large image using a faster SPI clock, for example 50 MHz or as fast as the flash device supports.

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 7.2 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables Link B around 200 ns after the boot process starts. Enabling the Link switches off the pull-down on

| Feature              | Bit  | Description                                                                                                                                                                                                                               |  |  |  |  |  |  |

|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                    |  |  |  |  |  |  |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island<br>with other tiles free for non-secure user application<br>code. |  |  |  |  |  |  |

| Secure Boot          | 5    | The xCORE Tile is forced to boot from address 0 o<br>the OTP, allowing the xCORE Tile boot ROM to be<br>bypassed ( <i>see</i> §7).                                                                                                        |  |  |  |  |  |  |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                            |  |  |  |  |  |  |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                      |  |  |  |  |  |  |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                      |  |  |  |  |  |  |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                      |  |  |  |  |  |  |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                      |  |  |  |  |  |  |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up dates to all sectors and security register.                                                                                                                                               |  |  |  |  |  |  |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inter<br>face to this OTP.                                                                                                                                                                |  |  |  |  |  |  |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                       |  |  |  |  |  |  |

|                      | 2115 | General purpose software accessable security registe available to end-users.                                                                                                                                                              |  |  |  |  |  |  |

|                      | 3122 | General purpose user programmable JTAG UserII code extension.                                                                                                                                                                             |  |  |  |  |  |  |

Figure 10: Security register features

data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

### 8.2 SRAM

Each xCORE Tile integrates a single 64KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

-XM()S

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 13. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, *see* §8.1 (all zero on unprogrammed devices).

Figure 13: USERCODE return value

|   | Bit31 Usercode Register |   |   |   |   |   |   |        |   |   |   |                  |   |   |   | BitO |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|-------------------------|---|---|---|---|---|---|--------|---|---|---|------------------|---|---|---|------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | OTP User ID             |   |   |   |   |   |   | Unused |   |   |   | Silicon Revision |   |   |   |      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| - | 0                       | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0 | 0 | 0 | 0                | 0 | 0 | 1 | 0    | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| - | 0                       |   | ( | ) |   |   | ( | D      | 2 |   | 2 | 8                |   | 0 |   |      | 0 |   |   | 0 |   |   |   |   |   |   |   |   |   |   |   |   |

#### 9.1 PCU

PCU\_WAKE should be left unconnected, PCU\_GATE should be left unconnected and PCU\_CLK must be tied to CLK.

## 10 Board Integration

The device has the following power supply pins:

- VDD pins for the xCORE Tile

- VDDIO pins for the I/O lines

- PLL\_AVDD pins for the PLL

- PCU\_VDD and PCU\_VDDIO pins for the PCU

- OTP\_VCC pins for the OTP

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0V to its final value within 10 ms to ensure correct startup.

The VDDIO and OTP\_VCC supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $2.2 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

The PCU\_VDD supply must be connected to the VDD supply.

The PCU\_VDDIO supply must be connected to the VDDIO supply.

The OTP\_VCC supply should be connected to the VDDIO supply.

The following ground pins are provided:

- PLL\_AGND for PLL\_AVDD

- ► GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example, 4x100nF 0402 low inductance MLCCs per supply rail). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (*see* §7). RST\_N and must be asserted low during and after power up for 100 ns.

#### 10.1 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints.

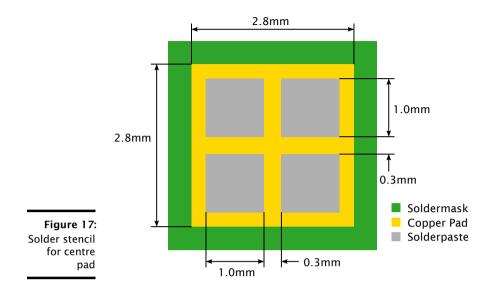

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. The size, type and number of vias used in the center pad affects how much solder wicks down the vias during reflow. This in turn, along with solder paster coverage, affects the final assembled package height. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

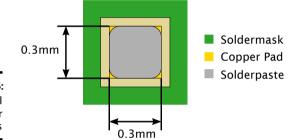

The package is a 124 pin dual row Quad Flat No lead package with exposed heat slug on a 0.5mm pitch. An example land pattern is shown in Figure 14.

Pad widths and spacings are such that solder mask can still be applied between the pads using standard design rules. This is highly recommended to reduce solder shorts between pads. See the recommended PCB solder mask diagram in Figure 15.

#### 10.2 Solder Stencil

The solder joints in the QFN package are formed exclusively from the solder paste deposited from the solder stencil. At the small aperture sizes required, the design of the stencil becomes important to ensure a reliable final solder joint volume and reliable solder joints.

20

The solder stencil recommendations here are based on those suggested in the IPC specification IPC-7525A "Stencil Design Guidelines".

As the aperture size in the stencil becomes very small, the amount of solder which remains on the PCB pad after printing is reduced. This occurs due to friction between the walls of the stencil and the solder paste dragging the paste from the pad when the stencil is removed. This effect is minimized as the thickness of the stencil is reduced.

For the 124 pin QFN package, our recommendations are to use a 4mil thick laser cut stencil. The solder stencil apertures for the pads should be 0.3mm square with 0.06mm radiused corners. This is the same size as the pads themselves apart from radiused corners to aid in paste transfer. This can be seen in the Figure 16.

Figure 16: Solder stencil for outer pads

> These dimensions should be the final aperture sizes used on the stencil, this should be agreed with the stencil makers or assembly house. It is common for assembly houses to subject the paste mask data to a global undersize before cutting the stencil. If this undersize is applied to these small apertures the paste transfer is likely to be poor and open solder joints may result.

> For the center pad of this package, four squares of solder paste is recommended, 1mm on a side as shown in Figure 17. This gives a paste to pad area ratio of 51%.

### 10.3 Ground and Thermal Vias

Vias under the heat slug into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. A 3 x 3 grid of vias, with a 0.6mm diameter annular ring and a 0.3mm drill, equally spaced across the heat slug, would be suitable.

### 10.4 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from *Joint IPC/JEDEC Standard For Moisture/Reflow Sensitivity Classification For Nonhermetic Solid State Surface-Mount Devices* J-STD-020 Revision D.

# 11 DC and Switching Characteristics

| Symbol    | Parameter                                     | MIN  | ТҮР  | MAX  | UNITS | Notes |

|-----------|-----------------------------------------------|------|------|------|-------|-------|

| VDD       | Tile DC supply voltage                        | 0.95 | 1.00 | 1.05 | V     |       |

| VDDIO     | I/O supply voltage                            | 3.00 | 3.30 | 3.60 | V     |       |

| PLL_AVDD  | PLL analog supply                             | 0.95 | 1.00 | 1.05 | V     |       |

| PCU_VDD   | PCU tile DC supply voltage                    | 0.95 | 1.00 | 1.05 | V     |       |

| PCU_VDDIO | PCU I/O DC supply voltage                     | 3.00 | 3.30 | 3.60 | V     |       |

| OTP_VCC   | OTP supply voltage                            | 3.00 | 3.30 | 3.60 | V     |       |

| Cl        | xCORE Tile I/O load<br>capacitance            |      |      | 25   | pF    |       |

| Та        | Ambient operating<br>temperature (Commercial) | 0    |      | 70   | °C    |       |

|           | Ambient operating<br>temperature (Industrial) | -40  |      | 85   | °C    |       |

| Тј        | Junction temperature                          |      |      | 125  | °C    |       |

| Tstg      | Storage temperature                           | -65  |      | 150  | °C    |       |

#### 11.1 Operating Conditions

Figure 18: Operating conditions

## 11.2 DC Characteristics

| Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|----------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage   | 2.00  |     | 3.60 | V     | А     |

| V(IL)  | Input low voltage    | -0.30 |     | 0.70 | V     | А     |

| V(OH)  | Output high voltage  | 2.00  |     |      | V     | B, C  |

| V(OL)  | Output low voltage   |       |     | 0.60 | V     | В, С  |

| R(PU)  | Pull-up resistance   |       | 35K |      | Ω     | D     |

| R(PD)  | Pull-down resistance |       | 35K |      | Ω     | D     |

Figure 19: DC characteristics

A All pins except power supply pins.

B Ports 1A, 1D, 1E, 1H, 1I, 1J, 1K and 1L are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry.

## 11.3 ESD Stress Voltage

Figure 20 ESD stress voltage

| 20: | Symbol | Parameter        | MIN   | TYP | MAX  | UNITS | Notes |

|-----|--------|------------------|-------|-----|------|-------|-------|

| ess | HBM    | Human body model | -2.00 |     | 2.00 | KV    |       |

| age | MM     | Machine model    | -200  |     | 200  | V     |       |

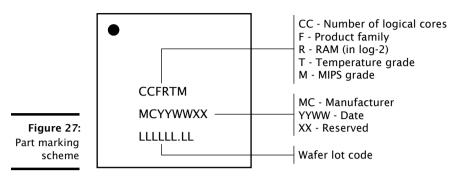

## 12.1 Part Marking

# 13 Ordering Information

|                                         | Product Code           | Marking | Qualification | Speed Grade |

|-----------------------------------------|------------------------|---------|---------------|-------------|

|                                         | XS1-L12A-128-QF124-C8  | 12L7C8  | Commercial    | 800 MIPS    |

| Figure 28:<br>Orderable<br>part numbers | XS1-L12A-128-QF124-C10 | 12L7C10 | Commercial    | 1000 MIPS   |

|                                         | XS1-L12A-128-QF124-I8  | 12L7I8  | Industrial    | 800 MIPS    |

|                                         | XS1-L12A-128-QF124-I10 | 12L7I10 | Industrial    | 1000 MIPS   |

| 0x11:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SPC | 31:0 | DRW  |      | Value.      |

#### B.13 Debug SSP: 0x12

This register contains the value of the SSP register when the debugger was called.

| 0x12:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SSP | 31:0 | DRW  |      | Value.      |

#### B.14 DGETREG operand 1: 0x13

The resource ID of the logical core whose state is to be read.

| 0x13:                | Bits | Perm | Init | Description              |

|----------------------|------|------|------|--------------------------|

| DGETREG<br>operand 1 | 31:8 | RO   | -    | Reserved                 |

|                      | 7:0  | DRW  |      | Thread number to be read |

#### B.15 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |

|------|------|------|----------------------------|

| 31:5 | RO   | -    | Reserved                   |

| 4:0  | DRW  |      | Register number to be read |

#### B.16 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

-XMC

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                       |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 17:16 | DRW  |      | If the debug interrupt was caused by a hardware breakpoint<br>or hardware watchpoint, this field contains the number of the<br>breakpoint or watchpoint. If multiple breakpoints or watch-<br>points trigger at once, the lowest number is taken. |

| 15:8  | DRW  |      | If the debug interrupt was caused by a logical core, this field contains the number of that core. Otherwise this field is 0.                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point                          |

**0x15:** Debug interrupt type

### B.17 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

0x16 Debug interrupt data

| <b>0x16:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ot data               | 31:0 | DRW  |      | Value.      |

#### B.18 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

**0x18:** Debug core control

| Bits | Perm | Init | Description                                                                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                                                                                                                                      |

| 7:0  | DRW  |      | 1-hot vector defining which logical cores are stopped when not<br>in debug mode. Every bit which is set prevents the respective<br>logical core from running. |

37

0x50 .. 0x53: Data watchpoint address 1

| Data<br>Ipoint | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ress 1         | 31:0 | DRW  |      | Value.      |

#### B.23 Data watchpoint address 2: 0x60 ... 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| ata<br>int | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| 5 2        | 31:0 | DRW  |      | Value.      |

#### B.24 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

|        | Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                       |

|--------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

|        | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                                                                                 |

|        | 15:3  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

|        | 2     | DRW  | 0    | Set to 1 to enable breakpoints to be triggered on loads. Breakpoints always trigger on stores.                                                                                                                                                                                                    |

| a<br>t | 1     | DRW  | 0    | By default, data watchpoints trigger if memory in the range [Address1Address2] is accessed (the range is inclusive of Address1 and Address2). If set to 1, data watchpoints trigger if memory outside the range (Address2Address1) is accessed (the range is exclusive of Address2 and Address1). |

| r      | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                                                                                     |

0x70 .. 0x73: Data breakpoint control register

#### B.25 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

-XMOS<sup>®</sup>

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref, ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | RO   | Device identification                          |

| 0x01      | RO   | xCORE Tile description 1                       |

| 0x02      | RO   | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | RW   | xCORE Tile clock divider                       |

| 0x07      | RO   | Security configuration                         |

| 0x100x13  | RO   | PLink status                                   |

| 0x200x27  | CRW  | Debug scratch                                  |

| 0x40      | RO   | PC of logical core 0                           |

| 0x41      | RO   | PC of logical core 1                           |

| 0x42      | RO   | PC of logical core 2                           |

| 0x43      | RO   | PC of logical core 3                           |

| 0x44      | RO   | PC of logical core 4                           |

| 0x45      | RO   | PC of logical core 5                           |

| 0x60      | RO   | SR of logical core 0                           |

| 0x61      | RO   | SR of logical core 1                           |

| 0x62      | RO   | SR of logical core 2                           |

| 0x63      | RO   | SR of logical core 3                           |

| 0x64      | RO   | SR of logical core 4                           |

| 0x65      | RO   | SR of logical core 5                           |

| 0x80 0x9F | RO   | Chanend status                                 |

-XMOS°

Figure 31: Summary

## C.1 Device identification: 0x00

| 0x00:          |

|----------------|

| Device         |

| identification |

| Bits  | Perm | Init | Description                                             |

|-------|------|------|---------------------------------------------------------|

| 31:24 | RO   |      | Processor ID of this xCORE tile.                        |

| 23:16 | RO   |      | Number of the node in which this xCORE tile is located. |

| 15:8  | RO   |      | xCORE tile revision.                                    |

| 7:0   | RO   |      | xCORE tile version.                                     |

## C.2 xCORE Tile description 1: 0x01

Bits Perm Init Description

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

|               |       |    |   | -                        |

|---------------|-------|----|---|--------------------------|

|               | 31:24 | RO |   | Number of channel ends.  |

| 0x01:         | 23:16 | RO |   | Number of locks.         |

| xCORE Tile    | 15:8  | RO |   | Number of synchronisers. |

| description 1 | 7:0   | RO | - | Reserved                 |

|               |       |    |   |                          |

## C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

| Bits  | Perm | Init | Description             |  |

|-------|------|------|-------------------------|--|

| 31:16 | RO   | -    | Reserved                |  |

| 15:8  | RO   |      | Number of clock blocks. |  |

| 7:0   | RO   |      | Number of timers.       |  |

## C.4 Control PSwitch permissions to debug registers: 0x04

-XMOS-

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                 |  |  |

|------|------|------|-------------------------------------------------------------------------------------------------------------|--|--|

| 31:1 | RO   | -    | Reserved                                                                                                    |  |  |

| 0    | CRW  |      | Set to 1 to restrict PSwitch access to all CRW marked registers to become read-only rather than read-write. |  |  |

#### C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

| Bits | Perm | Init | Description                                             |  |

|------|------|------|---------------------------------------------------------|--|

| 31:2 | RO   | -    | Reserved                                                |  |

| 1    | RO   | 0    | Set to 1 when the processor is in debug mode.           |  |

| 0    | CRW  | 0    | Set to 1 to request a debug interrupt on the processor. |  |

### C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| 6: | Bits | Perm | Init | Description                           |  |

|----|------|------|------|---------------------------------------|--|

| e. | 31:8 | RO   | -    | Reserved                              |  |

| er | 7:0  | RW   |      | Value of the clock divider minus one. |  |

### C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

0x07: Security configuration

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

## C.8 PLink status: 0x10 .. 0x13

Status of each of the four processor links; connecting the xCORE tile to the switch.

-XMOS<sup>®</sup>

## C.22 Chanend status: 0x80 .. 0x9F

These registers record the status of each channel-end on the tile.

|             | Bits  | Perm | Init | Description                                                                                                    |  |

|-------------|-------|------|------|----------------------------------------------------------------------------------------------------------------|--|

|             | 31:26 | RO   | -    | Reserved                                                                                                       |  |

|             | 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |  |

|             | 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |  |

|             | 15:6  | RO   | -    | Reserved                                                                                                       |  |

|             | 5:4   | RO   |      | Two-bit network identifier                                                                                     |  |

|             | 3     | RO   | -    | Reserved                                                                                                       |  |

|             | 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |  |

| x9F:        | 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |  |

| end<br>atus | 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |  |

-XMOS®

0x80 .. 0x9F: Chanend status

## D Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number    | Perm | Description                           |  |

|-----------|------|---------------------------------------|--|

| 0x00      | RO   | Device identification                 |  |

| 0x01      | RO   | System switch description             |  |

| 0x04      | RW   | Switch configuration                  |  |

| 0x05      | RW   | Switch node identifier                |  |

| 0x06      | RW   | PLL settings                          |  |

| 0x07      | RW   | System switch clock divider           |  |

| 0x08      | RW   | Reference clock                       |  |

| 0x0C      | RW   | Directions 0-7                        |  |

| 0x0D      | RW   | Directions 8-15                       |  |

| 0x10      | RW   | DEBUG_N configuration                 |  |

| 0x1F      | RO   | Debug source                          |  |

| 0x20 0x27 | RW   | Link status, direction, and network   |  |

| 0x40 0x43 | RW   | PLink status and network              |  |

| 0x80 0x87 | RW   | Link configuration and initialization |  |

| 0xA0 0xA7 | RW   | Static link configuration             |  |

Figure 32: Summary

## D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|                          | Bits  | Perm | Init | Description                                    |

|--------------------------|-------|------|------|------------------------------------------------|

|                          | 31:24 | RO   | 0x00 | Chip identifier.                               |

| 0x00:                    | 23:16 | RO   |      | Sampled values of pins MODE0, MODE1, on reset. |

| Device<br>identification | 15:8  | RO   |      | SSwitch revision.                              |

|                          | 7:0   | RO   |      | SSwitch version.                               |

### D.2 System switch description: 0x01

This register specifies the number of processors and links that are connected to this switch.

|                        | Bits  | Perm | Init | Description                                        |

|------------------------|-------|------|------|----------------------------------------------------|

|                        | 31:24 | RO   | -    | Reserved                                           |

| <b>0x01:</b><br>System | 23:16 | RO   |      | Number of links on the switch.                     |

| switch                 | 15:8  | RO   |      | Number of cores that are connected to this switch. |

| description            | 7:0   | RO   |      | Number of links per processor.                     |

#### D.3 Switch configuration: 0x04

This register enables the setting of two security modes (that disable updates to the PLL or any other registers) and the header-mode.

| Bits | Perm | Init | Description                                                                                        |

|------|------|------|----------------------------------------------------------------------------------------------------|

| 31   | RO   | 0    | Set to 1 to disable any write access to the configuration registers in this switch.                |

| 30:9 | RO   | -    | Reserved                                                                                           |

| 8    | RO   | 0    | Set to 1 to disable updates to the PLL configuration register.                                     |

| 7:1  | RO   | -    | Reserved                                                                                           |

| 0    | RO   | 0    | Header mode. Set to 1 to enable 1-byte headers. This must be performed on all nodes in the system. |

**0x04:** Switch configuration

### D.4 Switch node identifier: 0x05

This register contains the node identifier.

0x05 Switch node identifier

|               | Bits  | Perm | Init | Description                                                                                                                            |

|---------------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| -             | 31:16 | RO   | -    | Reserved                                                                                                                               |

| 5:<br>e<br>er | 15:0  | RW   | 0    | The unique 16-bit ID of this node. This ID is matched most-<br>significant-bit first with incoming messages for routing pur-<br>poses. |

### D.5 PLL settings: 0x06

An on-chip PLL multiplies the input clock up to a higher frequency clock, used to clock the I/O, processor, and switch, see Oscillator. Note: a write to this register will cause the tile to be reset.

- ▶ TDO to pin 13 of the xSYS header

- RST\_N and TRST\_N to pin 15 of the xSYS header

- If MODE2 is configured high, connect MODE2 to pin 3 of the xSYS header. Do not connect to VDDIO.

- If MODE3 is configured high, connect MODE3 to pin 3 of the xSYS header. Do not connect to VDDIO.

The RST\_N net should be open-drain, active-low, and have a pull-up to VDDIO.

#### G.3 Full xSYS header

For a full xSYS header you will need to connect the pins as discussed in Section G.2, and then connect a 2-wire xCONNECT Link to the xSYS header. The links can be found in the Signal description table (Section 4): they are labelled XLA, XLB, etc in the function column. The 2-wire link comprises two inputs and outputs, labelled  ${}^{1}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{in}$ , and  ${}^{1}_{in}$ . For example, if you choose to use XLB of tile 0 for xSCOPE I/O, you need to connect up XLB<sup>1</sup><sub>out</sub>, XLB<sup>0</sup><sub>out</sub>, XLB<sup>0</sup><sub>in</sub>, XLB<sup>1</sup><sub>in</sub> as follows:

- XLB<sup>1</sup><sub>out</sub> (X0D16) to pin 6 of the xSYS header with a 33R series resistor close to the device.

- XLB<sup>0</sup><sub>out</sub> (X0D17) to pin 10 of the xSYS header with a 33R series resistor close to the device.

- ▶ XLB<sup>0</sup><sub>in</sub> (X0D18) to pin 14 of the xSYS header.

- ▶ XLB<sup>1</sup><sub>in</sub> (X0D19) to pin 18 of the xSYS header.

-XM()S