Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-rdtum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. SFR Mapping

The Special Function Registers (SFRs) of the AT89C51RD2/ED2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3, PI2

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

- SPI registers: SPCON, SPSTR, SPDAT

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Clock Prescaler register: CKRL

- Others: AUXR, AUXR1, CKCON0, CKCON1

|  | Table 3-1. | C51 Core SFRs |

|--|------------|---------------|

|--|------------|---------------|

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

#### Table 3-2.System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF  | GF1  | GF0  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | M0     | XRS2 | XRS1 | XRS0 | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -    | GF3  | 0    | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | -     | -     | -      | -    | -    | -    | -      | -     |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2 | T2X2 | T1X2 | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -    | -    | -    | -      | SPIX2 |

# 5. Port Types

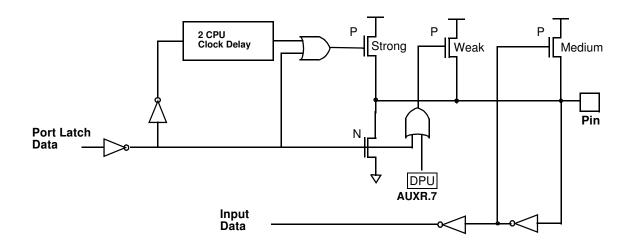

AT89C51RD2/ED2 I/O ports (P1, P2, P3, P4, P5) implement the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-tohigh transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 5-1.

Figure 5-1. Quasi-Bidirectional Output

# 8. Dual Data Pointer Register (DPTR)

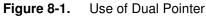

The additional data pointer can be used to speed up code execution and reduce code size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 8-1) that allows the program code to switch between them (Refer to Figure 8-1).

Table 8-1.AUXR1 RegisterAUXR1- Auxiliary Register 1(0A2h)

| 7             | 6               | 5                                                        | 4                                                                                                    | 3                         | 2                 | 1    | 0   |  |  |  |  |

|---------------|-----------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------|-------------------|------|-----|--|--|--|--|

| -             | -               | ENBOOT                                                   | -                                                                                                    | GF3                       | 0                 | -    | DPS |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                              | Description                                                                                          |                           |                   |      |     |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value read                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                      |                           |                   |      |     |  |  |  |  |

| 6             | -               | Reserved<br>The value read                               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                      |                           |                   |      |     |  |  |  |  |

| 5             | ENBOOT          | Cleared to disa                                          | Enable Boot Flash<br>Cleared to disable boot ROM.<br>Set to map the boot ROM between F800h - 0FFFFh. |                           |                   |      |     |  |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value read                        | I from this bit is                                                                                   | s indeterminate           | . Do not set this | bit. |     |  |  |  |  |

| 3             | GF3             | This bit is a ge                                         | neral-purpose                                                                                        | user flag. <sup>(1)</sup> |                   |      |     |  |  |  |  |

| 2             | 0               | Always cleared                                           | ł                                                                                                    |                           |                   |      |     |  |  |  |  |

| 1             | -               | <b>Reserved</b><br>The value read                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                      |                           |                   |      |     |  |  |  |  |

| 0             | DPS             | Data Pointer S<br>Cleared to select D<br>Set to select D | ect DPTR0.                                                                                           |                           |                   |      |     |  |  |  |  |

# Table 13-1.CMOD Register

CMOD - PCA Counter Mode Register (D9h)

| 7             | 6               | 5                                  | 4                                                                                                                                                                                              | 3               | 2                  | 1      | 0   |  |  |  |  |

|---------------|-----------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|--------|-----|--|--|--|--|

| CIDL          | WDTE            | -                                  | -                                                                                                                                                                                              | -               | CPS1               | CPS0   | ECF |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                        | Description                                                                                                                                                                                    |                 |                    |        |     |  |  |  |  |

| 7             | CIDL            | Cleared to pro                     | ounter Idle Control<br>leared to program the PCA Counter to continue functioning during idle Mode.<br>et to program PCA to be gated off during idle.                                           |                 |                    |        |     |  |  |  |  |

| 6             | WDTE            | Cleared to dis                     | <b>Watchdog Timer Enable</b><br>Cleared to disable Watchdog Timer function on PCA Module 4.<br>Set to enable Watchdog Timer function on PCA Module 4.                                          |                 |                    |        |     |  |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                |                 |                    |        |     |  |  |  |  |

| 4             | -               | Reserved<br>The value rea          | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                |                 |                    |        |     |  |  |  |  |

| 3             | -               | Reserved<br>The value rea          | d from this bit i                                                                                                                                                                              | s indeterminate | e. Do not set this | s bit. |     |  |  |  |  |

| 2             | CPS1            | PCA Count P                        | ulse Select                                                                                                                                                                                    |                 |                    |        |     |  |  |  |  |

| 1             | CPS0            | CPS1CPS0<br>0 0<br>1<br>1 0<br>1 1 | $\begin{array}{cccc} 0 & 0 & \text{Internal clock } F_{\text{CLK PERIPH}}/6 \\ 0 & 1 & \text{Internal clock } F_{\text{CLK PERIPH}}/2 \\ 1 & 0 & \text{Timer } 0 \text{ Overflow} \end{array}$ |                 |                    |        |     |  |  |  |  |

| 0             | ECF             | Cleared to dis                     | PCA Enable Counter Overflow Interrupt<br>Cleared to disable CF bit in CCON to inhibit an interrupt.<br>Set to enable CF bit in CCON to generate an interrupt.                                  |                 |                    |        |     |  |  |  |  |

Reset Value = 00XX X000b Not bit addressable

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 13-2).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

### Table 13-2. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7             | 6               | 5                                                                                                              | 4                                                                                                                                                                                                                  | 3    | 2      | 1    | 0    |  |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|--|--|--|--|

| CF            | CR              | -                                                                                                              | CCF4                                                                                                                                                                                                               | CCF3 | CCF2   | CCF1 | CCF0 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                    |                                                                                                                                                                                                                    |      |        |      |      |  |  |  |  |

| 7             | CF              | Set by hardwa<br>set. CF                                                                                       | PCA Counter Overflow flag<br>Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is<br>set. CF<br>may be set by either hardware or software but can only be cleared by software. |      |        |      |      |  |  |  |  |

| 6             | CR              | Must be clear                                                                                                  | PCA Counter Run control bit<br>Must be cleared by software to turn the PCA counter off.<br>Set by software to turn the PCA counter on.                                                                             |      |        |      |      |  |  |  |  |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                |                                                                                                                                                                                                                    |      |        |      |      |  |  |  |  |

| 4             | CCF4            | Must be clear                                                                                                  | PCA Module 4 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                     |      |        |      |      |  |  |  |  |

| 3             | CCF3            | Must be clear                                                                                                  | <b>3 interrupt fla</b><br>ed by software<br>are when a mai                                                                                                                                                         | -    | ccurs. |      |      |  |  |  |  |

| 2             | CCF2            | PCA Module 2 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |                                                                                                                                                                                                                    |      |        |      |      |  |  |  |  |

| 1             | CCF1            | PCA Module 1 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |                                                                                                                                                                                                                    |      |        |      |      |  |  |  |  |

| 0             | CCF0            | Must be clear                                                                                                  | <b>0 interrupt fla</b><br>ed by software<br>are when a mat                                                                                                                                                         | -    | ccurs. |      |      |  |  |  |  |

Reset Value = 00X0 0000b Bit addressable

The watchdog timer function is implemented in Module 4 (See Figure 13-4).

The PCA interrupt system is shown in Figure 13-2.

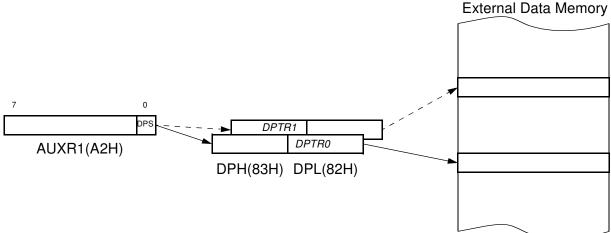

Figure 14-3. UART Timings in Modes 2 and 3

## 14.2 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, the user may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit. To support automatic address recognition, a device is identified by a given address and a broadcast address.

Note: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i. e. setting SM2 bit in SCON register in mode 0 has no effect).

### 14.2.1 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed.

To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

```

SADDR0101 0110b

SADEN1111 1100b

Given0101 01XXb

```

The following is an example of how to use given addresses to address different slaves:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 0X0Xb

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 0XX1b

```

```

Slave C:SADDR1111 0010b

<u>SADEN1111 1101b</u>

Given1111 00X1b

```

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1.To communicate with slave A only, the master must send an address where bit 0 is clear (e. g. 1111 0000b). For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e. g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e. g. 1111 0001b).

#### 14.2.2 Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e. g. :

```

SADDR0101 0110b

SADEN1111 1100b

Broadcast =SADDR OR SADEN1111 111Xb

```

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Broadcast1111 1X11b,

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Broadcast1111 1X11B,

Slave C:SADDR=1111 0011b

<u>SADEN1111 1101b</u>

Broadcast1111 1111b

```

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

#### 14.2.3 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i. e. the given and broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

# Table 14-11. T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                                                                                                                                              | 4                                                                                                                                                                                                                                             | 3                                                                   | 2               | 1              | 0               |  |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------|----------------|-----------------|--|--|--|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                           | TCLK                                                                                                                                                                                                                                          | EXEN2                                                               | TR2             | C/T2#          | CP/RL2#         |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                                                                                                                | Description                                                                                                                                                                                                                                   |                                                                     |                 |                |                 |  |  |  |  |

| 7             | TF2             |                                                                                                                                                                                                | ed by software                                                                                                                                                                                                                                | overflow, if RCI                                                    | _K = 0 and TCL  | .K = 0.        |                 |  |  |  |  |

| 6             | EXF2            | Set when a c<br>EXEN2=1.<br>When set, ca<br>enabled.<br>Must be clear                                                                                                                          | Vhen set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is                                                                                                                                                     |                                                                     |                 |                |                 |  |  |  |  |

| 5             | RCLK            | Receive Clock bit for UART<br>Cleared to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3. |                                                                                                                                                                                                                                               |                                                                     |                 |                |                 |  |  |  |  |

| 4             | TCLK            | Cleared to us                                                                                                                                                                                  | Transmit Clock bit for UART<br>Cleared to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                             |                                                                     |                 |                |                 |  |  |  |  |

| 3             | EXEN2           | Cleared to ign<br>Set to cause                                                                                                                                                                 | a capture or re                                                                                                                                                                                                                               | <b>it</b><br>T2EX pin for tir<br>load when a ne<br>the serial port. |                 |                | is detected, if |  |  |  |  |

| 2             | TR2             | Timer 2 Run<br>Cleared to tu<br>Set to turn or                                                                                                                                                 | rn off timer 2.                                                                                                                                                                                                                               |                                                                     |                 |                |                 |  |  |  |  |

| 1             | C/T2#           | Cleared for til<br>Set for count                                                                                                                                                               | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for<br>clock out mode. |                                                                     |                 |                |                 |  |  |  |  |

| 0             | CP/RL2#         | If RCLK=1 or<br>overflow.<br>Cleared to au<br>EXEN2=1.                                                                                                                                         | ito-reload on ti                                                                                                                                                                                                                              | <b>it</b><br>RL2# is ignored<br>mer 2 overflows<br>ransitions on T  | or negative tra | nsitions on T2 |                 |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

# 15.1 Registers

## Table 15-1. KBF Register

KBF-Keyboard Flag Register (9Eh)

| 7          | 6               | 5                              | 4                                                                                                                                                                                                                         | 3              | 2                                | 1    | 0       |  |  |  |  |

|------------|-----------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|------|---------|--|--|--|--|

| KBF7       | KBF6            | KBF5                           | KBF4                                                                                                                                                                                                                      | KBF3           | KBF2                             | KBF1 | KBF0    |  |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description                    | Description                                                                                                                                                                                                               |                |                                  |      |         |  |  |  |  |

| 7          | KBF7            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 7 flag</b><br>Set by hardware when the Port line 7 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBKBIE.7 bit in KBIE register is set.<br>Must be cleared by software. |                |                                  |      |         |  |  |  |  |

| 6          | KBF6            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 6 flag</b><br>Set by hardware when the Port line 6 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.6 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |  |  |

| 5          | KBF5            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 5 flag</b><br>Set by hardware when the Port line 5 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.5 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |  |  |

| 4          | KBF4            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 4 flag</b><br>Set by hardware when the Port line 4 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.4 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |  |  |

| 3          | KBF3            | Set by hardwa<br>Keyboard inte | Keyboard line 3 flag<br>Set by hardware when the Port line 3 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.3 bit in KBIE register is set.<br>Must be cleared by software.          |                |                                  |      |         |  |  |  |  |

| 2          | KBF2            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 2 flag</b><br>Set by hardware when the Port line 2 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.2 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |  |  |

| 1          | KBF1            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 1 flag</b><br>Set by hardware when the Port line 1 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.1 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |  |  |

| 0          | KBF0            | Keyboard inte                  | ire when the Po                                                                                                                                                                                                           | the KBIE.0 bit | s a programme<br>in KBIE registe |      | rates a |  |  |  |  |

## **Reset Value = 0000 0000b**

This register is read only access, all flags are automatically cleared by reading the register.

Table 15-2.KBE RegisterKBE-Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5             | 4                                                                                                                                                     | 3    | 2                | 1             | 0    |  |  |  |  |

|---------------|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|---------------|------|--|--|--|--|

| KBE7          | KBE6            | KBE5          | KBE4                                                                                                                                                  | KBE3 | KBE2             | KBE1          | KBE0 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   | Description                                                                                                                                           |      |                  |               |      |  |  |  |  |

| 7             | KBE7            | Cleared to en | e <b>7 Enable bit</b><br>able standard I<br>KBF.7 bit in KE                                                                                           |      | enerate an inter | rupt request. |      |  |  |  |  |

| 6             | KBE6            | Cleared to en | <b>Ceyboard line 6 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.6 bit in KBF register to generate an interrupt request. |      |                  |               |      |  |  |  |  |

| 5             | KBE5            | Cleared to en | <b>Keyboard line 5 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.5 bit in KBF register to generate an interrupt request. |      |                  |               |      |  |  |  |  |

| 4             | KBE4            | Cleared to en | Keyboard line 4 Enable bit<br>Cleared to enable standard I/O pin.<br>Set to enable KBF.4 bit in KBF register to generate an interrupt request.        |      |                  |               |      |  |  |  |  |

| 3             | KBE3            | Cleared to en | e <b>3 Enable bit</b><br>able standard I<br>KBF.3 bit in KE                                                                                           |      | enerate an inter | rupt request. |      |  |  |  |  |

| 2             | KBE2            | Cleared to en | <b>Keyboard line 2 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.2 bit in KBF register to generate an interrupt request. |      |                  |               |      |  |  |  |  |

| 1             | KBE1            | Cleared to en | <b>Keyboard line 1 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.1 bit in KBF register to generate an interrupt request. |      |                  |               |      |  |  |  |  |

| 0             | KBE0            | Cleared to en | e <b>0 Enable bit</b><br>able standard I<br>KBF.0 bit in KE                                                                                           |      | enerate an inter | rupt request. |      |  |  |  |  |

Reset Value = 0000 0000b

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                         |  |  |  |  |  |  |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 4          | MSTR         | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                       |  |  |  |  |  |  |

| 3          | CPOL         | <b>Clock Polarity</b><br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                           |  |  |  |  |  |  |

| 2          | СРНА         | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the idle state (see<br>CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see<br>CPOL).                                                 |  |  |  |  |  |  |

| 1          | SPR1         | SPR2         SPR1         SPR0 Serial Peripheral Rate           0         0         1F <sub>CLK PERIPH</sub> /2           0         0         1F <sub>CLK PERIPH</sub> /4           0         1         0F <sub>CLK PERIPH</sub> /8 |  |  |  |  |  |  |

|            | SPR0         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                               |  |  |  |  |  |  |

Reset Value = 0001 0100b

Not bit addressable

#### 16.3.5.2 Serial Peripheral Status Register (SPSTA)

The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 16-4 describes the SPSTA register and explains the use of every bit in the register.

## Table 16-4. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7          | 6               | 5                                                                                                                                                                                                                              | 4    | 3 | 2 | 1 | 0 |  |  |  |  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---|---|--|--|--|--|

| SPIF       | WCOL            | SSERR                                                                                                                                                                                                                          | MODF | - | - | - | - |  |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                    | •    |   |   |   |   |  |  |  |  |

| 7          | SPIF            | Serial Peripheral Data Transfer Flag<br>Cleared by hardware to indicate data transfer is in progress or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed. |      |   |   |   |   |  |  |  |  |

| 6          | WCOL            | Write Collision Flag<br>Cleared by hardware to indicate that no collision has occurred or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that a collision has been detected.                      |      |   |   |   |   |  |  |  |  |

# Table 17-7. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                                | 4                                                                               | 3               | 2                 | 1      | 0    |  |  |  |

|---------------|-----------------|----------------------------------|---------------------------------------------------------------------------------|-----------------|-------------------|--------|------|--|--|--|

| -             | -               | -                                | -                                                                               | -               | SPIL              | TWIL   | KBDL |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      |                                                                                 |                 |                   |        |      |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea | e value read from this bit is indeterminate. Do not set this bit.               |                 |                   |        |      |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | eserved<br>ne value read from this bit is indeterminate. Do not set this bit.   |                 |                   |        |      |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |

| 2             | SPIL            |                                  | SPI interrupt Priority bit<br>Refer to SPIH for priority level.                 |                 |                   |        |      |  |  |  |

| 1             | -               | <b>Reserved</b><br>The value rea | d from this bit i                                                               | s indeterminate | e. Do not set thi | s bit. |      |  |  |  |

| 0             | KBDL            |                                  | errupt Priority<br>I for priority lev                                           |                 |                   |        |      |  |  |  |

Reset Value = XXXX X000b Bit addressable

continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT89C51RD2/ED2 and vectors the CPU to address 0000h.

- 3. Generate an enabled external Keyboard interrupt (same behavior as external interrupt).

- Note: During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated the Power-Down mode should not write to a Port pin or to the external RAM.

- Note: Exit from power-down by reset redefines all the SFRs, but does not affect the internal RAM content.

| Mode                             | Port 0   | Port 1 | Port 2 | Port 3 | Port 4 | ALE  | PSEN# |

|----------------------------------|----------|--------|--------|--------|--------|------|-------|

| Reset                            | Floating | High   | High   | High   | High   | High | High  |

| ldle (internal code)             | Data     | Data   | Data   | Data   | Data   | High | High  |

| Idle (external code)             | Floating | Data   | Data   | Data   | Data   | High | High  |

| Power-Down<br>(internal<br>code) | Data     | Data   | Data   | Data   | Data   | Low  | Low   |

| Power-Down<br>(external<br>code) | Floating | Data   | Data   | Data   | Data   | Low  | Low   |

Table 18-1. Pin Conditions in Special Operating Modes

# 24. Flash/EEPROM Memory

The Flash memory increases EEPROM and ROM functionality with in-circuit electrical erasure and programming. It contains 64K bytes of program memory organized respectively in 512 pages of 128 bytes. This memory is both parallel and serial In-System Programmable (ISP). ISP allows devices to alter their own program memory in the actual end product under software control. A default serial loader (bootloader) program allows ISP of the Flash.

The programming **does not require** external dedicated programming voltage. The necessary high programming voltage is generated on-chip using the standard  $V_{CC}$  pins of the microcontroller.

## 24.1 Features

- Flash EEPROM Internal Program Memory

- Boot vector allows user provided Flash loader code to reside anywhere in the Flash memory space. This configuration provides flexibility to the user.

- Default loader in Boot ROM allows programming via the serial port without the need of a user provided loader.

- Up to 64K bytes external program memory if the internal program memory is disabled (EA = 0).

- Programming and erasing voltage with standard power supply

- Read/Programming/Erase:

- Byte-wise read without wait state

- Byte or page erase and programming (10 ms)

- Typical programming time (64K bytes) is 22s with on chip serial bootloader

- Parallel programming with 87C51 compatible hardware interface to programmer

- · Programmable security for the code in the Flash

- 100K write cycles

- · 10 years data retention

## 24.2 Flash Programming and Erasure

The 64-K byte Flash is programmed by bytes or by pages of 128 bytes. It is not necessary to erase a byte or a page before programming. The programming of a byte or a page includes a self erase before programming.

There are three methods of programming the Flash memory:

- 1. The on-chip ISP bootloader may be invoked which will use low level routines to program the pages. The interface used for serial downloading of Flash is the UART.

- 2. The Flash may be programmed or erased in the end-user application by calling lowlevel routines through a common entry point in the Boot ROM.

- 3. The Flash may be programmed using the parallel method by using a conventional EPROM programmer. The parallel programming method used by these devices is similar to that used by EPROM 87C51 but it is not identical and the commercially available programmers need to have support for the AT89C51RD2/ED2. The bootloader and the Application Programming Interface (API) routines are located in the BOOT ROM.

#### 24.6.4 Bootloader Functionality

The bootloader can be activated by two means: Hardware conditions or regular boot process.

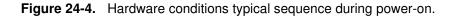

The Hardware conditions (EA = 1, PSEN = 0) during the Reset# falling edge force the on-chip bootloader execution. This allows an application to be built that will normally execute the end user's code but can be manually forced into default ISP operation.

As PSEN is a an output port in normal operating mode after reset, user application should take care to release PSEN after falling edge of reset signal. The hardware conditions are sampled at reset signal falling edge, thus they can be released at any time when reset input is low.

To ensure correct microcontroller startup, the PSEN pin should not be tied to ground during power-on (See Figure 24-4).

The on-chip bootloader boot process is shown Figure 24-5.

| Table 24-6. Boolloader Process Description | Table 24-6. | Bootloader Process Description |

|--------------------------------------------|-------------|--------------------------------|

|--------------------------------------------|-------------|--------------------------------|

|                     | Purpose                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Conditions | The Hardware Conditions force the bootloader execution whatever BLJB, BSB and SBV values.                                                                                                                                                                                                                                                     |

| BLJB                | The Boot Loader Jump Bit forces the application execution.<br>BLJB = 0 => Bootloader execution<br>BLJB = 1 => Application execution<br>The BLJB is a fuse bit in the Hardware Byte.<br>It can be modified by hardware (programmer) or by software (API).<br>Note: The BLJB test is performed by hardware to prevent any program<br>execution. |

| SBV                 | The Software Boot Vector contains the high address of customer bootloader<br>stored in the application.<br>SBV = FCh (default value) if no customer bootloader in user Flash.<br>Note: The customer bootloader is called by JMP [SBV]00h instruction.                                                                                         |

| Frequency<br>(MHz)                                       |                      |                      |                      |                |                      |                      |                      |                      |                      |

|----------------------------------------------------------|----------------------|----------------------|----------------------|----------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Baudrate (kHz)                                           | 1.8432               | 2                    | 2.4576               | 3              | 3.6864               | 4                    | 5                    | 6                    | 7.3728               |

| 4800                                                     | OK                   | -                    | ОК                   | OK             | OK                   | OK                   | OK                   | OK                   | OK                   |

| 9600                                                     | ОК                   | -                    | OK                   | OK             | OK                   | OK                   | OK                   | ОК                   | OK                   |

| 19200                                                    | ОК                   | -                    | OK                   | OK             | OK                   | -                    | -                    | ОК                   | OK                   |

| 38400                                                    | -                    | -                    | OK                   |                | OK                   | -                    | OK                   | ОК                   | ОК                   |

| 57600                                                    | -                    | -                    | -                    | -              | OK                   | -                    | -                    | -                    | OK                   |

| 115200                                                   | -                    | -                    | -                    | -              | -                    | -                    | -                    | -                    | OK                   |

| Fraguanay                                                |                      |                      |                      |                |                      |                      |                      |                      |                      |

| Frequency<br>(MHz)                                       | 0                    | 10                   | 11 0502              | 10             | 14 746               | 16                   | 20                   | 24                   | 26.6                 |

| (MHz)<br>Baudrate (kHz)                                  | 8                    | 10<br>OK             | 11.0592              | 12             | 14.746               | 16<br>OK             | <b>20</b>            | 24                   | 26.6                 |

| (MHz)<br>Baudrate (kHz)<br>2400                          | ОК                   | OK                   | OK                   | OK             | OK                   | OK                   | OK                   | OK                   | ОК                   |

| (MHz)<br>Baudrate (kHz)                                  |                      |                      |                      |                |                      |                      |                      |                      |                      |

| (MHz)<br>Baudrate (kHz)<br>2400                          | ОК                   | OK                   | OK                   | OK             | OK                   | OK                   | OK                   | OK                   | ОК                   |

| (MHz)<br>Baudrate (kHz)<br>2400<br>4800                  | ОК<br>ОК             | OK<br>OK             | OK<br>OK             | OK<br>OK       | OK<br>OK             | OK<br>OK             | OK<br>OK             | OK<br>OK             | OK<br>OK             |

| (MHz)<br>Baudrate (kHz)<br>2400<br>4800<br>9600          | ОК<br>ОК<br>ОК       | OK<br>OK<br>OK       | ОК<br>ОК<br>ОК       | OK<br>OK<br>OK | OK<br>OK<br>OK       | OK<br>OK<br>OK       | ОК<br>ОК<br>ОК       | OK<br>OK<br>OK       | ОК<br>ОК<br>ОК       |

| (MHz)<br>Baudrate (kHz)<br>2400<br>4800<br>9600<br>19200 | ОК<br>ОК<br>ОК<br>ОК | OK<br>OK<br>OK<br>OK | ОК<br>ОК<br>ОК<br>ОК | OK<br>OK<br>OK | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК |

| Table 24-8. | Autobaud Performances | (Continued) |

|-------------|-----------------------|-------------|

|             |                       |             |

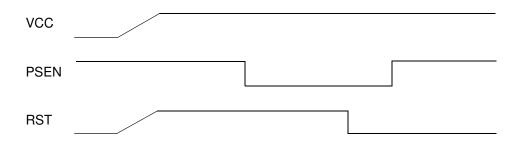

#### 24.9.4 Command Data Stream Protocol

All commands are sent using the same flow. Each frame sent by the host is echoed by the bootloader.

Figure 24-8. Command Flow

### 24.9.6.1 Example

| Blank Check ok    |     |      |         |     |      |      |    |    |    |    |    |    |    |

|-------------------|-----|------|---------|-----|------|------|----|----|----|----|----|----|----|

| HOST              | :   | 05   | 0000    | 04  | 0000 | 7fff | 01 | 78 |    |    |    |    |    |

| BOOTLOADER        | :   | 05   | 0000    | 04  | 0000 | 7fff | 01 | 78 | •  | CR | LF |    |    |

| Blank Check ok at | t a | ddre | ess xxx | X   |      |      |    |    |    |    |    |    |    |

| HOST              | :   | 05   | 0000    | 04  | 0000 | 7fff | 01 | 78 |    |    |    |    |    |

| BOOTLOADER        | :   | 05   | 0000    | 04  | 0000 | 7fff | 01 | 78 | XX | XX | CR | LF |    |

| Blank Check with  | cł  | neck | sum ei  | ror |      |      |    |    |    |    |    |    |    |

| HOST              | :   | 05   | 0000    | 04  | 0000 | 7fff | 01 | 70 |    |    |    |    |    |

| BOOTLOADER        | :   | 05   | 0000    | 04  | 0000 | 7fff | 01 | 70 | Х  | CR | LF | CR | LF |

|                   |     |      |         |     |      |      |    |    |    |    |    |    |    |

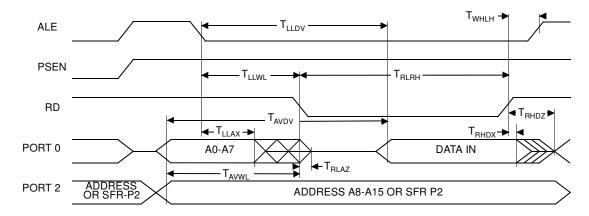

# External Program Memory Characteristics Table 25-1. Symbol Description 25.3.2

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |

### Table 25-2. AC Parameters for a Fix Clock

| Symbol            | -М  |      | Units |

|-------------------|-----|------|-------|

|                   | Min | Max  |       |

| Т                 | 25  |      | ns    |

| T <sub>LHLL</sub> | 35  |      | ns    |

| T <sub>AVLL</sub> | 5   |      | ns    |

| T <sub>LLAX</sub> | 5   |      | ns    |

| T <sub>LLIV</sub> |     | n 65 | ns    |

| T <sub>LLPL</sub> | 5   |      | ns    |

| T <sub>PLPH</sub> | 50  |      | ns    |

| T <sub>PLIV</sub> |     | 30   | ns    |

| T <sub>PXIX</sub> | 0   |      | ns    |

| T <sub>PXIZ</sub> |     | 10   | ns    |

| T <sub>AVIV</sub> |     | 80   | ns    |

| T <sub>PLAZ</sub> |     | 10   | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter for<br>-M range | Units |

|-------------------|------|-------------------|-----------|-----------------------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 25                          | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 25                          | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 30                          | ns    |

| T <sub>RHDX</sub> | Min  | x                 | х         | 0                           | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 25                          | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 45                          | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 65                          | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 30                          | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 30                          | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 30                          | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 20                          | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 20                          | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 15                          | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0                           | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 20                          | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 20                          | ns    |

| Table 25-6. | AC Parameters for a  | Variable Clock |

|-------------|----------------------|----------------|

|             | AU I alameters iul a |                |

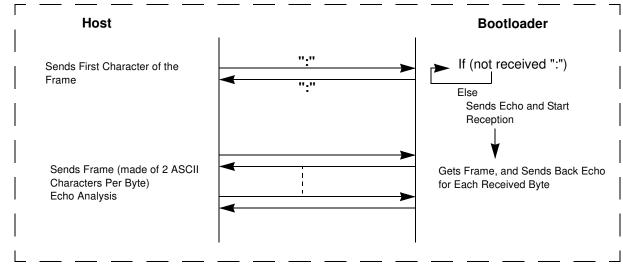

## 25.3.5 External Data Memory Write Cycle

### 25.3.6 External Data Memory Read Cycle

#### 25.3.7 Serial Port Timing - Shift Register Mode Table 25-7. Symbol Description

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 25-8.

AC Parameters for a Fix Clock

|                   | -M  |     |       |

|-------------------|-----|-----|-------|

| Symbol            | Min | Max | Units |

| T <sub>XLXL</sub> | 300 |     | ns    |

| T <sub>QVHX</sub> | 200 |     | ns    |

| T <sub>XHQX</sub> | 30  |     | ns    |

| T <sub>XHDX</sub> | 0   |     | ns    |

| T <sub>XHDV</sub> |     | 117 | ns    |