Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-rlrum |

|----------------------------|----------------------------------------------------------------------------|

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Package / Case             | 44-LQFP                                                                    |

| Mounting Type              | Surface Mount                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Oscillator Type            | External                                                                   |

| Data Converters            | -                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| RAM Size                   | 2K x 8                                                                     |

| EEPROM Size                | 2K x 8                                                                     |

| Program Memory Type        | FLASH                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Number of I/O              | 34                                                                         |

| Peripherals                | POR, PWM, WDT                                                              |

| Connectivity               | SPI, UART/USART                                                            |

| Speed                      | 60MHz                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Core Processor             | 80C51                                                                      |

| Product Status             | Obsolete                                                                   |

| Details                    |                                                                            |

# 3. SFR Mapping

The Special Function Registers (SFRs) of the AT890052/ED2 fall into the following categories:

C51 core registers: ACC, B, DPH, DPL, PSW, SP

I/O port registers: PO, P1, P2, P3, PI2

Timer registers: T2CON, T2MOD, TCON, THO, TH1, TH2TMOD, TL0, TL1, TL2, RCAP2L,

RCAP2H

Serial I/O port registers: SADDR, SADEN, SBUF, SCON

PCA (Programmable Counter Array) registers: CCOMCAPMx, CL, CH, CCAPxH, CCAPxL

(x: 0 to 4)

Power and clock control registers: PCON

Hardware Watchdog Timer registers: WDTRST, WDTPRG Interrupt system registers: IEO, IPLO, IPHO, IPL1, IPH1

Keyboard Interface registers: KBE, KBF, KBLS

SPI registers: SPCON, SPSTR, SPDAT

BRG (Baud Rate Generator) registers: BRL, BDRCON

Clock Prescaler register: CKRL

Others: AUXR, AUXR1, CKCONO, CKCON1

Table 3-1. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | EOh | Accumulator            |    |    |    |     |     |    |    |   |

| В        | FOh | B Register             |    |    |    |     |     |    |    |   |

| PSW      | DOh | Program Status Word    | CY | AC | FO | RS1 | RSO | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

Table 3-2. System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMODO | -      | POF  | GF1  | GFO  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register O     | DPU   | -     | MO     | XRS2 | XRS1 | XRSO | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -    | GF3  | 0    | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | 1     | -     | 1      | 1    | 1    | -    | -      | 1     |

| CKCKONO  | 8Fh | Clock Control Register O | i     | WDTX2 | PCAX2  | SIX2 | TK22 | T1X2 | TOX2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -    | 1    | 1    | -      | SPIX2 |

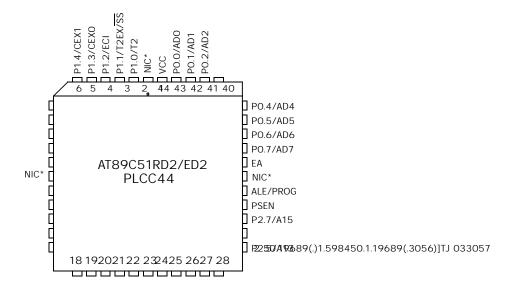

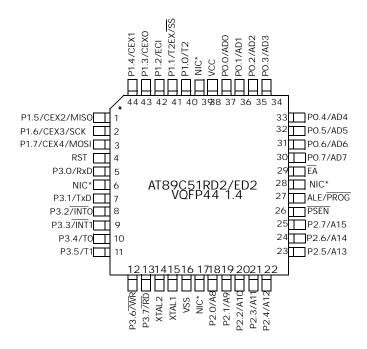

# 4. Pin Configurations

Figure 4-1. Pin Configurations

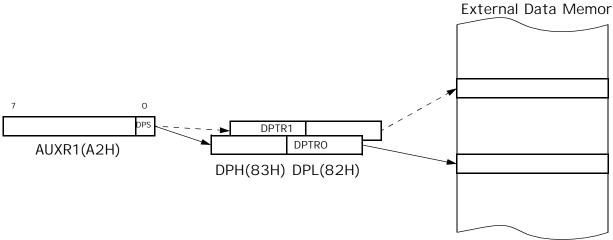

# 8. Dual Data Pointer Register (DPTR)

The additional data pointer can be used to speedoute execution and reduce code size.

The dual DPTR structure is a way by which the willpspecify the address of an external data memory location. There are two 16-bit DPTR registleat address the external memory, and a single bit called DPS = AUXR1.0 (see Table 8-1) thallows the program code to switch between them (Refer to Figure 8-1).

Figure 8-1. Use of Dual Pointer

Table 8-1. AUXR1 Register AUXR1- Auxiliary Register 1(OA2h)

| 7 | 6 | 5      | 4 | 3   | 2 | 1 | 0   |

|---|---|--------|---|-----|---|---|-----|

| - | - | ENBOOT | - | GF3 | 0 | - | DPS |

| Bit<br>Mnemonic | Description                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------|

| -               | Reserved The value read from this bit is indeterminate. @cspt this bit.                              |

| -               | Reserved The value read from this bit is indeterminate. Obcoset this bit.                            |

| ENBOOT          | Enable Boot Flash<br>Cleared to disable boot ROM.<br>Set to map the boot ROM between F800h - OFFFFh. |

| -               | Reserved The value read from this bit is indeterminate. Oboset this bit.                             |

| GF3             | This bit is a general-purpose user flag.                                                             |

| 0               | Always cleared                                                                                       |

| -               | Reserved The value read from this bit is indeterminate. Obcoset this bit.                            |

| DPS             | Data Pointer Selection Cleared to select DPTRO. Set to select DPTR1.                                 |

|                 | Mnemonic  ENBOOT  - GF3 O -                                                                          |

Reset Value = XXXX XXOXOb

Not bit addressable

Note: 1. Bit 2 stuck at 0; this allows to use INCRAUM toggle DPS without changing GF3.

#### ASSEMBLY LANGUAGE

```

; Block move using dual data pointers

; Modifies DPTRO, DPTR1, A and PSW

; note: DPS exits opposite of entry state

; unless an extra INC AUXR1 is added

OOA2 AUXR1 EQU OA2H

0000 909000MOV DPTR,#SOURCE; address of SOURCE

0003 05A2 INC AUXR1; switch data pointers

0005 90A000 MOV DPTR, #DEST; address of DEST

0008 LOOP:

0008 05A2 INC AUXR1; switch data pointers

OOOA EO MOVX A,@DPTR; get a byte from SOURCE

OOOB A3 INC DPTR; increment SOURCE address

000C 05A2 INC AUXR1; switch data pointers

OOOE FO MOVX @DPTR,A; write the byte to DEST

OOOF A3 INC DPTR; increment DEST address

0010 70F6JNZ LOOP; check for 0 terminator

0012 05A2 INC AUXR1; (optional) restore DPS

```

INC is a short (2 bytes) and fast (12 clocks)own antipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does nextly inforce the DPS bit to a particular state, but simply toggles it. In simple routines, sucthed block move example, only the fact that DPS is toggled in the proper sequence matters, national value. In other words, the block move routine works the same whether DPS is 'O' or 'entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPShien opposite state.

Table 13-4. PCA Module Modes (CCAPMn Registers)

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn N | odule Function                                    |

|-------|-------|-------|------|------|------|---------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0       | No Operation                                      |

| Х     | 1     | 0     | 0    | 0    | 0    | Х       | 16-bit capture by a positive-edge trigger on CEXn |

| Х     | 0     | 1     | 0    | 0    | 0    | х       | 16-bit capture by a negative trigger or CEXn      |

| Х     | 1     | 1     | 0    | 0    | 0    | Х       | 16-bit capture by a transition on CEXr            |

| 1     | 0     | 0     | 1    | 0    | 0    | Х       | 16-bit Software Timer/Compare mode                |

| 1     | 0     | 0     | 1    | 1    | 0    | Х       | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0       | 8-bit PWM                                         |

| 1     | 0     | 0     | 1    | Х    | 0    | Х       | Watchdog Timer (module 4 only)                    |

There are two additional registers associated with of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that strend 6-bit count when a capture occurs or a compare should occur. When a module is used in PtWAM mode these registers are used to control the duty cycle of the output (See Table&13-6).

Table 13-5. CCAPnH Registers (n = 0 - 4)

CCAPOH - PCA Module O Compare/Capture Control RegisHigh (OFAh)

CCAP1H - PCA Module 1 Compare/Capture Control Retegis High (OFBh)

CCAP2H - PCA Module 2 Compare/Capture Control RegisHigh (OFCh)

CCAP3H - PCA Module 3 Compare/Capture Control RegisHigh (OFDh)

CCAP4H - PCA Module 4 Compare/Capture Control RegrisHigh (OFEh)

| -             | -               | -                         | - | -             | -  | - | - |

|---------------|-----------------|---------------------------|---|---------------|----|---|---|

| Bit<br>Number | Bit<br>Mnemonic | Description               |   |               |    |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnH Valu |   | apture Contro | ıl |   |   |

3

Reset Value = 0000 0000b Not bit addressable

6

Table 14-3. Baud Rate Selection Table UART

| TCLK<br>(T2CON) | RCLK<br>(T2CON) | TBCK<br>(BDRCON) | RBCK<br>(BDRCON) | Clock Source<br>UART Tx | Clock Source<br>UART Rx |  |

|-----------------|-----------------|------------------|------------------|-------------------------|-------------------------|--|

| 0               | 0               | 0                | 0                | Timer 1                 | Timer 1                 |  |

| 1               | 0               | 0                | 0                | Timer 2                 | Timer 1                 |  |

| 0               | 1               | 0                | 0                | Timer 1                 | Timer 2                 |  |

| 1               | 1               | 0                | 0                | Timer 2                 | Timer 2                 |  |

| Х               | 0               | 1                | 0                | INT_BRG                 | Timer 1                 |  |

| Х               | 1               | 1                | 0                | INT_BRG                 | Timer 2                 |  |

| 0               | Х               | 0                | 1                | Timer 1                 | INT_BRG                 |  |

| 1               | Х               | 0                | 1                | Timer 2                 | INT_BRG                 |  |

| Х               | Х               | 1                | 1                | INT_BRG                 | INT_BRG                 |  |

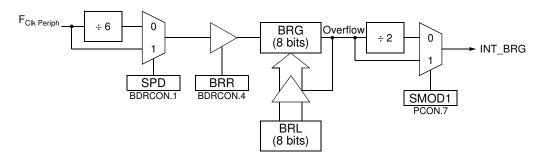

### 14.4.1 Internal Baud Rate Generator (BRG)

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow depending on the BRL reload value, the value of SPD bit (Speed Mode) in BDRCON register and the value of the SMOD1 bit in PCON register.

Figure 14-5. Internal Baud Rate

• The baud rate for UART is token by formula:

$$Baud\_Rate = \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot (256 \cdot BRL)}$$

$$BRL = 256 - \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot Baud\_Rate}$$

# 16. Serial Port Interface (SPI)

The Serial Peripheral Interface Module (SPI) allows full-duplex, synchronous, serial communication between the MCU and peripheral devices, including other MCUs.

## 16.1 Features

Features of the SPI Module include the following:

- · Full-duplex, three-wire synchronous transfers

- Master or Slave operation

- · Eight programmable Master clock rates

- Serial clock with programmable polarity and phase

- Master Mode fault error flag with MCU interrupt capability

- · Write collision flag protection

## 16.2 Signal Description

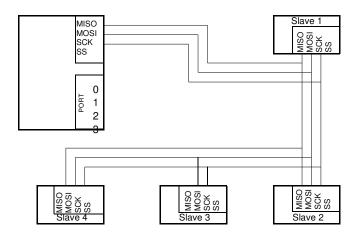

Figure 16-1 shows a typical SPI bus configuration using one Master controller and many Slave peripherals. The bus is made of three wires connecting all the devices.

Figure 16-1. SPI Master/Slaves Interconnection

The Master device selects the individual Slave devices by using four pins of a parallel port to control the four SS pins of the Slave devices.

### 16.2.1 Master Output Slave Input (MOSI)

This 1-bit signal is directly connected between the Master Device and a Slave Device. The MOSI line is used to transfer data in series from the Master to the Slave. Therefore, it is an output signal from the Master, and an input signal to a Slave. A Byte (8-bit word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

#### 16.2.2 Master Input Slave Output (MISO)

This 1-bit signal is directly connected between the Slave Device and a Master Device. The MISO line is used to transfer data in series from the Slave to the Master. Therefore, it is an output signal from the Slave, and an input signal to the Master. A Byte (8-bit word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

Table 17-7. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|---|---|---|---|---|------|------|------|

| - | - | - | - | - | SPIL | TWIL | KBDL |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 3             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 2             | SPIL            | SPI interrupt Priority bit Refer to SPIH for priority level.                 |

| 1             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 0             | KBDL            | Keyboard interrupt Priority bit Refer to KBDH for priority level.            |

Reset Value = XXXX X000b

Bit addressable

# 24. Flash/EEPROM Memory

The Flash memory increases EEPROM and ROM functionality with in-circuit electrical erasure and programming. It contains 64K bytes of program memory organized respectively in 512 pages of 128 bytes. This memory is both parallel and serial In-System Programmable (ISP). ISP allows devices to alter their own program memory in the actual end product under software control. A default serial loader (bootloader) program allows ISP of the Flash.

The programming does not require external dedicated programming voltage. The necessary high programming voltage is generated on-chip using the standard  $V_{CC}$  pins of the microcontroller.

#### 24.1 Features

- Flash EEPROM Internal Program Memory

- Boot vector allows user provided Flash loader code to reside anywhere in the Flash memory space. This configuration provides flexibility to the user.

- Default loader in Boot ROM allows programming via the serial port without the need of a user provided loader.

- Up to 64K bytes external program memory if the internal program memory is disabled (EA = 0).

- Programming and erasing voltage with standard power supply

- Read/Programming/Erase:

- Byte-wise read without wait state

- Byte or page erase and programming (10 ms)

- Typical programming time (64K bytes) is 22s with on chip serial bootloader

- Parallel programming with 87C51 compatible hardware interface to programmer

- Programmable security for the code in the Flash

- · 100K write cycles

- 10 years data retention

## 24.2 Flash Programming and Erasure

The 64-K byte Flash is programmed by bytes or by pages of 128 bytes. It is not necessary to erase a byte or a page before programming. The programming of a byte or a page includes a self erase before programming.

There are three methods of programming the Flash memory:

- 1. The on-chip ISP bootloader may be invoked which will use low level routines to program the pages. The interface used for serial downloading of Flash is the UART.

- 2. The Flash may be programmed or erased in the end-user application by calling low-level routines through a common entry point in the Boot ROM.

- 3. The Flash may be programmed using the parallel method by using a conventional EPROM programmer. The parallel programming method used by these devices is similar to that used by EPROM 87C51 but it is not identical and the commercially available programmers need to have support for the AT89C51RD2/ED2. The bootloader and the Application Programming Interface (API) routines are located in the BOOT ROM.