# E·XFL

#### Atmel - AT89C51ED2-RLTUM Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 60MHz                                                       |

| Connectivity               | SPI, UART/USART                                             |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 34                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LQFP                                                     |

| Supplier Device Package    | 44-VQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89c51ed2-rltum |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

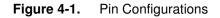

### 4. Pin Configurations

### 7. Enhanced Features

In comparison to the original 80C52, the AT89C51RD2/ED2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- · Power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

#### 7.1 X2 Feature

The AT89C51RD2/ED2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

#### 7.1.1 Description

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 7-1 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1  $\div$  2 to avoid glitches when switching from X2 to STD mode. Figure 7-2 shows the switching mode waveforms.

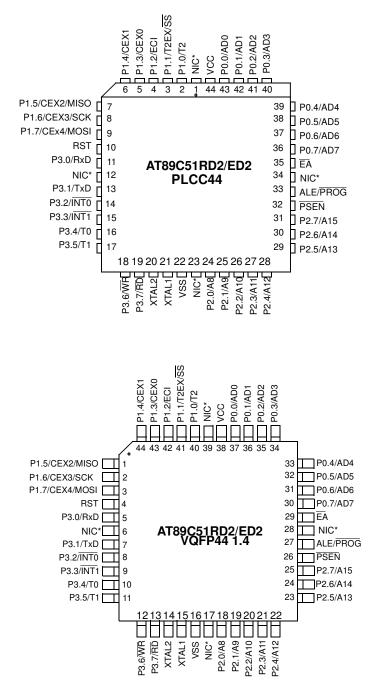

### 9. Expanded RAM (XRAM)

The AT89C51RD2/ED2 provides additional on-chip random access memory (RAM) space for increased data parameter handling and high level language usage.

AT89C51RD2/ED2 device haS expanded RAM in external data space configurable up to 1792 bytes (see Table 9-1).

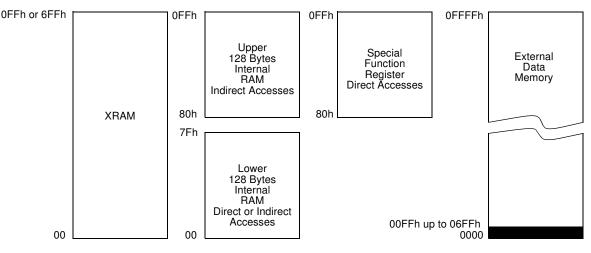

The AT89C51RD2/ED2 internal data memory is mapped into four separate segments.

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 9-1).

The lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7Fh, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

- Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0h (which is P2).

- Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example: MOV @R0, # data where R0 contains 0A0h, accesses the data byte at address 0A0h, rather than P2 (whose address is 0A0h).

- The XRAM bytes can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory which is physically located on-chip, logically occupies the first bytes of external data memory. The bits XRS0 and XRS1 are used to hide a

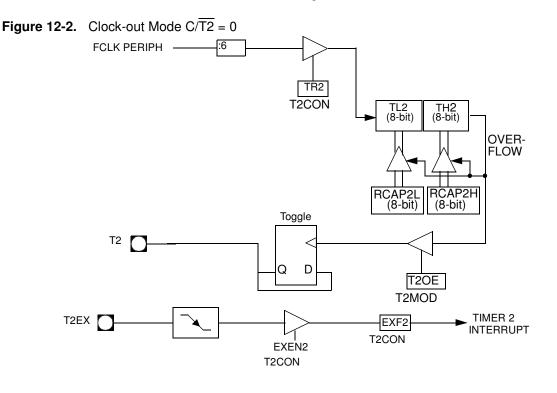

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

#### 12.3 Registers

Table 12-1.T2CON RegisterT2CON - Timer 2 Control Register (C8h)

| 7   | 6    | 5    | 4    | 3     | 2   | 1     | 0       |

|-----|------|------|------|-------|-----|-------|---------|

| TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |

#### Table 12-2. T2MOD Register

T2MOD - Timer 2 Mode Control Register (C9h)

| 7             | 6               | 5                          | 4                 | 3                               | 2                | 1      | 0    |

|---------------|-----------------|----------------------------|-------------------|---------------------------------|------------------|--------|------|

| -             | -               | -                          | -                 | -                               | -                | T2OE   | DCEN |

| Bit<br>Number | Bit<br>Mnemonic | Description                |                   |                                 |                  |        |      |

| 7             | -               | Reserved<br>The value read | d from this bit i | s indeterminate                 | . Do not set thi | s bit. |      |

| 6             | -               | Reserved<br>The value read | d from this bit i | s indeterminate                 | . Do not set thi | s bit. |      |

| 5             | -               | Reserved<br>The value read | d from this bit i | s indeterminate                 | . Do not set thi | s bit. |      |

| 4             | -               | Reserved<br>The value read | d from this bit i | s indeterminate                 | . Do not set thi | s bit. |      |

| 3             | -               | Reserved<br>The value read | d from this bit i | s indeterminate                 | . Do not set thi | s bit. |      |

| 2             | -               | Reserved<br>The value read | d from this bit i | s indeterminate                 | . Do not set thi | s bit. |      |

| 1             | T2OE            |                            |                   | as clock input c<br>ock output. | or I/O port.     |        |      |

| 0             | DCEN            |                            |                   | s up/down cour<br>down counter. | iter.            |        |      |

Reset Value = XXXX XX00b Not bit addressable

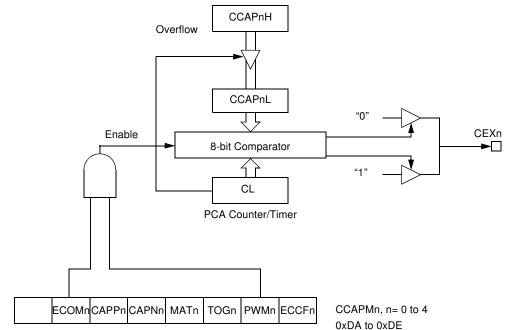

#### Figure 13-6. PCA PWM Mode

#### 13.5 PCA Watchdog Timer

An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 13-4 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. Periodically change the compare value so it will never match the PCA timer.

- 2. Periodically change the PCA timer value so it will never match the compare values.

- 3. Disable the watchdog by clearing the WDTE bit before a match occurs and then reenable it.

```

Slave C:SADDR1111 0010b

<u>SADEN1111 1101b</u>

Given1111 00X1b

```

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1.To communicate with slave A only, the master must send an address where bit 0 is clear (e. g. 1111 0000b). For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e. g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e. g. 1111 0001b).

#### 14.2.2 Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e. g. :

```

SADDR0101 0110b

SADEN1111 1100b

Broadcast =SADDR OR SADEN1111 111Xb

```

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Broadcast1111 1X11b,

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Broadcast1111 1X11B,

Slave C:SADDR=1111 0011b

<u>SADEN1111 1101b</u>

Broadcast1111 1111b

```

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

#### 14.2.3 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i. e. the given and broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

Table 15-2.KBE RegisterKBE-Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5             | 4                                                           | 3 | 2                | 1             | 0 |  |  |

|---------------|-----------------|---------------|-------------------------------------------------------------|---|------------------|---------------|---|--|--|

| KBE7          | KBE6            | KBE5          | KBE5 KBE4 KBE3 KBE2 KBE1                                    |   |                  |               |   |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   |                                                             |   |                  |               |   |  |  |

| 7             | KBE7            | Cleared to en | e <b>7 Enable bit</b><br>able standard I<br>KBF.7 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 6             | KBE6            | Cleared to en | e <b>6 Enable bit</b><br>able standard I<br>KBF.6 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 5             | KBE5            | Cleared to en | e <b>5 Enable bit</b><br>able standard I<br>KBF.5 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 4             | KBE4            | Cleared to en | e <b>4 Enable bit</b><br>able standard I<br>KBF.4 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 3             | KBE3            | Cleared to en | e <b>3 Enable bit</b><br>able standard I<br>KBF.3 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 2             | KBE2            | Cleared to en | e <b>2 Enable bit</b><br>able standard I<br>KBF.2 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 1             | KBE1            | Cleared to en | <b>e 1 Enable bit</b><br>able standard I<br>KBF.1 bit in KE |   | enerate an inter | rupt request. |   |  |  |

| 0             | KBE0            | Cleared to en | e <b>0 Enable bit</b><br>able standard I<br>KBF.0 bit in KE |   | enerate an inter | rupt request. |   |  |  |

Reset Value = 0000 0000b

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                         |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | MSTR         | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                       |

| 3          | CPOL         | <b>Clock Polarity</b><br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                           |

| 2          | СРНА         | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the idle state (see<br>CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see<br>CPOL).                                                 |

| 1          | SPR1         | SPR2         SPR1         SPR0 Serial Peripheral Rate           0         0         1F <sub>CLK PERIPH</sub> /2           0         0         1F <sub>CLK PERIPH</sub> /4           0         1         0F <sub>CLK PERIPH</sub> /8 |

|            | SPR0         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                               |

Reset Value = 0001 0100b

Not bit addressable

#### 16.3.5.2 Serial Peripheral Status Register (SPSTA)

The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 16-4 describes the SPSTA register and explains the use of every bit in the register.

#### Table 16-4. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7          | 6               | 5                                                                     | 4                       | 3                | 2 | 1 | 0             |

|------------|-----------------|-----------------------------------------------------------------------|-------------------------|------------------|---|---|---------------|

| SPIF       | WCOL            | SSERR                                                                 | MODF                    | -                | - | - | -             |

| Bit Number | Bit<br>Mnemonic | Description                                                           |                         |                  |   |   |               |

| 7          | SPIF            | Serial Periphe<br>Cleared by har<br>clearing seque<br>Set by hardwa   | dware to indicance.     | ate data transfe |   |   | oproved by a  |

| 6          | WCOL            | Write Collision<br>Cleared by har<br>clearing seque<br>Set by hardwar | dware to indica<br>nce. |                  |   |   | approved by a |

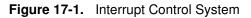

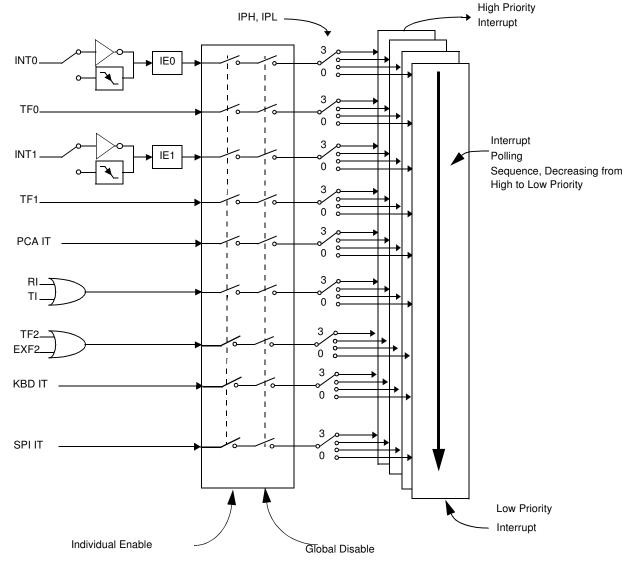

### 17. Interrupt System

The AT89C51RD2/ED2 has a total of 9 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt and the PCA global interrupt. These interrupts are shown in Figure 17-1.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 17-4 and Table 17-6). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (Table 17-7) and in the Interrupt Priority High register (Table 17-5 and Table 17-6) shows the bit values and priority levels associated with each combination.

### **18. Power Management**

#### 18.1 Introduction

Two power reduction modes are implemented in the AT89C51RD2/ED2. The Idle mode and the Power-Down mode. These modes are detailed in the following sections. In addition to these power reduction modes, the clocks of the core and peripherals can be dynamically divided by 2 using the X2 mode detailed in Section "Enhanced Features", page 17.

#### 18.2 Idle Mode

Idle mode is a power reduction mode that reduces the power consumption. In this mode, program execution halts. Idle mode freezes the clock to the CPU at known states while the peripherals continue to be clocked. The CPU status before entering Idle mode is preserved, i.e., the program counter and program status word register retain their data for the duration of Idle mode. The contents of the SFRs and RAM are also retained. The status of the Port pins during Idle mode is detailed in Table 18-1.

#### 18.2.1 Entering Idle Mode

To enter Idle mode, set the IDL bit in PCON register (see Table 18-2). The AT89C51RD2/ED2 enters Idle mode upon execution of the instruction that sets IDL bit. The instruction that sets IDL bit is the last instruction executed.

Note: If IDL bit and PD bit are set simultaneously, the AT89C51RD2/ED2 enters Power-Down mode. Then it does not go in Idle mode when exiting Power-Down mode.

#### 18.2.2 Exiting Idle Mode

There are two ways to exit Idle mode:

- 1. Generate an enabled interrupt.

- Hardware clears IDL bit in PCON register which restores the clock to the CPU. Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Idle mode. The general purpose flags (GF1 and GF0 in PCON register) may be used to indicate whether an interrupt occurred during normal operation or during Idle mode. When Idle mode is exited by an interrupt, the interrupt service routine may examine GF1 and GF0.

- 2. Generate a reset.

- A logic high on the RST pin clears IDL bit in PCON register directly and asynchronously. This restores the clock to the CPU. Program execution momentarily resumes with the instruction immediately following the instruction that activated the Idle mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT89C51RD2/ED2 and vectors the CPU to address C:0000h.

- Note: During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated Idle mode should not write to a Port pin or to the external RAM.

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                 |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | EEE             | Enable EEPROM Space bit<br>Set to map the EEPROM space during MOVX instructions (Write or Read to the<br>EEPROM.<br>Clear to map the XRAM space during MOVX.                |

| 0          | EEBUSY          | <b>Programming Busy flag</b><br>Set by hardware when programming is in progress.<br>Cleared by hardware when programming is done.<br>Can not be set or cleared by software. |

Reset Value = XXXX XX00b

Not bit addressable

#### 24.3 Flash Registers and Memory Map

The AT89C51RD2/ED2 Flash memory uses several registers for its management:

- Hardware register can only be accessed through the parallel programming modes which are handled by the parallel programmer.

- Software registers are in a special page of the Flash memory which can be accessed through the API or with the parallel programming modes. This page, called "Extra Flash Memory", is not in the internal Flash program memory addressing space.

#### 24.3.1 Hardware Register

The only hardware register of the AT89C51RD2/ED2 is called Hardware Byte or Hardware Security Byte (HSB).

| 7             | 6               | 5                                               | 4                                                                                                                                                | 3             | 2              | 1           | 0   |  |

|---------------|-----------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-------------|-----|--|

| X2            | BLJB            | -                                               | -                                                                                                                                                | XRAM          | LB2            | LB1         | LB0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                     |                                                                                                                                                  |               |                |             |     |  |

| 7             | X2              | <b>X2 Mode</b><br>Programmed ('<br>Unprogrammed | ,                                                                                                                                                | ,             | •              | ,           |     |  |

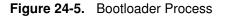

| 6             | BLJB            | Boot Loader J<br>Unprogrammed<br>Programmed (*  | d ('1' value) to s                                                                                                                               |               |                |             |     |  |

| 5             | -               | Reserved                                        |                                                                                                                                                  |               |                |             |     |  |

| 4             | -               | Reserved                                        |                                                                                                                                                  |               |                |             |     |  |

| 3             | XRAM            | Programmed to                                   | <b>CRAM config bit (only programmable by programmer tools)</b><br>Programmed to inhibit XRAM.<br>Jnprogrammed, this bit to valid XRAM (Default). |               |                |             |     |  |

| 2-0           | LB2-0           | User Memory<br>See Table 24-2                   | •                                                                                                                                                | ly programmal | ole by progran | nmer tools) |     |  |

Table 24-1.

Hardware Security Byte (HSB)

Boot Loader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is programmed ('0' value) the boot address is F800h.

- When this bit is unprogrammed ('1' value) the boot address is 0000h.

By default, this bit is programmed and the ISP is enabled.

#### 24.3.2 Flash Memory Lock Bits

The three lock bits provide different levels of protection for the on-chip code and data when programmed as shown in Table 24-2.

| Program Lock Bits |     |     |     |                                                                                                                                                                                                                                                                                         |

|-------------------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security<br>Level | LB0 | LB1 | LB2 | Protection Description                                                                                                                                                                                                                                                                  |

| 1                 | U   | U   | U   | No program lock features enabled.                                                                                                                                                                                                                                                       |

| 2                 | Ρ   | U   | U   | MOVC instruction executed from external program memory is disabled from fetching code bytes from internal memory, EA is sampled and latched on reset, and further parallel programming of the on chip code memory is disabled. ISP and software programming with API are still allowed. |

| 3                 | х   | Р   | U   | Same as 2, also verify code memory through parallel programming interface is disabled.                                                                                                                                                                                                  |

| 4                 | х   | Х   | Р   | Same as 3, also external execution is disabled (Default).                                                                                                                                                                                                                               |

Note: U: Unprogrammed or "one" level.

P: Programmed or "zero" level.

X: Do not care

WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

These security bits protect the code access through the parallel programming interface. They are set by default to level 4. The code access through the ISP is still possible and is controlled by the "software security bits" which are stored in the extra Flash memory accessed by the ISP firmware.

To load a new application with the parallel programmer, a chip erase must first be done. This will set the HSB in its inactive state and will erase the Flash memory. The part reference can always be read using Flash parallel programming modes.

#### 24.3.3 Default Values

The default value of the HSB provides parts ready to be programmed with ISP:

- BLJB: Programmed force ISP operation.

- X2: Unprogrammed to force X1 mode (Standard Mode).

- XRAM: Unprogrammed to valid XRAM

- LB2-0: Security level four to protect the code from a parallel access with maximum security.

#### 24.3.4 Software Registers

Several registers are used in factory and by parallel programmers. These values are used by Atmel ISP.

These registers are in the "Extra Flash Memory" part of the Flash memory. This block is also called "XAF" or eXtra Array Flash. They are accessed in the following ways:

- · Commands issued by the parallel memory programmer.

- · Commands issued by the ISP software.

- Calls of API issued by the application software.

Several software registers are described in Table 24-3.

#### Table 24-3. Default Values

| Mnemonic | Definition           | Default value | Description |

|----------|----------------------|---------------|-------------|

| SBV      | Software Boot Vector | FCh           |             |

#### Figure 24-2. Diagram Context Description

#### 24.6.2 Acronyms

- ISP: In-System Programming

- SBV: Software Boot Vector

- BSB: Boot Status Byte

- SSB: Software Security Byte

- HW: Hardware Byte

#### 24.6.5 Boot Process

| Frequency<br>(MHz)                                       |                      |                      |                      |                |                      |                      |                      |                      |                      |

|----------------------------------------------------------|----------------------|----------------------|----------------------|----------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Baudrate (kHz)                                           | 1.8432               | 2                    | 2.4576               | 3              | 3.6864               | 4                    | 5                    | 6                    | 7.3728               |

| 4800                                                     | OK                   | -                    | ОК                   | OK             | OK                   | OK                   | OK                   | OK                   | OK                   |

| 9600                                                     | ОК                   | -                    | OK                   | OK             | OK                   | OK                   | OK                   | ОК                   | OK                   |

| 19200                                                    | ОК                   | -                    | OK                   | OK             | OK                   | -                    | -                    | ОК                   | OK                   |

| 38400                                                    | -                    | -                    | OK                   |                | OK                   | -                    | OK                   | ОК                   | ОК                   |

| 57600                                                    | -                    | -                    | -                    | -              | OK                   | -                    | -                    | -                    | OK                   |

| 115200                                                   | -                    | -                    | -                    | -              | -                    | -                    | -                    | -                    | OK                   |

| Fraguanay                                                |                      |                      |                      |                |                      |                      |                      |                      |                      |

| Frequency<br>(MHz)                                       | 0                    | 10                   | 11 0502              | 10             | 14 746               | 16                   | 20                   | 24                   | 26.6                 |

| (MHz)<br>Baudrate (kHz)                                  | 8                    | 10<br>OK             | 11.0592              | 12             | 14.746               | 16<br>OK             | <b>20</b>            | 24                   | 26.6                 |

| (MHz)<br>Baudrate (kHz)<br>2400                          | ОК                   | OK                   | OK                   | OK             | OK                   | OK                   | OK                   | OK                   | ОК                   |

| (MHz)<br>Baudrate (kHz)                                  |                      |                      |                      |                |                      |                      |                      |                      |                      |

| (MHz)<br>Baudrate (kHz)<br>2400                          | ОК                   | OK                   | OK                   | OK             | OK                   | OK                   | OK                   | OK                   | ОК                   |

| (MHz)<br>Baudrate (kHz)<br>2400<br>4800                  | ОК<br>ОК             | OK<br>OK             | OK<br>OK             | OK<br>OK       | OK<br>OK             | OK<br>OK             | OK<br>OK             | OK<br>OK             | OK<br>OK             |

| (MHz)<br>Baudrate (kHz)<br>2400<br>4800<br>9600          | ОК<br>ОК<br>ОК       | OK<br>OK<br>OK       | ОК<br>ОК<br>ОК       | OK<br>OK<br>OK | OK<br>OK<br>OK       | OK<br>OK<br>OK       | ОК<br>ОК<br>ОК       | OK<br>OK<br>OK       | ОК<br>ОК<br>ОК       |

| (MHz)<br>Baudrate (kHz)<br>2400<br>4800<br>9600<br>19200 | ОК<br>ОК<br>ОК<br>ОК | OK<br>OK<br>OK<br>OK | ОК<br>ОК<br>ОК<br>ОК | OK<br>OK<br>OK | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК | ОК<br>ОК<br>ОК<br>ОК |

| Table 24-8. | Autobaud Performances | (Continued) |

|-------------|-----------------------|-------------|

|             |                       |             |

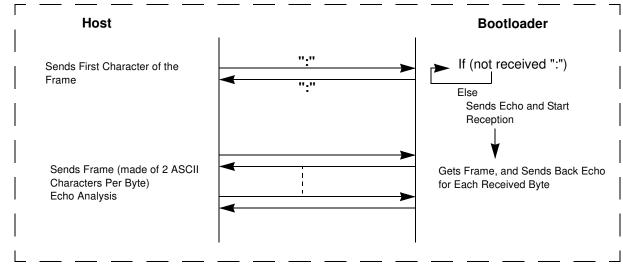

#### 24.9.4 Command Data Stream Protocol

All commands are sent using the same flow. Each frame sent by the host is echoed by the bootloader.

Figure 24-8. Command Flow

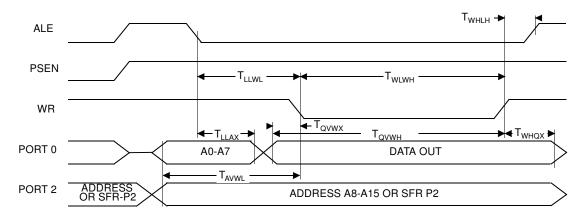

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter for<br>-M range | Units |

|-------------------|------|-------------------|-----------|-----------------------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 25                          | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 25                          | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 30                          | ns    |

| T <sub>RHDX</sub> | Min  | x                 | х         | 0                           | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 25                          | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 45                          | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 65                          | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 30                          | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 30                          | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 30                          | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 20                          | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 20                          | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 15                          | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0                           | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 20                          | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 20                          | ns    |

| Table 25-6. | AC Parameters for a  | Variable Clock |

|-------------|----------------------|----------------|

|             | AU I alameters iul a |                |

#### 25.3.5 External Data Memory Write Cycle

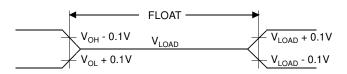

#### 25.3.11 Float Waveforms

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$  mA.

#### 25.3.12 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.

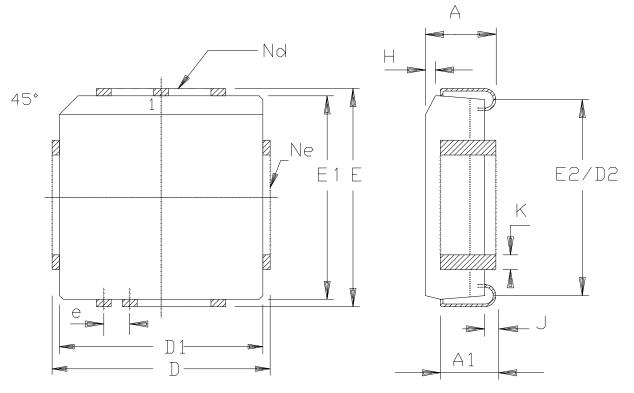

### 27. Packaging Information

### 27.1 PLCC44

|         | ММ     |        | INCH  |       |

|---------|--------|--------|-------|-------|

| A       | 4, 20  | 4. 57  | , 165 | . 180 |

| A1      | 2, 29  | 3. 04  | , 090 | . 120 |

| D       | 17.40  | 17.65  | . 685 | . 695 |

| D 1     | 16.44  | 16, 66 | , 647 | . 656 |

| D2      | 14, 99 | 16.00  | , 590 | . 630 |

| E       | 17.40  | 17.65  | , 685 | . 695 |

| E 1     | 16,44  | 16, 66 | , 647 | . 656 |

| E2      | 14, 99 | 16.00  | , 590 | . 630 |

| e       | 1, 27  | BSC    | , 050 | BSC   |

| Н       | 1.07   | 1.42   | , 042 | . 056 |

| J       | 0.51   | _      | . 020 | _     |

| К       | 0, 33  | 0, 53  | . 013 | . 021 |

| Nd      | 1 1    |        | 1 1   |       |

| Ne      | 1 1    |        | 1 1   |       |

| PKG STD |        | 00     |       |       |