# E·XFL

#### Atmel - AT89C51ED2-SLRUM Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 60MHz                                                       |

| Connectivity               | SPI, UART/USART                                             |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 34                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LCC (J-Lead)                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89c51ed2-slrum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

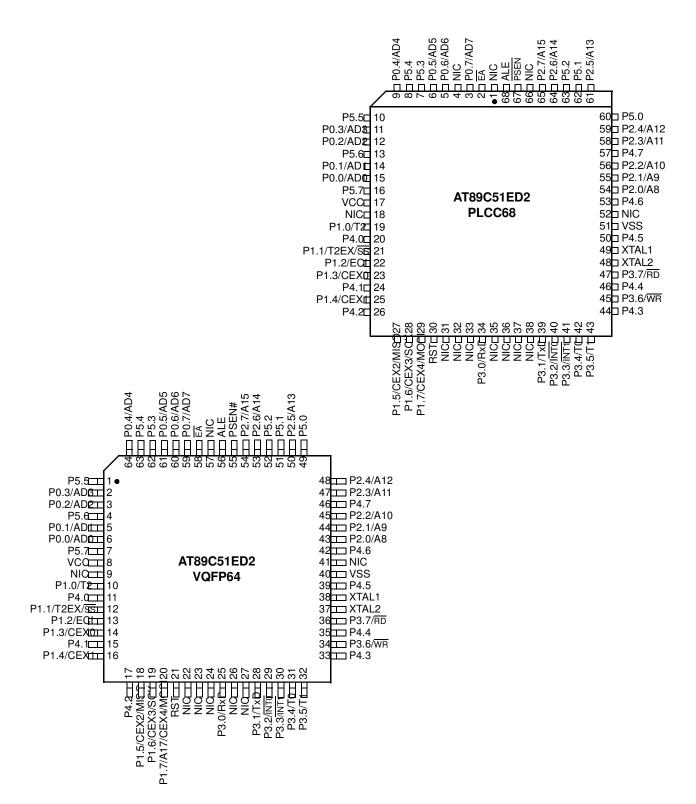

NIC: Not Internaly Connected

#### Table 4-1.Pin Description

|                 |         | Pin N            | lumber                                  |                                         | Turne |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|---------|------------------|-----------------------------------------|-----------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic        | PLCC44  | VQFP44           | PLCC68                                  | VQFP64                                  | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub> | 22      | 16               | 51                                      | 40                                      | I     | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>cc</sub> | 44      | 38               | 17                                      | 8                                       | I     | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P0.0 - P0.7     | 43 - 36 | 37 - 30          | 15, 14,<br>12, 11,<br>9,6, 5, 3         | 6, 5, 3, 2,<br>64,<br>61,60,59          | I/O   | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code bytes during EPROM programming. External pull-ups are required during program verification during which P0 outputs the code bytes. |

| P1.0 - P1.7     | 2 - 9   | 40 - 44<br>1 - 3 | 19, 21,<br>22, 23,<br>25, 27,<br>28, 29 | 10, 12,<br>13, 14,<br>16, 18,<br>19, 20 | I/O   | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address byte during memory programming and verification.<br>Alternate functions for AT89C51RD2/ED2 Port 1 include:                                                                                                                                                         |

|                 | 2       | 40               | 19                                      | 10                                      | I/O   | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I/O   | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | 3       | 41               | 21                                      | 12                                      | I/O   | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I     | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |         |                  |                                         |                                         | I     | SS: SPI Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 | 4       | 42               | 22                                      | 13                                      | I/O   | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I     | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | 5       | 43               | 23                                      | 14                                      | I/O   | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I/O   | CEX0: Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 6       | 44               | 25                                      | 16                                      | I/O   | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I/O   | CEX1: Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 | 7       | 1                | 27                                      | 18                                      | I/O   | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I/O   | CEX2: Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |         |                  |                                         |                                         | I/O   | MISO: SPI Master Input Slave Output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |         |                  |                                         |                                         |       | When SPI is in master mode, MISO receives data from the slave peripheral. When SPI is in slave mode, MISO outputs data to the maste controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 | 8       | 2                | 28                                      | 19                                      | I/O   | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |         |                  |                                         |                                         | I/O   | CEX3: Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |         |                  |                                         |                                         | I/O   | SCK: SPI Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### Table 4-1. Pin Description (Continued)

|             |                | Pin N        | lumber                                  |                                         | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------|--------------|-----------------------------------------|-----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    | PLCC44         | VQFP44       | PLCC68                                  | VQFP64                                  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 9              | 3            | 29                                      | 20                                      | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |              |                                         |                                         | I/O  | CEX4: Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |              |                                         |                                         | I/O  | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                |              |                                         |                                         |      | When SPI is in master mode, MOSI outputs data to the slave peripheral.<br>When SPI is in slave mode, MOSI receives data from the master<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XTALA1      | 21             | 15           | 49                                      | 38                                      | Ι    | <b>XTALA 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XTALA2      | 20             | 14           | 48                                      | 37                                      | 0    | XTALA 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P2.0 - P2.7 | 24 - 31        | 18 - 25      | 54, 55,<br>56, 58,<br>59, 61,<br>64, 65 | 43, 44,<br>45, 47,<br>48, 50,<br>53, 54 | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |

| P3.0 - P3.7 | 11,<br>13 - 19 | 5,<br>7 - 13 | 34, 39,<br>40, 41,<br>42, 43,<br>45, 47 | 25, 28,<br>29, 30,<br>31, 32,<br>34, 36 | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |

|             | 11             | 5            | 34                                      | 25                                      | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 13             | 7            | 39                                      | 28                                      | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 14             | 8            | 40                                      | 29                                      | I    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 15             | 9            | 41                                      | 30                                      | I    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 16             | 10           | 42                                      | 31                                      | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 17             | 11           | 43                                      | 32                                      | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 18             | 12           | 45                                      | 34                                      | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 19             | 13           | 47                                      | 36                                      | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P4.0 - P4.7 | -              | -            | 20, 24,<br>26, 44,<br>46, 50,<br>53, 57 | 11, 15,<br>17,33,<br>35,39,<br>42, 46   | I/O  | <b>Port 4:</b> Port 4 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| P5.0 - P5.7 | -              | -            | 60, 62,<br>63, 7, 8,<br>10, 13, 16      | 49, 51,<br>52, 62,<br>63, 1, 4, 7       | I/O  | <b>Port 5:</b> Port 5 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| RST         | 10             | 4            | 30                                      | 21                                      | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                       |

12 AT89C51RD2/ED2

### 7. Enhanced Features

In comparison to the original 80C52, the AT89C51RD2/ED2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- · Power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

#### 7.1 X2 Feature

The AT89C51RD2/ED2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

#### 7.1.1 Description

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

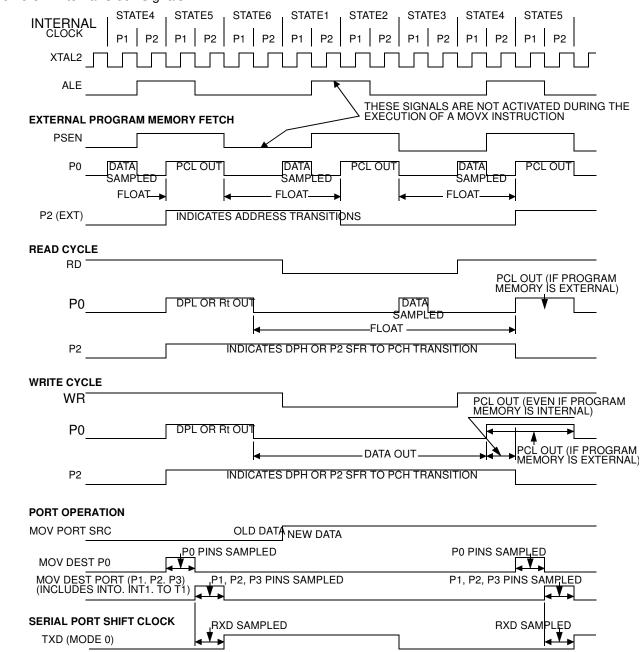

Figure 7-1 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1  $\div$  2 to avoid glitches when switching from X2 to STD mode. Figure 7-2 shows the switching mode waveforms.

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |  |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|--|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |  |

| x     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |  |

| x     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative trigger on CEXn      |  |

| х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |  |

| 1     | 0     | 0     | 1    | 0    | 0    | Х     | 16-bit Software Timer/Compare mode.               |  |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |  |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |  |

| 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer (module 4 only)                    |  |

Table 13-4.

PCA Module Modes (CCAPMn Registers)

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output (See Table 13-5 & Table 13-6).

Table 13-5.CCAPnH Registers (n = 0 - 4)

- CCAP0H PCA Module 0 Compare/Capture Control Register High (0FAh)

- CCAP1H PCA Module 1 Compare/Capture Control Register High (0FBh)

- CCAP2H PCA Module 2 Compare/Capture Control Register High (0FCh)

- CCAP3H PCA Module 3 Compare/Capture Control Register High (0FDh)

- CCAP4H PCA Module 4 Compare/Capture Control Register High (0FEh)

| 7             | 6               | 5                         | 4 | 3             | 2 | 1 | 0 |

|---------------|-----------------|---------------------------|---|---------------|---|---|---|

| -             | -               | -                         | - | -             | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description               |   |               |   |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnH Valu |   | pture Control |   |   |   |

Reset Value = 0000 0000b Not bit addressable

| TCLK<br>(T2CON) | RCLK<br>(T2CON) | TBCK<br>(BDRCON) | RBCK<br>(BDRCON) | Clock Source<br>UART Tx | Clock Source<br>UART Rx |

|-----------------|-----------------|------------------|------------------|-------------------------|-------------------------|

| 0               | 0               | 0                | 0                | Timer 1                 | Timer 1                 |

| 1               | 0               | 0                | 0                | Timer 2                 | Timer 1                 |

| 0               | 1               | 0                | 0                | Timer 1                 | Timer 2                 |

| 1               | 1               | 0                | 0                | Timer 2                 | Timer 2                 |

| Х               | 0               | 1                | 0                | INT_BRG                 | Timer 1                 |

| Х               | 1               | 1                | 0                | INT_BRG                 | Timer 2                 |

| 0               | Х               | 0                | 1                | Timer 1                 | INT_BRG                 |

| 1               | х               | 0                | 1                | Timer 2                 | INT_BRG                 |

| Х               | х               | 1                | 1                | INT_BRG                 | INT_BRG                 |

Table 14-3. Baud Rate Selection Table UART

#### 14.4.1 Internal Baud Rate Generator (BRG)

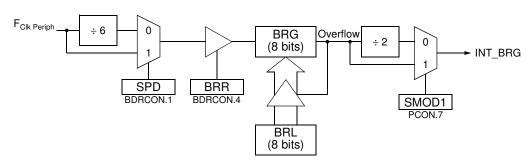

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow depending on the BRL reload value, the value of SPD bit (Speed Mode) in BDRCON register and the value of the SMOD1 bit in PCON register.

Figure 14-5. Internal Baud Rate

• The baud rate for UART is token by formula:

$Baud\_Rate = \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot (256 \text{ -BRL})}$

$BRL = 256 - \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot Baud_Rate}$

### 16. Serial Port Interface (SPI)

The Serial Peripheral Interface Module (SPI) allows full-duplex, synchronous, serial communication between the MCU and peripheral devices, including other MCUs.

### 16.1 Features

Features of the SPI Module include the following:

- Full-duplex, three-wire synchronous transfers

- Master or Slave operation

- · Eight programmable Master clock rates

- · Serial clock with programmable polarity and phase

- · Master Mode fault error flag with MCU interrupt capability

- Write collision flag protection

#### 16.2 Signal Description

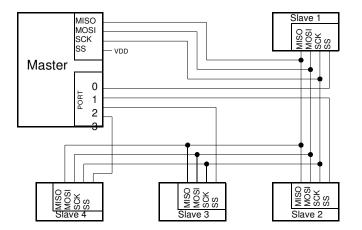

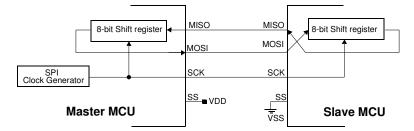

Figure 16-1 shows a typical SPI bus configuration using one Master controller and many Slave peripherals. The bus is made of three wires connecting all the devices.

Figure 16-1. SPI Master/Slaves Interconnection

The Master device selects the individual Slave devices by using four pins of a parallel port to control the four  $\overline{SS}$  pins of the Slave devices.

#### 16.2.1 Master Output Slave Input (MOSI)

This 1-bit signal is directly connected between the Master Device and a Slave Device. The MOSI line is used to transfer data in series from the Master to the Slave. Therefore, it is an output signal from the Master, and an input signal to a Slave. A Byte (8-bit word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

#### 16.2.2 Master Input Slave Output (MISO)

This 1-bit signal is directly connected between the Slave Device and a Master Device. The MISO line is used to transfer data in series from the Slave to the Master. Therefore, it is an output signal from the Slave, and an input signal to the Master. A Byte (8-bit word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

#### 16.2.3 SPI Serial Clock (SCK)

This signal is used to synchronize the data movement both in and out of the devices through their MOSI and MISO lines. It is driven by the Master for eight clock cycles which allows to exchange one Byte on the serial lines.

#### 16.2.4 Slave Select (SS)

Each Slave peripheral is selected by one Slave Select pin  $(\overline{SS})$ . This signal must stay low for any message for a Slave. It is obvious that only one Master ( $\overline{SS}$  high level) can drive the network. The Master may select each Slave device by software through port pins (Figure 16-2). To prevent bus conflicts on the MISO line, only one slave should be selected at a time by the Master for a transmission.

In a Master configuration, the  $\overline{SS}$  line can be used in conjunction with the MODF flag in the SPI Status register (SPSTA) to prevent multiple masters from driving MOSI and SCK (see Error conditions).

A high level on the  $\overline{SS}$  pin puts the MISO line of a Slave SPI in a high-impedance state.

The SS pin could be used as a general-purpose if the following conditions are met:

- The device is configured as a Master and the SSDIS control bit in SPCON is set. This kind of configuration can be found when only one Master is driving the network and there is no way that the  $\overline{SS}$  pin could be pulled low. Therefore, the MODF flag in the SPSTA will never be set<sup>(1)</sup>.

- The Device is configured as a Slave with CPHA and SSDIS control bits set<sup>(2)</sup>. This kind of configuration can happen when the system comprises one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device.

- Note: 1. Clearing SSDIS control bit does not clear MODF.

- Special care should be taken not to set SSDIS control bit when CPHA = '0' because in this mode, the SS is used to start the transmission.

#### 16.2.5 Baud Rate

In Master mode, the baud rate can be selected from a baud rate generator which is controlled by three bits in the SPCON register: SPR2, SPR1 and SPR0.The Master clock is selected from one of seven clock rates resulting from the division of the internal clock by 2, 4, 8, 16, 32, 64 or 128.

Table 16-1 gives the different clock rates selected by SPR2:SPR1:SPR0.

| Table 16-1. | SPI Master Baud Rate Selection |  |

|-------------|--------------------------------|--|

|             |                                |  |

| SPR2 | SPR1 | SPR0 | Clock Rate                   | Baud Rate Divisor (BD) |

|------|------|------|------------------------------|------------------------|

| 0    | 0    | 0    | F <sub>CLK PERIPH</sub> /2   | 2                      |

| 0    | 0    | 1    | F <sub>CLK PERIPH</sub> /4   | 4                      |

| 0    | 1    | 0    | F <sub>CLK PERIPH</sub> /8   | 8                      |

| 0    | 1    | 1    | F <sub>CLK PERIPH</sub> /16  | 16                     |

| 1    | 0    | 0    | F <sub>CLK PERIPH</sub> /32  | 32                     |

| 1    | 0    | 1    | F <sub>CLK PERIPH</sub> /64  | 64                     |

| 1    | 1    | 0    | F <sub>CLK PERIPH</sub> /128 | 128                    |

| 1    | 1    | 1    | Don't Use                    | No BRG                 |

#### 16.3.1.1 Master Mode

The SPI operates in Master mode when the Master bit, MSTR <sup>(1)</sup>, in the SPCON register is set. Only one Master SPI device can initiate transmissions. Software begins the transmission from a Master SPI Module by writing to the Serial Peripheral Data Register (SPDAT). If the shift register is empty, the Byte is immediately transferred to the shift register. The Byte begins shifting out on MOSI pin under the control of the serial clock, SCK. Simultaneously, another Byte shifts in from the Slave on the Master's MISO pin. The transmission ends when the Serial Peripheral transfer data flag, SPIF, in SPSTA becomes set. At the same time that SPIF becomes set, the received Byte from the Slave is transferred to the receive data register in SPDAT. Software clears SPIF by reading the Serial Peripheral Status register (SPSTA) with the SPIF bit set, and then reading the SPDAT.

#### 16.3.1.2 Slave Mode

The SPI operates in Slave mode when the Master bit, MSTR  $^{(2)}$ , in the SPCON register is cleared. Before a data transmission occurs, the Slave Select pin,  $\overline{SS}$ , of the Slave device must be set to '0'.  $\overline{SS}$  must remain low until the transmission is complete.

In a Slave SPI Module, data enters the shift register under the control of the SCK from the Master SPI Module. After a Byte enters the shift register, it is immediately transferred to the receive data register in SPDAT, and the SPIF bit is set. To prevent an overflow condition, Slave software must then read the SPDAT before another Byte enters the shift register <sup>(3)</sup>. A Slave SPI must complete the write to the SPDAT (shift register) at least one bus cycle before the Master SPI starts a transmission. If the write to the data register is late, the SPI transmits the data already in the shift register from the previous transmission. The maximum SCK frequency allowed in slave mode is F<sub>CLK PERIPH</sub>/4.

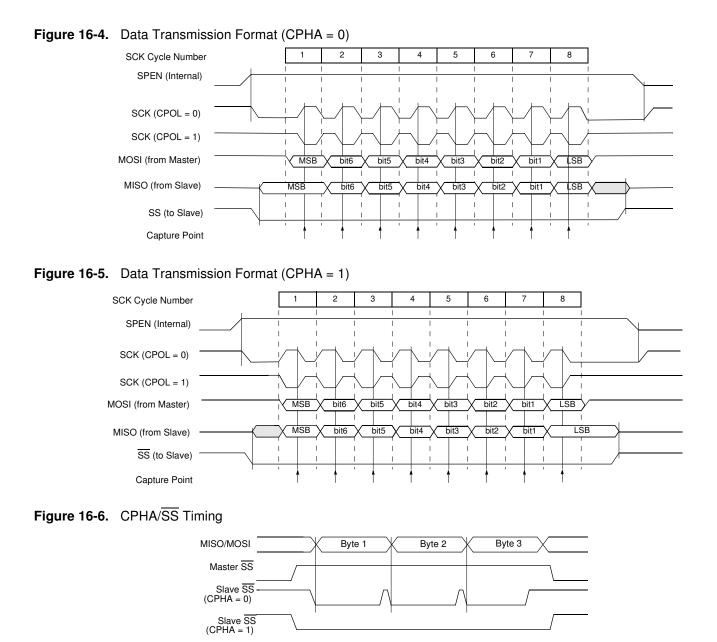

#### 16.3.2 Transmission Formats

Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPCON: the Clock Polarity (CPOL <sup>(4)</sup>) and the Clock Phase (CPHA<sup>4</sup>). CPOL defines the default SCK line level in idle state. It has no significant effect on the transmission format. CPHA defines the edges on which the input data are sampled and the edges on which the output data are shifted (Figure 16-4 and Figure 16-5). The clock phase and polarity should be identical for the Master SPI device and the communicating Slave device.

- The SPI Module should be configured as a Master before it is enabled (SPEN set). Also, the Master SPI should be configured before the Slave SPI.

- 2. The SPI Module should be configured as a Slave before it is enabled (SPEN set).

- 3. The maximum frequency of the SCK for an SPI configured as a Slave is the bus clock speed.

- 4. Before writing to the CPOL and CPHA bits, the SPI should be disabled (SPEN = '0').

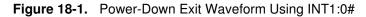

As shown in Figure 16-4, the first SCK edge is the MSB capture strobe. Therefore, the Slave must begin driving its data before the first SCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the transmission. The  $\overline{SS}$  pin must be toggled high and then low between each Byte transmitted (Figure 16-6).

Figure 16-5 shows an SPI transmission in which CPHA is '1'. In this case, the Master begins driving its MOSI pin on the first SCK edge. Therefore, the Slave uses the first SCK edge as a start transmission signal. The SS pin can remain low between transmissions (Figure 16-6). This format may be preferred in systems having only one Master and only one Slave driving the MISO data line.

#### 16.3.3 Error Conditions

The following flags in the SPSTA signal SPI error conditions:

# Table 17-3.IENO RegisterIEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5                                                | 4                                                                                                                                    | 3                 | 2   | 1   | 0   |  |

|---------------|-----------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|--|

| EA            | EC              | ET2                                              | ES                                                                                                                                   | ET1               | EX1 | ET0 | EX0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                      |                                                                                                                                      |                   |     |     |     |  |

| 7             | EA              | Enable All in<br>Cleared to dis<br>Set to enable | able all interru                                                                                                                     | pts.              |     |     |     |  |

| 6             | EC              | PCA interrup<br>Cleared to dis<br>Set to enable. | able.                                                                                                                                |                   |     |     |     |  |

| 5             | ET2             | Cleared to dis                                   | Timer 2 overflow interrupt Enable bit<br>Cleared to disable timer 2 overflow interrupt.<br>Set to enable timer 2 overflow interrupt. |                   |     |     |     |  |

| 4             | ES              |                                                  | <b>nable bit</b><br>able serial por<br>serial port inte                                                                              |                   |     |     |     |  |

| 3             | ET1             | Cleared to dis                                   | flow interrupt<br>able timer 1 ov<br>timer 1 overflo                                                                                 | verflow interrupt |     |     |     |  |

| 2             | EX1             | Cleared to dis                                   | External interrupt 1 Enable bit<br>Cleared to disable external interrupt 1.<br>Set to enable external interrupt 1.                   |                   |     |     |     |  |

| 1             | ET0             | Cleared to dis                                   | Timer 0 overflow interrupt Enable bit<br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                   |     |     |     |  |

| 0             | EX0             | Cleared to dis                                   | rrupt 0 Enable<br>able external in<br>external interru                                                                               | nterrupt 0.       |     |     |     |  |

Reset Value = 0000 0000b Bit addressable

### Table 17-5.IPH0 Register

IPH0 - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                                                                                 | 4                                        | 3                | 2                 | 1      | 0    |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-------------------|--------|------|

| -             | PPCH            | PT2H                                                                                                                              | PSH                                      | PT1H             | PX1H              | РТОН   | PX0H |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       |                                          |                  |                   |        |      |

| 7             | -               | <b>Reserved</b><br>The value rea                                                                                                  | d from this bit                          | is indeterminate | e. Do not set thi | s bit. |      |

| 6             | РРСН            | PCA interrup<br><u>PPCHPPCLP</u><br>0 0Lowest<br>0 1<br>1 0<br>1 1Highest                                                         | nt Priority high<br>riority <u>Level</u> | ı bit.           |                   |        |      |

| 5             | PT2H            | Timer 2 over           PT2HPT2L           0         0Lov           0         1           1         0           1         1Hig     | Priority Level<br>vest                   | Priority High t  | pit               |        |      |

| 4             | PSH             | Serial port Pr<br><u>PSH</u> <u>PSLPric</u><br>0 0Lov<br>0 1<br>1 0<br>1 1Hig                                                     | vest                                     | t                |                   |        |      |

| 3             | PT1H            | Timer 1 over           PT1HPT1L Pi           0         0 Lov           0         1           1         0           1         1Hig | riority Level<br>west                    | Priority High t  | pit               |        |      |

| 2             | PX1H            | External inte<br>PX1HPX1LPr<br>0 0Lov<br>0 1<br>1 0<br>1 1Hig                                                                     | vest                                     | y High bit       |                   |        |      |

| 1             | РТОН            | Timer 0 over           PT0HPT0LPri           0         0Lov           0         1           1         0           1         1Hig  | iorit <u>y Level</u><br>vest             | Priority High t  | bit               |        |      |

| 0             | РХОН            | External inte           PX0H PX0LP           0         0Lov           0         1           1         0           1         1 Hig | vest                                     | y High bit       |                   |        |      |

Reset Value = X000 0000b Not bit addressable

#### 18.3 Power-Down Mode

The Power-Down mode places the AT89C51RD2/ED2 in a very low power state. Power-Down mode stops the oscillator, freezes all clock at known states. The CPU status prior to entering Power-Down mode is preserved, i.e., the program counter, program status word register retain their data for the duration of Power-Down mode. In addition, the SFR and RAM contents are preserved. The status of the Port pins during Power-Down mode is detailed in Table 18-1.

Note: VCC may be reduced to as low as V<sub>RET</sub> during Power-Down mode to further reduce power dissipation. Take care, however, that VDD is not reduced until Power-Down mode is invoked.

#### 18.3.1 Entering Power-Down Mode

To enter Power-Down mode, set PD bit in PCON register. The AT89C51RD2/ED2 enters the Power-Down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.

#### 18.3.2 Exiting Power-Down Mode

Note: If VCC was reduced during the Power-Down mode, do not exit Power-Down mode until VCC is restored to the normal operating level.

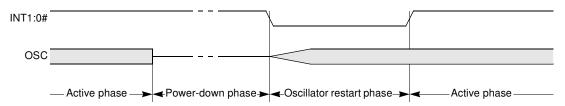

There are three ways to exit the Power-Down mode:

- 1. Generate an enabled external interrupt.

- The AT89C51RD2/ED2 provides capability to exit from Power-Down using INT0#, INT1#.

Hardware clears PD bit in PCON register which starts the oscillator and restores the clocks to the CPU and peripherals. Using INTx# input, execution resumes when the input is released (see Figure 18-1). Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Power-Down mode.

- Note: The external interrupt used to exit Power-Down mode must be configured as level sensitive (INT0# and INT1#) and must be assigned the highest priority. In addition, the duration of the interrupt must be long enough to allow the oscillator to stabilize. The execution will only resume when the interrupt is deasserted.

- Note: Exit from power-down by external interrupt does not affect the SFRs nor the internal RAM content.

- 2. Generate a reset.

- A logic high on the RST pin clears PD bit in PCON register directly and asynchronously. This starts the oscillator and restores the clock to the CPU and peripherals. Program execution momentarily resumes with the instruction immediately following the instruction that activated Power-Down mode and may

#### Table 19-2.WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7             | 6               | 5                                                     | 4                                                                                                                                                                                                    | 3                                                                                                                                   | 2                                                                                                                                                                                              | 1                             | 0  |

|---------------|-----------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----|

| -             | -               | -                                                     | -                                                                                                                                                                                                    | -                                                                                                                                   | S2                                                                                                                                                                                             | S1                            | S0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                           |                                                                                                                                                                                                      |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

| 7             | -               |                                                       |                                                                                                                                                                                                      |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

| 6             | -               |                                                       |                                                                                                                                                                                                      |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

| 5             | -               | Reserved<br>The value read                            | from this bit is                                                                                                                                                                                     | undetermined                                                                                                                        | . Do not try to se                                                                                                                                                                             | et this bit.                  |    |

| 4             | -               |                                                       |                                                                                                                                                                                                      |                                                                                                                                     | <b>,</b>                                                                                                                                                                                       |                               |    |

| 3             | -               |                                                       |                                                                                                                                                                                                      |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

| 2             | S2              | WDT Time-ou                                           | t select bit 2                                                                                                                                                                                       |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

| 1             | S1              | WDT Time-ou                                           | t select bit 1                                                                                                                                                                                       |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

| 0             | S0              | WDT Time-ou                                           | t select bit 0                                                                                                                                                                                       |                                                                                                                                     |                                                                                                                                                                                                |                               |    |

|               |                 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | <ul> <li><sup>15</sup> - 1) machine</li> <li>machine cyc</li> <li><sup>17</sup> - 1) machine</li> <li><sup>18</sup> - 1) machine</li> <li>machine cyc</li> <li><sup>20</sup> - 1) machine</li> </ul> | e cycles, 16. 3 r<br>e cycles, 32.7 m<br>les, 65. 5 ms @<br>e cycles, 131 m<br>e cycles, 262 m<br>les, 542 ms @<br>e cycles, 1.05 m | ns @ $F_{OSCA} = 12$<br>is @ $F_{OSCA} = 12$<br>P $F_{OSCA} = 12$ MH<br>s @ $F_{OSCA} = 12$ I<br>s @ $F_{OSCA} = 12$ I<br>F $_{OSCA} = 12$ MHz<br>is @ $F_{OSCA} = 12$<br>is @ $F_{OSCA} = 12$ | MHz<br>z<br>MHz<br>MHz<br>MHz |    |

Reset Value = XXXX X000

#### 19.2 WDT during Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Powerdown mode the user does not need to service the WDT. There are 2 methods of exiting Powerdown mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the AT89C51RD2/ED2 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is better to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the AT89C51RD2/ED2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

### 21. Power-off Flag

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (Table 21-1). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

Table 21-1.PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                                 | 4                                                                                                                   | 3                                     | 2                             | 1              | 0        |  |

|---------------|-----------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|----------------|----------|--|

| SMOD1         | SMOD0           | -                                                 | POF                                                                                                                 | GF1                                   | GF0                           | PD             | IDL      |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                       |                                                                                                                     |                                       |                               |                |          |  |

| 7             | SMOD1           | Serial port M<br>Set to select o                  |                                                                                                                     | e in mode 1, 2                        | or 3.                         |                |          |  |

| 6             | SMOD0           |                                                   | o <b>de bit 0</b><br>ect SM0 bit in S<br>E bit in SCON                                                              | •                                     |                               |                |          |  |

| 5             | -               | Reserved<br>The value rea                         | d from this bit is                                                                                                  | s indeterminate                       | . Do not set this             | bit.           |          |  |

| 4             | POF             |                                                   | ftware to recog                                                                                                     | nize the next re<br>ses from 0 to its | set type.<br>s nominal voltag | e. Can also be | e set by |  |

| 3             | GF1             |                                                   | <b>ose Flag</b><br>er for general-p<br>r general-purpo                                                              |                                       |                               |                |          |  |

| 2             | GF0             | Cleared by us                                     | <b>General-purpose Flag</b><br>Cleared by user for general-purpose usage.<br>Set by user for general-purpose usage. |                                       |                               |                |          |  |

| 1             | PD              | Cleared by ha                                     | Power-down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                      |                                       |                               |                |          |  |

| 0             | IDL             | Idle mode bit<br>Cleared by ha<br>Set to enter id | rdware when ir                                                                                                      | iterrupt or reset                     | occurs.                       |                |          |  |

Reset Value = 00X1 0000b Not bit addressable

| Program Lock Bits |     |     |     |                                                                                                                                                                                                                                                                                         |

|-------------------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security<br>Level | LB0 | LB1 | LB2 | Protection Description                                                                                                                                                                                                                                                                  |

| 1                 | U   | U   | U   | No program lock features enabled.                                                                                                                                                                                                                                                       |