Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ed2-slsum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3. SFR Mapping

The Special Function Registers (SFRs) of the AT89C51RD2/ED2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3, PI2

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

- SPI registers: SPCON, SPSTR, SPDAT

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Clock Prescaler register: CKRL

- Others: AUXR, AUXR1, CKCON0, CKCON1

|  | Table 3-1. | C51 Core SFRs |

|--|------------|---------------|

|--|------------|---------------|

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

#### Table 3-2.System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF  | GF1  | GF0  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | M0     | XRS2 | XRS1 | XRS0 | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -    | GF3  | 0    | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | -     | -     | -      | -    | -    | -    | -      | -     |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2 | T2X2 | T1X2 | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -    | -    | -    | -      | SPIX2 |

# 5. Port Types

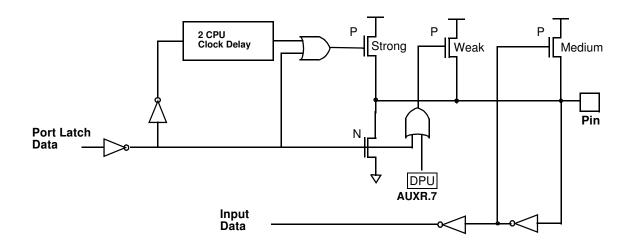

AT89C51RD2/ED2 I/O ports (P1, P2, P3, P4, P5) implement the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-tohigh transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 5-1.

Figure 5-1. Quasi-Bidirectional Output

| Bit<br>Number    | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                             |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                | TF2             | <b>Timer 2 overflow Flag</b><br>Must be cleared by software.<br>Set by hardware on Timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                          |

| 6                | EXF2            | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2<br>= 1.<br>When set, causes the CPU to vector to Timer 2 interrupt routine when Timer 2 interrupt<br>is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode<br>(DCEN = 1). |

| 5                | RCLK            | <b>Receive Clock bit</b><br>Cleared to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                            |

| 4                | TCLK            | <b>Transmit Clock bit</b><br>Cleared to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                                         |

| 3                | EXEN2           | <b>Timer 2 External Enable bit</b><br>Cleared to ignore events on T2EX pin for Timer 2 operation.<br>Set to cause a capture or reload when a negative transition on T2EX pin is detected, if<br>Timer 2 is not used to clock the serial port.                                                                                           |

| 2                | TR2             | Timer 2 Run control bit<br>Cleared to turn off Timer 2.<br>Set to turn on Timer 2.                                                                                                                                                                                                                                                      |

| 1                | C/T2#           | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for<br>clock out mode.                                                                                           |

| 0<br>Beset Value | CP/RL2#         | <b>Timer 2 Capture/Reload bit</b><br>If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to auto-reload on Timer<br>2 overflow.<br>Cleared to auto-reload on Timer 2 overflows or negative transitions on T2EX pin if<br>EXEN2=1.<br>Set to capture on negative transitions on T2EX pin if EXEN2 = 1.                       |

Reset Value = 0000 0000b Bit addressable

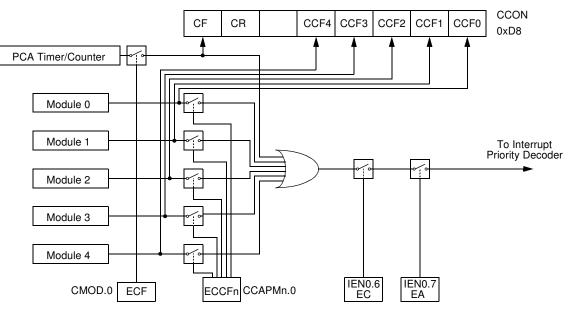

### Figure 13-2. PCA Interrupt System

**PCA Modules:** each one of the five compare/capture modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered

- 16-bit Capture, negative-edge triggered

- · 16-bit Capture, both positive and negative-edge triggered

- 16-bit Software Timer

- 16-bit High Speed Output

- · 8-bit Pulse Width Modulator

In addition, Module 4 can be used as a Watchdog Timer.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for Module 0, CCAPM1 for Module 1, etc. (See Table 13-3). The registers contain the bits that control the mode that each module will operate in.

- The ECCF bit (CCAPMn.0 where n = 0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module.

- PWM (CCAPMn.1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the modules capture/compare register.

- The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the modules capture/compare register.

- The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

Table 13-3 shows the CCAPMn settings for the various PCA functions.

### **Table 13-3.** CCAPMn Registers (n = 0-4)

CCAPM0 - PCA Module 0 Compare/Capture Control Register (0DAh)

CCAPM1 - PCA Module 1 Compare/Capture Control Register (0DBh)

CCAPM2 - PCA Module 2 Compare/Capture Control Register (0DCh)

CCAPM3 - PCA Module 3 Compare/Capture Control Register (0DDh)

CCAPM4 - PCA Module 4 Compare/Capture Control Register (0DEh)

| 7             | 6               | 5                          | 4                                                                                                          | 3                                               | 2                | 1              | 0        |  |  |

|---------------|-----------------|----------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|----------------|----------|--|--|

| -             | ECOMn           | CAPPn                      | CAPNn                                                                                                      | MATn                                            | TOGn             | PWMn           | ECCFn    |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                | Description                                                                                                |                                                 |                  |                |          |  |  |

| 7             | -               | Reserved<br>The value read | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                            |                                                 |                  |                |          |  |  |

| 6             | ECOMn           | Cleared to dis             | Enable Comparator<br>Cleared to disable the comparator function.<br>Set to enable the comparator function. |                                                 |                  |                |          |  |  |

| 5             | CAPPn           | Cleared to dis             | Capture Positive<br>Cleared to disable positive edge capture.<br>Set to enable positive edge capture.      |                                                 |                  |                |          |  |  |

| 4             | CAPNn           | Cleared to dis             | Capture Negative<br>Cleared to disable negative edge capture.<br>Set to enable negative edge capture.      |                                                 |                  |                |          |  |  |

| 3             | MATn            |                            |                                                                                                            | the PCA counter<br>in CCON to be                |                  |                | capture  |  |  |

| 2             | TOGn            |                            | = 1, a match of<br>s the CEXn pir                                                                          | the PCA countent to toggle.                     | er with this moc | lule's compare | /capture |  |  |

| 1             | PWMn            | Cleared to dis             |                                                                                                            | o <b>de</b><br>pin to be used<br>o be used as a | •                |                |          |  |  |

| 0             | CCF0            | interrupt.                 | able compare/d                                                                                             | capture flag CC<br>ire flag CCFn in             |                  | 0 0            |          |  |  |

Reset Value = X000 0000b Not bit addressable

### Table 14-9. SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

#### Table 14-10. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## 15.1 Registers

### Table 15-1. KBF Register

KBF-Keyboard Flag Register (9Eh)

| 7          | 6               | 5                              | 4                                                                                                                                                                                                                         | 3              | 2                                | 1    | 0       |  |  |

|------------|-----------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|------|---------|--|--|

| KBF7       | KBF6            | KBF5                           | KBF4                                                                                                                                                                                                                      | KBF3           | KBF2                             | KBF1 | KBF0    |  |  |

| Bit Number | Bit<br>Mnemonic | Description                    | Description                                                                                                                                                                                                               |                |                                  |      |         |  |  |

| 7          | KBF7            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 7 flag</b><br>Set by hardware when the Port line 7 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBKBIE.7 bit in KBIE register is set.<br>Must be cleared by software. |                |                                  |      |         |  |  |

| 6          | KBF6            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 6 flag</b><br>Set by hardware when the Port line 6 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.6 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |

| 5          | KBF5            | Set by hardwa<br>Keyboard inte | Keyboard line 5 flag<br>Set by hardware when the Port line 5 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.5 bit in KBIE register is set.<br>Must be cleared by software.          |                |                                  |      |         |  |  |

| 4          | KBF4            | Set by hardwa<br>Keyboard inte | Keyboard line 4 flag<br>Set by hardware when the Port line 4 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.4 bit in KBIE register is set.<br>Must be cleared by software.          |                |                                  |      |         |  |  |

| 3          | KBF3            | Keyboard inte                  | ire when the Po                                                                                                                                                                                                           | the KBIE.3 bit | s a programme<br>in KBIE registe |      | rates a |  |  |

| 2          | KBF2            | Set by hardwa<br>Keyboard inte | Keyboard line 2 flag<br>Set by hardware when the Port line 2 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.2 bit in KBIE register is set.<br>Must be cleared by software.          |                |                                  |      |         |  |  |

| 1          | KBF1            | Set by hardwa<br>Keyboard inte | <b>Keyboard line 1 flag</b><br>Set by hardware when the Port line 1 detects a programmed level. It generates a<br>Keyboard interrupt request if the KBIE.1 bit in KBIE register is set.<br>Must be cleared by software.   |                |                                  |      |         |  |  |

| 0          | KBF0            | Keyboard inte                  | ire when the Po                                                                                                                                                                                                           | the KBIE.0 bit | s a programme<br>in KBIE registe |      | rates a |  |  |

### **Reset Value = 0000 0000b**

This register is read only access, all flags are automatically cleared by reading the register.

## 16. Serial Port Interface (SPI)

The Serial Peripheral Interface Module (SPI) allows full-duplex, synchronous, serial communication between the MCU and peripheral devices, including other MCUs.

### 16.1 Features

Features of the SPI Module include the following:

- Full-duplex, three-wire synchronous transfers

- Master or Slave operation

- · Eight programmable Master clock rates

- · Serial clock with programmable polarity and phase

- · Master Mode fault error flag with MCU interrupt capability

- Write collision flag protection

### 16.2 Signal Description

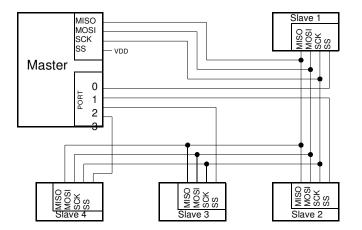

Figure 16-1 shows a typical SPI bus configuration using one Master controller and many Slave peripherals. The bus is made of three wires connecting all the devices.

Figure 16-1. SPI Master/Slaves Interconnection

The Master device selects the individual Slave devices by using four pins of a parallel port to control the four  $\overline{SS}$  pins of the Slave devices.

### 16.2.1 Master Output Slave Input (MOSI)

This 1-bit signal is directly connected between the Master Device and a Slave Device. The MOSI line is used to transfer data in series from the Master to the Slave. Therefore, it is an output signal from the Master, and an input signal to a Slave. A Byte (8-bit word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

### 16.2.2 Master Input Slave Output (MISO)

This 1-bit signal is directly connected between the Slave Device and a Master Device. The MISO line is used to transfer data in series from the Slave to the Master. Therefore, it is an output signal from the Slave, and an input signal to the Master. A Byte (8-bit word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                         |  |  |  |  |  |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4          | MSTR         | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                       |  |  |  |  |  |

| 3          | CPOL         | <b>Clock Polarity</b><br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                           |  |  |  |  |  |

| 2          | СРНА         | Clock Phase<br>Cleared to have the data sampled when the SCK leaves the idle state (see<br>CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see<br>CPOL).                                                 |  |  |  |  |  |

| 1          | SPR1         | SPR2         SPR1         SPR0 Serial Peripheral Rate           0         0         1F <sub>CLK PERIPH</sub> /2           0         0         1F <sub>CLK PERIPH</sub> /4           0         1         0F <sub>CLK PERIPH</sub> /8 |  |  |  |  |  |

|            | SPR0         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                               |  |  |  |  |  |

Reset Value = 0001 0100b

Not bit addressable

### 16.3.5.2 Serial Peripheral Status Register (SPSTA)

The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 16-4 describes the SPSTA register and explains the use of every bit in the register.

### Table 16-4. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7          | 6               | 5                                                                                                                                                                                                         | 4                                                                                                                                                                                                                              | 3 | 2 | 1 | 0 |  |  |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--|--|

| SPIF       | WCOL            | SSERR MODF                                                                                                                                                                                                |                                                                                                                                                                                                                                |   |   |   |   |  |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                               | Description                                                                                                                                                                                                                    |   |   |   |   |  |  |

| 7          | SPIF            | Cleared by har<br>clearing seque                                                                                                                                                                          | Serial Peripheral Data Transfer Flag<br>Cleared by hardware to indicate data transfer is in progress or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed. |   |   |   |   |  |  |

| 6          | WCOL            | Write Collision Flag<br>Cleared by hardware to indicate that no collision has occurred or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that a collision has been detected. |                                                                                                                                                                                                                                |   |   |   |   |  |  |

# Table 17-7. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                                | 4                                                                               | 3                | 2                 | 1      | 0    |  |  |

|---------------|-----------------|----------------------------------|---------------------------------------------------------------------------------|------------------|-------------------|--------|------|--|--|

| -             | -               | -                                | -                                                                               | -                | SPIL              | TWIL   | KBDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                      | Description                                                                     |                  |                   |        |      |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                   |        |      |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                   |        |      |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                   |        |      |  |  |

| 4             | -               | <b>Reserved</b><br>The value rea | d from this bit i                                                               | is indeterminate | e. Do not set thi | s bit. |      |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea | d from this bit i                                                               | is indeterminate | e. Do not set thi | s bit. |      |  |  |

| 2             | SPIL            |                                  | SPI interrupt Priority bit<br>Refer to SPIH for priority level.                 |                  |                   |        |      |  |  |

| 1             | -               | <b>Reserved</b><br>The value rea | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                  |                   |        |      |  |  |

| 0             | KBDL            |                                  | errupt Priority<br>I for priority le                                            |                  |                   |        |      |  |  |

Reset Value = XXXX X000b Bit addressable

# Table 17-8. IPH1 Register

IPH1 - Interrupt Priority High Register (B3h)

| 7             | 6               | 5                                                                                | 4                                                                               | 3               | 2                 | 1      | 0    |  |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|-------------------|--------|------|--|--|--|--|

| -             | -               | -                                                                                | -                                                                               | -               | SPIH              | -      | KBDH |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                      | Description                                                                     |                 |                   |        |      |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value rea                                                 | d from this bit i                                                               | s indeterminate | e. Do not set thi | s bit. |      |  |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea                                                 | d from this bit i                                                               | s indeterminate | e. Do not set thi | s bit. |      |  |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value rea                                                 | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |  |

| 4             | -               | Reserved<br>The value rea                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value rea                                                 | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |  |

| 2             | SPIH            | SPIHSPILPric00Low0110                                                            | 0 1<br>1 0                                                                      |                 |                   |        |      |  |  |  |  |

| 1             | -               | Reserved<br>The value rea                                                        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                   |        |      |  |  |  |  |

| 0             | KBDH            | KB DHKBDLF           0         0 Low           0         1           1         0 | 0 1<br>1 0                                                                      |                 |                   |        |      |  |  |  |  |

Reset Value = XXXX X000b Not bit addressable

## **18. Power Management**

### 18.1 Introduction

Two power reduction modes are implemented in the AT89C51RD2/ED2. The Idle mode and the Power-Down mode. These modes are detailed in the following sections. In addition to these power reduction modes, the clocks of the core and peripherals can be dynamically divided by 2 using the X2 mode detailed in Section "Enhanced Features", page 17.

### 18.2 Idle Mode

Idle mode is a power reduction mode that reduces the power consumption. In this mode, program execution halts. Idle mode freezes the clock to the CPU at known states while the peripherals continue to be clocked. The CPU status before entering Idle mode is preserved, i.e., the program counter and program status word register retain their data for the duration of Idle mode. The contents of the SFRs and RAM are also retained. The status of the Port pins during Idle mode is detailed in Table 18-1.

### 18.2.1 Entering Idle Mode

To enter Idle mode, set the IDL bit in PCON register (see Table 18-2). The AT89C51RD2/ED2 enters Idle mode upon execution of the instruction that sets IDL bit. The instruction that sets IDL bit is the last instruction executed.

Note: If IDL bit and PD bit are set simultaneously, the AT89C51RD2/ED2 enters Power-Down mode. Then it does not go in Idle mode when exiting Power-Down mode.

### 18.2.2 Exiting Idle Mode

There are two ways to exit Idle mode:

- 1. Generate an enabled interrupt.

- Hardware clears IDL bit in PCON register which restores the clock to the CPU. Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Idle mode. The general purpose flags (GF1 and GF0 in PCON register) may be used to indicate whether an interrupt occurred during normal operation or during Idle mode. When Idle mode is exited by an interrupt, the interrupt service routine may examine GF1 and GF0.

- 2. Generate a reset.

- A logic high on the RST pin clears IDL bit in PCON register directly and asynchronously. This restores the clock to the CPU. Program execution momentarily resumes with the instruction immediately following the instruction that activated the Idle mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT89C51RD2/ED2 and vectors the CPU to address C:0000h.

- Note: During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated Idle mode should not write to a Port pin or to the external RAM.

continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT89C51RD2/ED2 and vectors the CPU to address 0000h.

- 3. Generate an enabled external Keyboard interrupt (same behavior as external interrupt).

- Note: During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated the Power-Down mode should not write to a Port pin or to the external RAM.

- Note: Exit from power-down by reset redefines all the SFRs, but does not affect the internal RAM content.

| Mode                             | Port 0   | Port 1 | Port 2 | Port 3 | Port 4 | ALE  | PSEN# |

|----------------------------------|----------|--------|--------|--------|--------|------|-------|

| Reset                            | Floating | High   | High   | High   | High   | High | High  |

| ldle (internal code)             | Data     | Data   | Data   | Data   | Data   | High | High  |

| Idle (external code)             | Floating | Data   | Data   | Data   | Data   | High | High  |

| Power-Down<br>(internal<br>code) | Data     | Data   | Data   | Data   | Data   | Low  | Low   |

| Power-Down<br>(external<br>code) | Floating | Data   | Data   | Data   | Data   | Low  | Low   |

Table 18-1. Pin Conditions in Special Operating Modes

## 22. Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

**Table 22-1.**AUXR RegisterAUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                                                                                                                                                                                                                   | 4                                                                                                                                                                      | 3    | 2    | 1      | 0  |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|----|--|--|--|

| DPU           | -               | МО                                                                                                                                                                                                                                  | XRS2                                                                                                                                                                   | XRS1 | XRS0 | EXTRAM | AO |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                         |                                                                                                                                                                        |      |      |        |    |  |  |  |

| 7             | DPU             | Cleared by so                                                                                                                                                                                                                       | Disable Weak Pull-up<br>Cleared by software to activate the permanent weak pull-up (default)<br>Set by software to disable the weak pull-up (reduce power consumption) |      |      |        |    |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value rea                                                                                                                                                                                                    | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                        |      |      |        |    |  |  |  |

| 5             | MO              | (default).                                                                                                                                                                                                                          | Cleared to stretch MOVX control: the $\overline{\text{RD}}$ and the $\overline{\text{WR}}$ pulse length is 6 clock periods                                             |      |      |        |    |  |  |  |

| 4             | XRS2            | XRAM Size                                                                                                                                                                                                                           |                                                                                                                                                                        |      |      |        |    |  |  |  |

| 3             | XRS1            |                                                                                                                                                                                                                                     | <u>RS0XRAM size</u><br>0256 bytes                                                                                                                                      | 2    |      |        |    |  |  |  |

| 2             | XRS0            | 0 1<br>0 1                                                                                                                                                                                                                          | 0         0         1512 bytes           0         1         0768 bytes(default)           0         1         11024 bytes                                             |      |      |        |    |  |  |  |

| 1             | EXTRAM          | <b>EXTRAM bit</b><br>Cleared to access internal XRAM using MOVX @ Ri/ @ DPTR.<br>Set to access external memory.<br>Programmed by hardware after Power-up regarding Hardware Security Byte (HSB),<br>default setting, XRAM selected. |                                                                                                                                                                        |      |      |        |    |  |  |  |

| 0             | AO              | ALE Output bit<br>Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if X2<br>mode is used) (default). Set, ALE is active only during a MOVX or MOVC instruction is<br>used.                        |                                                                                                                                                                        |      |      |        |    |  |  |  |

Reset Value = XX00 10'HSB. XRAM'0b Not bit addressable

## 23. EEPROM Data Memory

This feature is available only for the AT89C51ED2 device.

The 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh of the XRAM/ERAM memory space and is selected by setting control bits in the EECON register.

A read or write access to the EEPROM memory is done with a MOVX instruction.

### 23.1 Write Data

Data is written by byte to the EEPROM memory block as for an external RAM memory.

The following procedure is used to write to the EEPROM memory:

- Check EEBUSY flag

- If the user application interrupts routines use XRAM memory space: Save and disable interrupts.

- · Load DPTR with the address to write

- Store A register with the data to be written

- Set bit EEE of EECON register

- Execute a MOVX @DPTR, A

- Clear bit EEE of EECON register

- Restore interrupts.

- EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading or writing.

- The end of programming is indicated by a hardware clear of the EEBUSY flag.

Figure 23-1 represents the optimal write sequence to the on-chip EEPROM data memory.

| Mnemonic | Definition                                       | Default value | Description                        |

|----------|--------------------------------------------------|---------------|------------------------------------|

| BSB      | Boot Status Byte                                 | 0FFh          |                                    |

| SSB      | Software Security Byte                           | FFh           |                                    |

|          | Copy of the Manufacturer Code                    | 58h           | Atmel                              |

|          | Copy of the Device ID #1: Family Code            | D7h           | C51 X2, Electrically Erasable      |

|          | Copy of the Device ID #2: Memories Size and Type | ECh           | AT89C51RD2/ED2 64KB                |

|          | Copy of the Device ID #3: Name and Revision      | EFh           | AT89C51RD2/ED2 64KB,<br>Revision 0 |

After programming the part by ISP, the BSB must be cleared (00h) in order to allow the application to boot at 0000h.

The content of the Software Security Byte (SSB) is described in Table 24-4 and Table 24-5.

To assure code protection from a parallel access, the HSB must also be at the required level.

| 7             | 6               | 5                            | 4                                  | 3 | 2 | 1   | 0   |  |  |

|---------------|-----------------|------------------------------|------------------------------------|---|---|-----|-----|--|--|

| -             | -               | -                            | -                                  | - | - | LB1 | LB0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                  |                                    |   |   |     |     |  |  |

| 7             | -               | Reserved<br>Do not clear th  | is bit.                            |   |   |     |     |  |  |

| 6             | -               | Reserved<br>Do not clear th  | Reserved<br>Do not clear this bit. |   |   |     |     |  |  |

| 5             | -               | Reserved<br>Do not clear th  | Reserved<br>Do not clear this bit. |   |   |     |     |  |  |

| 4             | -               | Reserved<br>Do not clear th  | is bit.                            |   |   |     |     |  |  |

| 3             | -               | Reserved<br>Do not clear th  | is bit.                            |   |   |     |     |  |  |

| 2             | -               | Reserved<br>Do not clear th  | is bit.                            |   |   |     |     |  |  |

| 1-0           | LB1-0           | User Memory<br>See Table 24- |                                    |   |   |     |     |  |  |

Table 24-4. Software Security Byte

The two lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 24-5.

### 24.7 ISP Protocol Description

### 24.7.1 Physical Layer

The UART used to transmit information has the following configuration:

- Character: 8-bit data

- Parity: none

- Stop: 2 bits

- · Flow control: none

- Baudrate: autobaud is performed by the bootloader to compute the baudrate chosen by the host.

#### 24.7.2 Frame Description

The Serial Protocol is based on the Intel Hex-type records.

Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below.

| Figure 24-6. | Intel Hex | Type Frame |

|--------------|-----------|------------|

|--------------|-----------|------------|

| Record<br>Mark<br>':' | Reclen | Load<br>Offset | Record<br>Type | Data<br>or<br>Info | Checksum |

|-----------------------|--------|----------------|----------------|--------------------|----------|

| 1-byte                | 1-byte | 2-bytes        | 1-byte         | n-bytes            | 1-byte   |

#### • Record Mark:

Record Mark is the start of frame. This field must contain ':'.

Reclen:

Reclen specifies the number of bytes of information or data which follows the Record Type field of the record.

Load Offset:

Load Offset specifies the 16-bit starting load offset of the data bytes, therefore this field is used only for Data Program Record (see Section "ISP Commands Summary").

• Record Type:

Record Type specifies the command type. This field is used to interpret the remaining information within the frame. The encoding for all the current record types is described in Section "ISP Commands Summary".

• Data/Info:

Data/Info is a variable length field. It consists of zero or more bytes encoded as pairs of hexadecimal digits. The meaning of data depends on the **Record Type**.

· Checksum:

The two's complement of the 8-bit bytes that result from converting each pair of ASCII hexadecimal digits to one byte of binary, and including the **Reclen** field to and including the last byte of the **Data/Info** field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the **Reclen** field to and including the **Checksum** field, is zero.

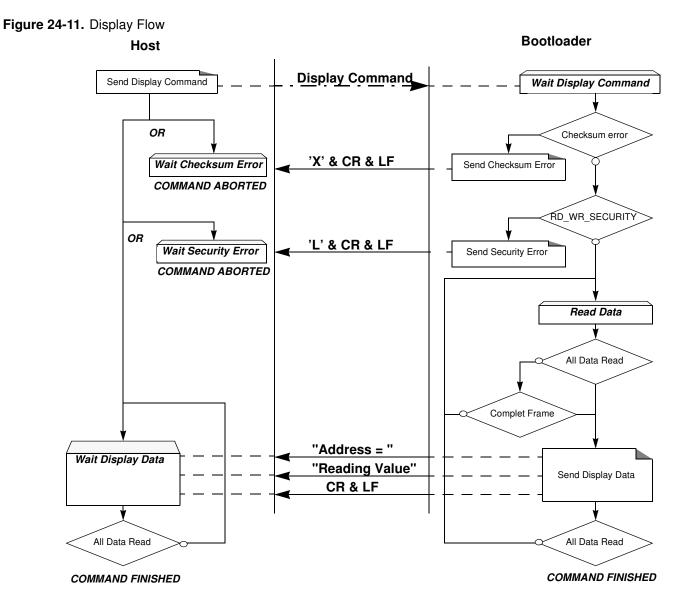

### 24.9.7 Display Data Description

### 24.9.7.1 Example

#### Display data from address 0000h to 0020h

| HOST       | : 05 0000 04 0000 0020 00 D7 |

|------------|------------------------------|

| BOOTLOADER | : 05 0000 04 0000 0020 00 D7 |

| BOOTLOADER | 0000=data CR LF (16 data)    |

| BOOTLOADER | 0010=data CR LF (16 data)    |

| BOOTLOADER | 0020=data CR LF (1 data)     |

### 24.9.8 Read Function Description

This flow is similar for the following frames:

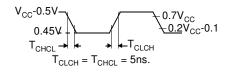

Figure 25-4. Clock Signal Waveform for I<sub>CC</sub> Tests in Active and Idle Modes

### 25.3 AC Parameters

#### 25.3.1 Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Address Valid to ALE Low.  $T_{LLPL}$  = Time for ALE Low to PSEN Low.

(Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF.)

Table 25-1 Table 25-4, and Table 25-7 give the description of each AC symbols.

Table 25-2, Table 25-3, Table 25-5 and Table 25-8 gives the range for each AC parameter.

Table 25-2, Table 25-3 and Table 25-9 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols. take the x value in the correponding column (-M) and use this value in the formula.

Example:  $T_{LLIU}$  for -M and 20 MHz, Standard clock. x = 35 ns T 50 ns  $T_{CCIV}$  = 4T - x = 165 ns

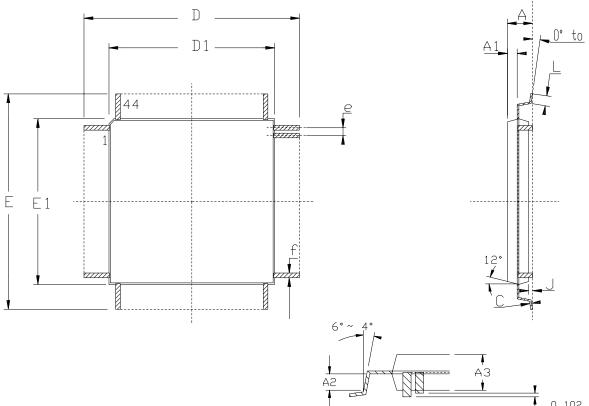

## 27.2 VQFP44

0. 102 LEAD COPLAN#

|     | М     | М       | INCH<br>Min Max |        |  |

|-----|-------|---------|-----------------|--------|--|

|     | Min   | Min Max |                 | Max    |  |

| А   | _     | 1, 60   | _               | , 063  |  |

| A 1 | Ο,    | 64 REF  | , 0             | 25 REF |  |

| A2  | Ο,    | 64 REF  | , 025 REF       |        |  |

| A3  | 1, 35 | 1, 45   | , 053           | , 057  |  |

| D   | 11,90 | 12.10   | , 468           | , 476  |  |

| D 1 | 9, 90 | 10, 10  | , 390           | , 398  |  |

| E   | 11,90 | 12.10   | , 468           | , 476  |  |

| E 1 | 9, 90 | 10, 10  | , 390           | , 398  |  |

| J   | 0, 05 | _       | , 002           | _      |  |

| L   | 0, 45 | 0, 75   | , 018           | , 030  |  |

| e   | 0, 8  | O BSC   | , 03            | 15 BSC |  |

| f   | 0, 3  | 5 BSC   | . 014 BSC       |        |  |