#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51rd2-rlrum |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 3-3.Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0  | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI |      | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PT0L | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH |      | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL |      | KBDL |

#### Table 3-4.Port SFRs

| Mnemonic | Add | Name                            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|---------------------------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0                    |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1                    |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2                    |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3                    |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4                    |   |   |   |   |   |   |   |   |

| P5       | E8h | 8-bit Port 5                    |   |   |   |   |   |   |   |   |

| P5       | C7h | 8-bit Port 5 (byte addressable) |   |   |   |   |   |   |   |   |

### Table 3-5.Timer SFRs

| Mnemonic | Add | Name                                        | 7     | 6     | 5    | 4    | 3     | 2     | 1     | 0       |

|----------|-----|---------------------------------------------|-------|-------|------|------|-------|-------|-------|---------|

| TCON     | 88h | Timer/Counter 0 and 1 Control               | TF1   | TR1   | TF0  | TR0  | IE1   | IT1   | IE0   | IT0     |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes                 | GATE1 | C/T1# | M11  | M01  | GATE0 | C/T0# | M10   | M00     |

| TL0      | 8Ah | Timer/Counter 0 Low Byte                    |       |       |      |      |       |       |       |         |

| TH0      | 8Ch | Timer/Counter 0 High Byte                   |       |       |      |      |       |       |       |         |

| TL1      | 8Bh | Timer/Counter 1 Low Byte                    |       |       |      |      |       |       |       |         |

| TH1      | 8Dh | Timer/Counter 1 High Byte                   |       |       |      |      |       |       |       |         |

| WDTRST   | A6h | WatchDog Timer Reset                        |       |       |      |      |       |       |       |         |

| WDTPRG   | A7h | WatchDog Timer Program                      | -     | -     | -    | -    | -     | WTO2  | WTO1  | WTO0    |

| T2CON    | C8h | Timer/Counter 2 control                     | TF2   | EXF2  | RCLK | TCLK | EXEN2 | TR2   | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2 Mode                        | -     | -     | -    | -    | -     | -     | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2 Reload/Capture<br>High Byte |       |       |      |      |       |       |       |         |

| RCAP2L   | CAh | Timer/Counter 2 Reload/Capture<br>Low Byte  |       |       |      |      |       |       |       |         |

| TH2      | CDh | Timer/Counter 2 High Byte                   |       |       |      |      |       |       |       |         |

#### Table 3-9.Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

#### Table 3-10. EEPROM data Memory SFR (AT89C51ED2 only)

| Mnemonic | Add | Name                | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0      |

|----------|-----|---------------------|---|---|---|---|---|---|-----|--------|

| EECON    | D2h | EEPROM Data Control |   |   |   |   |   |   | EEE | EEBUSY |

#### shows all SFRs with their address and their reset value.

#### Table 3-11.SFR Mapping

|     | Bit<br>Addressable                 |                    |                     | No                  | on Bit Addressal    | ble                 |                     |                                     |     |

|-----|------------------------------------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------------------------|-----|

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                                 |     |

| F8h |                                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAP2H<br>XXXX XXXX | CCAP3H<br>XXXX XXXX | CCAP4H<br>XXXX XXXX |                                     | FFh |

| F0h | B<br>0000 0000                     |                    |                     |                     |                     |                     |                     |                                     | F7h |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAP2L<br>XXXX XXXX | CCAP3L<br>XXXX XXXX | CCAP4L<br>XXXX XXXX |                                     | EFh |

| E0h | ACC<br>0000 0000                   |                    |                     |                     |                     |                     |                     |                                     | E7h |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000 | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000 |                                     | DFh |

| D0h | PSW<br>0000 0000                   | FCON<br>XXXX 0000  | EECON<br>xxxx xx00  |                     |                     |                     |                     |                                     | D7h |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                                     | CFh |

| C0h | P4<br>1111 1111                    |                    |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000  | SPDAT<br>XXXX XXXX  |                     | P5 byte<br>Addressable<br>1111 1111 | C7h |

| B8h | IPL0<br>X000 000                   | SADEN<br>0000 0000 |                     |                     |                     |                     |                     |                                     | BFh |

| B0h | P3<br>1111 1111                    | IEN1<br>XXXX X000  | IPL1<br>XXXX X000   | IPH1<br>XXXX X000   |                     |                     |                     | IPH0<br>X000 0000                   | B7h |

| A8h | IEN0<br>0000 0000                  | SADDR<br>0000 0000 |                     |                     |                     |                     |                     | CKCON1<br>XXXX XXX0                 | AFh |

Table 4-1.

Pin Description (Continued)

|              |        | Pin N  | lumber |        | Turne |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|--------|--------|--------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic     | PLCC44 | VQFP44 | PLCC68 | VQFP64 | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/PRO<br>G | 33     | 27     | 68     | 56     | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the<br>low byte of the address during an access to external memory. In normal<br>operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the<br>oscillator frequency, and can be used for external timing or clocking. Note<br>that one ALE pulse is skipped during each access to external data<br>memory. This pin is also the program pulse input (PROG) during Flash<br>programming. ALE can be disabled by setting SFR's AUXR.0 bit. With<br>this bit set, ALE will be inactive during internal fetches. |

| PSEN         | 32     | 26     | 67     | 55     | 0     | <b>Program Strobe ENable:</b> The read strobe to external program memory.<br>When executing code from the external program memory, <u>PSEN</u> is<br>activated twice each machine cycle, except that two <u>PSEN</u> activations<br>are skipped during each access to external data memory. <u>PSEN</u> is not<br>activated during fetches from internal program memory.                                                                                                                                                                                                                 |

| EA           | 35     | 29     | 2      | 58     | I     | <b>External Access Enable:</b> EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH. If security level 1 is programmed, EA will be internally latched on Reset.                                                                                                                                                                                                                                                                                                                                                       |

Reset Value = XXXX XX0X0b

Not bit addressable

Note: 1. Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

#### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Modifies DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added 00A2 AUXR1 EQU 0A2H 0000 909000MOV DPTR, #SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR, #DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A E0 MOVX A, @DPTR ; get a byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E F0 MOVX @DPTR,A ; write the byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

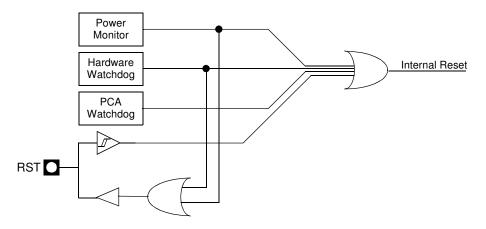

### 10. Reset

### 10.1 Introduction

The reset sources are: Power Management, Hardware Watchdog, PCA Watchdog and Reset input.

#### Figure 10-1. Reset schematic

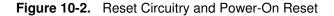

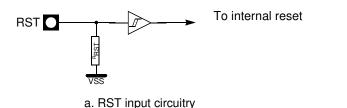

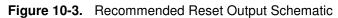

### 10.2 Reset Input

The Reset input can be used to force a reset pulse longer than the internal reset controlled by the Power Monitor. RST input has a pull-down resistor allowing power-on reset by simply connecting an external capacitor to  $V_{CC}$  as shown in Figure 10-2. Resistor value and input characteristics are discussed in the Section "DC Characteristics" of the AT89C51RD2/ED2 datasheet.

### 10.3 Reset Output

Reset output can be generated by two sources:

- Internal POR/PFD

- · Hardware watchdog timer

As detailed in Section "Hardware Watchdog Timer", page 84, the WDT generates a 96-clock period pulse on the RST pin.

In order to properly propagate this pulse to the rest of the application in case of external capacitor or power-supply supervisor circuit, a 1 k $\Omega$  resistor must be added as shown Figure 10-3.

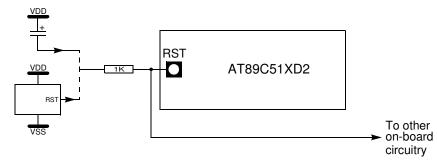

#### Figure 12-1. Auto-reload Mode Up/Down Counter (DCEN = 1)

### 12.2 Programmable Clock-output

In the clock-out mode, Timer 2 operates as a 50% duty-cycle, programmable clock generator (See Figure 12-2). The input clock increments TL2 at frequency  $F_{CLK PERIPH}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock-OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

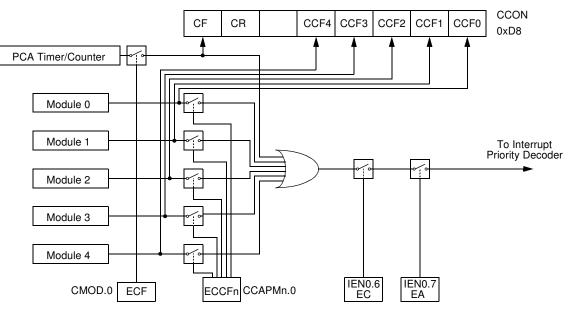

### Figure 13-2. PCA Interrupt System

**PCA Modules:** each one of the five compare/capture modules has six possible functions. It can perform:

- 16-bit Capture, positive-edge triggered

- 16-bit Capture, negative-edge triggered

- · 16-bit Capture, both positive and negative-edge triggered

- 16-bit Software Timer

- 16-bit High Speed Output

- · 8-bit Pulse Width Modulator

In addition, Module 4 can be used as a Watchdog Timer.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for Module 0, CCAPM1 for Module 1, etc. (See Table 13-3). The registers contain the bits that control the mode that each module will operate in.

- The ECCF bit (CCAPMn.0 where n = 0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module.

- PWM (CCAPMn.1) enables the pulse width modulation mode.

- The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the modules capture/compare register.

- The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the modules capture/compare register.

- The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

- The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

#### **Table 13-6.** CCAPnL Registers (n = 0 - 4)

CCAP0L - PCA Module 0 Compare/Capture Control Register Low (0EAh)

CCAP1L - PCA Module 1 Compare/Capture Control Register Low (0EBh)

CCAP2L - PCA Module 2 Compare/Capture Control Register Low (0ECh)

CCAP3L - PCA Module 3 Compare/Capture Control Register Low (0EDh)

CCAP4L - PCA Module 4 Compare/Capture Control Register Low (0EEh)

| 7             | 6               | 5                         | 4 | 3              | 2 | 1 | 0 |

|---------------|-----------------|---------------------------|---|----------------|---|---|---|

| -             | -               | -                         | - | -              | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description               |   |                |   |   |   |

| 7 - 0         | -               | PCA Module<br>CCAPnL Valu |   | apture Control |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 13-7. CH Register

CH - PCA Counter Register High (0F9h)

| 7             | 6               | 5                       | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------------------|---|---|---|---|---|

| -             | -               | -                       | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description             |   |   |   |   |   |

| 7 - 0         | -               | PCA counter<br>CH Value |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 13-8. CL Register

CL - PCA Counter Register Low (0E9h)

| 7             | 6               | 5                       | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------------------|---|---|---|---|---|

| -             | -               | -                       | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description             |   |   |   |   |   |

| 7 - 0         | -               | PCA Counter<br>CL Value |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

# Table 14-12.PCON RegisterPCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                               | 4                                                                                                                       | 3                            | 2                 | 1               | 0         |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------|-----------------|-----------|--|--|--|

| SMOD1         | SMOD0           | -                                                                                               | POF                                                                                                                     | GF1                          | GF0               | PD              | IDL       |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                 |                                                                                                                         | Desc                         | ription           |                 |           |  |  |  |

| 7             | SMOD1           |                                                                                                 | Serial port Mode bit 1 for UART<br>Set to select double baud rate in mode 1, 2 or 3.                                    |                              |                   |                 |           |  |  |  |

| 6             | SMOD0           | Cleared to se                                                                                   | erial port Mode bit 0 for UART<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register. |                              |                   |                 |           |  |  |  |

| 5             | -               | Reserved<br>The value re                                                                        | <b>eserved</b><br>he value read from this bit is indeterminate. Do not set this bit.                                    |                              |                   |                 |           |  |  |  |

| 4             | POF             |                                                                                                 | cognize next re                                                                                                         |                              | its nominal volta | age. Can also I | be set by |  |  |  |

| 3             | GF1             |                                                                                                 |                                                                                                                         | purpose usage.<br>ose usage. |                   |                 |           |  |  |  |

| 2             | GF0             |                                                                                                 |                                                                                                                         | purpose usage<br>ose usage.  |                   |                 |           |  |  |  |

| 1             | PD              | Cleared by h                                                                                    | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                          |                              |                   |                 |           |  |  |  |

| 0             | IDL             | Idle mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode. |                                                                                                                         |                              |                   |                 |           |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                         |  |  |  |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4          | MSTR         | Serial Peripheral Master<br>Cleared to configure the SPI as a Slave.<br>Set to configure the SPI as a Master.                                                                                                                       |  |  |  |

| 3          | CPOL         | Clock Polarity<br>Cleared to have the SCK set to '0' in idle state.<br>Set to have the SCK set to '1' in idle low.                                                                                                                  |  |  |  |

| 2          | СРНА         | Cleared to have the data sampled when the SCK leaves the idle state (see CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see CPOL).                                                                      |  |  |  |

| 1          | SPR1         | SPR2         SPR1         SPR0 Serial Peripheral Rate           0         0         1F <sub>CLK PERIPH</sub> /2           0         0         1F <sub>CLK PERIPH</sub> /4           0         1         0F <sub>CLK PERIPH</sub> /8 |  |  |  |

|            | SPR0         | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                               |  |  |  |

Reset Value = 0001 0100b

Not bit addressable

#### 16.3.5.2 Serial Peripheral Status Register (SPSTA)

The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 16-4 describes the SPSTA register and explains the use of every bit in the register.

### Table 16-4. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7          | 6               | 5                                                                                                                                                                                                                              | 4 | 3 | 2 | 1 | 0 |  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|--|

| SPIF       | WCOL            | SSERR MODF                                                                                                                                                                                                                     |   |   |   |   |   |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                    |   |   |   |   |   |  |

| 7          | SPIF            | Serial Peripheral Data Transfer Flag<br>Cleared by hardware to indicate data transfer is in progress or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed. |   |   |   |   |   |  |

| 6          | WCOL            | Write Collision Flag<br>Cleared by hardware to indicate that no collision has occurred or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that a collision has been detected.                      |   |   |   |   |   |  |

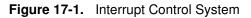

### 17. Interrupt System

The AT89C51RD2/ED2 has a total of 9 interrupt vectors: two external interrupts ( $\overline{INT0}$  and  $\overline{INT1}$ ), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt and the PCA global interrupt. These interrupts are shown in Figure 17-1.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 17-4 and Table 17-6). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (Table 17-7) and in the Interrupt Priority High register (Table 17-5 and Table 17-6) shows the bit values and priority levels associated with each combination.

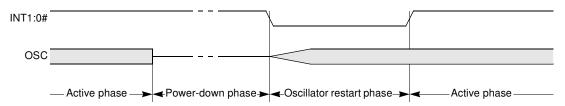

### 18.3 Power-Down Mode

The Power-Down mode places the AT89C51RD2/ED2 in a very low power state. Power-Down mode stops the oscillator, freezes all clock at known states. The CPU status prior to entering Power-Down mode is preserved, i.e., the program counter, program status word register retain their data for the duration of Power-Down mode. In addition, the SFR and RAM contents are preserved. The status of the Port pins during Power-Down mode is detailed in Table 18-1.

Note: VCC may be reduced to as low as V<sub>RET</sub> during Power-Down mode to further reduce power dissipation. Take care, however, that VDD is not reduced until Power-Down mode is invoked.

#### 18.3.1 Entering Power-Down Mode

To enter Power-Down mode, set PD bit in PCON register. The AT89C51RD2/ED2 enters the Power-Down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.

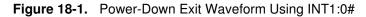

#### 18.3.2 Exiting Power-Down Mode

Note: If VCC was reduced during the Power-Down mode, do not exit Power-Down mode until VCC is restored to the normal operating level.

There are three ways to exit the Power-Down mode:

- 1. Generate an enabled external interrupt.

- The AT89C51RD2/ED2 provides capability to exit from Power-Down using INT0#, INT1#.

Hardware clears PD bit in PCON register which starts the oscillator and restores the clocks to the CPU and peripherals. Using INTx# input, execution resumes when the input is released (see Figure 18-1). Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Power-Down mode.

- Note: The external interrupt used to exit Power-Down mode must be configured as level sensitive (INT0# and INT1#) and must be assigned the highest priority. In addition, the duration of the interrupt must be long enough to allow the oscillator to stabilize. The execution will only resume when the interrupt is deasserted.

- Note: Exit from power-down by external interrupt does not affect the SFRs nor the internal RAM content.

- 2. Generate a reset.

- A logic high on the RST pin clears PD bit in PCON register directly and asynchronously. This starts the oscillator and restores the clock to the CPU and peripherals. Program execution momentarily resumes with the instruction immediately following the instruction that activated Power-Down mode and may

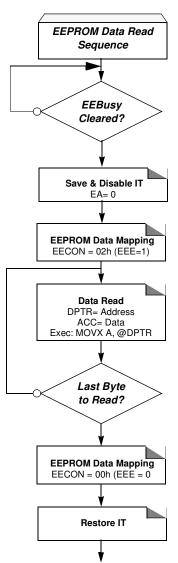

### Figure 23-2. Recommended EEPROM Data Read Sequence

### 23.3 Registers

Table 23-1.EECON RegisterEECON (0D2h)EEPROM Control Register

| 7          | 6               | 5                        | 4                                                                               | 3 | 2 | 1   | 0      |  |

|------------|-----------------|--------------------------|---------------------------------------------------------------------------------|---|---|-----|--------|--|

| -          | -               | -                        | -                                                                               | - | - | EEE | EEBUSY |  |

| Bit Number | Bit<br>Mnemonic | Description              | Description                                                                     |   |   |     |        |  |

| 7 - 2      | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |   |   |     |        |  |

#### 24.6.3 Functional Description

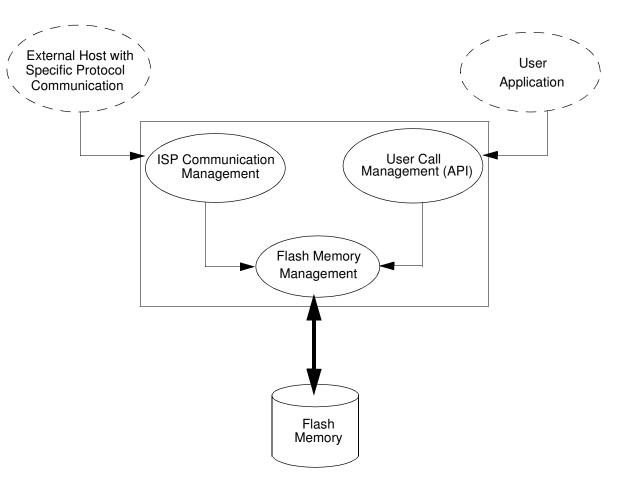

Figure 24-3. Bootloader Functional Description

On the above diagram, the on-chip bootloader processes are:

• ISP Communication Management

The purpose of this process is to manage the communication and its protocol between the onchip bootloader and a external device. The on-chip ROM implements a serial protocol (see section "Bootloader Protocol"). This process translate serial communication frame (UART) into Flash memory access (read, write, erase, etc.).

User Call Management

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made through a common interface (API calls), included in the ROM bootloader. The programming functions are selected by setting up the microcontroller's registers before making a call to a common entry point (0xFFF0). Results are returned in the registers. The purpose on this process is to translate the registers values into internal Flash Memory Management.

Flash Memory Management

This process manages low level access to Flash memory (performs read and write access).

#### 24.6.4 Bootloader Functionality

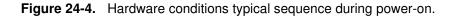

The bootloader can be activated by two means: Hardware conditions or regular boot process.

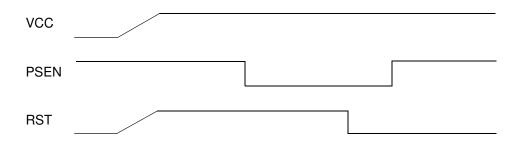

The Hardware conditions (EA = 1, PSEN = 0) during the Reset# falling edge force the on-chip bootloader execution. This allows an application to be built that will normally execute the end user's code but can be manually forced into default ISP operation.

As PSEN is a an output port in normal operating mode after reset, user application should take care to release PSEN after falling edge of reset signal. The hardware conditions are sampled at reset signal falling edge, thus they can be released at any time when reset input is low.

To ensure correct microcontroller startup, the PSEN pin should not be tied to ground during power-on (See Figure 24-4).

The on-chip bootloader boot process is shown Figure 24-5.

| Table 24-6. Boolloader Process Description | Table 24-6. | Bootloader Process Description |

|--------------------------------------------|-------------|--------------------------------|

|--------------------------------------------|-------------|--------------------------------|

|                     | Purpose                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Conditions | The Hardware Conditions force the bootloader execution whatever BLJB, BSB and SBV values.                                                                                                                                                                                                                                                     |

| BLJB                | The Boot Loader Jump Bit forces the application execution.<br>BLJB = 0 => Bootloader execution<br>BLJB = 1 => Application execution<br>The BLJB is a fuse bit in the Hardware Byte.<br>It can be modified by hardware (programmer) or by software (API).<br>Note: The BLJB test is performed by hardware to prevent any program<br>execution. |

| SBV                 | The Software Boot Vector contains the high address of customer bootloader<br>stored in the application.<br>SBV = FCh (default value) if no customer bootloader in user Flash.<br>Note: The customer bootloader is called by JMP [SBV]00h instruction.                                                                                         |

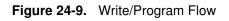

### 24.9.5 Write/Program Commands Description

This flow is common to the following frames:

- Flash/EEPROM Programming Data Frame

- EOF or Atmel Frame (only Programming Atmel Frame)

- Config Byte Programming Data Frame

- Baud Rate Frame

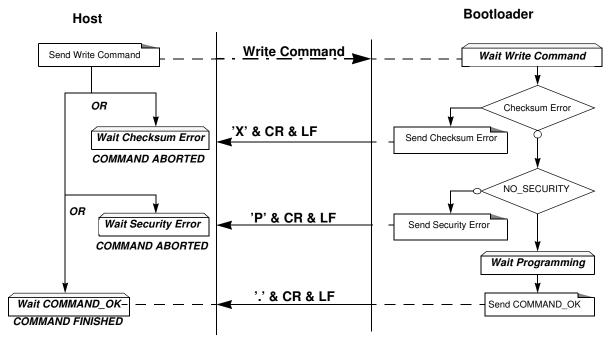

| Symbol            | Туре | Standard Clock | X2 Clock  | X parameter for<br>-M range | Units |

|-------------------|------|----------------|-----------|-----------------------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x        | T - x     | 15                          | ns    |

| T <sub>AVLL</sub> | Min  | T - x          | 0.5 T - x | 20                          | ns    |

| T <sub>LLAX</sub> | Min  | T - x          | 0.5 T - x | 20                          | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x        | 2 T - x   | 35                          | ns    |

| T <sub>LLPL</sub> | Min  | T - x          | 0.5 T - x | 15                          | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x        | 1.5 T - x | 25                          | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x        | 1.5 T - x | 45                          | ns    |

| T <sub>PXIX</sub> | Min  | x              | х         | 0                           | ns    |

| T <sub>PXIZ</sub> | Max  | T - x          | 0.5 T - x | 15                          | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x        | 2.5 T - x | 45                          | ns    |

| T <sub>PLAZ</sub> | Max  | х              | Х         | 10                          | ns    |

Table 25-3. AC Parameters for a Variable Clock

#### 25.3.3 External Program Memory Read Cycle

#### 25.3.4 External Data Memory Characteristics

| Symbol            | Туре | Standard<br>Clock | X2 Clock | X Parameter For<br>-M Range | Units |

|-------------------|------|-------------------|----------|-----------------------------|-------|

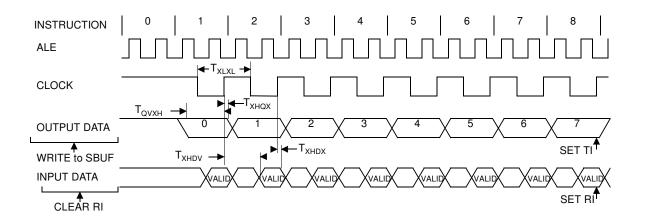

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |                             | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50                          | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20                          | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0                           | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133                         | ns    |

Table 25-9.

AC Parameters for a Variable Clock

#### 25.3.8 Shift Register Timing Waveforms

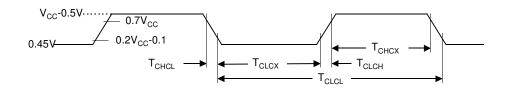

#### 25.3.9 External Clock Drive Waveforms

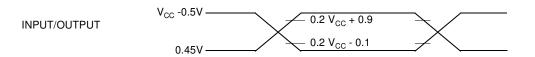

#### 25.3.10 AC Testing Input/Output Waveforms

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

| 14 | Serial  | I/O Port                                      | 48 |

|----|---------|-----------------------------------------------|----|

|    | 14.1    | Framing Error Detection                       | 48 |

|    | 14.2    | Automatic Address Recognition                 | 49 |

|    | 14.3    | Registers                                     | 51 |

|    | 14.4    | Baud Rate Selection for UART for Mode 1 and 3 | 51 |

|    | 14.5    | UART Registers                                | 54 |

| 15 | Keybo   | ard Interface                                 | 59 |

|    | 15.1    | Registers                                     | 60 |

| 16 | Serial  | Port Interface (SPI)                          | 63 |

|    | 16.1    | Features                                      | 63 |

|    | 16.2    | Signal Description                            | 63 |

|    | 16.3    | Functional Description                        | 65 |

| 17 | Interru | ıpt System                                    | 72 |

|    | 17.1    | Registers                                     | 73 |

|    | 17.2    | Interrupt Sources and Vector Addresses        | 73 |

| 18 | Power   | Management                                    | 80 |

|    | 18.1    | Introduction                                  | 80 |

|    | 18.2    | Idle Mode                                     | 80 |

|    | 18.3    | Power-Down Mode                               | 81 |

|    | 18.4    | Registers                                     | 83 |

| 19 | Hardw   | are Watchdog Timer                            | 84 |

|    | 19.1    | Using the WDT                                 | 84 |

|    | 19.2    | WDT during Power-down and Idle                | 85 |

| 20 | ONCE    | <sup>®</sup> Mode (ON- Chip Emulation)        | 86 |

| 21 | Power   | -off Flag                                     | 87 |

| 22 | Reduc   | ed EMI Mode                                   | 88 |

| 23 | EEPRO   | OM Data Memory                                |    |

|    | 23.1    | Write Data                                    |    |

|    | 23.2    | Read Data                                     |    |

|    | 23.3    | Registers                                     | 91 |

| 24 | Flash/  | EEPROM Memory                                 |    |

|    | 24.1    | Features                                      |    |

|    | 24.2    | Flash Programming and Erasure                 |    |

|    |         |                                               |    |

136 AT89C51RD2/ED2