# E·XFL

#### NXP USA Inc. - DSP56F803BU80E Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 56800                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 80MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SCI, SPI                                              |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 64KB (32K x 16)                                                        |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 16                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                              |

| Data Converters            | A/D 8x12b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56f803bu80e |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Add missing Ordering part section

| Part   | Supply<br>Voltage | Package Type                                 | Pin Count | Ambient<br>Frequency<br>(MHz) | Order Number                |

|--------|-------------------|----------------------------------------------|-----------|-------------------------------|-----------------------------|

|        |                   |                                              |           |                               |                             |

| 56F803 | 3.0–3.6 V         | Low Profile Plastic Quad Flat<br>Pack (LQFP) | 100       | 80                            | DSP56F803BU80E <sup>1</sup> |

#### Table 1. 56F803 Ordering Information

<sup>1</sup> This package is RoHS compliant

Addendum to Rev.16 of 56F803 Technical Data, Rev. 0, 10/2015

## **Document Revision History**

| Version History | Description of Change                                                                                                                                                                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 16         | Added revision history.<br>Added this text to footnote 2 in <b>Table 3-8</b> : "However, the high pulse width does not have to<br>be any particular percent of the low pulse width." |

56F803 Description

- Four General Purpose Quad Timers: Timer A (sharing pins with Quad Dec0), Timers B &C without external pins and Timer D with two pins

- CAN 2.0 B module with 2-pin ports for transmit and receive

- Serial Communication Interface (SCI) with two pins (or two additional GPIO lines)

- Serial Peripheral Interface (SPI) with configurable 4-pin port (or four additional GPIO lines)

- Computer Operating Properly (COP) Watchdog timer

- Two dedicated external interrupt pins

- Sixteen multiplexed General Purpose I/O (GPIO) pins

- External reset input pin for hardware reset

- JTAG/On-Chip Emulation (OnCE<sup>TM</sup>) for unobtrusive, processor speed-independent debugging

- Software-programmable, Phase Locked Loop-based frequency synthesizer for the controller core clock

### 1.1.4 Energy Information

- Fabricated in high-density CMOS with 5V-tolerant, TTL-compatible digital inputs

- Uses a single 3.3V power supply

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- Wait and Stop modes available

## 1.2 56F803 Description

The 56F803 is a member of the 56800 core-based family of processors. It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F803 is well-suited for many applications. The 56F803 includes many peripherals that are especially useful for applications such as motion control, smart appliances, steppers, encoders, tachometers, limit switches, power supply and control, automotive control, engine management, noise suppression, remote utility metering, and industrial control for power, lighting, and automation.

The 56800 core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact device and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

The 56F803 supports program execution from either internal or external memories. Two data operands can be accessed from the on-chip Data RAM per instruction cycle. The 56F803 also provides two external dedicated interrupt lines, and up to 16 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F803 controller includes 31.5K words (16-bit) of Program Flash and 4K words of Data Flash (each programmable through the JTAG port) with 512 words of Program RAM and 2K words of Data RAM. It also supports program execution from external memory.

A total of 2K words of Boot Flash is incorporated for easy customer-inclusion of field-programmable

## Part 2 Signal/Connection Descriptions

## 2.1 Introduction

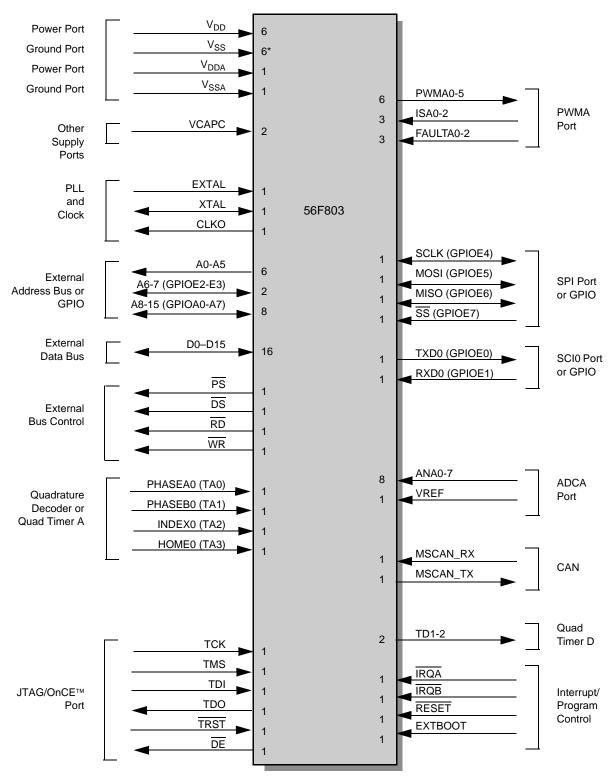

The input and output signals of the 56F803 are organized into functional groups, as shown in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2** through **Table 2-17**, each table row describes the signal or signals present on a pin.

| Functional Group                                        | Number of<br>Pins | Detailed<br>Description |  |

|---------------------------------------------------------|-------------------|-------------------------|--|

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )            | 7                 | Table 2-2               |  |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )           | 7                 | Table 2-3               |  |

| Supply Capacitors                                       | 2                 | Table 2-4               |  |

| PLL and Clock                                           | 3                 | Table 2-5               |  |

| Address Bus <sup>1</sup>                                | 16                | Table 2-6               |  |

| Data Bus                                                | 16                | Table 2-7               |  |

| Bus Control                                             | 4                 | Table 2-8               |  |

| Interrupt and Program Control                           | 4                 | Table 2-9               |  |

| Pulse Width Modulator (PWM) Port                        | 12                | Table 2-10              |  |

| Serial Peripheral Interface (SPI) Port <sup>1</sup>     | 4                 | Table 2-11              |  |

| Quadrature Decoder Port <sup>2</sup>                    | 4                 | Table 2-12              |  |

| Serial Communications Interface (SCI) Port <sup>1</sup> | 2                 | Table 2-13              |  |

| CAN Port                                                | 2                 | Table 2-14              |  |

| Analog to Digital Converter (ADC) Port                  | 9                 | Table 2-15              |  |

| Quad Timer Module Port                                  | 2                 | Table 2-16              |  |

| JTAG/On-Chip Emulation (OnCE)                           | 6                 | Table 2-17              |  |

1. Alternately, GPIO pins

2. Alternately, Quad Timer pins

Introduction

\*includes TCS pin which is reserved for factory use and is tied to VSS

## Figure 2-1 56F803 Signals Identified by Functional Group<sup>1</sup>

56F803 Technical Data, Rev. 16

<sup>1.</sup> Alternate pin functionality is shown in parenthesis.

## 2.3 Clock and Phase Locked Loop Signals

| No. of<br>Pins | Signal<br>Name | Signal<br>Type   | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | EXTAL          | Input            | Input                 | <b>External Crystal Oscillator Input</b> —This input should be connected to an 8MHz external crystal or ceramic resonator. For more information, please refer to <b>Section 3.5</b> .                                                                                                                                                                                                                             |

| 1              | XTAL           | Input/<br>Output | Chip-driven           | <b>Crystal Oscillator Output</b> —This output should be connected to an 8MHz external crystal or ceramic resonator. For more information, please refer to Section 3.5.<br>This pin can also be connected to an external clock source. For more information, please refer to Section 3.5.3.                                                                                                                        |

| 1              | CLKO           | Output           | Chip-driven           | <b>Clock Output</b> —This pin outputs a buffered clock signal. By<br>programming the CLKOSEL[4:0] bits in the CLKO Select Register<br>(CLKOSR), the user can select between outputting a version of the<br>signal applied to XTAL and a version of the device's master clock at the<br>output of the PLL. The clock frequency on this pin can also be disabled<br>by programming the CLKOSEL[4:0] bits in CLKOSR. |

#### Table 2-5 PLL and Clock

## 2.4 Address, Data, and Bus Control Signals

| No. of<br>Pins | Signal<br>Name    | Signal<br>Type   | State During<br>Reset | Signal Description                                                                                                                    |  |  |

|----------------|-------------------|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6              | A0–A5             | Output           | Tri-stated            | Address Bus—A0–A5 specify the address for external Program or Data memory accesses.                                                   |  |  |

| 2              | A6–A7             | Output           | Tri-stated            | Address Bus—A6–A7 specify the address for external Program or Data memory accesses.                                                   |  |  |

|                | GPIOE2-<br>GPIOE3 | Input/O<br>utput | Input                 | <b>Port E GPIO</b> —These two pins are General Purpose I/O (GPIO) pins that can be individually programmed as input or output pins.   |  |  |

|                |                   |                  |                       | After reset, the default state is Address Bus.                                                                                        |  |  |

| 8              | A8–A15            | Output           | Tri-stated            | Address Bus—A8–A15 specify the address for external Program or Data memory accesses.                                                  |  |  |

|                | GPIOA0-<br>GPIOA7 | Input/O<br>utput | Input                 | <b>Port A GPIO</b> —These eight pins are General Purpose I/O (GPIO) pins that can be individually programmed as input or output pins. |  |  |

|                |                   |                  |                       | After reset, the default state is Address Bus.                                                                                        |  |  |

#### **Table 2-6 Address Bus Signals**

| No. of<br>Pins | Signal<br>Name | Signal<br>Type     | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|----------------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | RESET          | Input<br>(Schmitt) | Input                 | Reset—This input is a direct hardware reset on the processor.When RESET is asserted low, the controller is initialized and placedin the Reset state. A Schmitt trigger input is used for noise immunity.When the RESET pin is deasserted, the initial chip operating modeis latched from the EXTBOOT pin. The internal reset signal will bedeasserted synchronous with the internal clocks, after a fixednumber of internal clocks.To ensure a complete hardware reset, RESET and TRST should beasserted together. The only exception occurs in a debuggingenvironment when a hardware device reset is required and it isnecessary not to reset the OnCE/JTAG module. In this case, assertRESET, but do not assert TRST. |

| 1              | EXTBOOT        | Input<br>(Schmitt) | Input                 | <b>External Boot</b> —This input is tied to $V_{DD}$ to force device to boot from off-chip memory. Otherwise, it is tied to $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 2-9 Interrupt and Program Control Signals (Continued)

## 2.6 Pulse Width Modulator (PWM) Signals

| No.of<br>Pins | Signal<br>Name | Signal<br>Type     | State During<br>Reset | Signal Description                                                                                                                                |  |  |

|---------------|----------------|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6             | PWMA0–5        | Output             | Tri-stated            | <b>PWMA0–5</b> — These are six PWMA output pins.                                                                                                  |  |  |

| 3             | ISA0–2         | Input<br>(Schmitt) | Input                 | <b>ISA0–2</b> — These three input current status pins are used for top/bottom pulse width correction in complementary channel operation for PWMA. |  |  |

| 3             | FAULTA0-2      | Input<br>(Schmitt) | Input                 | <b>FAULTA0–2</b> — These three fault input pins are used for disabling selected PWMA outputs in cases where fault conditions originate off-chip.  |  |  |

Absolute maximum ratings given in **Table 3-1** are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

The 56F803 DC/AC electrical specifications are preliminary and are from design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after complete characterization and device qualifications have been completed.

#### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

| Characteristic                                                                                                                              | Symbol          | Min                    | Max                    | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| Supply voltage                                                                                                                              | V <sub>DD</sub> | V <sub>SS</sub> -0.3   | V <sub>SS</sub> + 4.0  | V    |

| All other input voltages, excluding Analog inputs                                                                                           | V <sub>IN</sub> | V <sub>SS</sub> – 0.3  | V <sub>SS</sub> + 5.5V | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub>                                                                                      | $\Delta V_{DD}$ | - 0.3                  | 0.3                    | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub>                                                                                      | $\Delta V_{SS}$ | - 0.3                  | 0.3                    | V    |

| Analog inputs ANA0-7 and VREF                                                                                                               | V <sub>IN</sub> | V <sub>SSA</sub> - 0.3 | V <sub>DDA</sub> + 0.3 | V    |

| Analog inputs EXTAL and XTAL                                                                                                                | V <sub>IN</sub> | V <sub>SSA</sub> - 0.3 | V <sub>SSA</sub> + 3.0 | V    |

| Current drain per pin excluding V <sub>DD</sub> , V <sub>SS</sub> , PWM outputs, TCS, V <sub>PP</sub> , V <sub>DDA</sub> , V <sub>SSA</sub> | I               | _                      | 10                     | mA   |

#### Table 3-1 Absolute Maximum Ratings

#### **Table 3-2 Recommended Operating Conditions**

| Characteristic                                         | Symbol           | Min  | Тур | Мах | Unit |

|--------------------------------------------------------|------------------|------|-----|-----|------|

| Supply voltage, digital                                | V <sub>DD</sub>  | 3.0  | 3.3 | 3.6 | V    |

| Supply Voltage, analog                                 | V <sub>DDA</sub> | 3.0  | 3.3 | 3.6 | V    |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub> | $\Delta V_{DD}$  | -0.1 | -   | 0.1 | V    |

- 4. Thermal Characterization Parameter, Psi-JT ( $\Psi_{JT}$ ), is the "resistance" from junction to reference point thermocouple on top center of case as defined in JESD51-2.  $\Psi_{JT}$  is a useful value to use to estimate junction temperature in steady state customer environments.

- 5. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 6. See Section 5.1 from more details on thermal design considerations.

- 7. TJ = Junction Temperature TA = Ambient Temperature

## 3.2 DC Electrical Characteristic

#### **Table 3-4 DC Electrical Characteristics**

Operating Conditions:  $V_{SS} = V_{SSA} = 0$  V,  $V_{DD} = V_{DDA} = 3.0-3.6$  V,  $T_A = -40^{\circ}$  to  $+85^{\circ}$ C,  $C_L \le 50$  pF,  $f_{op} = 80$  MHz

| Characteristic                                                                      | Symbol                            | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------|-----------------------------------|------|-----|------|------|

| Input high voltage (XTAL/EXTAL)                                                     | V <sub>IHC</sub>                  | 2.25 | _   | 2.75 | V    |

| Input low voltage (XTAL/EXTAL)                                                      | V <sub>ILC</sub>                  | 0    | _   | 0.5  | V    |

| Input high voltage (Schmitt trigger inputs) <sup>1</sup>                            | V <sub>IHS</sub>                  | 2.2  | _   | 5.5  | V    |

| Input low voltage (Schmitt trigger inputs) <sup>1</sup>                             | V <sub>ILS</sub>                  | -0.3 | _   | 0.8  | V    |

| Input high voltage (all other digital inputs)                                       | V <sub>IH</sub>                   | 2.0  | —   | 5.5  | V    |

| Input low voltage (all other digital inputs)                                        | V <sub>IL</sub>                   | -0.3 | _   | 0.8  | V    |

| Input current high (pullup/pulldown resistors disabled, $V_{IN}$ =V <sub>DD</sub> ) | I <sub>IH</sub>                   | -1   | _   | 1    | μA   |

| Input current low (pullup/pulldown resistors disabled, $V_{IN}{=}V_{SS})$           | l <sub>IL</sub>                   | -1   | _   | 1    | μA   |

| Input current high (with pullup resistor, $V_{IN}=V_{DD}$ )                         | I <sub>IHPU</sub>                 | -1   | _   | 1    | μA   |

| Input current low (with pullup resistor, $V_{\text{IN}}\text{=}V_{\text{SS}})$      | I <sub>ILPU</sub>                 | -210 | _   | -50  | μA   |

| Input current high (with pulldown resistor, $V_{IN}=V_{DD}$ )                       | I <sub>IHPD</sub>                 | 20   | _   | 180  | μA   |

| Input current low (with pulldown resistor, $V_{IN} = V_{SS}$ )                      | I <sub>ILPD</sub>                 | -1   | —   | 1    | μA   |

| Nominal pullup or pulldown resistor value                                           | R <sub>PU</sub> , R <sub>PD</sub> |      | 30  |      | KΩ   |

| Output tri-state current low                                                        | I <sub>OZL</sub>                  | -10  | -   | 10   | μA   |

| Output tri-state current high                                                       | I <sub>OZH</sub>                  | -10  | _   | 10   | μΑ   |

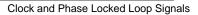

Note: The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

#### **Figure 3-2 Input Signal Measurement References**

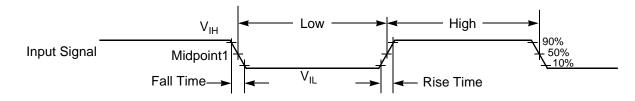

**Figure 3-3** shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached  $V_{OL}$  or  $V_{OH}$

- Data Invalid state, when a signal level is in transition between  $V_{\mbox{OL}}$  and  $V_{\mbox{OH}}$

**Figure 3-3 Signal States**

## 3.4 Flash Memory Characteristics

| Mode         | XE <sup>1</sup> | YE <sup>2</sup> | SE <sup>3</sup> | OE <sup>4</sup> | PROG <sup>5</sup> | ERASE <sup>6</sup> | MAS1 <sup>7</sup> | NVSTR <sup>8</sup> |

|--------------|-----------------|-----------------|-----------------|-----------------|-------------------|--------------------|-------------------|--------------------|

| Standby      | L               | L               | L               | L               | L                 | L                  | L                 | L                  |

| Read         | Н               | Н               | Н               | Н               | L                 | L                  | L                 | L                  |

| Word Program | Н               | Н               | L               | L               | Н                 | L                  | L                 | Н                  |

| Page Erase   | Н               | L               | L               | L               | L                 | Н                  | L                 | Н                  |

| Mass Erase   | Н               | L               | L               | L               | L                 | Н                  | Н                 | Н                  |

#### **Table 3-5 Flash Memory Truth Table**

1. X address enable, all rows are disabled when XE = 0

2. Y address enable, YMUX is disabled when YE = 0

3. Sense amplifier enable

4. Output enable, tri-state Flash data out bus when OE = 0

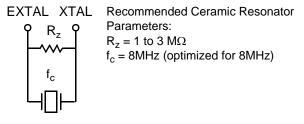

### 3.5.2 Ceramic Resonator

It is also possible to drive the internal oscillator with a ceramic resonator, assuming the overall system design can tolerate the reduced signal integrity. In **Figure 3-8**, a typical ceramic resonator circuit is shown. Refer to supplier's recommendations when selecting a ceramic resonator and associated components. The resonator and components should be mounted as close as possible to the EXTAL and XTAL pins. The internal 56F80x oscillator circuitry is designed to have no external load capacitors present. As shown in **Figure 3-7** no external load capacitors should be used.

Figure 3-8 Connecting a Ceramic Resonator

**Note:** Freescale recommends only two terminal ceramic resonators vs. three terminal resonators (which contain an internal bypass capacitor to ground).

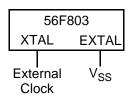

### 3.5.3 External Clock Source

The recommended method of connecting an external clock is given in **Figure 3-9**. The external clock source is connected to XTAL and the EXTAL pin is grounded.

Figure 3-9 Connecting an External Clock Signal

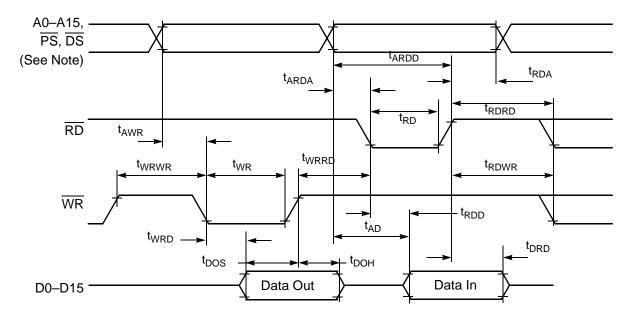

- 1. Timing is both wait state and frequency dependent. In the formulas listed, WS = the number of wait states and

- T = Clock Period. For 80MHz operation, T = 12.5ns.

- 2. Parameters listed are guaranteed by design.

To calculate the required access time for an external memory for any frequency < 80Mhz, use this formula:

Top = Clock period @ desired operating frequency

WS = Number of wait states

Memory Access Time =  $(Top^*WS) + (Top- 11.5)$

Note: During read-modify-write instructions and internal instructions, the address lines do not change state.

#### Figure 3-11 External Bus Asynchronous Timing

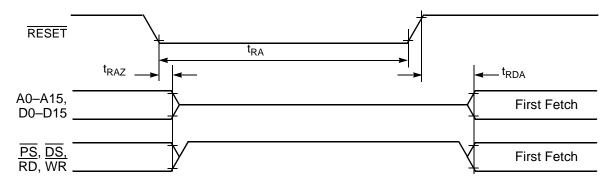

#### 3.7 Reset, Stop, Wait, Mode Select, and Interrupt Timing

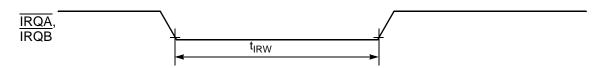

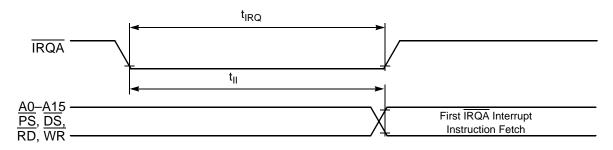

# Table 3-11 Reset, Stop, Wait, Mode Select, and Interrupt Timing <sup>1, 5</sup> Operating Conditions: $V_{SS} = V_{SSA} = 0$ V, $V_{DD} = V_{DDA} = 3.0-3.6$ V, $T_A = -40^{\circ}$ to $+85^{\circ}$ C, $C_L \le 50$ pF

| Characteristic                                                                                      | Symbol           | Min              | Max | Unit     | See Figure  |

|-----------------------------------------------------------------------------------------------------|------------------|------------------|-----|----------|-------------|

| RESET Assertion to Address, Data and Control Signals High Impedance                                 | t <sub>RAZ</sub> | _                | 21  | ns       | Figure 3-12 |

| Minimum $\overline{\text{RESET}}$ Assertion Duration <sup>2</sup><br>OMR Bit 6 = 0<br>OMR Bit 6 = 1 | t <sub>RA</sub>  | 275,000T<br>128T |     | ns<br>ns | Figure 3-12 |

| RESET De-assertion to First External Address Output                                                 | t <sub>RDA</sub> | 33T              | 34T | ns       | Figure 3-12 |

Figure 3-12 Asynchronous Reset Timing

Figure 3-13 External Interrupt Timing (Negative-Edge-Sensitive)

Figure 3-17 Recovery from Stop State Using IRQA Interrupt Service

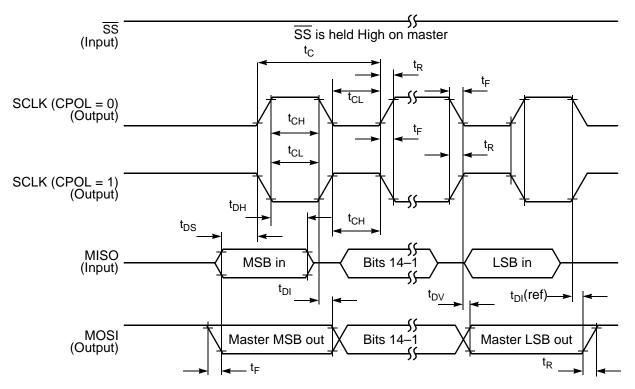

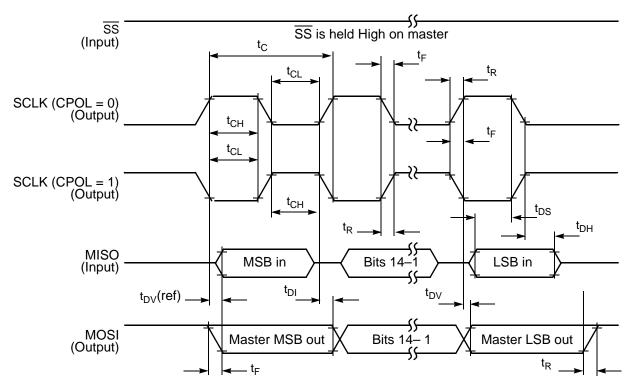

## 3.8 Serial Peripheral Interface (SPI) Timing

| Characteristic                                                          | Symbol           | Min          | Max  | Unit     | See Figure                                           |

|-------------------------------------------------------------------------|------------------|--------------|------|----------|------------------------------------------------------|

| Cycle time<br>Master<br>Slave                                           | t <sub>C</sub>   | 50<br>25     | _    | ns<br>ns | Figures <b>3-18</b> , ,<br><b>3-20</b> , <b>3-21</b> |

| Enable lead time<br>Master<br>Slave                                     | t <sub>ELD</sub> | <br>25       | _    | ns<br>ns | Figure 3-21                                          |

| Enable lag time<br>Master<br>Slave                                      | t <sub>ELG</sub> | <br>100      | _    | ns<br>ns | Figure 3-21                                          |

| Clock (SCLK) high time<br>Master<br>Slave                               | t <sub>CH</sub>  | 17.6<br>12.5 | _    | ns<br>ns | Figures <b>3-18</b> , ,<br><b>3-20</b> , <b>3-21</b> |

| Clock (SCLK) low time<br>Master<br>Slave                                | t <sub>CL</sub>  | 24.1<br>25   | _    | ns<br>ns | Figures <b>3-18</b> , ,<br><b>3-20</b> , <b>3-21</b> |

| Data set-up time required for inputs<br>Master<br>Slave                 | t <sub>DS</sub>  | 20<br>0      | _    | ns<br>ns | Figures <b>3-18</b> , ,<br><b>3-20</b> , <b>3-21</b> |

| Data hold time required for inputs<br>Master<br>Slave                   | t <sub>DH</sub>  | 0<br>2       | _    | ns<br>ns | Figures <b>3-18</b> , ,<br><b>3-20</b> , <b>3-21</b> |

| Access time (time to data active from high-impedance<br>state)<br>Slave | t <sub>A</sub>   | 4.8          | 15   | ns       | Figure 3-21                                          |

| Disable time (hold time to high-impedance state)<br>Slave               | t <sub>D</sub>   | 3.7          | 15.2 | ns       | Figure 3-21                                          |

$\label{eq:conditions} \begin{array}{l} \textbf{Table 3-12 SPI Timing^1} \\ \textbf{Operating Conditions: } v_{SS} = v_{SSA} = 0 \text{ V}, v_{DD} = v_{DDA} = 3.0 - 3.6 \text{ V}, \text{ } T_A = -40^\circ \text{ to } +85^\circ \text{C}, \text{ } C_L \leq 50 \text{pF}, \text{ } f_{OP} = 80 \text{MHz} \end{array}$

$\label{eq:conditions} \begin{array}{l} \textbf{Table 3-12 SPI Timing^1} \\ \textbf{Operating Conditions: } v_{SS} = v_{SSA} = 0 \text{ V}, v_{DD} = v_{DDA} = 3.0 - 3.6 \text{ V}, \text{ } T_A = -40^\circ \text{ to } +85^\circ \text{C}, \text{ } C_L \leq 50 \text{pF}, \text{ } f_{OP} = 80 \text{MHz} \end{array}$

| Characteristic            | Symbol          | Min | Max  | Unit | See Figure              |

|---------------------------|-----------------|-----|------|------|-------------------------|

| Data Valid for outputs    | t <sub>DV</sub> |     |      |      | Figures 3-18, ,         |

| Master                    |                 | —   | 4.5  | ns   | 3-20, 3-21              |

| Slave (after enable edge) |                 | —   | 20.4 | ns   |                         |

| Data invalid              | t <sub>DI</sub> |     |      |      | Figures 3-18, ,         |

| Master                    |                 | 0   | —    | ns   | 3-20, 3-21              |

| Slave                     |                 | 0   | —    | ns   |                         |

| Rise time                 | t <sub>R</sub>  |     |      |      | Figures 3-18, ,         |

| Master                    |                 | —   | 11.5 | ns   | 3-20, 3-21              |

| Slave                     |                 | —   | 10.0 | ns   |                         |

| Fall time                 | t <sub>F</sub>  |     |      |      | Figures <b>3-18</b> , , |

| Master                    |                 | —   | 9.7  | ns   | 3-20, 3-21              |

| Slave                     |                 | —   | 9.0  | ns   |                         |

1. Parameters listed are guaranteed by design.

Figure 3-19 SPI Master Timing (CPHA = 1)

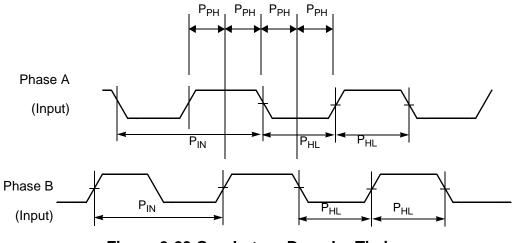

### Figure 3-23 Quadrature Decoder Timing

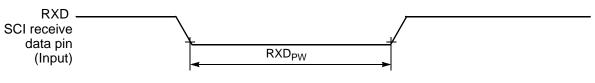

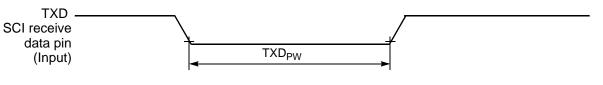

## 3.11 Serial Communication Interface (SCI) Timing

$\label{eq:conditions} \begin{array}{c} \textbf{Table 3-15 SCI Timing^4} \\ \textbf{Operating Conditions: } v_{SS} = v_{SSA} = 0 \text{ V}, \text{ } v_{DD} = v_{DDA} = 3.0 - 3.6 \text{ V}, \text{ } T_A = -40^\circ \text{ to } +85^\circ \text{C}, \text{ } C_L \leq 50 \text{pF}, \text{ } f_{OP} = 80 \text{MHz} \end{array}$

| Characteristic               | Symbol            | Min      | Мах                          | Unit |

|------------------------------|-------------------|----------|------------------------------|------|

| Baud Rate <sup>1</sup>       | BR                | _        | (f <sub>MAX</sub> *2.5)/(80) | Mbps |

| RXD <sup>2</sup> Pulse Width | RXD <sub>PW</sub> | 0.965/BR | 1.04/BR                      | ns   |

| TXD <sup>3</sup> Pulse Width | TXD <sub>PW</sub> | 0.965/BR | 1.04/BR                      | ns   |

1. f<sub>MAX</sub> is the frequency of operation of the system clock in MHz.

2. The RXD pin in SCI0 is named RXD0 and the RXD pin in SCI1 is named RXD1.

3. The TXD pin in SCI0 is named TXD0 and the TXD pin in SCI1 is named TXD1.

4. Parameters listed are guaranteed by design.

Figure 3-24 RXD Pulse Width

#### Figure 3-25 TXD Pulse Width

## 3.12 Analog-to-Digital Converter (ADC) Characteristics

| Characteristic                               | Symbol              | Min              | Тур     | Мах              | Unit                                 |  |

|----------------------------------------------|---------------------|------------------|---------|------------------|--------------------------------------|--|

| ADC input voltages                           | V <sub>ADCIN</sub>  | 0 <sup>1</sup>   | —       | $V_{REF}^2$      | V                                    |  |

| Resolution                                   | R <sub>ES</sub>     | 12               | _       | 12               | Bits                                 |  |

| Integral Non-Linearity <sup>3</sup>          | INL                 | —                | +/- 2.5 | +/- 4            | LSB <sup>4</sup>                     |  |

| Differential Non-Linearity                   | DNL                 | —                | +/- 0.9 | +/- 1            | LSB <sup>4</sup>                     |  |

| Monotonicity                                 |                     | GUARANTEED       |         |                  |                                      |  |

| ADC internal clock <sup>5</sup>              | f <sub>ADIC</sub>   | 0.5              | _       | 5                | MHz                                  |  |

| Conversion range                             | R <sub>AD</sub>     | V <sub>SSA</sub> | _       | V <sub>DDA</sub> | V                                    |  |

| Power-up time                                | t <sub>ADPU</sub>   | —                | 16      | —                | t <sub>AIC</sub> cycles <sup>6</sup> |  |

| Conversion time                              | t <sub>ADC</sub>    | _                | 6       | —                | t <sub>AIC</sub> cycles <sup>6</sup> |  |

| Sample time                                  | t <sub>ADS</sub>    | —                | 1       | —                | t <sub>AIC</sub> cycles <sup>6</sup> |  |

| Input capacitance                            | C <sub>ADI</sub>    | —                | 5       | —                | pF <sup>6</sup>                      |  |

| Gain Error (transfer gain) <sup>5</sup>      | E <sub>GAIN</sub>   | 0.95             | 1.00    | 1.10             | —                                    |  |

| Offset Voltage <sup>5</sup>                  | V <sub>OFFSET</sub> | -80              | -15     | +20              | mV                                   |  |

| Total Harmonic Distortion <sup>5</sup>       | THD                 | 60               | 64      | —                | dB                                   |  |

| Signal-to-Noise plus Distortion <sup>5</sup> | SINAD               | 55               | 60      | —                | dB                                   |  |

| Effective Number of Bits <sup>5</sup>        | ENOB                | 9                | 10      | _                | bit                                  |  |

| Spurious Free Dynamic Range <sup>5</sup>     | SFDR                | 65               | 70      | —                | dB                                   |  |

| Bandwidth                                    | BW                  | —                | 100     | —                | KHz                                  |  |

#### **Table 3-16 ADC Characteristics**

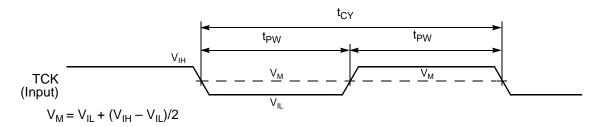

## 3.14 JTAG Timing

$\label{eq:conditions} \begin{array}{l} \mbox{Table 3-18 JTAG Timing}^{1,\ 3} \\ \mbox{Operating Conditions: } v_{SS} = v_{SSA} = 0 \ V, \ v_{DD} = v_{DDA} = 3.0 - 3.6 \ V, \ T_A = -40^\circ \ to \ +85^\circ C, \ C_L \le 50 \ pF, \ f_{OP} = 80 \ MHz \end{array}$

| Characteristic                          | Symbol            | Min | Max  | Unit |

|-----------------------------------------|-------------------|-----|------|------|

| TCK frequency of operation <sup>2</sup> | f <sub>OP</sub>   | DC  | 10   | MHz  |

| TCK cycle time                          | t <sub>CY</sub>   | 100 | _    | ns   |

| TCK clock pulse width                   | t <sub>PW</sub>   | 50  | _    | ns   |

| TMS, TDI data set-up time               | t <sub>DS</sub>   | 0.4 | _    | ns   |

| TMS, TDI data hold time                 | t <sub>DH</sub>   | 1.2 | _    | ns   |

| TCK low to TDO data valid               | t <sub>DV</sub>   | —   | 26.6 | ns   |

| TCK low to TDO tri-state                | t <sub>TS</sub>   | —   | 23.5 | ns   |

| TRST assertion time                     | t <sub>TRST</sub> | 50  | _    | ns   |

| DE assertion time                       | t <sub>DE</sub>   | 4T  | _    | ns   |

1. Timing is both wait state and frequency dependent. For the values listed, T = clock cycle. For 80MHz operation, T = 12.5ns.

2. TCK frequency of operation must be less than 1/8 the processor rate.

3. Parameters listed are guaranteed by design.

#### Figure 3-28 Test Clock Input Timing Diagram

| Pin No. | Signal Name     | Pin No. | Signal Name     | Pin No. | Signal Name      | Pin No. | Signal Name     |

|---------|-----------------|---------|-----------------|---------|------------------|---------|-----------------|

| 1       | D10             | 26      | A14             | 51      | AN2              | 76      | TXD0            |

| 2       | D11             | 27      | A15             | 52      | AN3              | 77      | RXD0            |

| 3       | D12             | 28      | V <sub>SS</sub> | 53      | AN4              | 78      | EXTBOOT         |

| 4       | D13             | 29      | WR              | 54      | AN5              | 79      | RESET           |

| 5       | D14             | 30      | RD              | 55      | AN6              | 80      | DE              |

| 6       | D15             | 31      | IRQA            | 56      | AN7              | 81      | CLKO            |

| 7       | A0              | 32      | IRQB            | 57      | XTAL             | 82      | TD1             |

| 8       | V <sub>DD</sub> | 33      | TCS             | 58      | EXTAL            | 83      | TD2             |

| 9       | V <sub>SS</sub> | 34      | ТСК             | 59      | V <sub>SSA</sub> | 84      | SS              |

| 10      | A1              | 35      | TMS             | 60      | V <sub>DDA</sub> | 85      | MISO            |

| 11      | A2              | 36      | TDI             | 61      | V <sub>DD</sub>  | 86      | MOSI            |

| 12      | A3              | 37      | TDO             | 62      | V <sub>DD</sub>  | 87      | SCLK            |

| 13      | A4              | 38      | TRST            | 63      | V <sub>SS</sub>  | 88      | VCAPC           |

| 14      | A5              | 39      | VCAPC           | 64      | PHASEA0          | 89      | D0              |

| 15      | A6              | 40      | ISA0            | 65      | PHASEB0          | 90      | D1              |

| 16      | A7              | 41      | ISA1            | 66      | V <sub>DD</sub>  | 91      | D2              |

| 17      | A8              | 42      | ISA2            | 67      | V <sub>SS</sub>  | 92      | V <sub>DD</sub> |

| 18      | A9              | 43      | FAULTA0         | 68      | INDEX0           | 93      | V <sub>SS</sub> |

| 19      | A10             | 44      | MSCAN_TX        | 69      | HOME0            | 94      | D3              |

| 20      | A11             | 45      | FAULTA1         | 70      | PWMA0            | 95      | D4              |

| 21      | A12             | 46      | MSCAN_RX        | 71      | PWMA1            | 96      | D5              |

| 22      | A13             | 47      | FAULTA2         | 72      | PWMA2            | 97      | D6              |

| 23      | V <sub>DD</sub> | 48      | VREF            | 73      | PWMA3            | 98      | D7              |

| 24      | PS              | 49      | AN0             | 74      | PWMA4            | 99      | D8              |

| 25      | DS              | 50      | AN1             | 75      | PWMA5            | 100     | D9              |

| Table 4-1 56F803 Pin Identification By Pin Number |

|---------------------------------------------------|

|---------------------------------------------------|