Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ROM                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

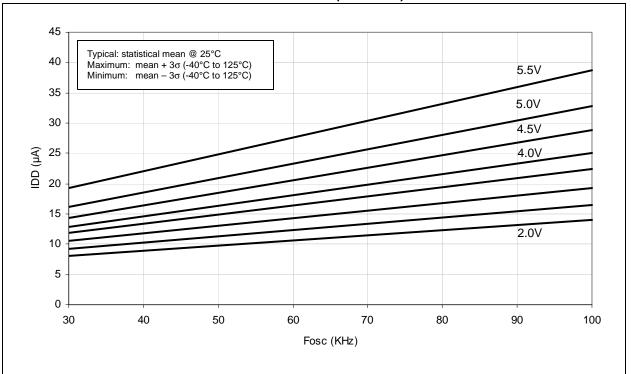

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

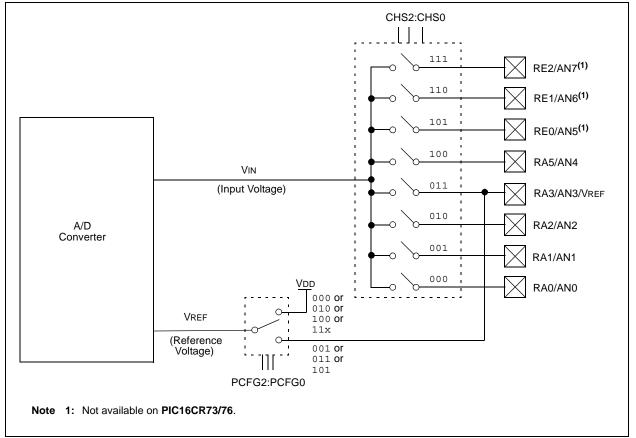

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr73-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-3: PIC16CR74 AND PIC16CR77 PINOUT DESCRIPTION

| PDIP<br>Pin# | PLCC<br>Pin#                                                                                           | QFP<br>Pin#                                                                                                                                                                                                    | I/O/P<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                  | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13           | 14                                                                                                     | 30                                                                                                                                                                                                             | Ι                                                                                                                                                                                                                                                                                                                                                                                                                              | ST/CMOS <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode. Otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                                                                                                        |                                                                                                                                                                                                                | Ι                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOS.<br>External clock source input. Always associated with pin<br>function OSC1 (see OSC1/CLKIN, OSC2/CLKOUT<br>pins).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14           | 15                                                                                                     | 31                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator<br>mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              |                                                                                                        |                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4<br>the frequency of OSC1 and denotes the instruction<br>cycle rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1            | 2                                                                                                      | 18                                                                                                                                                                                                             | I                                                                                                                                                                                                                                                                                                                                                                                                                              | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Master Clear (Reset) input. This pin is an active low Reset to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                                                                                                        |                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2            | 3                                                                                                      | 19                                                                                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                                                                                                                                       | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.<br>Analog input 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3            | 4                                                                                                      | 20                                                                                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                                                                                                                                       | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.<br>Analog input 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4            | 5                                                                                                      | 21                                                                                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                                                                                                                                       | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.<br>Analog input 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5            | 6                                                                                                      | 22                                                                                                                                                                                                             | I/O<br>I<br>I                                                                                                                                                                                                                                                                                                                                                                                                                  | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.<br>Analog input 3.<br>A/D reference voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6            | 7                                                                                                      | 23                                                                                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                                                                                                                                       | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital I/O – Open drain when configured as output.<br>Timer0 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7            | 8                                                                                                      | 24                                                                                                                                                                                                             | I/O<br>I<br>I                                                                                                                                                                                                                                                                                                                                                                                                                  | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.<br>Analog input 4.<br>SPI slave select input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | Pin#           13           14           1           2           3           4           5           6 | Pin#         Pin#           13         14           13         14           14         15           14         15           14         15           14         15           15         6           6         7 | Pin#         Pin#           13         14         30           13         14         30           14         30           14         15         31           14         15         31           14         15         31           1         2         18           2         3         19           3         4         20           4         5         21           5         6         22           6         7         23 | Pin#         Pin#         Type           13         14         30         1           13         14         30         1           14         14         30         1           14         15         31         0           14         15         31         0           14         15         31         0           14         15         31         0           14         15         31         0           14         15         31         0           14         15         31         0           1         2         18         1           2         3         19         1/0           3         4         20         1/0           4         5         21         1/0           5         6         22         1/0           6         7         23         1/0           7         8         24         1/0 | Pin#         Pin#         Type         Type           13         14         30         1         ST/CMOS <sup>(4)</sup> 13         14         30         1         1           14         15         31         1         1           14         15         31         O            1         2         18         I         ST           1         2         18         I         ST           1         1         ST             1         1         TTL         I/O            1         5         6         22         I/O            1         1               5         6         22         I/O |

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name        | PDIP<br>Pin# | PLCC<br>Pin#    | QFP<br>Pin#      | I/O/P<br>Type | Buffer<br>Type        | Description                                                                     |

|-----------------|--------------|-----------------|------------------|---------------|-----------------------|---------------------------------------------------------------------------------|

|                 |              |                 |                  |               |                       | PORTD is a bidirectional I/O port or parallel slave port                        |

|                 |              |                 |                  |               |                       | when interfacing to a microprocessor bus.                                       |

| RD0/PSP0        | 19           | 21              | 38               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD0<br>PSP0     |              |                 |                  | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                       |

|                 | 20           | 00              | 20               |               | ST/TTL <sup>(3)</sup> | Paraller Slave Port data.                                                       |

| RD1/PSP1<br>RD1 | 20           | 22              | 39               | I<br>I/O      | 51/1124               | Digital I/O.                                                                    |

| PSP1            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD2/PSP2        | 21           | 23              | 40               | 1             | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD2             |              |                 |                  | I/O           | 0.,                   | Digital I/O.                                                                    |

| PSP2            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD3/PSP3        | 22           | 24              | 41               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD3             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP3            |              |                 |                  | I/O           | (2)                   | Parallel Slave Port data.                                                       |

| RD4/PSP4        | 27           | 30              | 2                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD4<br>PSP4     |              |                 |                  | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                       |

| -               | 20           | 24              | 2                | 1/0           | ST/TTL <sup>(3)</sup> | Paraller Slave Port data.                                                       |

| RD5/PSP5<br>RD5 | 28           | 31              | 3                | I/O           | 51/1124               | Digital I/O.                                                                    |

| PSP5            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD6/PSP6        | 29           | 32              | 4                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD6             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP6            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD7/PSP7        | 30           | 33              | 5                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD7             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP7            | _            |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

|                 |              |                 |                  |               | (2)                   | PORTE is a bidirectional I/O port.                                              |

| RE0/AN5/RD/     | 8            | 9               | 25               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE0<br>AN5      |              |                 |                  | I/O<br>I      |                       | Digital I/O.<br>Analog input 5.                                                 |

|                 |              |                 |                  | 1             |                       | Read control for parallel slave port .                                          |

| RE1/AN6/WR/     | 9            | 10              | 26               | -             | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE1             | °,           |                 |                  | I/O           | 0.,                   | Digital I/O.                                                                    |

| AN6             |              |                 |                  | I             |                       | Analog input 6.                                                                 |

| WR              |              |                 |                  | I             |                       | Write control for parallel slave port .                                         |

| RE2/AN7/CS      | 10           | 11              | 27               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE2             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| AN7<br>CS       |              |                 |                  |               |                       | Analog input 7.<br>Chip Select control for parallel slave port .                |

| Vss             | 12,31        | 13,34           | 6,29             | P             |                       | Ground reference for logic and I/O pins.                                        |

| VSS<br>VDD      | 12,31        | 12,35           | 7,28             | <br>Р         |                       | Positive supply for logic and I/O pins.                                         |

| NC              | 11,52        |                 |                  | Г             |                       |                                                                                 |

|                 |              | 1,17,<br>28, 40 | 12,13,<br>33, 34 |               |                       | These pins are not internally connected. These pins should be left unconnected. |

#### TABLE 1-3: PIC16CR74 AND PIC16CR77 PINOUT DESCRIPTION (CONTINUED)

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Address              | Name       | Bit 7                | Bit 6          | Bit 5                     | Bit 4          | Bit 3        | Bit 2         | Bit 1         | Bit 0            | Value on<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|----------------------|----------------|---------------------------|----------------|--------------|---------------|---------------|------------------|-------------------------|--------------------|

| Bank 1               |            |                      |                |                           |                |              |               |               |                  |                         |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressin            | g this locatio | n uses conte              | ents of FSR to | address dat  | a memory (r   | not a physica | al register)     | 0000 0000               | 27, 96             |

| 81h                  | OPTION_REG | RBPU                 | INTEDG         | TOCS                      | T0SE           | PSA          | PS2           | PS1           | PS0              | 1111 1111               | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program C            | Counter (PC)   | Least Signif              | icant Byte     |              |               |               |                  | 0000 0000               | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                  | RP1            | RP0                       | TO             | PD           | Z             | DC            | C <sup>(2)</sup> | 0001 1xxx               | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect da          | ata memory a   | ddress poin               | ter            |              |               |               |                  | xxxx xxxx               | 27, 96             |

| 85h                  | TRISA      |                      | _              | PORTA Dat                 | a Direction Re | egister      |               |               |                  | 11 1111                 | 32, 96             |

| 86h                  | TRISB      | PORTB D              | ata Direction  |                           |                | •            |               |               |                  | 1111 1111               | 34, 96             |

| 87h                  | TRISC      | PORTC D              | ata Direction  | Register                  |                |              |               |               |                  | 1111 1111               | 35, 96             |

| 88h <b>(5)</b>       | TRISD      | PORTD D              | ata Direction  | Register                  |                |              |               |               |                  | 1111 1111               | 36, 96             |

| 89h <b>(5)</b>       | TRISE      | IBF                  | OBF            | IBOV                      | PSPMODE        | —            | PORTE Da      | ata Direction | Bits             | 0000 -111               | 38, 96             |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                    | —              | —                         | Write Buffer f | or the upper | 5 bits of the | Program C     | ounter           | 0 0000                  | 26, 96             |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                  | PEIE           | TMR0IE                    | INTE           | RBIE         | TMR0IF        | INTF          | RBIF             | 0000 000x               | 21, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup> | ADIE           | RCIE                      | TXIE           | SSPIE        | CCP1IE        | TMR2IE        | TMR1IE           | 0000 0000               | 22, 97             |

| 8Dh                  | PIE2       | _                    | —              | —                         | _              |              | _             | —             | CCP2IE           | 0                       | 24, 97             |

| 8Eh                  | PCON       | _                    | _              | _                         | _              | _            | _             | POR           | BOR              | dd                      | 22, 97             |

| 8Fh                  | _          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       | _                  |

| 90h                  | _          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       | _                  |

| 91h                  | —          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       | _                  |

| 92h                  | PR2        | Timer2 Mo            | odule Period   | Register                  |                |              |               |               |                  | 1111 1111               | 52, 97             |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po  | ort (l <sup>2</sup> C™ mo | de) Address F  | Register     |               |               |                  | 0000 0000               | 68, 97             |

| 94h                  | SSPSTAT    | SMP                  | CKE            | D/A                       | Р              | S            | R/W           | UA            | BF               | 0000 0000               | 60, 97             |

| 95h                  | —          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       | —                  |

| 96h                  | —          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       | _                  |

| 97h                  | —          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       | _                  |

| 98h                  | TXSTA      | CSRC                 | TX9            | TXEN                      | SYNC           |              | BRGH          | TRMT          | TX9D             | 0000 -010               | 69, 97             |

| 99h                  | SPBRG      | Baud Rate            | e Generator I  | Register                  |                |              |               |               |                  | 0000 0000               | 71, 97             |

| 9Ah                  | —          | Unimplemented        |                |                           |                |              |               |               |                  | _                       |                    |

| 9Bh                  | _          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       |                    |

| 9Ch                  | —          | Unimplemented        |                |                           |                |              |               |               |                  | _                       |                    |

| 9Dh                  | —          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       |                    |

| 9Eh                  | _          | Unimplem             | ented          |                           |                |              |               |               |                  | _                       |                    |

| 9Fh                  | ADCON1     | _                    | _              | _                         | _              | _            | PCFG2         | PCFG1         | PCFG0            | 000                     | 84, 97             |

| TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (C | CONTINUED) |

|-------------------------------------------------|------------|

|-------------------------------------------------|------------|

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

# 4.4 PORTD and TRISD Registers

This section is not applicable to the PIC16CR73 or PIC16CR76.

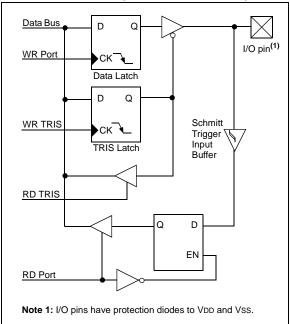

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 4-6: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Name Bit# Buffer Type |                       | Function                                           |  |  |  |

|----------|-----------------------|-----------------------|----------------------------------------------------|--|--|--|

| RD0/PSP0 | bit 0                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 0 |  |  |  |

| RD1/PSP1 | bit 1                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 1 |  |  |  |

| RD2/PSP2 | bit 2                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 2 |  |  |  |

| RD3/PSP3 | bit 3                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 3 |  |  |  |

| RD4/PSP4 | bit 4                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 4 |  |  |  |

| RD5/PSP5 | bit 5                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 5 |  |  |  |

| RD6/PSP6 | bit 6                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 6 |  |  |  |

| RD7/PSP7 | bit 7                 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit   |  |  |  |

### TABLE 4-7:PORTD FUNCTIONS

**Legend:** ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-8: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address | Name                                | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                                         | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------|-------|-------|-------|---------|-------|-----------------------------------------------|-------|-------|-------------------------|---------------------------------|

| 08h     | PORTD                               | RD7   | RD6   | RD5   | RD4     | RD3   | RD2                                           | RD1   | RD0   | xxxx xxxx               | uuuu uuuu                       |

| 88h     | TRISD PORTD Data Direction Register |       |       |       |         |       |                                               |       |       | 1111 1111               | 1111 1111                       |

| 89h     | TRISE                               | IBF   | OBF   | IBOV  | PSPMODE | —     | <ul> <li>PORTE Data Direction bits</li> </ul> |       |       | 0000 -111               | 0000 -111                       |

| Logandu |                                     |       |       |       |         |       |                                               |       |       |                         |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

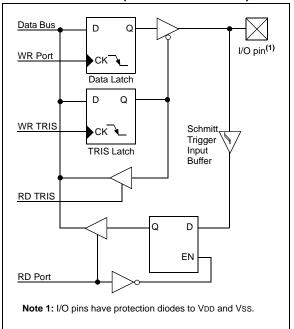

### 4.5 PORTE and TRISE Register

This section is not applicable to the PIC16CR73 or PIC16CR76.

PORTE has three pins, RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register, which also controls the Parallel Slave Port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

### FIGURE 4-7:

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

# PIC16CR7X

NOTES:

| U-0           | U-0                                     | R/W-0            | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |

|---------------|-----------------------------------------|------------------|-------|------------------------------------|--------|--------------------|--------|--|--|--|

| _             | —                                       | CCPxX            | CCPxY | CCPxM3                             | CCPxM2 | CCPxM1             | CCPxM0 |  |  |  |

| bit 7         |                                         |                  |       |                                    |        |                    | bit 0  |  |  |  |

|               |                                         |                  |       |                                    |        |                    |        |  |  |  |

| Legend:       |                                         |                  |       |                                    |        |                    |        |  |  |  |

| R = Readable  | e bit                                   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |

| -n = Value at | POR                                     | '1' = Bit is set |       | '0' = Bit is cle                   | ared   | x = Bit is unknown |        |  |  |  |

|               |                                         |                  |       |                                    |        |                    |        |  |  |  |

| bit 7-6       | Unimplemen                              | ted: Read as '   | 0'    |                                    |        |                    |        |  |  |  |

| bit 5-4       | CCPxX:CCPxY: PWM Least Significant bits |                  |       |                                    |        |                    |        |  |  |  |

|               | Capture mode                            | <u>ə:</u>        |       |                                    |        |                    |        |  |  |  |

#### REGISTER 8-1: CCP1CON/CCP2CON: (ADDRESS 17h/1Dh)

| bit 5-4 | CCPxX:CCPxY: PWM Least Significant bits                                                |

|---------|----------------------------------------------------------------------------------------|

|         | Capture mode:                                                                          |

|         | Unused                                                                                 |

|         | Compare mode:                                                                          |

|         | Unused                                                                                 |

|         | PWM mode:                                                                              |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Mode Select bits                                                   |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                               |

|         | 0100 = Capture mode, every falling edge                                                |

|         | 0101 = Capture mode, every rising edge                                                 |

|         | 0110 = Capture mode, every 4th rising edge                                             |

|         | And a Construction of the second ACthe size in a data                                  |

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, set output on match (CCPxIF bit is set)

- 1001 = Compare mode, clear output on match (CCPxIF bit is set)

- 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)

- 1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected); CCP1 clears Timer1; CCP2 clears Timer1 and starts an A/D conversion (if A/D module is enabled)

- 11xx = PWM mode

### 9.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 9-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| TABLE 9-2: | DATA TRANSFER RECEIVED BYTE ACTIONS |

|------------|-------------------------------------|

|            |                                     |

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|---------------------------------------------|-------|--------------------|--------------|----------------------------------------|--|--|

| BF                                          | SSPOV |                    | Pulse        | if enabled)                            |  |  |

| 0                                           | 0     | Yes                | Yes          | Yes                                    |  |  |

| 1                                           | 0     | No                 | No           | Yes                                    |  |  |

| 1                                           | 1     | No                 | No           | Yes                                    |  |  |

| 0                                           | 1     | No                 | No           | Yes                                    |  |  |

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 9.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge ( $\overrightarrow{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

|              |         | Fosc = 20 M | Hz                          |         | Fosc = 16 MHz |                             |         | Fosc = 10 MHz |                             |  |

|--------------|---------|-------------|-----------------------------|---------|---------------|-----------------------------|---------|---------------|-----------------------------|--|

| BAUD<br>RATE | BAUD    | %<br>ERROR  | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 1200         | 1,221   | 1.73%       | 255                         | 1,202   | 0.16%         | 207                         | 1,202   | 0.16%         | 129                         |  |

| 2400         | 2,404   | 0.16%       | 129                         | 2,404   | 0.16%         | 103                         | 2,404   | 0.16%         | 64                          |  |

| 9600         | 9,470   | -1.36%      | 32                          | 9,615   | 0.16%         | 25                          | 9,766   | 1.73%         | 15                          |  |

| 19,200       | 19,531  | 1.73%       | 15                          | 19,231  | 0.16%         | 12                          | 19,531  | 1.73%         | 7                           |  |

| 38,400       | 39,063  | 1.73%       | 7                           | 35,714  | -6.99%        | 6                           | 39,063  | 1.73%         | 3                           |  |

| 57,600       | 62,500  | 8.51%       | 4                           | 62,500  | 8.51%         | 3                           | 52,083  | -9.58%        | 2                           |  |

| 76,800       | 78,125  | 1.73%       | 3                           | 83,333  | 8.51%         | 2                           | 78,125  | 1.73%         | 1                           |  |

| 96,000       | 104,167 | 8.51%       | 2                           | 83,333  | -13.19%       | 2                           | 78,125  | -18.62%       | 1                           |  |

| 115,200      | 104,167 | -9.58%      | 2                           | 125,000 | 8.51%         | 1                           | 78,125  | -32.18%       | 1                           |  |

| 250,000      | 312,500 | 25.00%      | 0                           | 250,000 | 0.00%         | 0                           | 156,250 | -37.50%       | 0                           |  |

### TABLE 10-3:BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

|              |        | Fosc = 4 MHz |                             |        | Fosc = 3.6864 MHz |                             |        | Fosc = 3.579545 MHz |                             |  |

|--------------|--------|--------------|-----------------------------|--------|-------------------|-----------------------------|--------|---------------------|-----------------------------|--|

| BAUD<br>RATE | BAUD   | %<br>ERROR   | SPBRG<br>VALUE<br>(DECIMAL) | BAUD   | %<br>ERROR        | SPBRG<br>VALUE<br>(DECIMAL) | BAUD   | %<br>ERROR          | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 300          | 300    | 0.16%        | 207                         | 300    | 0.00%             | 191                         | 301    | 0.23%               | 185                         |  |

| 1200         | 1,202  | 0.16%        | 51                          | 1,200  | 0.00%             | 47                          | 1,190  | -0.83%              | 46                          |  |

| 2400         | 2,404  | 0.16%        | 25                          | 2,400  | 0.00%             | 23                          | 2,432  | 1.32%               | 22                          |  |

| 9600         | 8,929  | -6.99%       | 6                           | 9,600  | 0.00%             | 5                           | 9,322  | -2.90%              | 5                           |  |

| 19,200       | 20,833 | 8.51%        | 2                           | 19,200 | 0.00%             | 2                           | 18,643 | -2.90%              | 2                           |  |

| 38,400       | 31,250 | -18.62%      | 1                           | 28,800 | -25.00%           | 1                           | 27,965 | -27.17%             | 1                           |  |

| 57,600       | 62,500 | 8.51%        | 0                           | 57,600 | 0.00%             | 0                           | 55,930 | -2.90%              | 0                           |  |

| 76,800       | 62,500 | -18.62%      | 0                           | —      | _                 | _                           | —      | _                   | _                           |  |

# TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

|              |         | Fosc = 20 MHz |                             |         | Fosc = 16 MHz |                             |         | Fosc = 10 MHz |                             |  |

|--------------|---------|---------------|-----------------------------|---------|---------------|-----------------------------|---------|---------------|-----------------------------|--|

| BAUD<br>RATE | BAUD    | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR    | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 2400         | _       | _             | _                           | _       | _             | _                           | 2,441   | 1.73%         | 255                         |  |

| 9600         | 9,615   | 0.16%         | 129                         | 9,615   | 0.16%         | 103                         | 9,615   | 0.16%         | 64                          |  |

| 19,200       | 19,231  | 0.16%         | 64                          | 19,231  | 0.16%         | 51                          | 18,939  | -1.36%        | 32                          |  |

| 38,400       | 37,879  | -1.36%        | 32                          | 38,462  | 0.16%         | 25                          | 39,063  | 1.73%         | 15                          |  |

| 57,600       | 56,818  | -1.36%        | 21                          | 58,824  | 2.12%         | 16                          | 56,818  | -1.36%        | 10                          |  |

| 76,800       | 78,125  | 1.73%         | 15                          | 76,923  | 0.16%         | 12                          | 78,125  | 1.73%         | 7                           |  |

| 96,000       | 96,154  | 0.16%         | 12                          | 100,000 | 4.17%         | 9                           | 89,286  | -6.99%        | 6                           |  |

| 115,200      | 113,636 | -1.36%        | 10                          | 111,111 | -3.55%        | 8                           | 125,000 | 8.51%         | 4                           |  |

| 250,000      | 250,000 | 0.00%         | 4                           | 250,000 | 0.00%         | 3                           | 208,333 | -16.67%       | 2                           |  |

| 300,000      | 312,500 | 4.17%         | 3                           | 333,333 | 11.11%        | 2                           | 312,500 | 4.17%         | 1                           |  |

| DAUD                |         | Fosc = 4 MHz |                             |         | Fosc = 3.6864 MHz |                             |         | Fosc = 3.579545 MHz |                             |  |

|---------------------|---------|--------------|-----------------------------|---------|-------------------|-----------------------------|---------|---------------------|-----------------------------|--|

| BAUD<br>RATE<br>(K) | BAUD    | %<br>ERROR   | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR        | SPBRG<br>VALUE<br>(DECIMAL) | BAUD    | %<br>ERROR          | SPBRG<br>VALUE<br>(DECIMAL) |  |

| 1200                | 1,202   | 0.16%        | 207                         | 1,200   | 0.00%             | 191                         | 1,203   | 0.23%               | 185                         |  |

| 2400                | 2,404   | 0.16%        | 103                         | 2,400   | 0.00%             | 95                          | 2,406   | 0.23%               | 92                          |  |

| 9600                | 9,615   | 0.16%        | 25                          | 9,600   | 0.00%             | 23                          | 9,727   | 1.32%               | 22                          |  |

| 19,200              | 19,231  | 0.16%        | 12                          | 19,200  | 0.00%             | 11                          | 18,643  | -2.90%              | 11                          |  |

| 38,400              | 35,714  | -6.99%       | 6                           | 38,400  | 0.00%             | 5                           | 37,287  | -2.90%              | 5                           |  |

| 57,600              | 62,500  | 8.51%        | 3                           | 57,600  | 0.00%             | 3                           | 55,930  | -2.90%              | 3                           |  |

| 76,800              | 83,333  | 8.51%        | 2                           | 76,800  | 0.00%             | 2                           | 74,574  | -2.90%              | 2                           |  |