Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ROM                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr73-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Device Overview                                                 | 5     |

|-----------------------------------------------------------------|-------|

| Aemory Organization                                             | 13    |

| Reading Program Memory                                          |       |

| O Ports                                                         | 31    |

| imer0 Module                                                    | 43    |

| imer1 Module                                                    | 47    |

| imer2 Module                                                    | 51    |

| Capture/Compare/PWM Modules                                     | 53    |

| Synchronous Serial Port (SSP) Module                            | 59    |

| Iniversal Synchronous Asynchronous Receiver Transmitter (USART) | 69    |

| nalog-to-Digital Converter (A/D) Module                         | 83    |

| Special Features of the CPU                                     | 89    |

| nstruction Set Summary                                          | . 105 |

| Development Support                                             | . 113 |

| Electrical Characteristics                                      | . 117 |

| OC and AC Characteristics Graphs and Tables                     | . 139 |

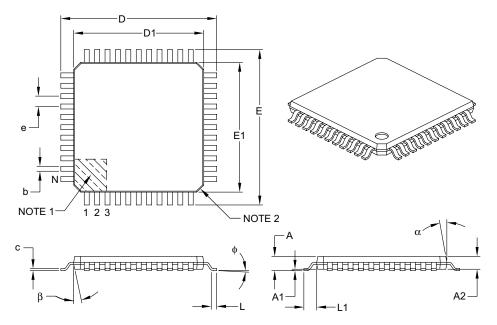

| Packaging Information                                           | . 149 |

| Appendix A: Revision History                                    |       |

| Appendix B: Device Differences                                  | . 159 |

| Appendix C: Conversion Considerations                           |       |

| he Microchip Web Site                                           | . 167 |

| Customer Change Notification Service                            |       |

| Customer Support                                                | . 167 |

| Reader Response                                                 | . 168 |

| Product Identification System                                   | . 169 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## REGISTER 2-2: OPTION\_REG: (ADDRESS 81h, 181h)

| R/W-1 | R/W-1            | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|------------------|-------|-------|-------|-------|-------|-------|

| RBPU  | RBPU INTEDG TOCS |       | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |                  |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | RBPU: PORTB Pull-up Enable bit                                                                                        |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | 1 = PORTB pull-ups are disabled                                                                                       |  |  |  |  |  |  |

|         | 0 = PORTB pull-ups are enabled by individual PORT latch values                                                        |  |  |  |  |  |  |

| bit 6   | INTEDG: Interrupt Edge Select bit                                                                                     |  |  |  |  |  |  |

|         | <ul> <li>1 = Interrupt on rising edge of RB0/INT pin</li> <li>0 = Interrupt on falling edge of RB0/INT pin</li> </ul> |  |  |  |  |  |  |

| bit 5   | TOCS: TMR0 Clock Source Select bit                                                                                    |  |  |  |  |  |  |

|         | 1 = Transition on RA4/T0CKI pin                                                                                       |  |  |  |  |  |  |

|         | 0 = Internal instruction cycle clock (CLKOUT)                                                                         |  |  |  |  |  |  |

| bit 4   | T0SE: TMR0 Source Edge Select bit                                                                                     |  |  |  |  |  |  |

|         | 1 = Increment on high-to-low transition on RA4/T0CKI pin                                                              |  |  |  |  |  |  |

|         | 0 = Increment on low-to-high transition on RA4/T0CKI pin                                                              |  |  |  |  |  |  |

| bit 3   | PSA: Prescaler Assignment bit                                                                                         |  |  |  |  |  |  |

|         | 1 = Prescaler is assigned to the WDT                                                                                  |  |  |  |  |  |  |

|         | 0 = Prescaler is assigned to the Timer0 module                                                                        |  |  |  |  |  |  |

| bit 2-0 | PS2:PS0: Prescaler Rate Select bits                                                                                   |  |  |  |  |  |  |

|         | Bit Value TMR0 Rate WDT Rate                                                                                          |  |  |  |  |  |  |

|         |                                                                                                                       |  |  |  |  |  |  |

| 000 | 1:2     | 1:1     |

|-----|---------|---------|

| 001 | 1:4     | 1:2     |

| 010 | 1:8     | 1:4     |

| 011 | 1:16    | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1 : 128 | 1:64    |

| 111 | 1 : 256 | 1 : 128 |

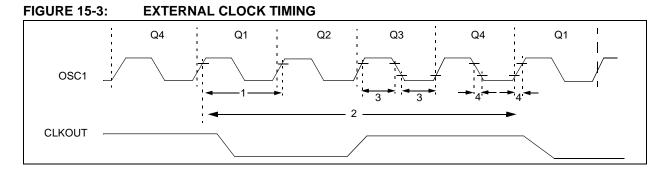

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and

#### **REGISTER 5-1: OPTION REG:**

bit 7

bit 7

bit 6

bit 5

bit 4

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU TOCS T0SE PS2 INTEDG PSA PS1 PS0 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown RBPU: PORTB Pull-up Enable bit (see Section 2.2.2.2 "OPTION\_REG Register") INTEDG: Interrupt Edge Select bit (see Section 2.2.2. "OPTION\_REG Register") TOCS: TMR0 Clock Source Select bit 1 = Transition on TOCKI pin 0 = Internal instruction cycle clock (CLKOUT) TOSE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

- bit 3 PSA: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

- bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1 : 256   | 1 : 128  |

|           |           |          |

Note: To avoid an unintended device Reset, the instruction sequences shown in Example 5-1 and Example 5-2 must be executed when changing the prescaler assignment between Timer0 and the WDT. This sequence must be followed even if the WDT is disabled.

Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

# PIC16CR7X

NOTES:

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 and CCP2 special event triggers.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type   | Frequency     | Capacitors Used:                                                                         |       |  |  |

|------------|---------------|------------------------------------------------------------------------------------------|-------|--|--|

| Osc Type   | Frequency     | cy         OSC1         OSC2           47 pF         47 pF           33 pF         33 pF | OSC2  |  |  |

| LP         | 32 kHz        | 47 pF                                                                                    | 47 pF |  |  |

|            | 100 kHz 33 pF | 33 pF                                                                                    | 33 pF |  |  |

|            | 200 kHz       | 15 pF                                                                                    | 15 pF |  |  |

| <b>A 1</b> |               |                                                                                          |       |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

| e notes (below) table for additional information. |

|---------------------------------------------------|

|---------------------------------------------------|

| Commonly Used Crystals:          |                                                                                                          |  |  |  |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 32.768 kHz Epson C-001R32.768K-A |                                                                                                          |  |  |  |  |  |  |

| 100 kHz                          | Epson C-2 100.00 KC-P                                                                                    |  |  |  |  |  |  |

| 200 kHz                          | STD XTL 200.000 kHz                                                                                      |  |  |  |  |  |  |

| 0                                | e 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time. |  |  |  |  |  |  |

| c<br>tł<br>a                     | · · · · · · · · · · · · · · · · · · ·                                                                    |  |  |  |  |  |  |

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name                                                                                 | Bit 7                                                                      | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|---------|---------|---------|--------|-----------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON                                                                               | GIE                                                                        | PEIE  | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF      | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch                   | PIR1                                                                                 | PSPIF <sup>(1)</sup>                                                       | ADIF  | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000               | 0000 0000                       |

| 8Ch                   | PIE1                                                                                 | PSPIE <sup>(1)</sup>                                                       | ADIE  | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000               | 0000 0000                       |

| 0Eh                   | Eh TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                                                            |       |         |         |         |        | xxxx xxxx | uuuu uuuu |                         |                                 |

| 0Fh                   | TMR1H                                                                                | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |       |         |         |         |        | xxxx xxxx | uuuu uuuu |                         |                                 |

| 10h                   | T1CON                                                                                | —                                                                          | _     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS    | TMR10N    | 00 0000                 | uu uuuu                         |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

|                     |                                                    |                  | •            |                  |                  |                 |         |

|---------------------|----------------------------------------------------|------------------|--------------|------------------|------------------|-----------------|---------|

| U-0                 | R/W-0                                              | R/W-0            | R/W-0        | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| —                   | TOUTPS3                                            | TOUTPS2          | TOUTPS1      | TOUTPS0          | TMR2ON           | T2CKPS1         | T2CKPS0 |

| bit 7               |                                                    |                  |              |                  |                  |                 | bit 0   |

|                     |                                                    |                  |              |                  |                  |                 |         |

| Legend:             |                                                    |                  |              |                  |                  |                 |         |

| R = Readable        | e bit                                              | W = Writable     | bit          | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at       | POR                                                | '1' = Bit is set |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                     |                                                    |                  |              |                  |                  |                 |         |

| bit 7               | Unimplemen                                         | ted: Read as '   | 0'           |                  |                  |                 |         |

| bit 6-3             | TOUTPS3:TO                                         | DUTPS0: Timer    | 2 Output Pos | tscale Select b  | its              |                 |         |

|                     | 0000 = 1:1 P                                       | ostscale         |              |                  |                  |                 |         |

|                     | 0001 = 1:2 P                                       |                  |              |                  |                  |                 |         |

|                     | 0010 = 1:3 P                                       | ostscale         |              |                  |                  |                 |         |

|                     | •                                                  |                  |              |                  |                  |                 |         |

|                     | •                                                  |                  |              |                  |                  |                 |         |

|                     | 1111 <b>= 1:16</b>                                 | Postscale        |              |                  |                  |                 |         |

| bit 2               | TMR2ON: Tir                                        | ner2 On bit      |              |                  |                  |                 |         |

| 1 = Timer2 is on    |                                                    |                  |              |                  |                  |                 |         |

|                     | 0 = Timer2 is                                      | off              |              |                  |                  |                 |         |

| bit 1-0             | T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits |                  |              |                  |                  |                 |         |

|                     | 00 = Prescale                                      |                  |              |                  |                  |                 |         |

| 01 = Prescaler is 4 |                                                    |                  |              |                  |                  |                 |         |

|                     | 1x = Prescale                                      | er is 16         |              |                  |                  |                 |         |

## REGISTER 7-1: T2CON: TIMER2 CONTROL (ADDRESS 12h)

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|--------|------------------------|------------------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                    | PEIE                   | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>   | ADIF                   | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>   | ADIE                   | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000               | 0000 0000                       |

| 11h                    | TMR2   | Timer2 Mc              | Timer2 Module Register |         |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h                    | T2CON  | _                      | TOUTPS3                | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h                    | PR2    | Timer2 Period Register |                        |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

**Note** 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

#### 8.5.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 8-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                | Bit 6                                | Bit 5      | Bit 4      | Bit 3   | Bit 2  | Bit 1   | Bit 0   | PC   | e on<br>)R,<br>)R | all o | e on<br>other<br>sets |

|-----------------------|---------|----------------------|--------------------------------------|------------|------------|---------|--------|---------|---------|------|-------------------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                 | TMR0IE     | INTE       | RBIE    | TMR0IF | INTF    | RBIF    | 0000 | 000x              | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                 | RCIF       | TXIF       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 | 0000              | 0000  | 0000                  |

| 0Dh                   | PIR2    | —                    | _                                    | _          | _          | —       | —      | _       | CCP2IF  |      | 0                 |       | 0                     |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                 | RCIE       | TXIE       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 | 0000              | 0000  | 0000                  |

| 8Dh                   | PIE2    | —                    | _                                    | _          | _          | —       | —      | _       | CCP2IE  |      | 0                 |       | 0                     |

| 87h                   | TRISC   | PORTC D              | Data Directi                         | on Registe |            |         |        |         |         | 1111 | 1111              | 1111  | 1111                  |

| 11h                   | TMR2    | Timer2 M             | Timer2 Module Register 0000 0000     |            |            |         |        |         |         |      | 0000              |       |                       |

| 92h                   | PR2     | Timer2 M             | odule Peric                          | d Register |            |         |        |         |         | 1111 | 1111              | 1111  | 1111                  |

| 12h                   | T2CON   | —                    | TOUTPS3                              | TOUTPS2    | TOUTPS1    | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000              | -000  | 0000                  |

| 15h                   | CCPR1L  | Capture/C            | Compare/P                            | WM Regist  | er 1 (LSB) |         |        |         |         | xxxx | xxxx              | uuuu  | uuuu                  |

| 16h                   | CCPR1H  | Capture/C            | Compare/P                            | WM Regist  | er 1 (MSB) |         |        |         |         | xxxx | xxxx              | uuuu  | uuuu                  |

| 17h                   | CCP1CON | —                    | _                                    | CCP1X      | CCP1Y      | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00   | 0000              | 00    | 0000                  |

| 1Bh                   | CCPR2L  | Capture/C            | Capture/Compare/PWM Register 2 (LSB) |            |            |         |        |         |         | uuuu | uuuu              |       |                       |

| 1Ch                   | CCPR2H  | Capture/C            | Capture/Compare/PWM Register 2 (MSB) |            |            |         |        |         |         |      |                   |       |                       |

| 1Dh                   | CCP2CON | —                    | —                                    | CCP2X      | CCP2Y      | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00   | 0000              | 00    | 0000                  |

$\label{eq:logend: Legend: Legend: u = unchanged, - = unimplemented, read as `0'. Shaded cells are not used by PWM and Timer2.$

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

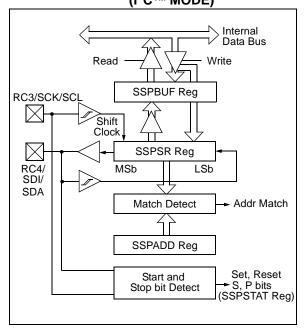

## 9.3 SSP I<sup>2</sup>C<sup>™</sup> Operation

The SSP module in  $l^2C$  mode fully implements all slave functions except general call support, and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Start and Stop bit interrupts enabled to support Firmware Master mode, Slave is Idle

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

## 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The Buffer Full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

| FIGURE 9-6:       | I <sup>∠</sup> C <sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | ing Address RW=0 Receiving Data ACK Receiving Data ACK<br>A4\A3\A2\A1\ ACK/D7\D6\D5\D4\D3\D2\D1\D0\ D7\D6\D5\D4\D3\D2\D1\D0\ 1 1 1<br>4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_9\_1\_2\_3\_4\_5\_6\_7\_8\_3\_3\_3\_3\_3\_3\_3\_3\_3\_3\_3\_3\_3\ |

| SSPOV (SSPCON<6>) | Bit SSPOV is set because the SSPBUF register is still full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

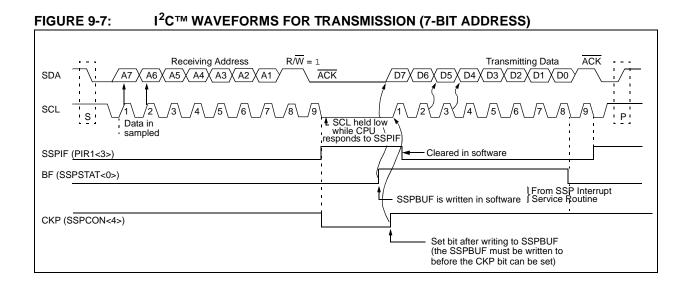

#### 9.3.1.3 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the masterreceiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/ SCK/SCL should be enabled by setting bit CKP.

| Register   |    | Dev | ices |    | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|----|-----|------|----|------------------------------------|--------------------------|---------------------------------|

| W          | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| INDF       | 73 | 74  | 76   | 77 | N/A                                | N/A                      | N/A                             |

| TMR0       | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL        | 73 | 74  | 76   | 77 | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS     | 73 | 74  | 76   | 77 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR        | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA      | 73 | 74  | 76   | 77 | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTC      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTD      | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTE      | 73 | 74  | 76   | 77 | xxx                                | uuu                      | uuu                             |

| PCLATH     | 73 | 74  | 76   | 77 | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON     | 73 | 74  | 76   | 77 | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1       | 73 | 74  | 76   | 77 | r000 0000                          | r000 0000                | ruuu uuuu <b>(1)</b>            |

|            | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |

| PIR2       | 73 | 74  | 76   | 77 | 0                                  | 0                        | u(1)                            |

| TMR1L      | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H      | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON      | 73 | 74  | 76   | 77 | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2       | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON      | 73 | 74  | 76   | 77 | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON     | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON    | 73 | 74  | 76   | 77 | 00 0000                            | 00 0000                  | uu uuuu                         |

| RCSTA      | 73 | 74  | 76   | 77 | 0000 -00x                          | 0000 -00x                | uuuu -uuu                       |

| TXREG      | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| RCREG      | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR2L     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR2H     | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP2CON    | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADRES      | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0     | 73 | 74  | 76   | 77 | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA      | 73 | 74  | 76   | 77 | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISD      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISE      | 73 | 74  | 76   | 77 | 0000 -111                          | 0000 -111                | uuuu -uuu                       |

## TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 12-5 for Reset value for specific condition.

#### 12.11.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep, if bit INTE was set prior to going into Sleep. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 12.14 "Power-down Mode** (**Sleep**)" for details on Sleep mode.

#### 12.11.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>). (Section 5.0 "Timer0 Module")

#### 12.11.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<3>), see Section 4.2 "PORTB and the TRISB Register".

## 12.12 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, PCLATH and STATUS registers). This will have to be implemented in software, as shown in Example 12-1.

For the PIC16CR73/74 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 20h in bank 0, it must also be defined at A0h in bank 1.). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16CR76/77 devices, temporary holding registers W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and, therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

#### EXAMPLE 12-1: SAVING STATUS, W AND PCLATH REGISTERS IN RAM

|   | MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|---|--------|----------------|---------------------------------------------------------|

|   | SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

|   | CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

|   | MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

|   | MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

|   | MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

|   | CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

|   | :      |                |                                                         |

|   | :(ISR) |                | ;Insert user code here                                  |

|   | :      |                |                                                         |

|   | MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

|   | MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

|   | SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|   |        |                | ;(sets bank to original state)                          |

|   | MOVWF  | STATUS         | ;Move W into STATUS register                            |

|   | SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

|   | SWAPF  | W_TEMP,W       | ;Swap W_TEMP into W                                     |

| 1 |        |                |                                                         |

## 13.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                      |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                            |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                         |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is 1, the result is stored back in<br>register 'f'. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TcY instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                   |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                         |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                         |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                     |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                        |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded and a NOP is executed instead, making this a 2TcY instruction. |  |  |  |  |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                        |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |

## SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                           |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                        |

| Status Affected: | TO, PD                                                                                                                                                                                                                                         |

| Description:     | The power-down Status bit $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                            |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                          |  |  |  |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |

| Operation:       | $k \text{ - (W)} \to (W)$                                                                                                    |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                           |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                    |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

## 14.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 14.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and the dsPIC30, dsPIC33 and PIC24 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 14.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## 14.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 14.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

## 14.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

## 14.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.