Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ROM                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr73-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Address              | Name    | Bit 7                                | Bit 6                        | Bit 5         | Bit 4           | Bit 3           | Bit 2         | Bit 1         | Bit 0            | Value on<br>POR,<br>BOR | Details<br>on page |

|----------------------|---------|--------------------------------------|------------------------------|---------------|-----------------|-----------------|---------------|---------------|------------------|-------------------------|--------------------|

| Bank 0               |         |                                      |                              |               |                 |                 |               |               |                  |                         |                    |

| 00h <sup>(4)</sup>   | INDF    | Addressing                           | g this locatio               | n uses conte  | ents of FSR to  | address dat     | a memory (r   | not a physica | al register)     | 0000 0000               | 27, 96             |

| 01h                  | TMR0    | Timer0 Mc                            | dule Registe                 | er            |                 |                 |               |               |                  | XXXX XXXX               | 45, 96             |

| 02h <sup>(4)</sup>   | PCL     | Program C                            | Counter (PC)                 | Least Signif  | icant Byte      |                 |               |               |                  | 0000 0000               | 26, 96             |

| 03h <sup>(4)</sup>   | STATUS  | IRP                                  | RP1                          | RP0           | TO              | PD              | Z             | DC            | C <sup>(2)</sup> | 0001 1xxx               | 19, 96             |

| 04h <sup>(4)</sup>   | FSR     | Indirect Da                          | ata Memory                   | Address Poir  | nter            |                 |               |               |                  | xxxx xxxx               | 27, 96             |

| 05h                  | PORTA   |                                      | _                            | PORTA Dat     | a Latch when    | written: POF    | RTA pins wh   | en read       |                  | 0x 0000                 | 32, 96             |

| 06h                  | PORTB   | PORTB D                              | ata Latch wh                 | en written: P | ORTB pins w     | /hen read       |               |               |                  | xxxx xxxx               | 34, 96             |

| 07h                  | PORTC   | PORTC D                              | ata Latch wh                 | en written: P | ORTC pins v     | vhen read       |               |               |                  | XXXX XXXX               | 35, 96             |

| 08h <b>(5)</b>       | PORTD   | PORTD D                              | ata Latch wh                 | en written: F | ORTD pins v     | vhen read       |               |               |                  | xxxx xxxx               | 36, 96             |

| 09h <b>(5)</b>       | PORTE   | _                                    | _                            | _             |                 | _               | RE2           | RE1           | RE0              | xxx                     | 39, 96             |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                                    |                              | _             | Write Buffer    | for the upper   | 5 bits of the | Program C     | ounter           | 0 0000                  | 26, 96             |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                                  | PEIE                         | TMR0IE        | INTE            | RBIE            | <b>TMR0IF</b> | INTF          | RBIF             | 0000 000x               | 21, 96             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup>                 | ADIF                         | RCIF          | TXIF            | SSPIF           | CCP1IF        | TMR2IF        | TMR1IF           | 0000 0000               | 23, 96             |

| 0Dh                  | PIR2    | _                                    |                              | _             | _               | _               | _             | _             | CCP2IF           | 0                       | 24, 96             |

| 0Eh                  | TMR1L   | Holding Re                           | egister for th               | e Least Sign  | ificant Byte of | f the 16-bit TM | MR1 Registe   | er            |                  | xxxx xxxx               | 50, 96             |

| 0Fh                  | TMR1H   | Holding Re                           | egister for the              | e Most Signi  | ficant Byte of  | the 16-bit TN   | IR1 Registe   | r             |                  | XXXX XXXX               | 50, 96             |

| 10h                  | T1CON   | _                                    |                              | T1CKPS1       | T1CKPS0         | T1OSCEN         | T1SYNC        | TMR1CS        | TMR10N           | 00 0000                 | 47, 96             |

| 11h                  | TMR2    | Timer2 Mc                            | dule Registe                 | er            |                 |                 |               |               |                  | 0000 0000               | 52, 96             |

| 12h                  | T2CON   |                                      | TOUTPS3                      | TOUTPS2       | TOUTPS1         | TOUTPS0         | TMR2ON        | T2CKPS1       | T2CKPS0          | -000 0000               | 52, 96             |

| 13h                  | SSPBUF  | Synchrono                            | ous Serial Po                | ort Receive B | uffer/Transmi   | it Register     |               |               |                  | xxxx xxxx               | 64, 68, 96         |

| 14h                  | SSPCON  | WCOL                                 | SSPOV                        | SSPEN         | CKP             | SSPM3           | SSPM2         | SSPM1         | SSPM0            | 0000 0000               | 61, 96             |

| 15h                  | CCPR1L  | Capture/C                            | ompare/PWI                   | M Register 1  | (LSB)           |                 |               |               |                  | xxxx xxxx               | 56, 96             |

| 16h                  | CCPR1H  | Capture/C                            | ompare/PWI                   | M Register 1  | (MSB)           | T               | 1             | r             |                  | xxxx xxxx               | 56, 96             |

| 17h                  | CCP1CON |                                      | _                            | CCP1X         | CCP1Y           | CCP1M3          | CCP1M2        | CCP1M1        | CCP1M0           | 00 0000                 | 54, 96             |

| 18h                  | RCSTA   | SPEN                                 | RX9                          | SREN          | CREN            | —               | FERR          | OERR          | RX9D             | 0000 -00x               | 70, 96             |

| 19h                  | TXREG   | USART Tr                             | USART Transmit Data Register |               |                 |                 |               |               |                  |                         | 75, 96             |

| 1Ah                  | RCREG   | USART Receive Data Register          |                              |               |                 |                 |               |               |                  | 0000 0000               | 77, 96             |

| 1Bh                  | CCPR2L  | Capture/Compare/PWM Register 2 (LSB) |                              |               |                 |                 |               |               |                  | xxxx xxxx               | 58, 96             |

| 1Ch                  | CCPR2H  | Capture/Compare/PWM Register 2 (MSB) |                              |               |                 |                 |               |               |                  | xxxx xxxx               | 58, 96             |

| 1Dh                  | CCP2CON | —                                    | _                            | CCP2X         | CCP2Y           | CCP2M3          | CCP2M2        | CCP2M1        | CCP2M0           | 00 0000                 | 54, 96             |

| 1Eh                  | ADRES   | A/D Resul                            | t Register By                | /te           | T               | 1               | 1             |               | 1                | xxxx xxxx               | 88, 96             |

| 1Fh                  | ADCON0  | ADCS1                                | ADCS0                        | CHS2          | CHS1            | CHS0            | GO/<br>DONE   | —             | ADON             | 0000 00-0               | 83, 96             |

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

**6:** This bit always reads as a '1'.

# 2.2.2.8 PCON Register

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

| Note: | BOR is unknown on POR. It must be set by        |

|-------|-------------------------------------------------|

|       | the user and checked on subsequent              |

|       | Resets to see if BOR is clear, indicating a     |

|       | brown-out has occurred. The BOR Status          |

|       | bit is not predictable if the brown-out circuit |

|       | is disabled (by clearing the BOREN bit in       |

|       | the Configuration Word).                        |

# REGISTER 2-8: PCON: (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                              |

|---------|-----------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                          |

|         | 1 = No Power-on Reset occurred                                                          |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)   |

| bit 0   | BOR: Brown-out Reset Status bit                                                         |

|         | 1 = No Brown-out Reset occurred                                                         |

|         | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) |

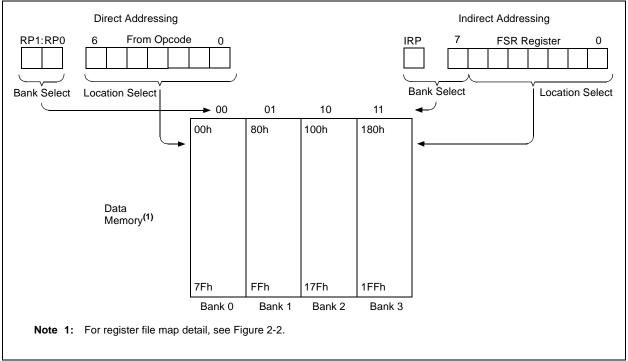

# 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register (FSR). Reading the INDF register itself indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-2.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

| EXAM   | PLE 2-2: | INC   | INDIRECT ADDRESSING  |  |  |  |  |

|--------|----------|-------|----------------------|--|--|--|--|

|        | MOVLW    | 0x20  | ;initialize pointer  |  |  |  |  |

|        | MOVWF    | FSR   | ;to RAM              |  |  |  |  |

| NEXT   | CLRF     | INDF  | clear INDF register; |  |  |  |  |

|        | INCF     | FSR,F | ;inc pointer         |  |  |  |  |

|        | BTFSS    | FSR,4 | ;all done?           |  |  |  |  |

|        | GOTO     | NEXT  | ;no clear next       |  |  |  |  |

| CONTIN | IUE      |       |                      |  |  |  |  |

| :      |          |       | ;yes continue        |  |  |  |  |

|        |          |       |                      |  |  |  |  |

# FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

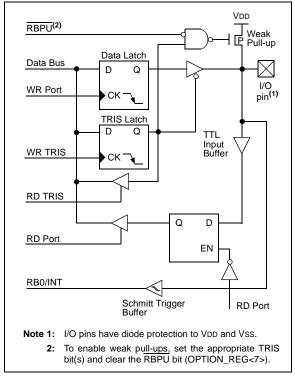

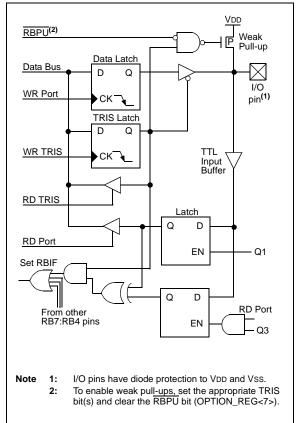

# 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impendance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "*Implementing Wake-up on Key Stroke*" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in **Section 12.11.1 "INT Interrupt"**.

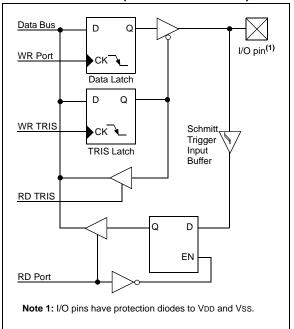

#### BLOCK DIAGRAM OF RB7:RB4 PINS

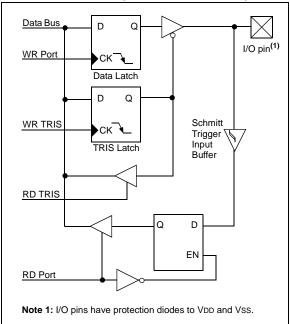

# 4.4 PORTD and TRISD Registers

This section is not applicable to the PIC16CR73 or PIC16CR76.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 4-6: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit#  | Buffer Type           | Function                                           |  |

|----------|-------|-----------------------|----------------------------------------------------|--|

| RD0/PSP0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 0 |  |

| RD1/PSP1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 1 |  |

| RD2/PSP2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 2 |  |

| RD3/PSP3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 3 |  |

| RD4/PSP4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 4 |  |

| RD5/PSP5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 5 |  |

| RD6/PSP6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 6 |  |

| RD7/PSP7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit   |  |

#### TABLE 4-7:PORTD FUNCTIONS

**Legend:** ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-8: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit 7                                             | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1        | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------|-------|---------|-------|----------|--------------|---------|-------------------------|---------------------------------|

| 08h     | PORTD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RD7                                               | RD6   | RD5   | RD4     | RD3   | RD2      | RD1          | RD0     | xxxx xxxx               | uuuu uuuu                       |

| 88h     | TRISD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PORTD Data Direction Register 1111 1111 1111 1111 |       |       |         |       |          |              |         |                         |                                 |

| 89h     | TRISE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IBF                                               | OBF   | IBOV  | PSPMODE | —     | PORTE Da | ata Directio | on bits | 0000 -111               | 0000 -111                       |

| Logondu | x = up (pown, y = up (pop q d)) = up (pop q d) = d (pop q d) (po |                                                   |       |       |         |       |          |              |         |                         |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

### 4.5 PORTE and TRISE Register

This section is not applicable to the PIC16CR73 or PIC16CR76.

PORTE has three pins, RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 4-1 shows the TRISE register, which also controls the Parallel Slave Port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

#### FIGURE 4-7:

#### PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| R-0        | R-0          | R/W-0                                  | R/W-0          | U-0              | R/W-1            | R/W-1           | R/W-1 |

|------------|--------------|----------------------------------------|----------------|------------------|------------------|-----------------|-------|

| IBF        | OBF          | IBOV                                   | PSPMODE        | —                | Bit 2            | Bit 1           | Bit 0 |

| bit 7      |              |                                        |                |                  |                  |                 | bit   |

| Legend:    |              |                                        |                |                  |                  |                 |       |

| R = Readal | ble bit      | W = Writable                           | bit            | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value | at POR       | '1' = Bit is se                        | t              | '0' = Bit is cle |                  | x = Bit is unkr | nown  |

|            |              |                                        |                |                  |                  |                 |       |

| bit 7      | Parallel SI  | <u>ave Port Status</u>                 | Control bits:  |                  |                  |                 |       |

|            | IBF: Input I | Buffer Full Status                     | s bit          |                  |                  |                 |       |

|            |              | has been receiv                        |                | ng to be read l  | by the CPU       |                 |       |

|            |              | d has been rece                        |                |                  |                  |                 |       |

| bit 6      | •            | ut Buffer Full Sta                     |                |                  |                  |                 |       |

|            |              | tput buffer still he tput buffer has b | •              | ly written word  |                  |                 |       |

| bit 5      |              | t Buffer Overflov                      |                | Microprocesso    | r mode)          |                 |       |

|            | •            | occurred when                          | •              | •                | ,                |                 |       |

|            | ,            | e cleared in soft                      | ware)          |                  |                  |                 |       |

|            |              | rflow occurred                         |                |                  |                  |                 |       |

| bit 4      |              | Parallel Slave                         |                | ect bit          |                  |                 |       |

|            |              | I Slave Port moo<br>al Purpose I/O m   |                |                  |                  |                 |       |

| bit 3      |              | ented: Read as                         |                |                  |                  |                 |       |

| bit 2      | -            | ta Direction bit                       |                |                  |                  |                 |       |

|            |              | ction Control bit f                    |                | AN7              |                  |                 |       |

|            | 1 = Input    |                                        |                |                  |                  |                 |       |

|            | 0 = Output   |                                        |                |                  |                  |                 |       |

| bit 1      | Bit 1: Direc | ction Control bit f                    | or pin RE1/WR  | AN6              |                  |                 |       |

|            | 1 = Input    |                                        |                |                  |                  |                 |       |

| L:4 0      | 0 = Output   |                                        |                | / A N I 🗖        |                  |                 |       |

| bit 0      |              | ction Control bit f                    | or pin REU/RD/ | ANS              |                  |                 |       |

|            | 1 = Input    |                                        |                |                  |                  |                 |       |

#### REGISTER 4-1: TRISE: (ADDRESS 89h)

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and

#### **REGISTER 5-1: OPTION REG:**

bit 7

bit 7

bit 6

bit 5

bit 4

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU TOCS T0SE PS2 INTEDG PSA PS1 PS0 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown RBPU: PORTB Pull-up Enable bit (see Section 2.2.2.2 "OPTION\_REG Register") INTEDG: Interrupt Edge Select bit (see Section 2.2.2. "OPTION\_REG Register") TOCS: TMR0 Clock Source Select bit 1 = Transition on TOCKI pin 0 = Internal instruction cycle clock (CLKOUT) TOSE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

- bit 3 PSA: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

- bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1 : 256   | 1 : 128  |

|           |           |          |

Note: To avoid an unintended device Reset, the instruction sequences shown in Example 5-1 and Example 5-2 must be executed when changing the prescaler assignment between Timer0 and the WDT. This sequence must be followed even if the WDT is disabled.

Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

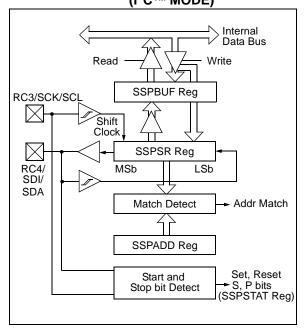

# 9.3 SSP I<sup>2</sup>C<sup>™</sup> Operation

The SSP module in  $l^2C$  mode fully implements all slave functions except general call support, and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/ SCK/SCL pin, which is the clock (SCL), and the RC4/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 9-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has five registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Start and Stop bit interrupts enabled to support Firmware Master mode, Slave is Idle

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

# 9.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The Buffer Full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

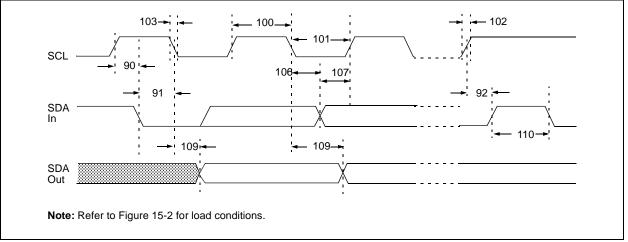

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, are shown in timing parameter #100 and parameter #101.

| U-0                                                     | U-0                                                                                                                      | U-0             | U-0                   | U-0                         | U-0   | U-0   |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------------|-------|-------|

| _                                                       | _                                                                                                                        | —               | _                     | —                           | _     |       |

| bit 13                                                  |                                                                                                                          | ·               | ·                     |                             |       | bit   |

|                                                         |                                                                                                                          |                 |                       |                             |       |       |

| R/P-1                                                   | U-0                                                                                                                      | R/P-1           | R/P-1                 | R/P-1                       | R/P-1 | R/P-1 |

| BOREN                                                   | —                                                                                                                        | CP0             | PWRTEN                | WDTEN                       | FOSC1 | FOSC0 |

| bit 6                                                   |                                                                                                                          |                 |                       |                             |       | bit   |

| Legend:                                                 |                                                                                                                          |                 |                       |                             |       |       |

| R = Readable                                            | bit                                                                                                                      | W = Writable bi | t                     | U = Unimplemented bit, read |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |                                                                                                                          | ed              | x = Bit is<br>unknown |                             |       |       |

| bit 13-7                                                | Unimplemente                                                                                                             | ed: Read as '1' |                       |                             |       |       |

| bit 6                                                   | BOREN: Brown-out Reset Enable bit<br>1 = BOR enabled<br>0 = BOR disabled                                                 |                 |                       |                             |       |       |

| bit 5                                                   | Unimplemented: Read as '1'                                                                                               |                 |                       |                             |       |       |

| bit 4                                                   | <b>CP0:</b> ROM Program Memory Code Protection bit<br>1 = Code protection off<br>0 = All memory locations code protected |                 |                       |                             |       |       |

| bit 3                                                   | <b>PWRTEN</b> : Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                       |                 |                       |                             |       |       |

| bit 2                                                   | <b>WDTEN</b> : Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                          |                 |                       |                             |       |       |

| bit 1-0                                                 | FOSC1:FOSC<br>11 = RC oscilla<br>10 = HS oscilla<br>01 = XT oscilla<br>00 = LP oscilla                                   | ator            | tion bits             |                             |       |       |

**Note 1:** The erased (unprogrammed) value of the Configuration Word is 3FFFh.

| Mnemonic,<br>Operands                  |         | Description                                    |               |       | 14-Bit   | Status |          |              |        |

|----------------------------------------|---------|------------------------------------------------|---------------|-------|----------|--------|----------|--------------|--------|

|                                        |         | Description                                    | Cycles        | MSb   |          |        | LSb      | Affected     | Notes  |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                                                |               |       |          |        |          |              |        |

| ADDWF                                  | f, d    | Add W and f                                    | 1             | 00    | 0111     | dfff   | ffff     | C,DC,Z       | 1,2    |

| ANDWF                                  | f, d    | AND W with f                                   | 1             | 00    | 0101     | dfff   | ffff     | Z            | 1,2    |

| CLRF                                   | f       | Clear f                                        | 1             | 00    | 0001     | lfff   | ffff     | Z            | 2      |

| CLRW                                   | —       | Clear W                                        | 1             | 00    | 0001     | 0xxx   | xxxx     | Z            |        |

| COMF                                   | f, d    | Complement f                                   | 1             | 00    | 1001     | dfff   | ffff     | Z            | 1,2    |

| DECF                                   | f, d    | Decrement f                                    | 1             | 00    | 0011     | dfff   | ffff     | Z            | 1,2    |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0                         | 1(2)          | 00    | 1011     | dfff   | ffff     |              | 1,2,3  |

| INCF                                   | f, d    | Increment f                                    | 1             | 00    | 1010     | dfff   | ffff     | Z            | 1,2    |

| INCFSZ                                 | f, d    | Increment f, Skip if 0                         | 1(2)          | 00    | 1111     | dfff   | ffff     |              | 1,2,3  |

| IORWF                                  | f, d    | Inclusive OR W with f                          | 1             | 00    | 0100     | dfff   | ffff     | Z            | 1,2    |

| MOVF                                   | f, d    | Move f                                         | 1             | 00    | 1000     | dfff   | ffff     | Z            | 1,2    |

| MOVWF                                  | f       | Move W to f                                    | 1             | 00    | 0000     | lfff   | ffff     |              |        |

| NOP                                    | _       | No Operation                                   | 1             | 00    | 0000     | 0xx0   | 0000     |              |        |

| RLF                                    | f, d    | Rotate Left f through Carry                    | 1             | 00    | 1101     | dfff   | ffff     | С            | 1,2    |

| RRF                                    | f, d    | Rotate Right f through Carry                   | 1             | 00    | 1100     | dfff   | ffff     | С            | 1,2    |

| SUBWF                                  | f, d    | Subtract W from f                              | 1             | 00    | 0010     | dfff   | ffff     | C,DC,Z       | 1,2    |

| SWAPF                                  | f, d    | Swap nibbles in f                              | 1             | 00    | 1110     | dfff   | ffff     |              | 1,2    |

| XORWF                                  | f, d    | Exclusive OR W with f                          | 1             | 00    | 0110     | dfff   | ffff     | Z            | 1,2    |

|                                        |         | BIT-ORIENTED FILE                              |               | RATIO | NS       |        |          |              |        |

| BCF                                    | f, b    | Bit Clear f                                    | 1             | 01    | 00bb     | bfff   | ffff     |              | 1,2    |

| BSF                                    | f, b    | Bit Set f                                      | 1             | 01    | 01bb     | bfff   | ffff     |              | 1,2    |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear                      | 1 (2)         | 01    | 10bb     | bfff   | ffff     |              | 3      |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set                        | 1 (2)         | 01    | 11bb     | bfff   | ffff     |              | 3      |

|                                        |         | LITERAL AND CO                                 |               | IONS  |          |        |          |              |        |

| ADDLW                                  | k       | Add literal and W                              | 1             | 11    | 111x     | kkkk   | kkkk     | C,DC,Z       |        |

| ANDLW                                  | k       | AND literal with W                             | 1             | 11    | 1001     | kkkk   | kkkk     | Z            |        |

| CALL                                   | k       | Call subroutine                                | 2             | 10    | 0kkk     | kkkk   | kkkk     |              |        |

| CLRWDT                                 | —       | Clear Watchdog Timer                           | 1             | 00    | 0000     | 0110   | 0100     | TO,PD        |        |

| GOTO                                   | k       | Go to address                                  | 2             | 10    | 1kkk     | kkkk   | kkkk     |              |        |

| IORLW                                  | k       | Inclusive OR literal with W                    | 1             | 11    | 1000     | kkkk   | kkkk     | Z            |        |

| MOVLW                                  | k       | Move literal to W                              | 1             | 11    | 00xx     | kkkk   | kkkk     |              |        |

| RETFIE                                 | —       | Return from interrupt                          | 2             | 00    | 0000     | 0000   | 1001     |              |        |

| RETLW                                  | k       | Return with literal in W                       | 2             | 11    | 01xx     | kkkk   | kkkk     |              |        |

| RETURN                                 | _       | Return from Subroutine                         | 2             | 00    | 0000     | 0000   | 1000     |              |        |

| SLEEP                                  | _       | Go into Standby mode                           | 1             | 00    | 0000     | 0110   | 0011     | TO,PD        |        |

| SUBLW                                  | k       | Subtract W from literal                        | 1             | 11    | 110x     | kkkk   | kkkk     | C,DC,Z       |        |

| XORLW                                  | k       | Exclusive OR literal with W                    | 1             | 11    | 1010     |        |          | Z            |        |

| Note 1.                                | When an | I/O register is modified as a function of itse | f(ea MOVE POI | סידים | 1) the v |        | d will b | e that value | nreser |

#### TABLE 13-2: PIC16CR7X INSTRUCTION SET

on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

# 14.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 14.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and the dsPIC30, dsPIC33 and PIC24 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 14.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 14.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 14.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

# 14.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

# 14.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

# 15.3 Timing Parameter Symbology

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2p                             | pS                                    | 3. Tcc:st | (I <sup>2</sup> C <sup>™</sup> specifications only) |

|---------------------------------------|---------------------------------------|-----------|-----------------------------------------------------|

| 2. TppS                               |                                       | 4. Ts     | (I <sup>2</sup> C <sup>™</sup> specifications only) |

| Т                                     |                                       |           | · · · · ·                                           |

| F                                     | Frequency                             | Т         | Time                                                |

| Lowerca                               | se letters (pp) and their meanings:   |           |                                                     |

| рр                                    |                                       |           |                                                     |

| сс                                    | CCP1                                  | OSC       | OSC1                                                |

| ck                                    | CLKOUT                                | rd        | RD                                                  |

| CS                                    | CS                                    | rw        | RD or WR                                            |

| di                                    | SDI                                   | SC        | SCK                                                 |

| do                                    | SDO                                   | SS        | SS                                                  |

| dt                                    | Data in                               | tO        | ТОСКІ                                               |

| io                                    | I/O port                              | t1        | T1CKI                                               |

| mc                                    | MCLR                                  | wr        | WR                                                  |

| Uppercase letters and their meanings: |                                       |           |                                                     |

| S                                     |                                       |           |                                                     |

| F                                     | Fall                                  | Р         | Period                                              |

| Н                                     | High                                  | R         | Rise                                                |

| I                                     | Invalid (High-impendance)             | V         | Valid                                               |

| L                                     | Low                                   | Z         | High-impendance                                     |

| I <sup>2</sup> C™ only                | ,                                     |           |                                                     |

| AA                                    | output access                         | High      | High                                                |

| BUF                                   | Bus free                              | Low       | Low                                                 |

| Tcc:st (                              | I <sup>2</sup> C specifications only) |           |                                                     |

| CC                                    |                                       |           |                                                     |

| HD                                    | Hold                                  | SU        | Setup                                               |

| ST                                    |                                       |           |                                                     |

| DAT                                   | DATA input hold                       | STO       | Stop condition                                      |

| STA                                   | Start condition                       |           |                                                     |

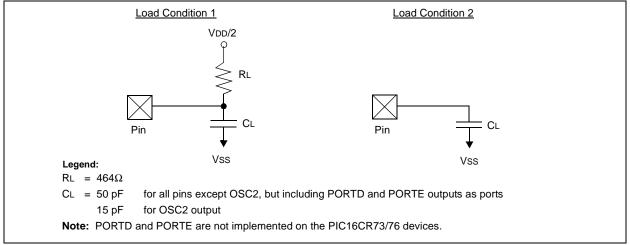

### FIGURE 15-2: LOAD CONDITIONS

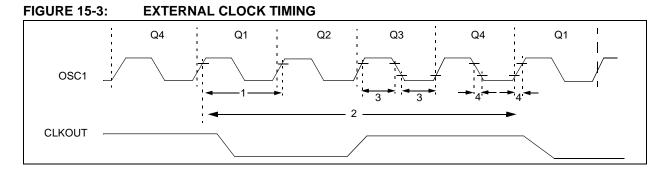

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                     | Min  | Тур† | Max    | Units | Conditions    |

|------------------|--------|------------------------------------|------|------|--------|-------|---------------|

|                  | Fosc   | External CLKIN Frequency           | DC   |      | 1      | MHz   | XT osc mode   |

|                  |        | (Note 1)                           | DC   | _    | 20     | MHz   | HS osc mode   |

|                  |        |                                    | DC   | _    | 32     | kHz   | LP osc mode   |

|                  |        | Oscillator Frequency               | DC   |      | 4      | MHz   | RC osc mode   |

|                  |        | (Note 1)                           | 0.1  | _    | 4      | MHz   | XT osc mode   |

|                  |        |                                    | 4    | _    | 20     | MHz   | HS osc mode   |

|                  |        |                                    | 5    |      | 200    | kHz   | LP osc mode   |

| 1                | Tosc   | External CLKIN Period              | 1000 | _    | —      | ns    | XT osc mode   |

|                  |        | (Note 1)                           | 50   | —    | —      | ns    | HS osc mode   |

|                  |        |                                    | 5    | —    | —      | ms    | LP osc mode   |

|                  |        | Oscillator Period                  | 250  |      |        | ns    | RC osc mode   |

|                  |        | (Note 1)                           | 250  | _    | 10,000 | ns    | XT osc mode   |

|                  |        |                                    | 50   | _    | 250    | ns    | HS osc mode   |

|                  |        |                                    | 5    | _    | —      | ms    | LP osc mode   |

| 2                | Тсү    | Instruction Cycle Time<br>(Note 1) | 200  | Тсү  | DC     | ns    | Tcy = 4/Fosc  |

| 3                | TosL,  | External Clock in (OSC1)           | 500  |      |        | ns    | XT oscillator |

|                  | TosH   | High or Low Time                   | 2.5  | —    | —      | ms    | LP oscillator |

|                  |        |                                    | 15   | —    | —      | ns    | HS oscillator |

| 4                | TosR,  | External Clock in (OSC1)           | —    | _    | 25     | ns    | XT oscillator |

|                  | TosF   | Rise or Fall Time                  | —    | —    | 50     | ns    | LP oscillator |

|                  |        |                                    | —    | —    | 15     | ns    | HS oscillator |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

| Param<br>No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                                            |  |

|--------------|---------|-----------------|--------------|------|-----|-----|-------|-------------------------------------------------------|--|

| 90*          | TSU:STA | Start condition | 100 kHz mode | 4700 |     | _   | ns    | Only relevant for Repeated                            |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | —   |       | Start condition                                       |  |

| 91*          | THD:STA | Start condition | 100 kHz mode | 4000 | _   | —   | ns    | After this period, the first clock pulse is generated |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   | —   |       |                                                       |  |

| 92*          | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                                       |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _   |       |                                                       |  |

| 93           | THD:STO | Stop condition  | 100 kHz mode | 4000 | —   |     | ns    |                                                       |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   |     |       |                                                       |  |

| TABLE 15-8: | I <sup>2</sup> C <sup>™</sup> BUS START/STOP BITS REQUIREMENTS |

|-------------|----------------------------------------------------------------|

|-------------|----------------------------------------------------------------|

\* These parameters are characterized but not tested.

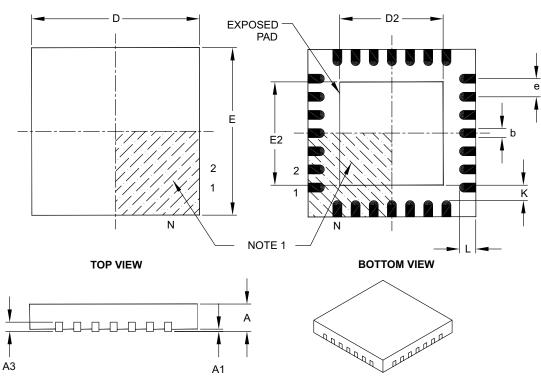

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |                | MILLIMETERS | 6    |  |

|------------------------|------------------|----------------|-------------|------|--|

| C                      | Dimension Limits | MIN            | NOM         | MAX  |  |

| Number of Pins         |                  | 28             |             |      |  |

| Pitch                  | е                |                | 0.65 BSC    |      |  |

| Overall Height         | А                | 0.80           | 0.90        | 1.00 |  |

| Standoff               | A1               | 0.00           | 0.02        | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF       |             |      |  |

| Overall Width          | E                | 6.00 BSC       |             |      |  |

| Exposed Pad Width      | E2               | 3.65 3.70 4.20 |             |      |  |

| Overall Length         | D                | 6.00 BSC       |             |      |  |

| Exposed Pad Length     | D2               | 3.65           | 3.70        | 4.20 |  |

| Contact Width          |                  | 0.23           | 0.30        | 0.35 |  |

| Contact Length         | L                | 0.50           | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad | К                | 0.20           | -           | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | X /XX XXX<br>Temperature Package Pattern<br>Range                                                        | Examples:                                                                                                                             |

|-----------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Device:               | PIC16CR73<br>PIC16CR74<br>PIC16CR76<br>PIC16CR77                                                         |                                                                                                                                       |

| Temperature<br>Range: | $I = -40^{\circ}C \text{ to } +85^{\circ}C  (Industrial)$<br>E = -40^{\circ}C to+125^{\circ}C (Extended) |                                                                                                                                       |

| Package:              | PT = TQFP (Thin Quad Flatpack)<br>L = PLCC<br>SO = SOIC<br>SP = Skinny Plastic DIP<br>P = PDIP           | <ul> <li>Note1: F = Standard Voltage Range<br/>LF = Wide Voltage Range</li> <li>2: T = in tape and reel PLCC, and<br/>TQFP</li> </ul> |

| Pattern:              | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                | packages only.                                                                                                                        |

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445