Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ROM                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr73-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

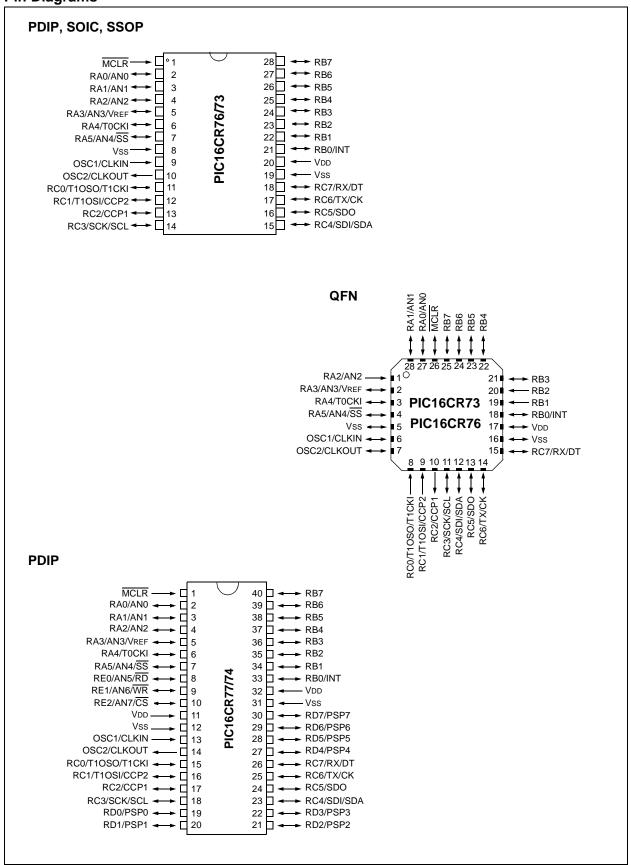

### **Pin Diagrams**

TABLE 1-2: PIC16CR73 AND PIC16CR76 PINOUT DESCRIPTION

| Pin Name            | PDIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                              |

|---------------------|------------------------------|-------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN<br>OSC1  | 9                            | 6           |               | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.                                                                                                                                                                              |

| CLKIN               |                              |             | l<br>I        |                        | Oscillator crystal input or external clock source input. ST buffer when configured in RC mode. Otherwise CMOS. External clock source input. Always associated with pin function OSC1 (see OSC1/CLKIN, OSC2/CLKOUT pins). |

| OSC2/CLKOUT<br>OSC2 | 10                           | 7           | 0             | _                      | Oscillator crystal or clock output.  Oscillator crystal output.  Connects to crystal or resonator in Crystal Oscillator mode.                                                                                            |

| CLKOUT              |                              |             | 0             |                        | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                                                                         |

| MCLR                | 1                            | 26          | I             | ST                     | Master Clear (Reset) input. This pin is an active low Reset to the device.                                                                                                                                               |

|                     | _                            |             |               |                        | PORTA is a bidirectional I/O port.                                                                                                                                                                                       |

| RAO/ANO             | 2                            | 27          | 1/0           | TTL                    | Digital I/O                                                                                                                                                                                                              |

| RA0<br>AN0          |                              |             | I/O<br>I      |                        | Digital I/O.<br>Analog input 0.                                                                                                                                                                                          |

| RA1/AN1             | 3                            | 28          | ·             | TTL                    | , maiog input of                                                                                                                                                                                                         |

| RA1                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                                                                             |

| AN1                 |                              |             | I             |                        | Analog input 1.                                                                                                                                                                                                          |

| RA2/AN2             | 4                            | 1           |               | TTL                    | 5. 5. 5.                                                                                                                                                                                                                 |

| RA2<br>AN2          |                              |             | I/O           |                        | Digital I/O.<br>Analog input 2.                                                                                                                                                                                          |

| RA3/AN3/VREF        | 5                            | 2           | Į.            | TTL                    | Analog input 2.                                                                                                                                                                                                          |

| RA3                 | 3                            | 2           | I/O           | 1112                   | Digital I/O.                                                                                                                                                                                                             |

| AN3                 |                              |             | I             |                        | Analog input 3.                                                                                                                                                                                                          |

| VREF                |                              |             | 1             |                        | A/D reference voltage input.                                                                                                                                                                                             |

| RA4/T0CKI           | 6                            | 3           |               | ST                     |                                                                                                                                                                                                                          |

| RA4                 |                              |             | I/O           |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                      |

| T0CKI<br>RA5/AN4/SS | 7                            |             | 1             | TTL                    | Timer0 external clock input.                                                                                                                                                                                             |

| RA5/AN4/SS          | 7                            | 4           | I/O           | 111                    | Digital I/O.                                                                                                                                                                                                             |

| AN4                 |                              |             | ı, O          |                        | Analog input 4.                                                                                                                                                                                                          |

| SS                  |                              |             | 1             |                        | SPI slave select input.                                                                                                                                                                                                  |

|                     |                              |             |               |                        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                             |

| RB0/INT             | 21                           | 18          |               | TTL/ST <sup>(1)</sup>  | programmed for internal weak pair up on all inputs.                                                                                                                                                                      |

| RB0                 |                              |             | I/O           | 1.12,01                | Digital I/O.                                                                                                                                                                                                             |

| INT                 |                              |             | 1             |                        | External interrupt.                                                                                                                                                                                                      |

| RB1                 | 22                           | 19          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB2                 | 23                           | 20          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB3                 | 24                           | 21          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB4                 | 25                           | 22          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB5                 | 26                           | 23          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB6                 | 27                           | 24          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB7                 | 28                           | 25          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

**Legend:** I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

- 3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

TABLE 1-3: PIC16CR74 AND PIC16CR77 PINOUT DESCRIPTION

| Pin Name           | PDIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                          |

|--------------------|--------------|--------------|-------------|---------------|------------------------|------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN<br>OSC1 | 13           | 14           | 30          | ı             | ST/CMOS <sup>(4)</sup> | Oscillator crystal or external clock input. Oscillator crystal input or external clock source input. |

| 0301               |              |              |             | ,             |                        | ST buffer when configured in RC mode. Otherwise                                                      |

| CLKIN              |              |              |             | I             |                        | CMOS.                                                                                                |

|                    |              |              |             |               |                        | External clock source input. Always associated with pin function OSC1 (see OSC1/CLKIN, OSC2/CLKOUT   |

|                    |              |              |             |               |                        | pins).                                                                                               |

| OSC2/CLKOUT        | 14           | 15           | 31          |               | _                      | Oscillator crystal or clock output.                                                                  |

| OSC2               |              |              |             | 0             |                        | Oscillator crystal output.                                                                           |

|                    |              |              |             |               |                        | Connects to crystal or resonator in Crystal Oscillator mode.                                         |

| CLKOUT             |              |              |             | 0             |                        | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4                                                   |

|                    |              |              |             |               |                        | the frequency of OSC1 and denotes the instruction                                                    |

|                    |              |              |             |               |                        | cycle rate.                                                                                          |

| MCLR               | 1            | 2            | 18          | I             | ST                     | Master Clear (Reset) input. This pin is an active low                                                |

|                    |              |              |             |               |                        | Reset to the device.                                                                                 |

| DAG/ANG            |              |              | 40          |               | TT1                    | PORTA is a bidirectional I/O port.                                                                   |

| RA0/AN0<br>RA0     | 2            | 3            | 19          | I/O           | TTL                    | Digital I/O.                                                                                         |

| AN0                |              |              |             | ı, O          |                        | Analog input 0.                                                                                      |

| RA1/AN1            | 3            | 4            | 20          |               | TTL                    | - '                                                                                                  |

| RA1                |              |              |             | I/O           |                        | Digital I/O.                                                                                         |

| AN1                |              |              |             | I             |                        | Analog input 1.                                                                                      |

| RA2/AN2            | 4            | 5            | 21          | 1/0           | TTL                    | Dimital I/O                                                                                          |

| RA2<br>AN2         |              |              |             | I/O<br>I      |                        | Digital I/O. Analog input 2.                                                                         |

| RA3/AN3/VREF       | 5            | 6            | 22          | '             | TTL                    | Analog input 2.                                                                                      |

| RA3                |              |              |             | I/O           | 112                    | Digital I/O.                                                                                         |

| AN3                |              |              |             | I             |                        | Analog input 3.                                                                                      |

| VREF               |              |              |             | I             |                        | A/D reference voltage input.                                                                         |

| RA4/T0CKI          | 6            | 7            | 23          |               | ST                     | B: 11/10 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                           |

| RA4<br>T0CKI       |              |              |             | I/O<br>I      |                        | Digital I/O – Open drain when configured as output. Timer0 external clock input.                     |

| RA5/AN4/SS         | 7            | 8            | 24          | '             | TTL                    | mmore external clock input.                                                                          |

| RA5                | , ,          |              |             | I/O           | '''                    | Digital I/O.                                                                                         |

| AN4                |              |              |             | I             |                        | Analog input 4.                                                                                      |

| SS                 |              |              |             | I             |                        | SPI slave select input.                                                                              |

Legend:

**l:** I = input

O = output

I/O = input/output

P = power

- = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

TABLE 1-3: PIC16CR74 AND PIC16CR77 PINOUT DESCRIPTION (CONTINUED)

| Pin Name              | PDIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                    |

|-----------------------|--------------|--------------|-------------|---------------|-----------------------|--------------------------------------------------------------------------------|

|                       |              |              |             |               |                       | PORTB is a bidirectional I/O port. PORTB can be software                       |

|                       |              |              |             |               | (0-(1)                | programmed for internal weak pull-up on all inputs.                            |

| RB0/INT<br>RB0        | 33           | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup> | Digital I/O.                                                                   |

| INT                   |              |              |             |               |                       | External interrupt.                                                            |

| RB1                   | 34           | 37           | 9           | I/O           | TTL                   | Digital I/O.                                                                   |

| RB2                   | 35           | 38           | 10          | I/O           | TTL                   | Digital I/O.                                                                   |

| RB3                   | 36           | 39           | 11          | I/O           | TTL                   | Digital I/O.                                                                   |

| RB4                   | 37           | 41           | 14          | I/O           | TTL                   | Digital I/O.                                                                   |

| RB5                   | 38           | 42           | 15          | I/O           | TTL                   | Digital I/O.                                                                   |

| RB6                   | 39           | 43           | 16          | I/O           | TTL                   | Digital I/O.                                                                   |

| RB7                   | 40           | 44           | 17          | I/O           | TTL                   | Digital I/O.                                                                   |

|                       |              |              |             |               |                       | PORTC is a bidirectional I/O port.                                             |

| RC0/T1OSO/            | 15           | 16           | 32          |               | ST                    | ·                                                                              |

| T1CKI                 |              |              |             | I/O           |                       | Digital I/O.                                                                   |

| RC0                   |              |              |             | 0             |                       | Timer1 oscillator output.                                                      |

| T10S0                 |              |              |             | I             |                       | Timer1 external clock input.                                                   |

| T1CKI                 | 40           | 40           | 25          |               | O.T.                  |                                                                                |

| RC1/T1OSI/CCP2<br>RC1 | 16           | 18           | 35          | I/O           | ST                    | Digital I/O.                                                                   |

| T1OSI                 |              |              |             | ı,o           |                       | Timer1 oscillator input.                                                       |

| CCP2                  |              |              |             | I/O           |                       | Capture2 input, Compare2 output, PWM2 output.                                  |

| RC2/CCP1              | 17           | 19           | 36          |               | ST                    |                                                                                |

| RC2                   |              |              |             | I/O           |                       | Digital I/O.                                                                   |

| CCP1                  |              |              |             | I/O           |                       | Capture1 input/Compare1 output/PWM1 output.                                    |

| RC3/SCK/SCL           | 18           | 20           | 37          | 1/0           | ST                    | District 140                                                                   |

| RC3<br>SCK            |              |              |             | I/O<br>I/O    |                       | Digital I/O. Synchronous serial clock input/output for SPI mode.               |

| SCL                   |              |              |             | 1/0           |                       | Synchronous serial clock input/output for I <sup>2</sup> C <sup>TM</sup> mode. |

| RC4/SDI/SDA           | 23           | 25           | 42          |               | ST                    | ,                                                                              |

| RC4                   |              |              |             | I/O           |                       | Digital I/O.                                                                   |

| SDI                   |              |              |             | I             |                       | SPI data in.                                                                   |

| SDA                   |              |              |             | I/O           |                       | I <sup>2</sup> C™ data I/O.                                                    |

| RC5/SDO               | 24           | 26           | 43          |               | ST                    |                                                                                |

| RC5                   |              |              |             | I/O<br>O      |                       | Digital I/O.                                                                   |

| SDO                   | 0.5          | 07           | 4.4         | U             | O.T.                  | SPI data out.                                                                  |

| RC6/TX/CK<br>RC6      | 25           | 27           | 44          | I/O           | ST                    | Digital I/O.                                                                   |

| TX                    |              |              |             | 0             |                       | USART asynchronous transmit.                                                   |

| CK                    |              |              |             | I/O           |                       | USART 1 synchronous clock.                                                     |

| RC7/RX/DT             | 26           | 29           | 1           |               | ST                    |                                                                                |

| RC7                   |              |              |             | I/O           |                       | Digital I/O.                                                                   |

| RX                    |              |              |             | I             |                       | USART asynchronous receive.                                                    |

| DT                    |              | 0 0ts        |             | I/O in        | nt/ntnt               | USART synchronous data.                                                        |

Legend: I =

I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input ST = Schmitt Trigger input

input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

- 3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

- 4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

FIGURE 2-2: PIC16CR77/76 REGISTER FILE MAP

| £                    | File<br>Address | A                    | File<br>Address |                      | File<br>Address |                     | File<br>Addre |

|----------------------|-----------------|----------------------|-----------------|----------------------|-----------------|---------------------|---------------|

| Indirect addr.(*)    | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)    | 100h            | Indirect addr.(*)   | 180           |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                 | 101h            | OPTION_REG          | 181           |

| PCL                  | 02h             | PCL                  | 82h             | PCL                  | 102h            | PCL                 | 182           |

| STATUS               | 03h             | STATUS               | 83h             | STATUS               | 103h            | STATUS              | 183           |

| FSR                  | 04h             | FSR                  | 84h             | FSR                  | 104h            | FSR                 | 184           |

| PORTA                | 05h             | TRISA                | 85h             |                      | 105h            |                     | 185           |

| PORTB                | 06h             | TRISB                | 86h             | PORTB                | 106h            | TRISB               | 186           |

| PORTC                | 07h             | TRISC                | 87h             |                      | 107h            |                     | 187           |

| PORTD <sup>(1)</sup> | 08h             | TRISD <sup>(1)</sup> | 88h             |                      | 108h            |                     | 188           |

| PORTE <sup>(1)</sup> | 09h             | TRISE <sup>(1)</sup> | 89h             |                      | 109h            |                     | 189           |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH               | 10Ah            | PCLATH              | 18/           |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON               | 10Bh            | INTCON              | 18E           |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | PMDATA               | 10Ch            | PMCON1              | 180           |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | PMADR                | 10Dh            |                     | 18[           |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | PMDATH               | 10Eh            |                     | 18E           |

| TMR1H                | 0Fh             | . 55.1               | 8Fh             | PMADRH               | 10Fh            |                     | 18F           |

| T1CON                | 10h             |                      | 90h             | 7 1111 12 1 11 1     | 110h            |                     | 190           |

| TMR2                 | 11h             |                      | 91h             |                      | 111h            |                     | 191           |

| T2CON                | 12h             | PR2                  | 92h             |                      | 112h            |                     | 192           |

| SSPBUF               | 13h             | SSPADD               | 93h             |                      | 113h            |                     | 193           |

| SSPCON               | 14h             | SSPSTAT              | 94h             |                      | 114h            |                     | 194           |

| CCPR1L               | 15h             | 001 01741            | 95h             |                      | 115h            |                     | 195           |

| CCPR1H               | 16h             |                      | 96h             |                      | 116h            |                     | 196           |

| CCP1CON              | 17h             |                      | 97h             | General              | 117h            | General             | 197           |

| RCSTA                | 18h             | TXSTA                | 98h             | Purpose              | 118h            | Purpose<br>Register | 198           |

| TXREG                | 19h             | SPBRG                | 99h             | Register<br>16 Bytes | 119h            | 16 Bytes            | 199           |

| RCREG                | 1Ah             | OI BIXO              | 9Ah             |                      | 11Ah            |                     | 19/           |

| CCPR2L               | 1Bh             |                      | 9Bh             |                      | 11Bh            |                     | 19E           |

| CCPR2H               | 1Ch             |                      | 9Ch             |                      | 11Ch            |                     | 190           |

| CCP2CON              | 1Dh             |                      | 9Dh             |                      | 11Dh            |                     | 190           |

| ADRES                | 1Eh             |                      | 9Eh             |                      | 11Eh            |                     | 19E           |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                      | 11Fh            |                     | 19F           |

| 71200110             | 20h             | 7.000111             | A0h             |                      | 120h            |                     | 1A(           |

| General              | 2011            | General              | AUN             | General              |                 | General             | IAC           |

| Purpose              |                 | Purpose              |                 | Purpose              |                 | Purpose             |               |

| Register             |                 | Register             |                 | Register             |                 | Register            |               |

| 96 Bytes             |                 | 80 Bytes             | EFh             | 80 Bytes             | 16Fh            | 80 Bytes            | 1EF           |

|                      | 7Fh             | accesses<br>70h-7Fh  | F0h<br>FFh      | accesses<br>70h-7Fh  | 170h<br>17Fh    | accesses<br>70h-7Fh | 1F0           |

| Bank 0               | 1111            | Bank 1               | 1 1 11          | Bank 2               | 17111           | Bank 3              |               |

Unimplemented data memory locations, read as '0'.

Note 1: These registers are not implemented on 28-pin devices.

<sup>\*</sup> Not a physical register.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address               | Name       | Bit 7                                                    | Bit 6           | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1         | Bit 0        | Value on<br>POR,<br>BOR | Details on page |

|-----------------------|------------|----------------------------------------------------------|-----------------|---------------|----------------|----------------|---------------|---------------|--------------|-------------------------|-----------------|

| Bank 2                |            |                                                          |                 |               |                |                |               |               |              |                         |                 |

| 100h <sup>(4)</sup>   | INDF       | Addressin                                                | g this location | al register)  | 0000 0000      | 27, 96         |               |               |              |                         |                 |

| 101h                  | TMR0       | Timer0 Mo                                                | dule Registe    | er            |                |                |               |               |              | xxxx xxxx               | 45, 96          |

| 102h <sup>(4)</sup>   | PCL        | Program C                                                | Counter (PC)    | Least Signif  | icant Byte     |                |               |               |              | 0000 0000               | 26, 96          |

| 103h <sup>(4)</sup>   | STATUS     | IRP                                                      | RP1             | RP0           | TO             | PD             | Z             | DC            | С            | 0001 1xxx               | 19, 96          |

| 104h <sup>(4)</sup>   | FSR        | Indirect Da                                              | ata Memory A    | Address Poir  | nter           |                |               |               |              | xxxx xxxx               | 27, 96          |

| 105h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              | _                       | _               |

| 106h                  | PORTB      | PORTB D                                                  | ata Latch wh    | en written: F | ORTB pins w    | hen read       |               |               |              | xxxx xxxx               | 34, 96          |

| 107h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              |                         | _               |

| 108h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              | _                       | _               |

| 109h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              | _                       | _               |

| 10Ah <sup>(1,4)</sup> | PCLATH     | _                                                        | 1               | _             | Write Buffer   | for the upper  | 5 bits of the | Program C     | ounter       | 0 0000                  | 26, 96          |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE                                                      | PEIE            | TMR0IE        | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x               | 21, 96          |

| 10Ch                  | PMDATA     | Data Regis                                               | ster Low Byte   | е             |                |                |               |               |              | xxxx xxxx               | 29, 97          |

| 10Dh                  | PMADR      | Address R                                                | egister Low     | Byte          |                |                |               |               |              | xxxx xxxx               | 29, 97          |

| 10Eh                  | PMDATH     | _                                                        | 1               | Data Regist   | ter High Byte  |                |               |               |              | xxxx xxxx               | 29, 97          |

| 10Fh                  | PMADRH     | _                                                        | _               | _             | Address Reg    | gister High By | ⁄te           |               |              | xxxx xxxx               | 29, 97          |

| Bank 3                |            |                                                          |                 |               |                |                |               |               |              |                         |                 |

| 180h <sup>(4)</sup>   | INDF       | Addressin                                                | g this location | n uses conte  | ents of FSR to | address data   | a memory (r   | not a physica | al register) | 0000 0000               | 27, 96          |

| 181h                  | OPTION_REG | RBPU                                                     | INTEDG          | T0CS          | TOSE           | PSA            | PS2           | PS1           | PS0          | 1111 1111               | 20, 44, 96      |

| 182h <sup>(4)</sup>   | PCL        | Program C                                                | Counter (PC)    | Least Signif  | icant Byte     |                |               |               |              | 0000 0000               | 26, 96          |

| 183h <sup>(4)</sup>   | STATUS     | IRP                                                      | RP1             | RP0           | TO             | PD             | Z             | DC            | С            | 0001 1xxx               | 19, 96          |

| 184h <sup>(4)</sup>   | FSR        | Indirect Da                                              | ata Memory A    | Address Poir  | nter           |                |               |               |              | xxxx xxxx               | 27, 96          |

| 185h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              | _                       | _               |

| 186h                  | TRISB      | PORTB D                                                  | ata Direction   | Register      |                |                |               |               |              | 1111 1111               | 34, 96          |

| 187h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              | _                       | _               |

| 188h                  | _          | Unimplem                                                 | ented           |               |                |                |               |               |              | _                       | _               |

| 189h                  | _          | Unimplemented                                            |                 |               |                |                |               |               |              | _                       | _               |

| 18Ah <sup>(1,4)</sup> | PCLATH     | Write Buffer for the upper 5 bits of the Program Counter |                 |               |                |                |               |               |              | 0 0000                  | 26, 96          |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE                                                      | PEIE            | TMR0IE        | INTE           | RBIE           | TMR0IF        | INTF          | RBIF         | 0000 000x               | 21, 96          |

| 18Ch                  | PMCON1     | (6)                                                      | _               | _             | _              | _              | _             | _             | RD           | 10                      | 29, 97          |

| 18Dh                  |            | Unimplemented                                            |                 |               |                |                |               |               |              |                         |                 |

| 18Eh                  |            | Reserved maintain clear                                  |                 |               |                |                |               |               |              |                         |                 |

| 18Fh                  | _          | Reserved                                                 | maintain clea   | ar            |                |                |               |               |              | 0000 0000               |                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

- 2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

- **6:** This bit always reads as a '1'.

NOTES:

## 3.3 Reading the ROM Program Memory

A program memory location may be read by writing two bytes of the address to the PMADR and PMADRH registers and then setting control bit RD (PMCON1<0>). Once the read control bit is set, the microcontroller will use the next two instruction cycles to read the data. The data is available in the PMDATA and PMDATH registers after the second NOP instruction. Therefore, it can be read as two bytes in the following instructions. The PMDATA and PMDATH registers will hold this value until the next read operation.

#### 3.4 Operation During Code-Protect

ROM program memory has its own code-protect mechanism. External Read operations by programmers are disabled if this mechanism is enabled.

The microcontroller can read and execute instructions out of the internal ROM program memory, regardless of the state of the code-protect Configuration bits.

#### **EXAMPLE 3-1:** ROM PROGRAM READ

```

STATUS, RP1

BCF

STATUS, RPO

; Bank 2

MOVF

ADDRH, W

; MSByte of Program Address to read

MOVWF

PMADRH

MOVF

ADDRL, W

;

MOVWF

PMADR

; LSByte of Program Address to read

BSF

STATUS, RPO

; Bank 3 Required

; ROM Read Sequence

Required

BSF

PMCON1, RD

; memory is read in the next two cycles after BSF PMCON1,RD

Sequence

NOP

NOP

STATUS, RPO

BCF

; Bank 2

; W = LSByte of Program PMDATA

MOVF

PMDATA, W

; W = MSByte of Program PMDATA

MOVF

PMDATH, W

```

#### TABLE 3-1: REGISTERS ASSOCIATED WITH PROGRAM ROM

| Address | Name   | Bit 7     | Bit 6       | Bit 5    | Bit 4      | Bit 3      | Bit 2   | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|--------|-----------|-------------|----------|------------|------------|---------|-------|-------|-------------------------|---------------------------------|

| 10Dh    | PMADR  | Address F | Register Lo | w Byte   |            |            |         |       |       | xxxx xxxx               | uuuu uuuu                       |

| 10Fh    | PMADRH | _         | _           |          | Address F  | Register H | gh Byte |       |       | xxxx xxxx               | uuuu uuuu                       |

| 10Ch    | PMDATA | Data Reg  | ister Low I | Byte     |            |            |         |       |       | xxxx xxxx               | uuuu uuuu                       |

| 10Eh    | PMDATH | _         | _           | Data Reg | ister High | Byte       |         |       |       | xxxx xxxx               | uuuu uuuu                       |

| 18Ch    | PMCON1 | _(1)      | _           | _        | _          | _          | _       | _     | RD    | 1                       | 10                              |

**Legend:** x = unknown, u = unchanged, r = reserved, - = unimplemented read as '0'. Shaded cells are not used during ROM access.

Note 1: This bit always reads as a '1'.

NOTES:

# 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the "PIC<sup>®</sup> Mid-Range MCU Family Reference Manual" (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

#### 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

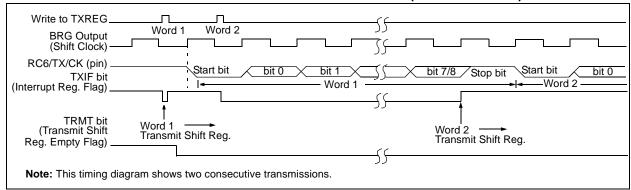

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK-TO-BACK)

TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | ansmit Da | ta Registe | er    |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  | or Registe | r     |       |        |        |        | 0000 0000               | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in

the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received, therefore, it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading RCREG register, in order not to lose the old FERR and RX9D information.

### REGISTER 11-2: ADCON1: (ADDRESS 1Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-3 **Unimplemented**: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | VDD  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | VDD  |

A = Analog input D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16CR74/77 only.

#### 15.1 DC Characteristics: PIC16CR73/74/76/77 (Industrial, Extended) (Continued)

| PIC16C<br>(Indus | <b>R73/74/</b><br>trial, Ex |                            |          |      |     | ure -40 | ditions (unless otherwise stated) $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $0^{\circ}C \leq TA \leq +125^{\circ}C$ for extended |

|------------------|-----------------------------|----------------------------|----------|------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.     | Sym                         | Characteristic             | Min      | Тур† | Max | Units   | Conditions                                                                                                                                   |

|                  | IDD                         | Supply Current (Notes 2, 5 | 5)       |      |     |         |                                                                                                                                              |

| D010             |                             | PIC16CR7X                  | _        | 0.5  | 2   | mA      | XT, RC osc configuration                                                                                                                     |

| D010A            |                             |                            | _        | 20   | 48  | μΑ      | Fosc = 4 MHz, VDD = 3.0V (Note 4) LP osc configuration Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                               |

| D010             |                             | PIC16CR7X                  | _        | 1.1  | 4   | mA      | XT, RC osc configuration                                                                                                                     |

| D013             |                             |                            | _        | 6.3  | 15  | mA      | FOSC = 4 MHz, VDD = 5.5V (Note 4) HS osc configuration FOSC = 20 MHz, VDD = 5.5V                                                             |

| D015*            | $\Delta$ lbor               | Brown-out                  | -        | 30   | 200 | μΑ      | BOR enabled, VDD = 5.0V                                                                                                                      |

|                  |                             | Reset Current (Note 6)     |          |      |     |         |                                                                                                                                              |

| D020             | IPD                         | Power-down Current (Note   | es 3, 5) |      |     |         |                                                                                                                                              |

|                  |                             | PIC16CR7X                  | _        | 2.0  | 30  | μΑ      | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                                                      |

| D021             |                             |                            | _        | 0.1  | 5   | μΑ      | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                                                     |

| D020             |                             | PIC16CR7X                  | _        | 5    | 42  | μΑ      | VDD = 4.0V, WDT enabled, -40°C to +85°C                                                                                                      |

| D021             |                             |                            | _        | 0.1  | 19  | μΑ      | VDD = 4.0V, WDT disabled, -40°C to +85°C                                                                                                     |

| D021A            |                             |                            | _        | 10.5 | 57  | μA      | VDD = 4.0V, WDT enabled, -40°C to                                                                                                            |

|                  |                             |                            | _        | 1.5  | 42  | μΑ      | +125°C                                                                                                                                       |

|                  |                             |                            |          |      |     |         | VDD = 4.0V, WDT disabled, -40°C to +125°C                                                                                                    |

| D023*            | $\Delta IBOR$               | Brown-out                  | _        | 30   | 200 | μΑ      | BOR enabled, VDD = 5.0V                                                                                                                      |

|                  |                             | Reset Current (Note 6)     |          |      |     |         |                                                                                                                                              |

**Legend:** Shading of rows is to assist in readability of of the table.

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impendance state and tied to VDD and VSs.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The Δ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

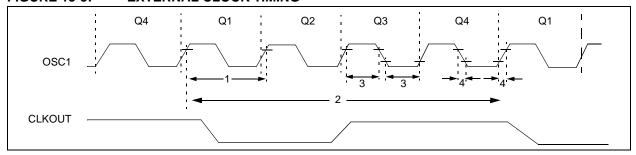

FIGURE 15-3: EXTERNAL CLOCK TIMING

TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter No. | Symbol | Characteristic                  | Min  | Тур† | Max    | Units | Conditions    |

|---------------|--------|---------------------------------|------|------|--------|-------|---------------|

|               | Fosc   | External CLKIN Frequency        | DC   | _    | 1      | MHz   | XT osc mode   |

|               |        | (Note 1)                        | DC   | _    | 20     | MHz   | HS osc mode   |

|               |        |                                 | DC   | _    | 32     | kHz   | LP osc mode   |

|               |        | Oscillator Frequency            | DC   | _    | 4      | MHz   | RC osc mode   |

|               |        | (Note 1)                        | 0.1  | _    | 4      | MHz   | XT osc mode   |

|               |        |                                 | 4    | _    | 20     | MHz   | HS osc mode   |

|               |        |                                 | 5    |      | 200    | kHz   | LP osc mode   |

| 1             | Tosc   | External CLKIN Period           | 1000 | _    |        | ns    | XT osc mode   |

|               |        | (Note 1)                        | 50   | _    | _      | ns    | HS osc mode   |

|               |        |                                 | 5    | _    | _      | ms    | LP osc mode   |

|               |        | Oscillator Period               | 250  | _    | _      | ns    | RC osc mode   |

|               |        | (Note 1)                        | 250  | _    | 10,000 | ns    | XT osc mode   |

|               |        |                                 | 50   | _    | 250    | ns    | HS osc mode   |

|               |        |                                 | 5    | _    | _      | ms    | LP osc mode   |

| 2             | Tcy    | Instruction Cycle Time (Note 1) | 200  | Tcy  | DC     | ns    | Tcy = 4/Fosc  |

| 3             | TosL,  | External Clock in (OSC1)        | 500  | _    | _      | ns    | XT oscillator |

|               | TosH   | High or Low Time                | 2.5  | _    | _      | ms    | LP oscillator |

|               |        |                                 | 15   |      | _      | ns    | HS oscillator |

| 4             | TosR,  | External Clock in (OSC1)        | _    | _    | 25     | ns    | XT oscillator |

|               | TosF   | Rise or Fall Time               | _    | _    | 50     | ns    | LP oscillator |

|               |        |                                 | _    | _    | 15     | ns    | HS oscillator |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

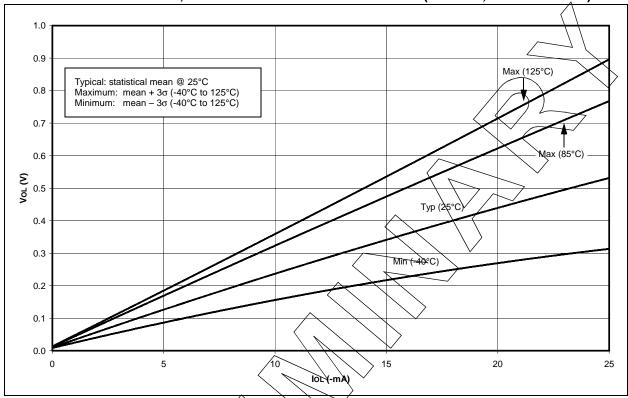

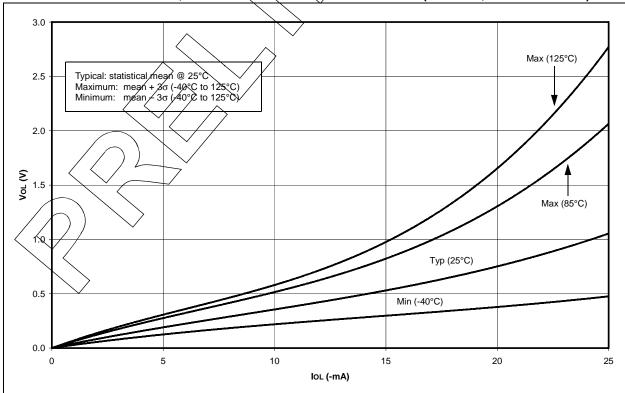

FIGURE 16-17: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO 125°C)

FIGURE 16-18: TYPICAL, MINIMUM, AND MAXIMUM Vol vs. Iol (VDD = 3V, -40°C TO 125°C)

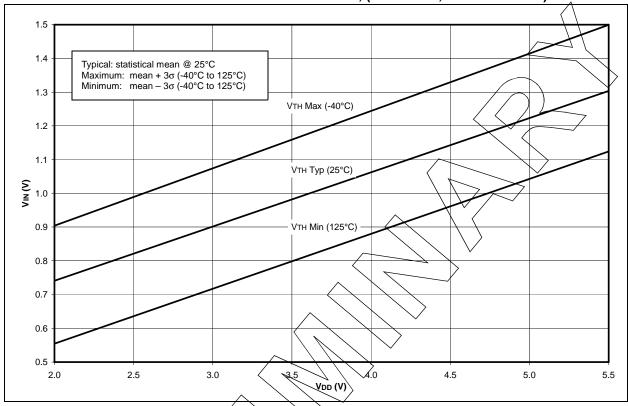

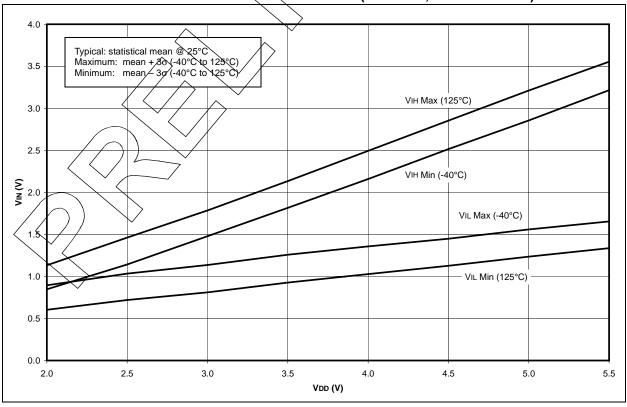

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO 125°C)

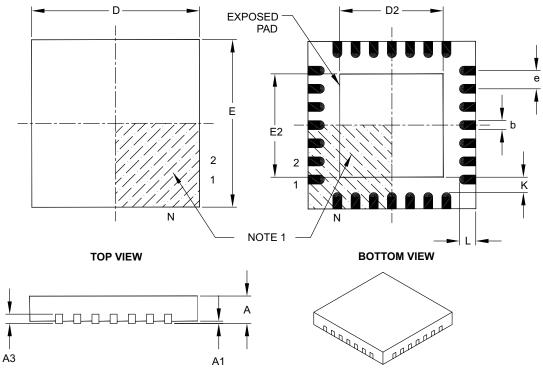

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |      | 3    |

|------------------------|------------------|-------------|------|------|

|                        | Dimension Limits | MIN         | NOM  | MAX  |

| Number of Pins         | N                | 28          |      |      |

| Pitch                  | е                | 0.65 BSC    |      |      |

| Overall Height         | A                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Width          | E                | 6.00 BSC    |      |      |

| Exposed Pad Width      | E2               | 3.65        | 3.70 | 4.20 |

| Overall Length         | D                | 6.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 3.65        | 3.70 | 4.20 |

| Contact Width          | b                | 0.23        | 0.30 | 0.35 |

| Contact Length         | L                | 0.50        | 0.55 | 0.70 |

| Contact-to-Exposed Pad | K                | 0.20        | -    | -    |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

| SSPIF bit                                        | 23    | I <sup>2</sup> C Bus Start/Stop Bits            | 132    |

|--------------------------------------------------|-------|-------------------------------------------------|--------|

| SSPM<3:0> bits                                   |       | I <sup>2</sup> C Reception (7-bit Address)      | 132    |

| SSPOV bit                                        |       | I <sup>2</sup> C Transmission (7-bit Address)   |        |

| Stack                                            |       | Parallel Slave Port                             |        |

| Overflows                                        | _     | Parallel Slave Port Read Waveforms              |        |

| Underflow                                        |       | Parallel Slave Port Write Waveforms             |        |

| STATUS Register                                  |       | Power-up Timer                                  |        |

| DC Bit                                           | 19    | PWM Output                                      |        |

| IRP Bit                                          |       | RESET                                           |        |

| PD Bit                                           |       | Slow Rise Time (MCLR Tied to VDD                | 0      |

| TO Bit                                           |       | Through RC Network)                             | 98     |

| Z Bit                                            |       | SPI Master Mode (CKE = 0, SMP = 0)              |        |

| Synchronous Serial Port Enable bit (SSPEN)       | 61    | SPI Master Mode (CKE = 1, SMP = 1)              | 130    |

| Synchronous Serial Port Interrupt bit (SSPIF)    |       | SPI Mode (Master Mode)                          |        |

| Synchronous Serial Port Mode Select bits (SSPM<3 |       | SPI Mode (Slave Mode with CKE = 0)              |        |

| Synchronous Serial Port. See SSP                 |       | SPI Mode (Slave Mode with CKE = 1)              | 64     |

| T                                                |       | SPI Slave Mode (CKE = 0)                        | 131    |

| Т                                                |       | SPI Slave Mode (CKE = 1)                        | 131    |

| T1CKPS0 bit                                      | 47    | Start-up Timer                                  | 126    |

| T1CKPS1 bit                                      |       | Time-out Sequence on Power-up                   |        |

| T10SCEN bit                                      |       | (MCLR Not Tied to VDD)                          |        |

| T1SYNC bit                                       |       | Case 1                                          | 98     |

| T2CKPS0 bit                                      | _     | Case 2                                          | 98     |

| T2CKPS1 bit                                      | _     | Time-out Sequence on Power-up                   |        |

| TAD                                              |       | (MCLR Tied to VDD Through RC Network)           |        |

| Time-out Sequence                                |       | Timer0                                          |        |

| Timer0                                           |       | Timer1                                          |        |

| Associated Registers                             |       | USART Asynchronous Master Transmission          | /4     |

| Clock Source Edge Select (TOSE Bit)              |       | USART Asynchronous Master Transmission          | 7.     |

| Clock Source Select (T0CS Bit) External Clock    |       | (Back to Back)                                  |        |

| Interrupt                                        |       | USART Asynchronous Reception                    |        |

| Overflow Enable (TMR0IE Bit)                     |       | USART Synchronous Receive (Master/Slave)        | 133    |

| Overflow Flag (TMR0IF Bit)                       |       | USART Synchronous Reception (Master Mode, SREN) | 90     |

| Overflow Interrupt                               |       | USART Synchronous Transmission                  |        |

| Prescaler                                        |       | USART Synchronous Transmission                  | 13     |

| RA4/T0CKI Pin, External Clock                    |       | (Master/Slave)                                  | 135    |

| T0CKI                                            |       | USART Synchronous Transmission                  | 100    |

| Timer1                                           |       | (Through TXEN)                                  | 79     |

| Associated Registers                             |       | Wake-up from Sleep via Interrupt                |        |

| Asynchronous Counter Mode                        | 49    | Watchdog Timer                                  |        |

| Capacitor Selection                              |       | Timing Parameter Symbology                      |        |

| Counter Operation                                | 48    | Timing Requirements                             |        |

| Operation in Timer Mode                          | 48    | Capture/Compare/PWM (CCP1 and CCP2)             | 128    |

| Oscillator                                       | 50    | CLKOUT and I/O                                  |        |

| Prescaler                                        |       | External Clock                                  | 124    |

| RC0/T1OSO/T1CKI Pin                              | 9, 11 | I <sup>2</sup> C Bus Data                       | 134    |

| RC1/T1OSI/CCP2 Pin                               | 9, 11 | I2C Bus Start/Stop Bits                         | 133    |

| Resetting of Timer1 Registers                    |       | Parallel Slave Port                             | 129    |