#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ROM                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr73t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Device Overview                                                 | 5     |

|-----------------------------------------------------------------|-------|

| Aemory Organization                                             | 13    |

| Reading Program Memory                                          |       |

| O Ports                                                         | 31    |

| imer0 Module                                                    | 43    |

| imer1 Module                                                    | 47    |

| imer2 Module                                                    | 51    |

| Capture/Compare/PWM Modules                                     | 53    |

| Synchronous Serial Port (SSP) Module                            | 59    |

| Iniversal Synchronous Asynchronous Receiver Transmitter (USART) | 69    |

| nalog-to-Digital Converter (A/D) Module                         | 83    |

| Special Features of the CPU                                     | 89    |

| nstruction Set Summary                                          | . 105 |

| Development Support                                             | . 113 |

| Electrical Characteristics                                      | . 117 |

| OC and AC Characteristics Graphs and Tables                     | . 139 |

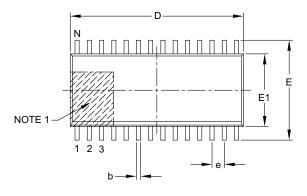

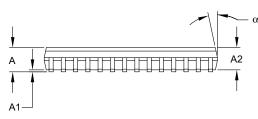

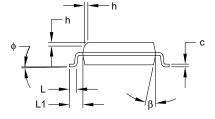

| Packaging Information                                           | . 149 |

| Appendix A: Revision History                                    |       |

| Appendix B: Device Differences                                  | . 159 |

| Appendix C: Conversion Considerations                           |       |

| he Microchip Web Site                                           | . 167 |

| Customer Change Notification Service                            |       |

| Customer Support                                                | . 167 |

| Reader Response                                                 | . 168 |

| Product Identification System                                   | . 169 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## TABLE 1-2:PIC16CR73 AND PIC16CR76 PINOUT DESCRIPTION

| Pin Name            | PDIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                      |  |

|---------------------|------------------------------|-------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSC1/CLKIN<br>OSC1  | 9                            | 6           | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode. Otherwise CMOS. |  |

| CLKIN               |                              |             | Ι             |                        | External clock source input. Always associated with pin<br>function OSC1 (see OSC1/CLKIN, OSC2/CLKOUT pins).                                                     |  |

| OSC2/CLKOUT<br>OSC2 | 10                           | 7           | 0             | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator<br>mode.                             |  |

| CLKOUT              |                              |             | 0             |                        | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                 |  |

| MCLR                | 1                            | 26          | Ι             | ST                     | Master Clear (Reset) input. This pin is an active low Reset to the device.                                                                                       |  |

|                     |                              |             |               |                        | PORTA is a bidirectional I/O port.                                                                                                                               |  |

| RA0/AN0             | 2                            | 27          |               | TTL                    |                                                                                                                                                                  |  |

| RA0                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |  |

| AN0                 |                              |             | I             |                        | Analog input 0.                                                                                                                                                  |  |

| RA1/AN1             | 3                            | 28          |               | TTL                    |                                                                                                                                                                  |  |

| RA1                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |  |

| AN1                 |                              |             | I             |                        | Analog input 1.                                                                                                                                                  |  |

| RA2/AN2             | 4                            | 1           | 1/0           | TTL                    |                                                                                                                                                                  |  |

| RA2<br>AN2          |                              |             | I/O           |                        | Digital I/O.<br>Analog input 2.                                                                                                                                  |  |

| RA3/AN3/VREF        | 5                            | 2           | 1             | TTL                    |                                                                                                                                                                  |  |

| RA3/AN3/VREF        | 5                            | 2           | I/O           | 116                    | Digital I/O.                                                                                                                                                     |  |

| AN3                 |                              |             | 1/C           |                        | Analog input 3.                                                                                                                                                  |  |

| VREF                |                              |             | I             |                        | A/D reference voltage input.                                                                                                                                     |  |

| RA4/T0CKI           | 6                            | 3           |               | ST                     |                                                                                                                                                                  |  |

| RA4                 |                              |             | I/O           |                        | Digital I/O – Open drain when configured as output.                                                                                                              |  |

| TOCKI               |                              |             | I             |                        | Timer0 external clock input.                                                                                                                                     |  |

| RA5/AN4/SS          | 7                            | 4           |               | TTL                    |                                                                                                                                                                  |  |

| RA5                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |  |

| AN4                 |                              |             |               |                        | Analog input 4.                                                                                                                                                  |  |

| SS                  |                              |             |               |                        | SPI slave select input.                                                                                                                                          |  |

|                     |                              |             |               |                        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                     |  |

| RB0/INT             | 21                           | 18          |               | TTL/ST <sup>(1)</sup>  |                                                                                                                                                                  |  |

| RB0                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |  |

| INT                 |                              |             | I             |                        | External interrupt.                                                                                                                                              |  |

| RB1                 | 22                           | 19          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

| RB2                 | 23                           | 20          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

| RB3                 | 24                           | 21          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

| RB4                 | 25                           | 22          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

| RB5                 | 26                           | 23          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

| RB6                 | 27                           | 24          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

| RB7                 | 28                           | 25          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |  |

|                     | 1                            | 1           |               | 1                      |                                                                                                                                                                  |  |

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

#### FIGURE 2-2: PIC16CR77/76 REGISTER FILE MAP

| F                                          | File<br>\ddress | P                                          | File<br>Address |                                            | File<br>Address |                                            | File<br>Addres |

|--------------------------------------------|-----------------|--------------------------------------------|-----------------|--------------------------------------------|-----------------|--------------------------------------------|----------------|

| Indirect addr.(*)                          | 00h             | Indirect addr.(*)                          | 80h             | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180h           |

| TMR0                                       | 01h             | OPTION_REG                                 | 81h             | TMR0                                       | 101h            | OPTION_REG                                 | 181h           |

| PCL                                        | 02h             | PCL                                        | 82h             | PCL                                        | 102h            | PCL                                        | 182h           |

| STATUS                                     | 03h             | STATUS                                     | 83h             | STATUS                                     | 103h            | STATUS                                     | 183h           |

| FSR                                        | 04h             | FSR                                        | 84h             | FSR                                        | 104h            | FSR                                        | 184h           |

| PORTA                                      | 05h             | TRISA                                      | 85h             |                                            | 105h            |                                            | 185h           |

| PORTB                                      | 06h             | TRISB                                      | 86h             | PORTB                                      | 106h            | TRISB                                      | 186h           |

| PORTC                                      | 07h             | TRISC                                      | 87h             |                                            | 107h            |                                            | 187h           |

| PORTD <sup>(1)</sup>                       | 08h             | TRISD <sup>(1)</sup>                       | 88h             |                                            | 108h            |                                            | 188h           |

| PORTE <sup>(1)</sup>                       | 09h             | TRISE <sup>(1)</sup>                       | 89h             |                                            | 109h            |                                            | 189h           |

| PCLATH                                     | 0Ah             | PCLATH                                     | 8Ah             | PCLATH                                     | 10Ah            | PCLATH                                     | 18Ah           |

| INTCON                                     | 0Bh             | INTCON                                     | 8Bh             | INTCON                                     | 10Bh            | INTCON                                     | 18Bh           |

| PIR1                                       | 0Ch             | PIE1                                       | 8Ch             | PMDATA                                     | 10Ch            | PMCON1                                     | 18Ch           |

| PIR2                                       | 0Dh             | PIE2                                       | 8Dh             | PMADR                                      | 10Dh            |                                            | 18Dh           |

| TMR1L                                      | 0Eh             | PCON                                       | 8Eh             | PMDATH                                     | 10Eh            |                                            | 18Eh           |

| TMR1H                                      | 0Fh             |                                            | 8Fh             | PMADRH                                     | 10Fh            |                                            | 18Fh           |

| T1CON                                      | 10h             |                                            | 90h             |                                            | 110h            |                                            | 190h           |

| TMR2                                       | 11h             | -                                          | 91h             |                                            | 111h            |                                            | 191h           |

| T2CON                                      | 12h             | PR2                                        | 92h             |                                            | 112h            |                                            | 192h           |

| SSPBUF                                     | 13h             | SSPADD                                     | 93h             |                                            | 113h            |                                            | 193h           |

| SSPCON                                     | 14h             | SSPSTAT                                    | 94h             |                                            | 114h            |                                            | 194h           |

| CCPR1L                                     | 15h             |                                            | 95h             |                                            | 115h            |                                            | 195h           |

| CCPR1H                                     | 16h             |                                            | 96h             |                                            | 116h            |                                            | 196h           |

| CCP1CON                                    | 17h             |                                            | 97h             | General                                    | 117h            | General                                    | 197h           |

| RCSTA                                      | 18h             | TXSTA                                      | 98h             | Purpose<br>Register                        | 118h            | Purpose<br>Register                        | 198h           |

| TXREG                                      | 19h             | SPBRG                                      | 99h             | 16 Bytes                                   | 119h            | 16 Bytes                                   | 199h           |

| RCREG                                      | 1Ah             |                                            | 9Ah             | ,                                          | 11Ah            | ,                                          | 19Ah           |

| CCPR2L                                     | 1Bh             |                                            | 9Bh             |                                            | 11Bh            |                                            | 19Bh           |

| CCPR2H                                     | 1Ch             |                                            | 9Ch             |                                            | 11Ch            |                                            | 19Ch           |

| CCP2CON                                    | 1Dh             |                                            | 9Dh             |                                            | 11Dh            |                                            | 19Dh           |

| ADRES                                      | 1Eh             |                                            | 9Eh             |                                            | 11Eh            |                                            | 19Eh           |

| ADCON0                                     | 1Fh             | ADCON1                                     | 9Fh             |                                            | 11Fh            |                                            | 19Fh           |

|                                            | 20h             |                                            | A0h             |                                            | 120h            |                                            | 1A0h           |

| General<br>Purpose<br>Register<br>96 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes | EFh             | General<br>Purpose<br>Register<br>80 Bytes | 16Fh            | General<br>Purpose<br>Register<br>80 Bytes | 1EFh           |

|                                            | 7Fh             | accesses<br>70h-7Fh                        | FOh<br>FFh      | accesses<br>70h-7Fh                        | 170h<br>17Fh    | accesses<br>70h-7Fh                        | 1F0h           |

| Bank 0                                     |                 | Bank 1                                     |                 | Bank 2                                     |                 | Bank 3                                     |                |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

**Note 1:** These registers are not implemented on 28-pin devices.

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by either of the two CCP modules as the special event trigger (see Sections 8.1 and 8.2). Register 6-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| —     | —   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

#### REGISTER 6-1: T1CON: TIMER1 CONTROL (ADDRESS 10h)

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6       | Unimplemented: Read as '0'                                                                                      |

|---------------|-----------------------------------------------------------------------------------------------------------------|

| bit 5-4       | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                                                        |

|               | 11 = 1:8 Prescale value                                                                                         |

|               | 10 = 1:4 Prescale value                                                                                         |

|               | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                              |

| <b>h</b> it 0 |                                                                                                                 |

| bit 3         | <b>T1OSCEN</b> : Timer1 Oscillator Enable Control bit<br>1 = Oscillator is enabled                              |

|               | <ul> <li>0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)</li> </ul> |

| bit 2         | <b>TISYNC</b> : Timer1 External Clock Input Synchronization Control bit                                         |

| DIT Z         | $\underline{\text{TMR1CS}} = 1$ :                                                                               |

|               | 1 = Do not synchronize external clock input                                                                     |

|               | 0 = Synchronize external clock input                                                                            |

|               | <u>TMR1CS = 0:</u>                                                                                              |

|               | This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.                                            |

| bit 1         | TMR1CS: Timer1 Clock Source Select bit                                                                          |

|               | 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)                                                |

|               | 0 = Internal clock (Fosc/4)                                                                                     |

| bit 0         | TMR1ON: Timer1 On bit                                                                                           |

|               | 1 = Enables Timer1                                                                                              |

|               | 0 = Stops Timer1                                                                                                |

|               |                                                                                                                 |

## 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1 "Reading and writing Timer1 in asynchronous counter mode").

In Asynchronous Counter mode, Timer1 cannot be used as a time base for capture or compare operations.

### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. The example code provided in Example 6-1 and Example 6-2 demonstrates how to write to and read Timer1 while it is running in Asynchronous mode.

#### EXAMPLE 6-1: WRITING A 16-BIT FREE-RUNNING TIMER

| ; All  | interrupts   | are  | e disabled                                     |

|--------|--------------|------|------------------------------------------------|

| CLRF   | TMR1L        | ;    | Clear Low byte, Ensures no rollover into TMR1H |

| MOVLW  | HI_BYTE      | ;    | Value to load into TMR1H                       |

| MOVWF  | TMR1H, F     | ;    | Write High byte                                |

| MOVLW  | LO_BYTE      | ;    | Value to load into TMR1L                       |

| MOVWF  | TMR1H, F     | ;    | Write Low byte                                 |

| ; Re-e | enable the I | Inte | errupt (if required)                           |

| CONTIN | IUE          | ;    | Continue with your code                        |

#### EXAMPLE 6-2: READING A 16-BIT FREE-RUNNING TIMER

| ; All in | nterrupts  | are  | disabled                                             |

|----------|------------|------|------------------------------------------------------|

| MOVF     | TMR1H, W   | ;    | Read high byte                                       |

| MOVWF    | TMPH       |      |                                                      |

| MOVF     | TMR1L, W   | ;    | Read low byte                                        |

| MOVWF    | TMPL       |      |                                                      |

| MOVF     | TMR1H, W   | ;    | Read high byte                                       |

| SUBWF    | TMPH, W    | ;    | Sub 1st read with 2nd read                           |

| BTFSC    | STATUS,Z   | ;    | Is result = 0                                        |

| GOTO     | CONTINUE   | ;    | Good 16-bit read                                     |

| ; TMR1L  | may have   | rol  | led over between the read of the high and low bytes. |

| ; Readin | ng the hig | ſh a | nd low bytes now will read a good value.             |

| MOVF     | TMR1H, W   | ;    | Read high byte                                       |

| MOVWF    | TMPH       |      |                                                      |

| MOVF     | TMR1L, W   | ;    | Read low byte                                        |

| MOVWF    | TMPL       | ;    | Re-enable the Interrupt (if required)                |

| CONTINU  | Ε          | ;    | Continue with your code                              |

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

## 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 and CCP2 special event triggers.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

|          | Frequency | Capacitors Used: |       |  |  |  |

|----------|-----------|------------------|-------|--|--|--|

| Osc Type | Frequency | OSC1             | OSC2  |  |  |  |

| LP       | 32 kHz    | 47 pF            | 47 pF |  |  |  |

|          | 100 kHz   | 33 pF            | 33 pF |  |  |  |

|          | 200 kHz   | 15 pF            | 15 pF |  |  |  |

|          |           |                  |       |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

| e notes (below) table for additional information. |

|---------------------------------------------------|

|---------------------------------------------------|

| Commonly Used Crystals:                                                                                                                                                                 |                                                                                                                                 |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 32.768 kHz                                                                                                                                                                              | Epson C-001R32.768K-A                                                                                                           |  |  |  |  |  |  |

| 100 kHz                                                                                                                                                                                 | Epson C-2 100.00 KC-P                                                                                                           |  |  |  |  |  |  |

| 200 kHz                                                                                                                                                                                 | STD XTL 200.000 kHz                                                                                                             |  |  |  |  |  |  |

| 0                                                                                                                                                                                       | <ol> <li>Higher capacitance increases the stability<br/>of the oscillator, but also increases the<br/>start-up time.</li> </ol> |  |  |  |  |  |  |

| <ul> <li>Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                                                                                                                 |  |  |  |  |  |  |

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

## 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name                                                                              | Bit 7                                                                      | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|---------|---------|---------|--------|--------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON                                                                            | GIE                                                                        | PEIE  | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch                   | PIR1                                                                              | PSPIF <sup>(1)</sup>                                                       | ADIF  | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF    | 0000 0000               | 0000 0000                       |

| 8Ch                   | PIE1                                                                              | PSPIE <sup>(1)</sup>                                                       | ADIE  | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE    | 0000 0000               | 0000 0000                       |

| 0Eh                   | TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                                                            |       |         |         |         |        |        | xxxx xxxx | uuuu uuuu               |                                 |

| 0Fh                   | TMR1H                                                                             | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |       |         |         |         |        |        | xxxx xxxx | uuuu uuuu               |                                 |

| 10h                   | T1CON                                                                             | —                                                                          | _     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N    | 00 0000                 | uu uuuu                         |

## TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

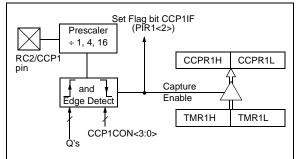

## 8.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

## 8.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |

|-------|-----------------------------------------|

|       | output, a write to the port can cause a |

|       | capture condition.                      |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

## 8.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ;the new prescaler      |

|       |             | ;move value and CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ;value                  |

|       |             |                         |

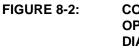

## 8.4 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit TMR1F (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

| R/W-0            | R/W-0                                                                                                                                                                                    | R/W-0                | R/W-0                 | R/W-0                | R/W-0                           | R/W-0            | R/W-0 |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|----------------------|---------------------------------|------------------|-------|--|--|--|

| WCOL             | SSPOV                                                                                                                                                                                    | SSPEN                | CKP                   | SSPM3                | SSPM2                           | SSPM1            | SSPM0 |  |  |  |

| bit 7            |                                                                                                                                                                                          |                      |                       |                      |                                 |                  | bit C |  |  |  |

|                  |                                                                                                                                                                                          |                      |                       |                      |                                 |                  |       |  |  |  |

| Legend:          |                                                                                                                                                                                          |                      |                       |                      |                                 |                  |       |  |  |  |

| R = Readable bi  |                                                                                                                                                                                          | W = Writable bit     |                       |                      | ented bit, read as              |                  |       |  |  |  |

| -n = Value at PO | R                                                                                                                                                                                        | '1' = Bit is set     |                       | '0' = Bit is clea    | red                             | x = Bit is unkno | wn    |  |  |  |

| L:+ 7            |                                                                                                                                                                                          | Alliaian Dataat ki   |                       |                      |                                 |                  |       |  |  |  |

| bit 7            |                                                                                                                                                                                          | Collision Detect bit |                       | still transmitting t | he previous word                |                  |       |  |  |  |

|                  |                                                                                                                                                                                          | leared in software   |                       |                      |                                 |                  |       |  |  |  |

|                  | 0 = No collisio                                                                                                                                                                          | n                    |                       |                      |                                 |                  |       |  |  |  |

| bit 6            |                                                                                                                                                                                          | ve Overflow Indica   | ator bit              |                      |                                 |                  |       |  |  |  |

|                  | <u>In SPI mode:</u><br>1 = A new byte                                                                                                                                                    | e is received while  | the SSPRUE            | register is still b  | olding the previou              | s data. In case  |       |  |  |  |

|                  |                                                                                                                                                                                          |                      |                       |                      | occur in Slave mod              |                  |       |  |  |  |

|                  |                                                                                                                                                                                          |                      |                       |                      | void setting overf              |                  |       |  |  |  |

|                  |                                                                                                                                                                                          |                      |                       |                      | ception (and trans              | smission) is     |       |  |  |  |

|                  | initiated by writing to the SSPBUF register.<br>0 = No overflow                                                                                                                          |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | In I <sup>2</sup> C mode:                                                                                                                                                                |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV<br>is a "don't care" in Transmit mode. SSPOV must be cleared in software in either mode.      |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | is a "don't care" in Transmit mode. SSPOV must be cleared in software in either mode.<br>0 = No overflow                                                                                 |                      |                       |                      |                                 |                  |       |  |  |  |

| bit 5            | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | In SPI mode:                                                                                                                                                                             |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 1 = Enables serial port and configures SCK, SDO and SDI as serial port pins                                                                                                              |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 0 = Disables serial port and configures these pins as I/O port pins<br>In $I^2C$ mode:                                                                                                   |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 1 = Enables the serial port and configures the SDA and SCL pins as serial port pins                                                                                                      |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | <ul> <li>D = Disables serial port and configures these pins as I/O port pins</li> <li>In both modes, when enabled, these pins must be properly configured as input or output.</li> </ul> |                      |                       |                      |                                 |                  |       |  |  |  |

| L:+ 4            |                                                                                                                                                                                          |                      | iese pins must        | be properly con      | figured as input of             | r output.        |       |  |  |  |

| bit 4            | CKP: Clock Po<br>In SPI mode:                                                                                                                                                            | larity Select bit    |                       |                      |                                 |                  |       |  |  |  |

|                  | 1 = Idle state for clock is a high level (Microwire default)                                                                                                                             |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 0 = Idle state for clock is a low level (Microwire alternate)                                                                                                                            |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | In I <sup>2</sup> C mode:                                                                                                                                                                | ontrol               |                       |                      |                                 |                  |       |  |  |  |

|                  | SCK release control<br>1 = Enable clock                                                                                                                                                  |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 0 = Holds clock                                                                                                                                                                          | low (clock stretc    | h). (Used to er       | nsure data setup     | time.)                          |                  |       |  |  |  |

| bit 3-0          |                                                                                                                                                                                          | 0: Synchronous S     |                       | le Select bits       |                                 |                  |       |  |  |  |

|                  | 0000 = SPI Master mode, clock = Fosc/4                                                                                                                                                   |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 0001 = SPI Master mode, clock = Fosc/16<br>0010 = SPI Master mode, clock = Fosc/64                                                                                                       |                      |                       |                      |                                 |                  |       |  |  |  |

|                  | 0011 = SPI Ma                                                                                                                                                                            | ster mode, clock     | = TMR2 o <u>utp</u> u |                      |                                 |                  |       |  |  |  |

|                  |                                                                                                                                                                                          | ave mode, clock =    |                       |                      | ed.<br>led. <u>SS</u> can be us | ad as 1/0 sis    |       |  |  |  |

|                  |                                                                                                                                                                                          | Slave mode, clock =  |                       | pin control disabi   | ieu. 55 can be us               | eu as i/O pin.   |       |  |  |  |

|                  | 0111 = I <sup>2</sup> C™ S                                                                                                                                                               | Slave mode, 10-bi    | t address             |                      |                                 |                  |       |  |  |  |

|                  |                                                                                                                                                                                          | Firmware Controlle   |                       |                      | interrupts enable               | d                |       |  |  |  |

|                  |                                                                                                                                                                                          |                      |                       |                      | it interrupts enable            |                  |       |  |  |  |

|                  |                                                                                                                                                                                          |                      |                       |                      |                                 |                  |       |  |  |  |

# REGISTER 9-2: SSPCON: SYNC SERIAL PORT CONTROL (ADDRESS 14h)

## 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined. It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

## 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

## TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = FOSC/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

## TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7   | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|---------|------------------------------|-------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 98h     | TXSTA | CSRC    | TX9                          | TXEN  | SYNC  | —     | BRGH  | TRMT  | TX9D  | 0000 -010               | 0000 -010                       |

| 18h     | RCSTA | SPEN    | RX9                          | SREN  | CREN  | —     | FERR  | OERR  | RX9D  | 0000 -00x               | 0000 -00x                       |

| 99h     | SPBRG | Baud Ra | Baud Rate Generator Register |       |       |       |       |       |       | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one Start bit, eight or nine data bits, and one Stop bit). The most common data format is 8bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

## 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the Transmit (serial) Shift Register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>) are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read-only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to high-impendance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

## 12.2 Oscillator Configurations

#### 12.2.1 OSCILLATOR TYPES

The PIC16CR7X can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High-Speed Crystal/Resonator

- RC Resistor/Capacitor

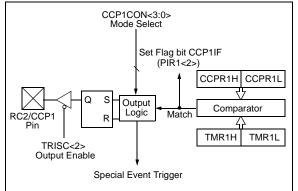

#### 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

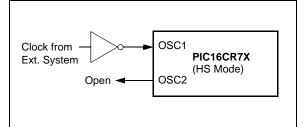

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16CR7X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS mode, the device can accept an external clock source to drive the OSC1/CLKIN pin (Figure 12-2). See Figure 15-1 or Figure 15-2 (depending on the part number and VDD range) for valid external clock frequencies.

#### FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### FIGURE 12-2:

#### EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

#### TABLE 12-1: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| 1                    | Typical Capacitor Values Used: |       |       |  |  |  |  |  |  |

|----------------------|--------------------------------|-------|-------|--|--|--|--|--|--|

| Mode Freq. OSC1 OSC2 |                                |       |       |  |  |  |  |  |  |

| XT                   | 455 kHz                        | 56 pF | 56 pF |  |  |  |  |  |  |

|                      | 2.0 MHz                        | 47 pF | 47 pF |  |  |  |  |  |  |

|                      | 4.0 MHz                        | 33 pF | 33 pF |  |  |  |  |  |  |

| HS                   | 8.0 MHz                        | 27 pF | 27 pF |  |  |  |  |  |  |

|                      | 16.0 MHz                       | 22 pF | 22 pF |  |  |  |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes at the bottom of page 92 for additional information.

| Resonators Used:               |                        |  |  |  |  |  |

|--------------------------------|------------------------|--|--|--|--|--|

| 455 kHz Panasonic EFO-A455K04B |                        |  |  |  |  |  |

| 2.0 MHz Murata Erie CSA2.00MG  |                        |  |  |  |  |  |

| 4.0 MHz                        | Murata Erie CSA4.00MG  |  |  |  |  |  |

| 8.0 MHz                        | Murata Erie CSA8.00MT  |  |  |  |  |  |

| 16.0 MHz                       | Murata Erie CSA16.00MX |  |  |  |  |  |

#### TABLE 12-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freg. | Typical Capacitor Values<br>Tested: |       |  |  |  |

|----------|------------------|-------------------------------------|-------|--|--|--|

|          | rieq.            | C1                                  | C2    |  |  |  |

| LP       | 32 kHz           | 33 pF                               | 33 pF |  |  |  |

|          | 200 kHz          | 15 pF                               | 15 pF |  |  |  |

| XT       | 200 kHz          | 56 pF                               | 56 pF |  |  |  |

|          | 1 MHz            | 15 pF                               | 15 pF |  |  |  |

|          | 4 MHz            | 15 pF                               | 15 pF |  |  |  |

| HS       | 4 MHz            | 15 pF                               | 15 pF |  |  |  |

|          | 8 MHz            | 15 pF                               | 15 pF |  |  |  |

|          | 20 MHz           | 15 pF                               | 15 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

|                              | Crystals Used:                |  |  |  |  |  |  |  |

|------------------------------|-------------------------------|--|--|--|--|--|--|--|

| 32 kHz Epson C-001R32.768K-A |                               |  |  |  |  |  |  |  |

| 200 kHz STD XTL 200.000KHz   |                               |  |  |  |  |  |  |  |

| 1 MHz                        | 1 MHz ECS ECS-10-13-1         |  |  |  |  |  |  |  |

| 4 MHz                        | ECS ECS-40-20-1               |  |  |  |  |  |  |  |

| 8 MHz                        | EPSON CA-301 8.000M-C         |  |  |  |  |  |  |  |

| 20 MHz                       | 20 MHz EPSON CA-301 20.000M-C |  |  |  |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

#### 12.2.3 RC OSCILLATOR

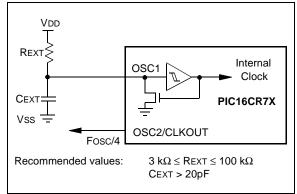

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16CR7X.

#### FIGURE 12-3: RC OSCILLATOR MODE

## 15.1 DC Characteristics: PIC16CR73/74/76/77 (Industrial, Extended)

| PIC16CR73/74/76/77<br>(Industrial, Extended) |      |                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |                   |             |                                                                                        |  |  |  |

|----------------------------------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|-------------|----------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.                                 | Sym  | Characteristic                                                   | Min                                                                                                                                                                                     | Тур† | Max               | Units       | Conditions                                                                             |  |  |  |