Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

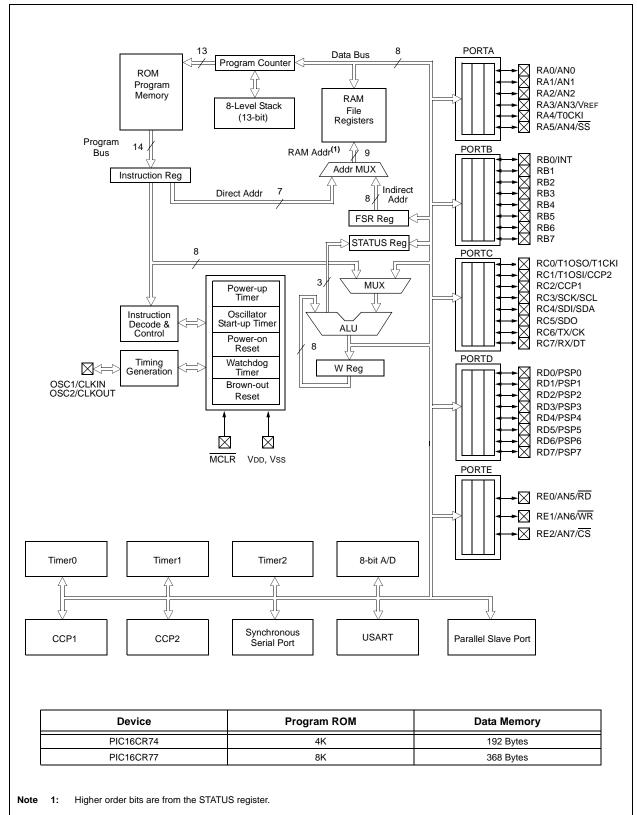

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | ROM                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr74-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| D) |

|----|

|    |

| Pin Name          | PDIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type | Description                                                 |

|-------------------|------------------------------|-------------|---------------|----------------|-------------------------------------------------------------|

|                   |                              |             |               |                | PORTC is a bidirectional I/O port.                          |

| RC0/T1OSO/T1CKI   | 11                           | 8           |               | ST             |                                                             |

| RC0               |                              |             | I/O           |                | Digital I/O.                                                |

| T1OSO             |                              |             | 0             |                | Timer1 oscillator output.                                   |

| T1CKI             |                              |             | I             |                | Timer1 external clock input.                                |

| RC1/T1OSI/CCP2    | 12                           | 9           |               | ST             |                                                             |

| RC1               | . –                          | -           | I/O           |                | Digital I/O.                                                |

| T1OSI             |                              |             | 1             |                | Timer1 oscillator input.                                    |

| CCP2              |                              |             | I/O           |                | Capture2 input, Compare2 output, PWM2 output.               |

| RC2/CCP1          | 13                           | 10          |               | ST             |                                                             |

| RC2               |                              |             | I/O           | 0.             | Digital I/O.                                                |

| CCP1              |                              |             | I/O           |                | Capture1 input/Compare1 output/PWM1 output.                 |

| RC3/SCK/SCL       | 14                           | 11          |               | ST             |                                                             |

| RC3               | 17                           |             | I/O           | 01             | Digital I/O.                                                |

| SCK               |                              |             | 1/O           |                | Synchronous serial clock input/output for SPI mode.         |

| SCL               |                              |             | I/O           |                | Synchronous serial clock input/output for $l^2C^{TM}$ mode. |

| RC4/SDI/SDA       | 15                           | 12          | ., C          | ST             |                                                             |

| RC4               | 15                           | 12          | I/O           | 51             | Digital I/O.                                                |

| SDI               |                              |             | 1/0<br>I      |                | SPI data in.                                                |

| SDA               |                              |             | I/O           |                | $I^2 C^{TM}$ data I/O.                                      |

| RC5/SDO           | 16                           | 13          | 1, 0          | ST             |                                                             |

| RC5               | 10                           | 15          | I/O           | 51             | Digital I/O.                                                |

| SDO               |                              |             | 0             |                | SPI data out.                                               |

| RC6/TX/CK         | 17                           | 14          | Ŭ             | ST             |                                                             |

| RC6               | 17                           | 14          | I/O           | 31             | Digital I/O.                                                |

| TX                |                              |             | 0             |                | USART asynchronous transmit.                                |

| CK                |                              |             | 1/O           |                | USART 1 synchronous clock.                                  |

| RC7/RX/DT         | 18                           | 15          | "             | ST             |                                                             |

| RC7/RX/D1<br>RC7  | 10                           | 10          | I/O           | 31             | Digital I/O.                                                |

| RX                |                              |             | 1             |                | USART asynchronous receive.                                 |

| DT                |                              |             | 1/O           |                | USART synchronous data.                                     |

| Vss               | 8, 19                        | 5, 16       | .,,е<br>Р     |                | Ground reference for logic and I/O pins.                    |

| VDD               | 20                           | 17          | P             |                | Positive supply for logic and I/O pins.                     |

| Legend: I = input |                              | D = output  |               | O = input/out  |                                                             |

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name        | PDIP<br>Pin# | PLCC<br>Pin#    | QFP<br>Pin#      | I/O/P<br>Type | Buffer<br>Type        | Description                                                                     |

|-----------------|--------------|-----------------|------------------|---------------|-----------------------|---------------------------------------------------------------------------------|

|                 |              |                 |                  |               |                       | PORTD is a bidirectional I/O port or parallel slave port                        |

|                 |              |                 |                  |               |                       | when interfacing to a microprocessor bus.                                       |

| RD0/PSP0        | 19           | 21              | 38               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD0<br>PSP0     |              |                 |                  | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                       |

|                 | 20           | 00              | 20               |               | ST/TTL <sup>(3)</sup> | Paraller Slave Port data.                                                       |

| RD1/PSP1<br>RD1 | 20           | 22              | 39               | I<br>I/O      | 51/1124               | Digital I/O.                                                                    |

| PSP1            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD2/PSP2        | 21           | 23              | 40               | 1             | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD2             |              |                 |                  | I/O           | 0.,                   | Digital I/O.                                                                    |

| PSP2            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD3/PSP3        | 22           | 24              | 41               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD3             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP3            |              |                 |                  | I/O           | (2)                   | Parallel Slave Port data.                                                       |

| RD4/PSP4        | 27           | 30              | 2                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD4<br>PSP4     |              |                 |                  | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                       |

| -               | 20           | 24              | 2                | 1/0           | ST/TTL <sup>(3)</sup> | Paraller Slave Port data.                                                       |

| RD5/PSP5<br>RD5 | 28           | 31              | 3                | I/O           | 51/1124               | Digital I/O.                                                                    |

| PSP5            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD6/PSP6        | 29           | 32              | 4                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD6             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP6            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD7/PSP7        | 30           | 33              | 5                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD7             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP7            | _            |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

|                 |              |                 |                  |               | (2)                   | PORTE is a bidirectional I/O port.                                              |

| RE0/AN5/RD/     | 8            | 9               | 25               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE0<br>AN5      |              |                 |                  | I/O<br>I      |                       | Digital I/O.<br>Analog input 5.                                                 |

|                 |              |                 |                  | 1             |                       | Read control for parallel slave port .                                          |

| RE1/AN6/WR/     | 9            | 10              | 26               | -             | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE1             | °,           |                 |                  | I/O           | 0.,                   | Digital I/O.                                                                    |

| AN6             |              |                 |                  | I             |                       | Analog input 6.                                                                 |

| WR              |              |                 |                  | I             |                       | Write control for parallel slave port .                                         |

| RE2/AN7/CS      | 10           | 11              | 27               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE2             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| AN7<br>CS       |              |                 |                  |               |                       | Analog input 7.<br>Chip Select control for parallel slave port .                |

| Vss             | 12,31        | 13,34           | 6,29             | P             |                       | Ground reference for logic and I/O pins.                                        |

| VSS<br>VDD      | 12,31        | 12,35           | 7,28             | <br>Р         |                       | Positive supply for logic and I/O pins.                                         |

| NC              | 11,52        |                 |                  | Г             |                       |                                                                                 |

|                 |              | 1,17,<br>28, 40 | 12,13,<br>33, 34 |               |                       | These pins are not internally connected. These pins should be left unconnected. |

#### TABLE 1-3: PIC16CR74 AND PIC16CR77 PINOUT DESCRIPTION (CONTINUED)

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The Program Memory can be read internally by user code (see Section 3.0 "Reading Program Memory").

Additional information on device memory may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

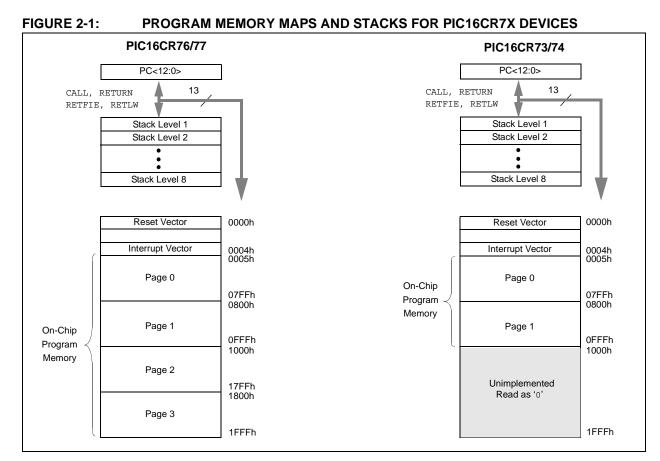

## 2.1 Program Memory Organization

The PIC16CR7X devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16CR77/76 devices have 8K words of ROM program memory and the PIC16CR73/74 devices have 4K words. The program memory maps for PIC16CR7X devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits:

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file (shown in Figure 2-2 and Figure 2-3) can be accessed either directly, or indirectly, through the File Select Register (FSR).

# PIC16CR7X

NOTES:

## 3.0 READING PROGRAM MEMORY

The ROM Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the ROM location being accessed. These devices can have up to 8K words of program ROM, with an address range from 0h to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as '0's.

## 3.1 PMADR

The address registers can address up to a maximum of 8K words of program ROM.

When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADR register. The upper MSb's of PMADRH must always be clear.

## 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

### REGISTER 3-1: PMCON1: (ADDRESS 18Ch)

| R-1      | U-0 | U-0 | U-0 | U-x | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| reserved | —   | —   | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Reserved: Read as '1' |

|-------|-----------------------|

|-------|-----------------------|

bit 6-1 **Unimplemented**: Read as '0'

bit 0 **RD**: Read Control bit

1 = Initiates a ROM read, RD is cleared in hardware. The RD bit can only be set (not cleared) in software.

0 = ROM read completed

| Name    | Bit#  | Buffer                | Function                                                                                   |

|---------|-------|-----------------------|--------------------------------------------------------------------------------------------|

| RB0/INT | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up. |

| RB1     | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                             |

| RB2     | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                             |

| RB3     | bit 3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                             |

| RB4     | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

| RB5     | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

| RB6     | bit 6 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

| RB7     | bit 7 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

## TABLE 4-3: PORTB FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

| TABLE 4-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address   | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------|------------|---------|-------------------------------|-------|-------|-------|-------|-----------|-----------|-------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1       | RB0       | XXXX XXXX               | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB [ | PORTB Data Direction Register |       |       |       |       | 1111 1111 | 1111 1111 |                         |                                 |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                        | TOCS  | TOSE  | PSA   | PS2   | PS1       | PS0       | 1111 1111               | 1111 1111                       |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

## 4.4 PORTD and TRISD Registers

This section is not applicable to the PIC16CR73 or PIC16CR76.

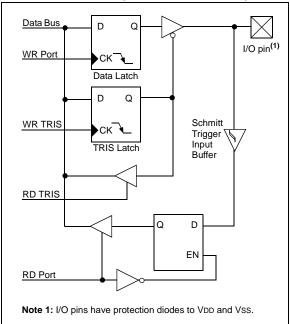

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 4-6: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit#  | Buffer Type           | Function                                           |  |

|----------|-------|-----------------------|----------------------------------------------------|--|

| RD0/PSP0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 0 |  |

| RD1/PSP1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 1 |  |

| RD2/PSP2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 2 |  |

| RD3/PSP3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 3 |  |

| RD4/PSP4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 4 |  |

| RD5/PSP5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 5 |  |

| RD6/PSP6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 6 |  |

| RD7/PSP7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit   |  |

### TABLE 4-7:PORTD FUNCTIONS

**Legend:** ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-8: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address | Name  | Bit 7                                                                               | Bit 6                                        | Bit 5 | Bit 4                                                   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|-------------------------------------------------------------------------------------|----------------------------------------------|-------|---------------------------------------------------------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 08h     | PORTD | RD7                                                                                 | RD6                                          | RD5   | RD4                                                     | RD3   | RD2   | RD1   | RD0   | xxxx xxxx               | uuuu uuuu                       |

| 88h     | TRISD | PORT                                                                                | PORTD Data Direction Register 1111 1111 1111 |       |                                                         |       |       |       |       |                         | 1111 1111                       |

| 89h     | TRISE | IBF                                                                                 | OBF                                          | IBOV  | V PSPMODE - PORTE Data Direction bits 0000 -111 0000 -1 |       |       |       |       |                         | 0000 -111                       |

| Logondu |       | unknown w - unchanged unimplemented read as (a). Shaded calls are not used by DOPTD |                                              |       |                                                         |       |       |       |       |                         |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and

#### **REGISTER 5-1: OPTION REG:**

bit 7

bit 7

bit 6

bit 5

bit 4

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU TOCS T0SE PS2 INTEDG PSA PS1 PS0 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown RBPU: PORTB Pull-up Enable bit (see Section 2.2.2.2 "OPTION\_REG Register") INTEDG: Interrupt Edge Select bit (see Section 2.2.2. "OPTION\_REG Register") TOCS: TMR0 Clock Source Select bit 1 = Transition on TOCKI pin 0 = Internal instruction cycle clock (CLKOUT) TOSE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

- bit 3 PSA: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

- bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1 : 256   | 1 : 128  |

|           |           |          |

Note: To avoid an unintended device Reset, the instruction sequences shown in Example 5-1 and Example 5-2 must be executed when changing the prescaler assignment between Timer0 and the WDT. This sequence must be followed even if the WDT is disabled.

Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

## 5.3 Prescaler

There is only one prescaler available on the microcontroller; it is shared exclusively between the Timer0 module and the Watchdog Timer. The usage of the prescaler is also mutually exclusive: that is, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio. Examples of code for assigning the prescaler assignment are shown in Example 5-1 and Example 5-2. Note that when the prescaler is being assigned to the WDT with ratios other than 1:1, lines 2 and 3 (high-lighted) are optional. If a prescale ratio of 1:1 is used, however, these lines must be used to set a temporary

value. The final 1:1 value is then set in lines 10 and 11 (highlighted). (Line numbers are included in the example for illustrative purposes only, and are not part of the actual code.)

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### EXAMPLE 5-1: CHANGING THE PRESCALER ASSIGNMENT FROM TIMER0 TO WDT

| 1)  | BSF    | STATUS, RPO | ; | Bank1                                     |

|-----|--------|-------------|---|-------------------------------------------|

| 2)  | MOVLW  | b'xx0x0xxx' | ; | Select clock source and prescale value of |

| 3)  | MOVWF  | OPTION_REG  | ; | other than 1:1                            |

| 4)  | BCF    | STATUS, RPO | ; | Bank0                                     |

| 5)  | CLRF   | TMR0        | ; | Clear TMR0 and prescaler                  |

| 6)  | BSF    | STATUS, RP1 | ; | Bank1                                     |

| 7)  | MOVLW  | b'xxxx1xxx' | ; | Select WDT, do not change prescale value  |

| 8)  | MOVWF  | OPTION_REG  |   |                                           |

| 9)  | CLRWDT |             | ; | Clears WDT and prescaler                  |

| 10) | MOVLW  | b'xxxx1xxx' | ; | Select new prescale value and WDT         |

| 11) | MOVWF  | OPTION_REG  |   |                                           |

| 12) | BCF    | STATUS, RPO | ; | Bank0                                     |

### EXAMPLE 5-2: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0

| CLRWDT |             | ; | Clear WDT and prescaler   |

|--------|-------------|---|---------------------------|

| BSF    | STATUS, RPO | ; | Bank1                     |

| MOVLW  | b'xxxx0xxx' | ; | Select TMR0, new prescale |

| MOVWF  | OPTION_REG  | ; | value and clock source    |

| BCF    | STATUS, RPO | ; | Bank0                     |

|        |             |   |                           |

### TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6                 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|--------|-----------------------|--------|-------|-------|--------|-------|-------|-------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | imer0 Module Register |        |       |       |        |       |       | xxxx xxxx               | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE                  | TMR0IE | INTE  | RBIE  | TMR0IF | INTF  | RBIF  | 0000 000x               | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG                | TOCS   | TOSE  | PSA   | PS2    | PS1   | PS0   | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

## 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 and CCP2 special event triggers.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

|          | Frequency | Capacito | ors Used: |  |  |  |  |  |

|----------|-----------|----------|-----------|--|--|--|--|--|

| Osc Type | Frequency | OSC1     | OSC2      |  |  |  |  |  |

| LP       | 32 kHz    | 47 pF    | 47 pF     |  |  |  |  |  |

|          | 100 kHz   | 33 pF    | 33 pF     |  |  |  |  |  |

|          | 200 kHz   | 15 pF    | 15 pF     |  |  |  |  |  |

|          |           |          |           |  |  |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

| e notes (below) table for additional information. |

|---------------------------------------------------|

|---------------------------------------------------|

| Commonly Used Crystals: |                                                                                                           |  |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 32.768 kHz              | Epson C-001R32.768K-A                                                                                     |  |  |  |  |  |  |

| 100 kHz                 | Epson C-2 100.00 KC-P                                                                                     |  |  |  |  |  |  |

| 200 kHz                 | STD XTL 200.000 kHz                                                                                       |  |  |  |  |  |  |

| 0                       | Higher capacitance increases the stability<br>of the oscillator, but also increases the<br>start-up time. |  |  |  |  |  |  |

| c<br>tł<br>a            | · · · · · · · ·                                                                                           |  |  |  |  |  |  |

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name   | Bit 7                | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|--------|----------------------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                                        | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 0Eh                   | TMR1L  | Holding Reg          | lolding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |        | xxxx xxxx               | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding Reg          | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |         |         |         |        |        |        | xxxx xxxx               | uuuu uuuu                       |

| 10h                   | T1CON  | —                    | _                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00 0000                 | uu uuuu                         |

### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

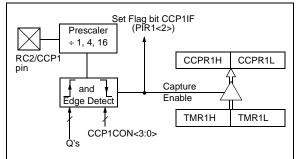

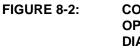

## 8.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

### 8.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |

|-------|-----------------------------------------|

|       | output, a write to the port can cause a |

|       | capture condition.                      |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

### 8.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module | off     |

|-------|-------------|------------------|---------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg  | with    |

|       |             | the new prescal; | er      |

|       |             | ;move value and  | CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON wi | th this |

|       |             | ;value           |         |

|       |             |                  |         |

## 8.4 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit TMR1F (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

## 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

## 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

## 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

## 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and an appropriate acquisition time should pass before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address                | Name                 | Bit 7                | Bit 6      | Bit 5   | Bit 4         | Bit 3    | Bit 2    | Bit 1       | Bit 0   | PC   | e on<br>DR,<br>DR | all o | e on<br>ther<br>sets |

|------------------------|----------------------|----------------------|------------|---------|---------------|----------|----------|-------------|---------|------|-------------------|-------|----------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON               | GIE                  | PEIE       | TMR0IE  | INTE          | RBIE     | TMR0IF   | INTF        | RBIF    | 0000 | 000x              | 0000  | 000u                 |

| 0Ch                    | PIR1                 | PSPIF <sup>(1)</sup> | ADIF       | RCIF    | TXIF          | SSPIF    | CCP1IF   | TMR2IF      | TMR1IF  | 0000 | 0000              | 0000  | 0000                 |

| 0Dh                    | PIR2                 | _                    |            | —       | _             | _        | —        | _           | CCP2IF  |      | 0                 |       | 0                    |

| 8Ch                    | PIE1                 | PSPIE <sup>(1)</sup> | ADIE       | RCIE    | TXIE          | SSPIE    | CCP1IE   | TMR2IE      | TMR1IE  | 0000 | 0000              | 0000  | 0000                 |

| 8Dh                    | PIE2                 | _                    |            |         | _             |          |          |             | CCP2IE  |      | 0                 |       | 0                    |

| 1Eh                    | ADRES                | A/D Resu             | It Registe | er Byte |               |          |          |             |         | xxxx | xxxx              | uuuu  | uuuu                 |

| 1Fh                    | ADCON0               | ADCS1                | ADCS0      | CHS2    | CHS1          | CHS0     | GO/DONE  | _           | ADON    | 0000 | 0 - 0 0           | 0000  | 00-0                 |

| 9Fh                    | ADCON1               | _                    |            |         | _             | _        | PCFG2    | PCFG1       | PCFG0   |      | -000              |       | -000                 |

| 05h                    | PORTA                | —                    | —          | RA5     | RA4           | RA3      | RA2      | RA1         | RA0     | 0x   | 0000              | 0u    | 0000                 |

| 85h                    | TRISA                | —                    | —          | PORTA I | Data Directio | n Regist | er       |             |         | 11   | 1111              | 11    | 1111                 |

| 09h                    | PORTE <sup>(2)</sup> | _                    | _          | _       | _             | _        | RE2      | RE1         | RE0     |      | -xxx              |       | -uuu                 |

| 89h                    | TRISE <sup>(2)</sup> | IBF                  | OBF        | IBOV    | PSPMODE       |          | PORTE Da | ta Directio | on Bits | 0000 | -111              | 0000  | -111                 |

TABLE 11-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

2: These registers are reserved on the PIC16CR73/76.

## 12.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if

| TABLE 12-3: TIVIE-OUT IN VARIOUS SITUATIONS | TABLE 12-3: | TIME-OUT IN VARIOUS SITUATIONS |

|---------------------------------------------|-------------|--------------------------------|

|---------------------------------------------|-------------|--------------------------------|

bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit 1 is  $\overrightarrow{POR}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Ossillator Configuration | Power              | -up       | Drawn aut         | Wake-up from |  |

|--------------------------|--------------------|-----------|-------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0PWRTE = 1 |           | Brown-out         | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024 Tosc  | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc    |  |

| RC                       | 72 ms              | —         | 72 ms             | —            |  |

## TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR<br>(PCON<1>) | BOR<br>(PCON<0>) | TO<br>(STATUS<4>) | PD<br>(STATUS<3>) | Significance                                            |

|------------------|------------------|-------------------|-------------------|---------------------------------------------------------|

| 0                | x                | 1                 | 1                 | Power-on Reset                                          |

| 0                | х                | 0                 | x                 | Illegal, TO is set on POR                               |

| 0                | х                | x                 | 0                 | Illegal, PD is set on POR                               |

| 1                | 0                | 1                 | 1                 | Brown-out Reset                                         |

| 1                | 1                | 0                 | 1                 | WDT Reset                                               |

| 1                | 1                | 0                 | 0                 | WDT Wake-up                                             |

| 1                | 1                | u                 | u                 | MCLR Reset during normal operation                      |

| 1                | 1                | 1                 | 0                 | MCLR Reset during Sleep or interrupt wake-up from Sleep |

## TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| FIGURE 12-12                                       | : WAKI                    |                                         | <b>I SLEEP THR</b>                             | OUGH INTER                 | RUPT                                                |                       |                            |

|----------------------------------------------------|---------------------------|-----------------------------------------|------------------------------------------------|----------------------------|-----------------------------------------------------|-----------------------|----------------------------|

| _Q<br>OSC1 /<br>CLKOUT <sup>(4)</sup> /<br>INT pin | 1  Q2  Q3  Q4;<br>//<br>/ | Q1  Q2  Q3  Q4<br>\                     |                                                |                            | Q1 Q2 Q3 Q4<br>//////////////////////////////////// | Q1  Q2  Q3  Q4; (<br> | 21  Q2  Q3  Q4;<br>\/_\/\/ |

| INTF Flag<br>(INTCON<1>)<br>GIE bit<br>(INTCON<7>) |                           |                                         | Processor in<br>Sleep                          | 1<br>1<br>1<br>1<br>1<br>1 | Interrupt Latency<br>(Note 2)                       |                       | י<br>                      |

| INSTRUCTION FL                                     | .OW                       |                                         |                                                | :                          | i i                                                 | 1                     | 1                          |

| PC X                                               | PC X                      | PC + 1                                  | X PC + 2                                       | X PC + 2                   | X PC + 2                                            | <u>0004h X</u>        | 0005h                      |

| Instruction { Ins                                  | st(PC) = Sleep            | Inst(PC + 1)                            |                                                | Inst(PC + 2)               | , ,<br>, , , , ,<br>, , , , ,                       | Inst(0004h)           | Inst(0005h)                |

| Instruction {<br>Executed                          | Inst(PC - 1)              | Sleep                                   | 1<br>1<br>1                                    | Inst(PC + 1)               | Dummy cycle                                         | Dummy cycle           | Inst(0004h)                |

| 2: Tost<br>3: GIE                                  | •                         | Irawing not to so<br>In this case, afte | ale) This delay will n<br>r wake-up, the proce |                            |                                                     |                       |                            |

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been enabled, the on-chip program memory can be read out for verification purposes.

## 12.16 ID Locations

Four memory locations (2000h-2002h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable for program verification. It is recommended that only the 4 Least Significant bits of the ID location are used.

## 12.17 User Code

PIC16CR7X microcontrollers are ROM-based, thus user programming is not possible. Please contact your Microchip sales representitive for details on how to submit your final code. This information can also be found in Application Note AN1010, "PIC16CR *ROM Code Submission Process*".

## 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

## 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

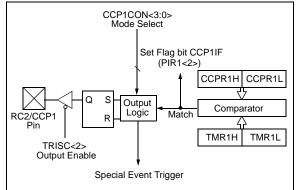

### TABLE 15-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol   | Characte                     | ristic       | Min | Тур† | Max | Units | Conditions |

|--------------|----------|------------------------------|--------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &          | Standard(5V) |     |      |     |       |            |

|              |          | <u>SLAVE)</u>                |              | —   | —    | 80  | ns    |            |

|              |          | Clock high to data out valid | Extended(3V) | _   | -    | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall | Standard(5V) |     | _    | 45  | ns    |            |

|              |          | time (Master mode)           | Extended(3V) |     | _    | 50  | ns    |            |

| 122          | Tdtrf    | Data out rise time and fall  | Standard(5V) |     | _    | 45  | ns    |            |

|              |          | time                         | Extended(3V) | _   | _    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

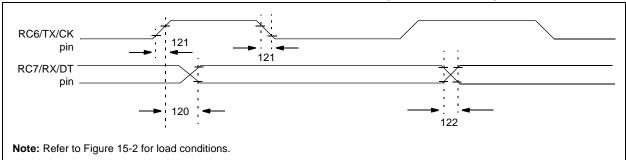

### FIGURE 15-17: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 15-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Symbol   | Characteristic                                                     | Min | Тур† | Max | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              |          | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK↓ (DT setup time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                     | 15  | _    | —   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## **17.0 PACKAGING INFORMATION**

## 17.1 Package Marking Information

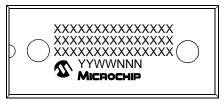

#### 28-Lead PDIP

#### 40-Lead PDIP

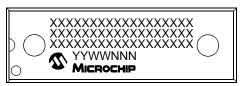

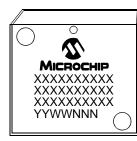

#### 44-Lead PLCC

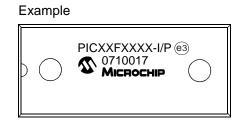

## Example

#### Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                  | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ł       | In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | X /XX XXX<br>Temperature Package Pattern<br>Range                                                        | Examples:                                                                                                                             |

|-----------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Device:               | PIC16CR73<br>PIC16CR74<br>PIC16CR76<br>PIC16CR77                                                         |                                                                                                                                       |

| Temperature<br>Range: | $I = -40^{\circ}C \text{ to } +85^{\circ}C  (Industrial)$<br>E = -40^{\circ}C to+125^{\circ}C (Extended) |                                                                                                                                       |

| Package:              | PT = TQFP (Thin Quad Flatpack)<br>L = PLCC<br>SO = SOIC<br>SP = Skinny Plastic DIP<br>P = PDIP           | <ul> <li>Note1: F = Standard Voltage Range<br/>LF = Wide Voltage Range</li> <li>2: T = in tape and reel PLCC, and<br/>TQFP</li> </ul> |

| Pattern:              | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                | packages only.                                                                                                                        |