Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ROM                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr74-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

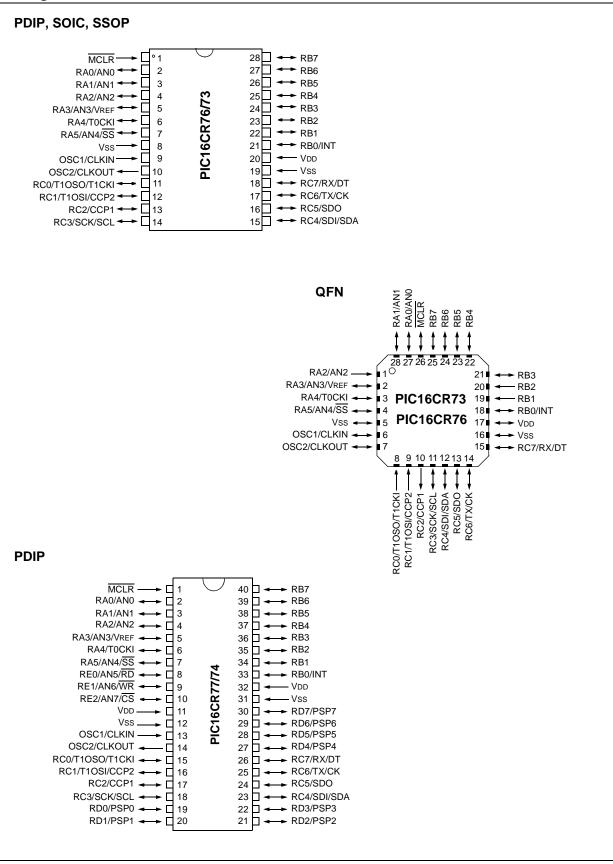

## **Pin Diagrams**

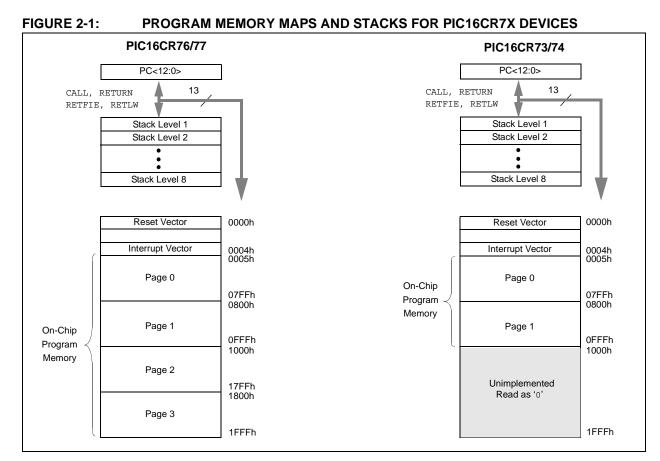

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The Program Memory can be read internally by user code (see Section 3.0 "Reading Program Memory").

Additional information on device memory may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

## 2.1 Program Memory Organization

The PIC16CR7X devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16CR77/76 devices have 8K words of ROM program memory and the PIC16CR73/74 devices have 4K words. The program memory maps for PIC16CR7X devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits:

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file (shown in Figure 2-2 and Figure 2-3) can be accessed either directly, or indirectly, through the File Select Register (FSR).

## 3.0 READING PROGRAM MEMORY

The ROM Program Memory is readable during normal operation over the entire VDD range. It is indirectly addressed through Special Function Registers (SFR). Up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that forms an invalid instruction results in a NOP.

There are five SFRs used to read the program and memory. These registers are:

- PMCON1

- PMDATA

- PMDATH

- PMADR

- PMADRH

The program memory allows word reads. Program memory access allows for checksum calculation and reading calibration tables.

When interfacing to the program memory block, the PMDATH:PMDATA registers form a two-byte word, which holds the 14-bit data for reads. The PMADRH:PMADR registers form a two-byte word, which holds the 13-bit address of the ROM location being accessed. These devices can have up to 8K words of program ROM, with an address range from 0h to 3FFFh. The unused upper bits in both the PMDATH and PMADRH registers are not implemented and read as '0's.

## 3.1 PMADR

The address registers can address up to a maximum of 8K words of program ROM.

When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADR register. The upper MSb's of PMADRH must always be clear.

## 3.2 PMCON1 Register

PMCON1 is the control register for memory accesses.

The control bit RD initiates read operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the read operation.

## REGISTER 3-1: PMCON1: (ADDRESS 18Ch)

| R-1      | U-0 | U-0 | U-0 | U-x | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| reserved | —   | —   | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Reserved: Read as '1' |

|-------|-----------------------|

|-------|-----------------------|

bit 6-1 **Unimplemented**: Read as '0'

bit 0 **RD**: Read Control bit

1 = Initiates a ROM read, RD is cleared in hardware. The RD bit can only be set (not cleared) in software.

0 = ROM read completed

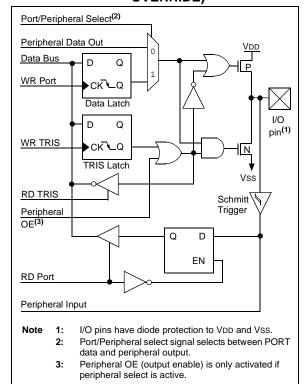

## 4.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impendance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 4-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings, and to **Section 13.1 "READ-MOD-IFY-WRITE OPERATIONS"** for additional information on read-modify-write operations.

### FIGURE 4-5:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

| Name            | Bit#  | Buffer Type | Function                                                                                            |

|-----------------|-------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit 0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit 1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit 2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output.                                |

| RC3/SCK/SCL     | bit 3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2 C^{{\mbox{\tiny TM}}}$ modes.    |

| RC4/SDI/SDA     | bit 4 | ST          | RC4 can also be the SPI Data In (SPI mode) or Data I/O (I <sup>2</sup> C <sup>™</sup> mode).        |

| RC5/SDO         | bit 5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |

| RC6/TX/CK       | bit 6 | ST          | Input/output port pin or USART Asynchronous Transmit or<br>Synchronous Clock.                       |

| RC7/RX/DT       | bit 7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                            |

## TABLE 4-5: PORTC FUNCTIONS

**Legend:** ST = Schmitt Trigger input

## TABLE 4-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                                             | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|-------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                                               | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx               | uuuu uuuu                       |

| 87h     | TRISC | PORTC | PORTC Data Direction Register 1111 1111 1111 1111 |       |       |       |       |       |       |                         |                                 |

**Legend:** x = unknown, u = unchanged

## 6.1 Timer1 Operation in Timer Mode

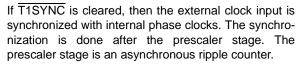

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

## 6.2 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

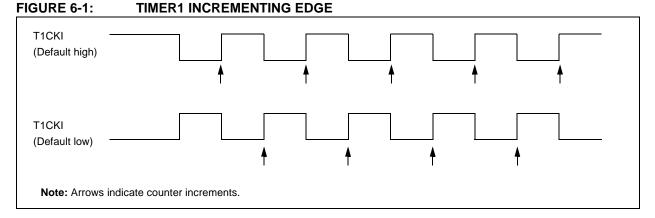

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

## 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

## FIGURE 6-2: TIMER1 BLOCK DIAGRAM

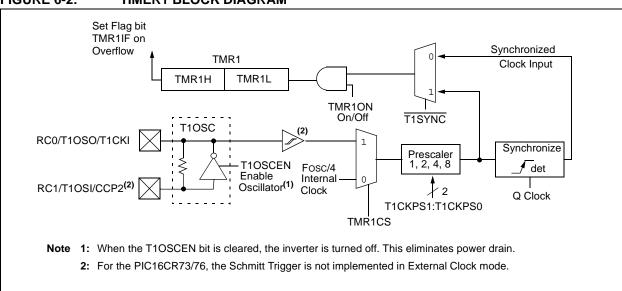

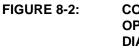

## 8.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

## 8.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |  |  |

|-------|-----------------------------------------|--|--|

|       | output, a write to the port can cause a |  |  |

|       | capture condition.                      |  |  |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

## 8.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ;the new prescaler      |

|       |             | ;move value and CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ;value                  |

|       |             |                         |

## 8.4 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit TMR1F (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

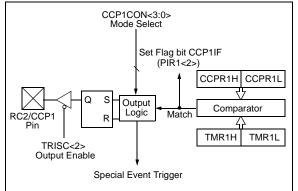

## 8.5 PWM Mode (PWM)

FIGURE 8-3:

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 8.5.3** "**SetUp for PWM Operation**".

SIMPLIFIED PWM BLOCK

|                | D                             | DIAGRAM                                 |

|----------------|-------------------------------|-----------------------------------------|

| Duty Cycle Reg | isters                        | CCP1CON<5:4>                            |

| CCPR1L         |                               | $\leftarrow$                            |

|                | (1)<br>Clear<br>CCP1<br>latch | is concatenated with the 2-bit inter-   |

|                | ime base                      | e 2 bits of the prescaler to create the |

A PWM output (Figure 8-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =  $[(PR2) + 1] \cdot 4 \cdot TOSC \cdot$

(TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

## 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

|           | 0,                                                                                                                  |

|-----------|---------------------------------------------------------------------------------------------------------------------|

| Resolutio | $\operatorname{pn} = \frac{\log\left(\frac{\operatorname{Fosc}}{\operatorname{FpWM}}\right)}{\log(2)} \text{ bits}$ |

| Note:     | If the PWM duty cycle value is longer than<br>the PWM period, the CCP1 pin will not be<br>cleared.                  |

Note: The Timer2 postscaler (see Section 8.3 "Capture Mode") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

# PIC16CR7X

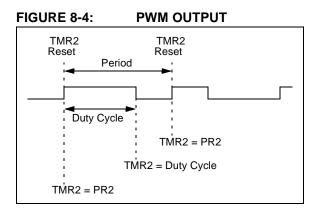

#### FIGURE 9-1: SSP BLOCK DIAGRAM (SPI MODE)

To enable the serial port, SSP enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and ADCON must be configured such that RA5 is a digital I/O

Note 1: When the SPI is in Slave mode with  $\overline{SS}$ pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$ pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = '1', then the  $\overline{SS}$  pin control must be enabled.

- 3: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = '0100'), the state of the  $\overline{SS}$  pin can affect the state read back from the TRISC<5> bit. The Peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<5> bit (see Section 4.3 "PORTC and the TRISC Register" for information on PORTC). If Read-Modify-Write instructions, such as BSF are performed on the TRISC register while the  $\overline{SS}$  pin is high, this will cause the TRISC<5> bit to be set, thus disabling the SDO output.

| Address                | Name                               | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|------------------------------------|----------------------|----------|------------|-------|-------|--------|-----------|-----------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                  | PEIE     | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF      | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000               | 0000 0000                       |

| 18h                    | RCSTA                              | SPEN                 | RX9      | SREN       | CREN  |       | FERR   | OERR      | RX9D      | 0000 000x               | 0000 000x                       |

| 19h                    | TXREG                              | USART Tr             | ansmit D | ata Regist | er    |       |        |           |           | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000               | 0000 0000                       |

| 98h                    | TXSTA                              | CSRC                 | TX9      | TXEN       | SYNC  |       | BRGH   | TRMT      | TX9D      | 0000 -010               | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                      |          |            |       |       |        | 0000 0000 | 0000 0000 |                         |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76 devices; always maintain these bits clear.

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

| Address                | Name                                   | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|----------------------------------------|----------------------|----------|------------|-------|-------|--------|--------|-----------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE     | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000               | 0000 0000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9      | SREN       | CREN  | —     | FERR   | OERR   | RX9D      | x000 000x               | 0000 000x                       |

| 1Ah                    | RCREG                                  | USART R              | eceive D | ata Regist | er    |       |        |        |           | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000               | 0000 0000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9      | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010               | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |          |            |       |       |        |        | 0000 0000 | 0000 0000               |                                 |

#### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

**Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16CR73/76 devices, always maintain these bits clear.

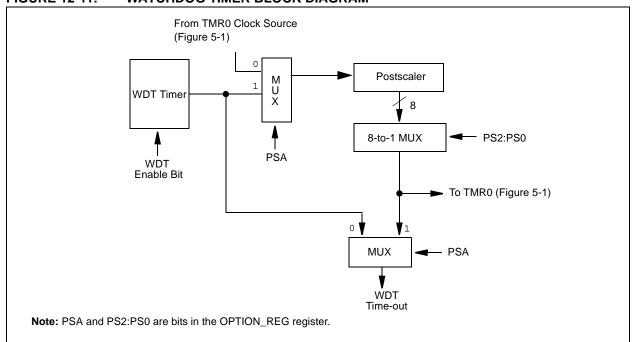

## 12.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing Configuration bit, WDTE (Section 12.1 "Configuration Bits").

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler), may be assigned using the OPTION\_REG register.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> |       | CP0   | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 12-1 for operation of these bits.

## 12.14 Power-down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or high-impendance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are high-impendance inputs, high or low externally, to avoid switching currents caused by floating inputs. The T0CKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

### 12.14.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a Peripheral Interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write (PIC16CR74/77 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode, using an external clock).

- 5. SSP (Start/Stop) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs, regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

## 12.14.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

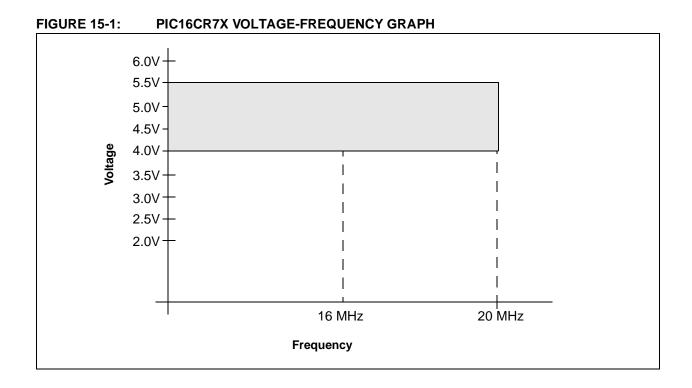

## 15.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                          | 55 to +125°C                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Storage temperature                                                                                                                                     | 65°C to +150°C                                     |

| Voltage on any pin with respect to Vss                                                                                                                  | 0.3V to (VDD + 0.3V)                               |

| Voltage on VDD with respect to Vss                                                                                                                      | 0.3 to +6.5V                                       |

| Voltage on MCLR with respect to Vss                                                                                                                     | 0 to +5.5V                                         |

| Voltage on RA4 with respect to Vss                                                                                                                      | 0 to +5.5V                                         |

| Total power dissipation (Note 1)                                                                                                                        | 1.0W                                               |

| Maximum current out of Vss pin                                                                                                                          | 300 mA                                             |

| Maximum current into VDD pin                                                                                                                            | 250 mA                                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                                            | ±20 mA                                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                                          | ±20 mA                                             |

| Maximum output current sunk by any I/O pin                                                                                                              | 25 mA                                              |

| Maximum output current sourced by any I/O pin                                                                                                           | 25 mA                                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                     | 200 mA                                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                  | 200 mA                                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                                             | 200 mA                                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                                          | 200 mA                                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VOH)                                        | $x \text{ IOH} + \sum (\text{VOI } x \text{ IOL})$ |

| 2: Voltage spikes at the MCLR pin may cause latch-up. A series resistor of greater than to pull MCLR to VDD, rather than tying the pin directly to VDD. | 1 k $\Omega$ should be used                        |

3: PORTD and PORTE are not implemented on the PIC16CR73/76 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16CR7X

## 15.1 DC Characteristics: PIC16CR73/74/76/77 (Industrial, Extended) (Continued)

| PIC16C<br>(Indus      | <b>R73/74/</b><br>trial, Ex |                                     |          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                      |                      |                                                                                                                                                                                                                                                                    |  |  |

|-----------------------|-----------------------------|-------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.          | Sym                         | Characteristic                      | Min      | Тур†                                                                                                                                                                                    | Max                  | Units                | Conditions                                                                                                                                                                                                                                                         |  |  |

|                       | Idd                         | Supply Current (Notes 2, 5          | i)       |                                                                                                                                                                                         |                      |                      |                                                                                                                                                                                                                                                                    |  |  |

| D010                  |                             | PIC16CR7X                           | _        | 0.5                                                                                                                                                                                     | 2                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                                                                                      |  |  |

| D010A                 |                             |                                     | —        | 20                                                                                                                                                                                      | 48                   | μA                   | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                                                                                    |  |  |

| D010                  |                             | PIC16CR7X                           |          | 1.1                                                                                                                                                                                     | 4                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                      |  |  |

| D013                  |                             |                                     | —        | 6.3                                                                                                                                                                                     | 15                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                  |  |  |

| D015*                 | $\Delta$ Ibor               | Brown-out<br>Reset Current (Note 6) |          | 30                                                                                                                                                                                      | 200                  | μA                   | BOR enabled, VDD = 5.0V                                                                                                                                                                                                                                            |  |  |

| D020                  | IPD                         | Power-down Current (Note            | es 3, 5) |                                                                                                                                                                                         |                      |                      |                                                                                                                                                                                                                                                                    |  |  |

| D021                  |                             | PIC16CR7X                           | _        | 2.0<br>0.1                                                                                                                                                                              | 30<br>5              | μΑ<br>μΑ             | VDD = $3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$                                                                                                                                      |  |  |

| D020<br>D021<br>D021A |                             | PIC16CR7X                           | <br>     | 5<br>0.1<br>10.5<br>1.5                                                                                                                                                                 | 42<br>19<br>57<br>42 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, $-40^{\circ}$ C to $+85^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-40^{\circ}$ C to $+85^{\circ}$ C<br>VDD = 4.0V, WDT enabled, $-40^{\circ}$ C to<br>$+125^{\circ}$ C<br>VDD = 4.0V, WDT disabled, $-40^{\circ}$ C to<br>$+125^{\circ}$ C |  |  |

| D023*                 | ΔIBOR                       | Brown-out<br>Reset Current (Note 6) |          | 30                                                                                                                                                                                      | 200                  | μA                   | BOR enabled, VDD = 5.0V                                                                                                                                                                                                                                            |  |  |

**Legend:** Shading of rows is to assist in readability of of the table.

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in active operation mode are:

<u>OSC1</u> = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impendance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

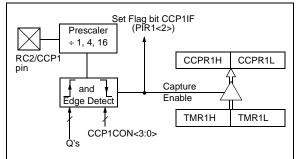

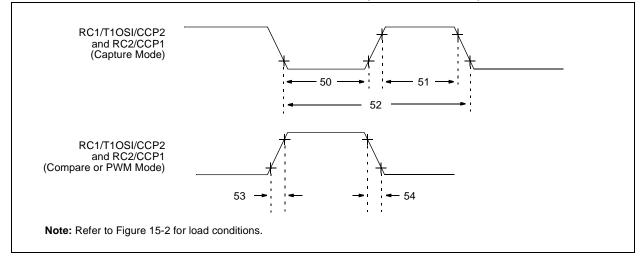

#### **FIGURE 15-8:** CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2) TABLE 15-5:

| Param<br>No. | Symbol                            |                    | Characteristic                |              |             | Тур† | Max | Units | Conditions                        |

|--------------|-----------------------------------|--------------------|-------------------------------|--------------|-------------|------|-----|-------|-----------------------------------|

| 50*          | TccL                              |                    |                               |              | 0.5Tcy + 20 | _    | —   | ns    |                                   |

|              |                                   | input low time     | Mith Due e e le s             | Standard(5V) | 10          | _    | _   | ns    |                                   |

|              |                                   |                    |                               | Extended(3V) | 20          | _    | _   | ns    |                                   |

| 51*          | * TccH CCP1 and CCP2 No Prescaler |                    |                               | 0.5Tcy + 20  |             |      | ns  |       |                                   |

|              |                                   | input high time    | With Prescaler                | Standard(5V) | 10          |      |     | ns    |                                   |

|              |                                   |                    |                               | Extended(3V) | 20          |      |     | ns    |                                   |

| 52*          | TccP                              | CCP1 and CCP2 i    | CP2 input period              |              |             |      |     | ns    | N = prescale<br>value (1,4 or 16) |

| 53*          | TccR                              | CCP1 and CCP2 of   | output rise time              | Standard(5V) | —           | 10   | 25  | ns    |                                   |

|              |                                   |                    |                               | Extended(3V) | —           | 25   | 50  | ns    |                                   |

| 54*          | TccF                              | CCP1 and CCP2 of   | CP1 and CCP2 output fall time |              | —           | 10   | 25  | ns    |                                   |

|              |                                   |                    |                               | Extended(3V) | —           | 25   | 45  | ns    |                                   |

| *            | These                             | parameters are cha | aracterized but r             | not tested   | •           | •    | •   |       |                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

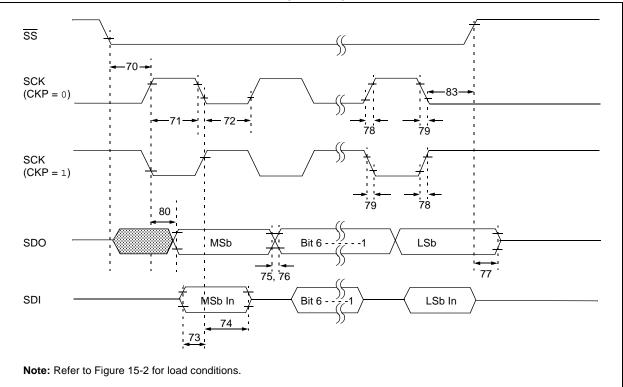

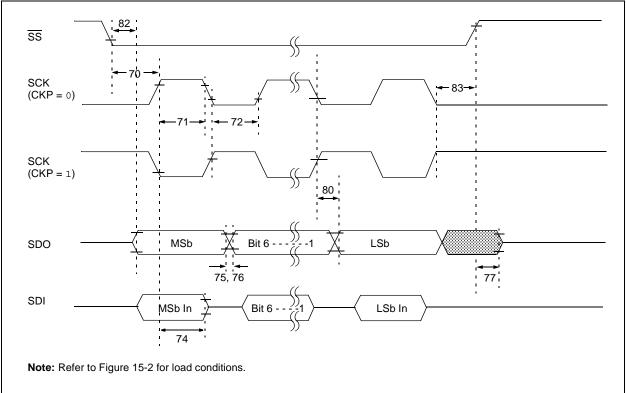

## FIGURE 15-13: SPI SLAVE MODE TIMING (CKE = 1)

| Param<br>No. | Symbol                | Characteristic                                                               | Min                                           | Тур†     | Max      | Units     | Conditions |  |

|--------------|-----------------------|------------------------------------------------------------------------------|-----------------------------------------------|----------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{\text{SS}}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү                                           | —        | —        | ns        |            |  |

| 71*          | TscH                  | SCK input high time (Slave mo                                                | de)                                           | TCY + 20 | —        |           | ns         |  |

| 72*          | TscL                  | SCK input low time (Slave mod                                                | le)                                           | TCY + 20 | —        | —         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to                                              | 100                                           | —        | _        | ns        |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                                      |                                               | 100      | _        |           | ns         |  |

| 75*          | TdoR                  | SDO data output rise time                                                    | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | —        | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO data output fall time                                                    | _                                             | 10       | 25       | ns        |            |  |

| 77*          | TssH2doZ              | SS <sup>↑</sup> to SDO output high-imper                                     | ndance                                        | 10       | —        | 50        | ns         |  |

| 78*          | TscR                  | SCK output rise time<br>(Master mode)                                        | Standard(5V)<br>Extended(3V)                  | _        | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK output fall time (Master m                                               | ode)                                          | _        | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after<br>SCK edge                                      | Standard(5V)<br>Extended(3V)                  | —        | _        | 50<br>145 | ns<br>ns   |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK                                                 | Тсу                                           | _        |          | ns        |            |  |

| 82*          | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge                   |                                               |          |          | 50        | ns         |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                          | 1.5Tcy + 40                                   | —        | —        | ns        |            |  |

#### TABLE 15-7: SPI MODE REQUIREMENTS

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

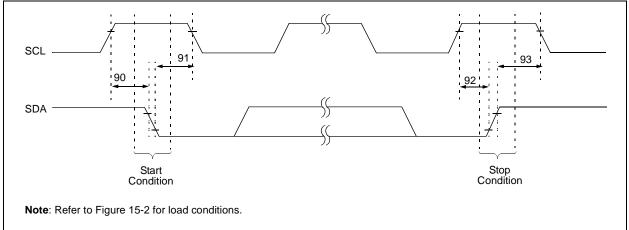

#### I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING FIGURE 15-14:

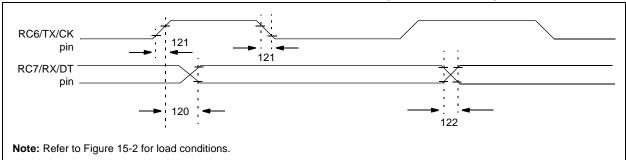

## TABLE 15-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol                                | Characteristic               |              | Min | Тур† | Max | Units | Conditions |

|--------------|---------------------------------------|------------------------------|--------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV                              | SYNC XMIT (MASTER &          | Standard(5V) |     |      |     |       |            |

|              |                                       | <u>SLAVE)</u>                |              | —   | —    | 80  | ns    |            |

|              | Clock high to data out valid          | Clock high to data out valid | Extended(3V) |     | _    | 100 | ns    |            |

| 121          | Tckrf                                 | Clock out rise time and fall | Standard(5V) |     | _    | 45  | ns    |            |

|              |                                       | time (Master mode)           | Extended(3V) |     | _    | 50  | ns    |            |

| 122          | 122 Tdtrf Data out rise time and fall |                              | Standard(5V) |     | _    | 45  | ns    |            |

|              |                                       | time                         | Extended(3V) | _   | _    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

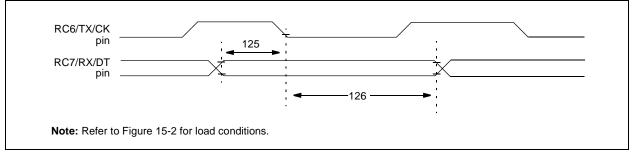

## FIGURE 15-17: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 15-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Symbol   | Characteristic                                                                | Min | Тур† | Max | Units | Conditions |

|------------------|----------|-------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              |          | <u>SYNC RCV (MASTER &amp; SLAVE)</u><br>Data setup before CK↓ (DT setup time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                | 15  | _    | —   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16CR7X

| SSPIF bit                                              |

|--------------------------------------------------------|

| SSPM<3:0> bits                                         |

| SSPOV bit61                                            |

| Stack                                                  |

| Overflows                                              |

| Underflow26                                            |

| STATUS Register                                        |

| DC Bit19                                               |

| IRP Bit19                                              |

| PD Bit                                                 |

| TO Bit                                                 |

| Z Bit19                                                |

| Synchronous Serial Port Enable bit (SSPEN)61           |

| Synchronous Serial Port Interrupt bit (SSPIF)23        |

| Synchronous Serial Port Mode Select bits (SSPM<3:0>)61 |

| Synchronous Serial Port. See SSP                       |

### Т

| T1CKPS0 bit                                 | 47    |

|---------------------------------------------|-------|

| T1CKPS1 bit                                 | 47    |

| T1OSCEN bit                                 |       |

| T1SYNC bit                                  | 47    |

| T2CKPS0 bit                                 | 52    |

| T2CKPS1 bit                                 | 52    |

| TAD                                         | 87    |

| Time-out Sequence                           | 94    |

| Timer0                                      | 43    |

| Associated Registers                        |       |

| Clock Source Edge Select (T0SE Bit)         |       |

| Clock Source Select (T0CS Bit)              |       |

| External Clock                              | 44    |

| Interrupt                                   |       |

| Overflow Enable (TMR0IE Bit)                | 21    |

| Overflow Flag (TMR0IF Bit)                  | 100   |

| Overflow Interrupt                          | 100   |

| Prescaler                                   |       |

| RA4/T0CKI Pin, External Clock               | 8, 10 |

| T0CKI                                       | 44    |

| Timer1                                      |       |

| Associated Registers                        | 50    |

| Asynchronous Counter Mode                   |       |

| Capacitor Selection                         |       |

| Counter Operation                           |       |

| Operation in Timer Mode                     | 48    |

| Oscillator                                  | 50    |

| Prescaler                                   | 50    |

| RC0/T1OSO/T1CKI Pin                         |       |

| RC1/T1OSI/CCP2 Pin                          |       |

| Resetting of Timer1 Registers               | 50    |

| Resetting Timer1 using a CCP Trigger Output |       |

| Synchronized Counter Mode                   |       |

| TMR1H Register                              |       |

| TMR1L Register                              | 49    |

| Timer2                                      |       |

| Associated Registers                        |       |

| Output                                      | 51    |

| Postscaler                                  | 51    |

| Prescaler                                   | 51    |

| Prescaler and Postscaler                    | 51    |

| Timing Diagrams                             |       |

| A/D Conversion                              | 137   |

| Brown-out Reset                             |       |

| Capture/Compare/PWM (CCP1 and CCP2)         |       |

| CLKOUT and I/O                              | 125   |

| External Clock                              |       |

| I <sup>2</sup> C Bus Data                   | 133   |

|                                             |       |

| I <sup>2</sup> C Bus Start/Stop Bits          | 132 |

|-----------------------------------------------|-----|

| I <sup>2</sup> C Reception (7-bit Address)    |     |

| I <sup>2</sup> C Transmission (7-bit Address) |     |

| Parallel Slave Port                           |     |

| Parallel Slave Port Read Waveforms            |     |

| Parallel Slave Port Write Waveforms           |     |

|                                               |     |

| Power-up Timer                                |     |

| PWM Output                                    |     |

| RESET                                         | 126 |

| Slow Rise Time (MCLR Tied to VDD              |     |

| Through RC Network)                           |     |

| SPI Master Mode (CKE = 0, SMP = 0)            |     |

| SPI Master Mode (CKE = 1, SMP = 1)            |     |

| SPI Mode (Master Mode)                        | 63  |

| SPI Mode (Slave Mode with CKE = 0)            | 63  |

| SPI Mode (Slave Mode with CKE = 1)            | 64  |

| SPI Slave Mode (CKE = 0)                      |     |

| SPI Slave Mode (CKE = 1)                      | 131 |

| Start-up Timer                                |     |

| Time-out Sequence on Power-up                 | 120 |

| (MCLR Not Tied to VDD)                        |     |

|                                               | ~~  |

| Case 1                                        |     |

| Case 2                                        | 98  |

| Time-out Sequence on Power-up                 |     |

| (MCLR Tied to VDD Through RC Network)         |     |

| Timer0                                        |     |

| Timer1                                        | 127 |

| USART Asynchronous Master Transmission        | 74  |

| USART Asynchronous Master Transmission        |     |

| (Back to Back)                                | 75  |

| USART Asynchronous Reception                  |     |

| USART Synchronous Receive (Master/Slave)      |     |

| USART Synchronous Reception                   | 100 |

| (Master Mode, SREN)                           | 80  |

| USART Synchronous Transmission                |     |

|                                               | 79  |

| USART Synchronous Transmission                | 405 |

| (Master/Slave)                                | 135 |

| USART Synchronous Transmission                |     |

| (Through TXEN)                                |     |

| Wake-up from Sleep via Interrupt              |     |

| Watchdog Timer                                |     |

| Timing Parameter Symbology                    | 123 |

| Timing Requirements                           |     |

| Capture/Compare/PWM (CCP1 and CCP2)           | 128 |

| CLKOUT and I/O                                |     |

| External Clock                                |     |

| I <sup>2</sup> C Bus Data                     |     |

| I2C Bus Start/Stop Bits                       |     |

| Parallel Slave Port                           |     |

|                                               | 129 |

| Reset, Watchdog Timer, Oscillator Start-up    | 400 |

| Timer, Power-up Timer and Brown-out Reset.    |     |

| SPI Mode                                      |     |

| Timer0 and Timer1 External Clock              |     |

| USART Synchronous Receive                     |     |

| USART Synchronous Transmission                | 135 |

| TMR1CS bit                                    | 47  |

| TMR10N bit                                    | 47  |

| TMR2ON bit                                    |     |

| TOUTPS<3:0> bits                              |     |

| TRISA Register                                |     |

| TRISB Register                                |     |

| TRISC Register                                |     |

| TRISC Register                                |     |

| INIOD NEGISIEI                                | 30  |

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Gumi** Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069 Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820