Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ROM                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr74t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

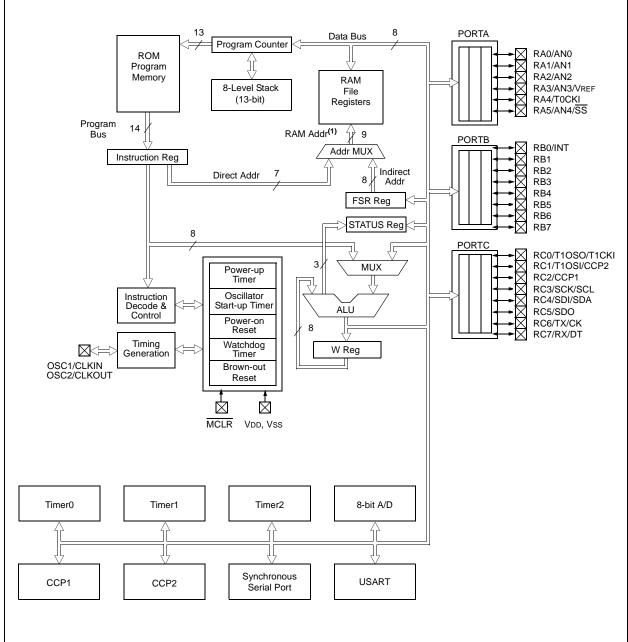

PIC16CR73 AND PIC16CR76 BLOCK DIAGRAM FIGURE 1-1: 13 8 Data Bus **Program Counter**

| Device    | Program ROM | Data Memory |

|-----------|-------------|-------------|

| PIC16CR73 | 4K          | 192 Bytes   |

| PIC16CR76 | 8K          | 368 Bytes   |

Higher order bits are from the STATUS register. Note

TABLE 1-2: PIC16CR73 AND PIC16CR76 PINOUT DESCRIPTION

| Pin Name            | PDIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                              |

|---------------------|------------------------------|-------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN<br>OSC1  | 9                            | 6           |               | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.                                                                                                                                                                              |

| CLKIN               |                              |             | l<br>I        |                        | Oscillator crystal input or external clock source input. ST buffer when configured in RC mode. Otherwise CMOS. External clock source input. Always associated with pin function OSC1 (see OSC1/CLKIN, OSC2/CLKOUT pins). |

| OSC2/CLKOUT<br>OSC2 | 10                           | 7           | 0             | _                      | Oscillator crystal or clock output.  Oscillator crystal output.  Connects to crystal or resonator in Crystal Oscillator mode.                                                                                            |

| CLKOUT              |                              |             | 0             |                        | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                                                                         |

| MCLR                | 1                            | 26          | I             | ST                     | Master Clear (Reset) input. This pin is an active low Reset to the device.                                                                                                                                               |

|                     | _                            |             |               |                        | PORTA is a bidirectional I/O port.                                                                                                                                                                                       |

| RAO/ANO             | 2                            | 27          | 1/0           | TTL                    | Digital I/O                                                                                                                                                                                                              |

| RA0<br>AN0          |                              |             | I/O<br>I      |                        | Digital I/O.<br>Analog input 0.                                                                                                                                                                                          |

| RA1/AN1             | 3                            | 28          | ·             | TTL                    | , maiog input of                                                                                                                                                                                                         |

| RA1                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                                                                             |

| AN1                 |                              |             | I             |                        | Analog input 1.                                                                                                                                                                                                          |

| RA2/AN2             | 4                            | 1           |               | TTL                    | 5. 5. 5.                                                                                                                                                                                                                 |

| RA2<br>AN2          |                              |             | I/O           |                        | Digital I/O.<br>Analog input 2.                                                                                                                                                                                          |

| RA3/AN3/VREF        | 5                            | 2           | Į.            | TTL                    | Analog input 2.                                                                                                                                                                                                          |

| RA3                 | 3                            | 2           | I/O           | 1112                   | Digital I/O.                                                                                                                                                                                                             |

| AN3                 |                              |             | I             |                        | Analog input 3.                                                                                                                                                                                                          |

| VREF                |                              |             | 1             |                        | A/D reference voltage input.                                                                                                                                                                                             |

| RA4/T0CKI           | 6                            | 3           |               | ST                     |                                                                                                                                                                                                                          |

| RA4                 |                              |             | I/O           |                        | Digital I/O – Open drain when configured as output.                                                                                                                                                                      |

| T0CKI<br>RA5/AN4/SS | 7                            |             | 1             | TTL                    | Timer0 external clock input.                                                                                                                                                                                             |

| RA5/AN4/SS          | 7                            | 4           | I/O           | 111                    | Digital I/O.                                                                                                                                                                                                             |

| AN4                 |                              |             | ı, O          |                        | Analog input 4.                                                                                                                                                                                                          |

| SS                  |                              |             | 1             |                        | SPI slave select input.                                                                                                                                                                                                  |

|                     |                              |             |               |                        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                             |

| RB0/INT             | 21                           | 18          |               | TTL/ST <sup>(1)</sup>  | programmed for internal weak pair up on all inputs.                                                                                                                                                                      |

| RB0                 |                              |             | I/O           | 1.12,01                | Digital I/O.                                                                                                                                                                                                             |

| INT                 |                              |             | 1             |                        | External interrupt.                                                                                                                                                                                                      |

| RB1                 | 22                           | 19          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB2                 | 23                           | 20          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB3                 | 24                           | 21          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB4                 | 25                           | 22          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB5                 | 26                           | 23          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB6                 | 27                           | 24          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

| RB7                 | 28                           | 25          | I/O           | TTL                    | Digital I/O.                                                                                                                                                                                                             |

**Legend:** I = input

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

- 3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

FIGURE 2-2: PIC16CR77/76 REGISTER FILE MAP

| £                    | File<br>Address | A                    | File<br>Address |                      | File<br>Address |                     | File<br>Addre |

|----------------------|-----------------|----------------------|-----------------|----------------------|-----------------|---------------------|---------------|

| Indirect addr.(*)    | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)    | 100h            | Indirect addr.(*)   | 180           |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                 | 101h            | OPTION_REG          | 181           |

| PCL                  | 02h             | PCL                  | 82h             | PCL                  | 102h            | PCL                 | 182           |

| STATUS               | 03h             | STATUS               | 83h             | STATUS               | 103h            | STATUS              | 183           |

| FSR                  | 04h             | FSR                  | 84h             | FSR                  | 104h            | FSR                 | 184           |

| PORTA                | 05h             | TRISA                | 85h             |                      | 105h            |                     | 185           |

| PORTB                | 06h             | TRISB                | 86h             | PORTB                | 106h            | TRISB               | 186           |

| PORTC                | 07h             | TRISC                | 87h             |                      | 107h            |                     | 187           |

| PORTD <sup>(1)</sup> | 08h             | TRISD <sup>(1)</sup> | 88h             |                      | 108h            |                     | 188           |

| PORTE <sup>(1)</sup> | 09h             | TRISE <sup>(1)</sup> | 89h             |                      | 109h            |                     | 189           |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH               | 10Ah            | PCLATH              | 18/           |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON               | 10Bh            | INTCON              | 18E           |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | PMDATA               | 10Ch            | PMCON1              | 180           |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | PMADR                | 10Dh            |                     | 18[           |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | PMDATH               | 10Eh            |                     | 18E           |

| TMR1H                | 0Fh             | . 55.1               | 8Fh             | PMADRH               | 10Fh            |                     | 18F           |

| T1CON                | 10h             |                      | 90h             | 7 1111 12 1 11 1     | 110h            |                     | 190           |

| TMR2                 | 11h             |                      | 91h             |                      | 111h            |                     | 191           |

| T2CON                | 12h             | PR2                  | 92h             |                      | 112h            |                     | 192           |

| SSPBUF               | 13h             | SSPADD               | 93h             |                      | 113h            |                     | 193           |

| SSPCON               | 14h             | SSPSTAT              | 94h             |                      | 114h            |                     | 194           |

| CCPR1L               | 15h             | 001 01741            | 95h             |                      | 115h            |                     | 195           |

| CCPR1H               | 16h             |                      | 96h             |                      | 116h            |                     | 196           |

| CCP1CON              | 17h             |                      | 97h             | General              | 117h            | General             | 197           |

| RCSTA                | 18h             | TXSTA                | 98h             | Purpose              | 118h            | Purpose<br>Register | 198           |

| TXREG                | 19h             | SPBRG                | 99h             | Register<br>16 Bytes | 119h            | 16 Bytes            | 199           |

| RCREG                | 1Ah             | OI BIXO              | 9Ah             |                      | 11Ah            |                     | 19/           |

| CCPR2L               | 1Bh             |                      | 9Bh             |                      | 11Bh            |                     | 19E           |

| CCPR2H               | 1Ch             |                      | 9Ch             |                      | 11Ch            |                     | 190           |

| CCP2CON              | 1Dh             |                      | 9Dh             |                      | 11Dh            |                     | 190           |

| ADRES                | 1Eh             |                      | 9Eh             |                      | 11Eh            |                     | 19E           |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                      | 11Fh            |                     | 19F           |

| 71200110             | 20h             | 7.000111             | A0h             |                      | 120h            |                     | 1A(           |

| General              | 2011            | General              | AUN             | General              |                 | General             | IAC           |

| Purpose              |                 | Purpose              |                 | Purpose              |                 | Purpose             |               |

| Register             |                 | Register             |                 | Register             |                 | Register            |               |

| 96 Bytes             |                 | 80 Bytes             | EFh             | 80 Bytes             | 16Fh            | 80 Bytes            | 1EF           |

|                      | 7Fh             | accesses<br>70h-7Fh  | F0h<br>FFh      | accesses<br>70h-7Fh  | 170h<br>17Fh    | accesses<br>70h-7Fh | 1F0           |

| Bank 0               | 1111            | Bank 1               | 1 1 11          | Bank 2               | 17111           | Bank 3              |               |

Unimplemented data memory locations, read as '0'.

Note 1: These registers are not implemented on 28-pin devices.

<sup>\*</sup> Not a physical register.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address              | Name       | Bit 7                | Bit 6          | Bit 5                     | Bit 4          | Bit 3        | Bit 2         | Bit 1        | Bit 0            | Value on<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|----------------------|----------------|---------------------------|----------------|--------------|---------------|--------------|------------------|-------------------------|--------------------|

| Bank 1               |            |                      |                |                           |                |              |               |              |                  |                         |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressin            | g this locatio | n uses conte              | ents of FSR to | address dat  | a memory (r   | ot a physica | al register)     | 0000 0000               | 27, 96             |

| 81h                  | OPTION_REG | RBPU                 | INTEDG         | T0CS                      | T0SE           | PSA          | PS2           | PS1          | PS0              | 1111 1111               | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program C            | Counter (PC)   | Least Signif              | icant Byte     |              |               |              |                  | 0000 0000               | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                  | RP1            | RP0                       | TO             | PD           | Z             | DC           | C <sup>(2)</sup> | 0001 1xxx               | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect da          | ita memory a   | ddress point              | ter            |              |               |              |                  | xxxx xxxx               | 27, 96             |

| 85h                  | TRISA      | _                    | -              | PORTA Dat                 | a Direction Re | egister      |               |              |                  | 11 1111                 | 32, 96             |

| 86h                  | TRISB      | PORTB D              | ata Direction  | Register                  |                |              |               |              |                  | 1111 1111               | 34, 96             |

| 87h                  | TRISC      | PORTC D              | ata Direction  | Register                  |                |              |               |              |                  | 1111 1111               | 35, 96             |

| 88h <sup>(5)</sup>   | TRISD      | PORTD D              | ata Direction  | Register                  |                |              |               |              |                  | 1111 1111               | 36, 96             |

| 89h <sup>(5)</sup>   | TRISE      | IBF                  | OBF            | IBOV                      | PSPMODE        | -            | PORTE Da      | ta Direction | Bits             | 0000 -111               | 38, 96             |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                    | _              | _                         | Write Buffer f | or the upper | 5 bits of the | Program C    | ounter           | 0 0000                  | 26, 96             |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                  | PEIE           | TMR0IE                    | INTE           | RBIE         | TMR0IF        | INTF         | RBIF             | 0000 000x               | 21, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup> | ADIE           | RCIE                      | TXIE           | SSPIE        | CCP1IE        | TMR2IE       | TMR1IE           | 0000 0000               | 22, 97             |

| 8Dh                  | PIE2       | _                    |                | _                         | _              | -            | _             | -            | CCP2IE           | 0                       | 24, 97             |

| 8Eh                  | PCON       | _                    | -              | _                         | _              | -            | _             | POR          | BOR              | qq                      | 22, 97             |

| 8Fh                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       | _                  |

| 90h                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       | _                  |

| 91h                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       | _                  |

| 92h                  | PR2        | Timer2 Mo            | dule Period    | Register                  |                |              |               |              |                  | 1111 1111               | 52, 97             |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po  | ort (I <sup>2</sup> C™ mo | de) Address F  | Register     |               |              |                  | 0000 0000               | 68, 97             |

| 94h                  | SSPSTAT    | SMP                  | CKE            | D/A                       | Р              | S            | R/W           | UA           | BF               | 0000 0000               | 60, 97             |

| 95h                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       | _                  |

| 96h                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       | _                  |

| 97h                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       | _                  |

| 98h                  | TXSTA      | CSRC                 | TX9            | TXEN                      | SYNC           | _            | BRGH          | TRMT         | TX9D             | 0000 -010               | 69, 97             |

| 99h                  | SPBRG      | Baud Rate            | Generator F    | Register                  |                |              |               |              |                  | 0000 0000               | 71, 97             |

| 9Ah                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       |                    |

| 9Bh                  | _          | Unimplemented        |                |                           |                |              |               |              |                  | _                       |                    |

| 9Ch                  | _          | Unimplemented        |                |                           |                |              |               |              |                  | _                       |                    |

| 9Dh                  | _          | Unimplem             | Unimplemented  |                           |                |              |               |              |                  |                         |                    |

| 9Eh                  | _          | Unimplem             | ented          |                           |                |              |               |              |                  | _                       |                    |

| 9Fh                  | ADCON1     | _                    | _              | _                         | _              | _            | PCFG2         | PCFG1        | PCFG0            | 000                     | 84, 97             |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

- 2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

- **6:** This bit always reads as a '1'.

**TABLE 4-3: PORTB FUNCTIONS**

| Name    | Bit#  | Buffer                | Function                                                                                   |

|---------|-------|-----------------------|--------------------------------------------------------------------------------------------|

| RB0/INT | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up. |

| RB1     | bit 1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                             |

| RB2     | bit 2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                             |

| RB3     | bit 3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                             |

| RB4     | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

| RB5     | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

| RB6     | bit 6 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

| RB7     | bit 7 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.  |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

TABLE 4-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------|------------|---------|-------------------------------|-------|-------|-------|-------|-------|-------|-------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx               | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB I | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111               | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU    | INTEDG                        | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111               | 1111 1111                       |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

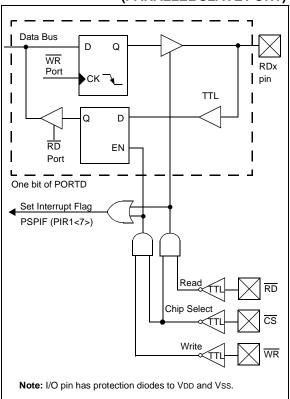

#### 4.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16CR73 or PIC16CR76.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by an external system using the read control input pin RE0/RD, the write control input pin RE1/WR, and the Chip Select control input pin RE2/CS

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (i.e., set). The A/D port Configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data output (external reads) and one for data input (external writes). The firmware writes 8-bit data to the PORTD output data latch and reads data from the PORTD input data latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

An external write to the PSP occurs when the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  lines are both detected low. Firmware can read the actual data on the PORTD pins during this time. When either the  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  lines become high (level triggered), the data on the PORTD pins is latched, and the Input Buffer Full (IBF) status flag bit (TRISE<7>) and interrupt flag bit PSPIF (PIR1<7>) are set on the Q4 clock cycle, following the next Q2 cycle to signal the write is complete (Figure 4-9). Firmware clears the IBF flag by reading the latched PORTD data and clears the PSPIF bit.

The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if an external write to the PSP occurs while the IBF flag is set from a previous external write. The previous PORTD data is overwritten with the new data. IBOV is cleared by reading PORTD and clearing IBOV.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are detected low. The data in the PORTD output latch is output to the PORTD pins. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 4-10), indicating that the PORTD latch is being read, or has been read by the external bus. If firmware writes new data to the output latch during this time, it is immediately output to the PORTD pins, but OBF will remain cleared.

When either the  $\overline{\text{CS}}$  or  $\overline{\text{RD}}$  pins are detected high, the PORTD outputs are disabled, and the interrupt flag bit PSPIF is set on the Q4 clock cycle following the next Q2 cycle, indicating that the read is complete. OBF remains low until firmware writes new data to PORTD.

When not in PSP mode, the IBF and OBF bits are held clear. Flag bit IBOV remains unchanged. The PSPIF bit must be cleared by the user in firmware; the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

FIGURE 4-8: PORTD AND PORTE

BLOCK DIAGRAM

(PARALLEL SLAVE PORT)

# 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

### **REGISTER 5-1: OPTION\_REG:**

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 | •      |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | RBPU: PORTB Pull-up Enable bit (see Section 2.2.2.2 "OPTION_REG Register") |                                                                               |              |                    |  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------|--------------------|--|--|--|--|--|--|--|

| bit 6   | INTEDG:                                                                    | INTEDG: Interrupt Edge Select bit (see Section 2.2.2.2 "OPTION_REG Register") |              |                    |  |  |  |  |  |  |  |

| bit 5   | T0CS: TMR0 Clock Source Select bit                                         |                                                                               |              |                    |  |  |  |  |  |  |  |

|         | 1 = Trans                                                                  | ition on T0Ck                                                                 | (I pin       |                    |  |  |  |  |  |  |  |

|         | 0 = Intern                                                                 | al instruction                                                                | cycle clock  | (CLKOUT)           |  |  |  |  |  |  |  |

| bit 4   | TOSE: TM                                                                   | /IR0 Source E                                                                 | dge Select   | bit                |  |  |  |  |  |  |  |

|         | 1 = Increr                                                                 | ment on high-                                                                 | to-low trans | ition on T0CKI pin |  |  |  |  |  |  |  |

|         | 0 = Increr                                                                 | ment on low-to                                                                | o-high trans | ition on T0CKI pin |  |  |  |  |  |  |  |

| bit 3   | PSA: Pre                                                                   | scaler Assign                                                                 | ment bit     |                    |  |  |  |  |  |  |  |

|         | 1 = Prescaler is assigned to the WDT                                       |                                                                               |              |                    |  |  |  |  |  |  |  |

|         | 0 = Presc                                                                  | aler is assign                                                                | ed to the Ti | ner0 module        |  |  |  |  |  |  |  |

| bit 2-0 | PS2:PS0                                                                    | : Prescaler Ra                                                                | ate Select b | ts                 |  |  |  |  |  |  |  |

|         | Bit Value                                                                  | TMR0 Rate                                                                     | WDT Rate     |                    |  |  |  |  |  |  |  |

|         | 000                                                                        | 1:2                                                                           | 1:1          |                    |  |  |  |  |  |  |  |

|         | 001                                                                        | 1:4                                                                           | 1:2          |                    |  |  |  |  |  |  |  |

|         | 010                                                                        | 1:8                                                                           | 1:4          |                    |  |  |  |  |  |  |  |

|         | 011                                                                        | 1:16                                                                          | 1:8          |                    |  |  |  |  |  |  |  |

1:16

1:32

1:64

1:128

1:32

1:64

1:128

1:256

100

101

110

111

**Note:** To avoid an unintended device Reset, the instruction sequences shown in Example 5-1 and Example 5-2 must be executed when changing the prescaler assignment between Timer0 and the WDT. This sequence must be followed even if the WDT is disabled.

### 9.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 9-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- Update the SSPADD register with the first (high) byte of address, if match releases SCL line, this will clear bit UA.

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- Receive first (high) byte of address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| TARI F 9-2. | DATA TRANSFER RECEIVED BYT | F ACTIONS |

|-------------|----------------------------|-----------|

| Status Bits as Data<br>Transfer is Received |       | SSPSR → SSPBUF | Generate ACK Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |

|---------------------------------------------|-------|----------------|--------------------|----------------------------------------|

| BF                                          | SSPOV |                | Pulse              | if enabled)                            |

| 0                                           | 0     | Yes            | Yes                | Yes                                    |

| 1                                           | 0     | No             | No                 | Yes                                    |

| 1                                           | 1     | No             | No                 | Yes                                    |

| 0                                           | 1     | No             | No                 | Yes                                    |

**Note:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

### 9.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

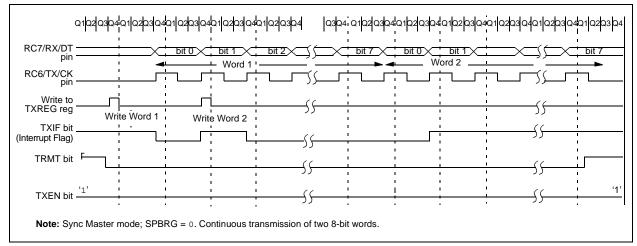

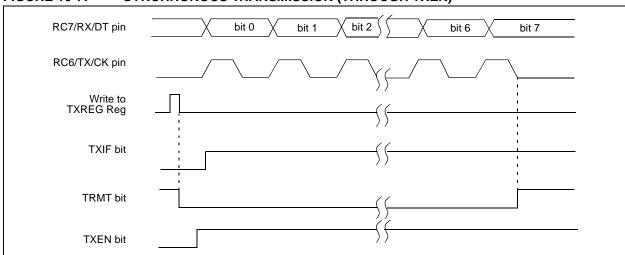

FIGURE 10-6: SYNCHRONOUS TRANSMISSION

FIGURE 10-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                                | Name   | Bit 7                | Bit 6                        | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|----------------------------------------|--------|----------------------|------------------------------|--------|-----------|-----------|--------|-----------|-----------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE                         | TMR0IE | INTE      | RBIE      | TMR0IF | INTF      | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF   | TXIF      | SSPIF     | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000               | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9                          | SREN   | CREN      | _         | FERR   | OERR      | RX9D      | 0000 -00x               | 0000 -00x                       |

| 19h                                    | TXREG  | USART Tr             | JSART Transmit Data Register |        |           |           |        | 0000 0000 | 0000 0000 |                         |                                 |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE   | TXIE      | SSPIE     | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000               | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9                          | TXEN   | SYNC      | _         | BRGH   | TRMT      | TX9D      | 0000 -010               | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |                              |        | 0000 0000 | 0000 0000 |        |           |           |                         |                                 |

**Legend:** x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76 devices; always maintain these bits clear.

### REGISTER 12-1: CONFIGURATION WORD: (ADDRESS 2007h<sup>(1)</sup>)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 U-0 |   |  |

|--------------|-----|-----|-----|-----|---------|---|--|

| _            | _   | _   | _   | _   | _       | _ |  |

| bit 13 bit 7 |     |     |     |     |         |   |  |

| R/P-1 | U-0 | R/P-1 | R/P-1  | R/P-1 | R/P-1 | R/P-1 |

|-------|-----|-------|--------|-------|-------|-------|

| BOREN | _   | CP0   | PWRTEN | WDTEN | FOSC1 | FOSC0 |

| bit 6 |     |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 13-7 Unimplemented: Read as '1'

bit 6 BOREN: Brown-out Reset Enable bit

1 = BOR enabled0 = BOR disabled

bit 5 Unimplemented: Read as '1'

bit 4 CP0: ROM Program Memory Code Protection bit

1 = Code protection off

0 = All memory locations code protected

bit 3 **PWRTEN**: Power-up Timer Enable bit

1 = PWRT disabled0 = PWRT enabled

bit 2 WDTEN: Watchdog Timer Enable bit

1 = WDT enabled0 = WDT disabled

bit 1-0 FOSC1:FOSC0: Oscillator Selection bits

11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator

**Note 1:** The erased (unprogrammed) value of the Configuration Word is 3FFFh.

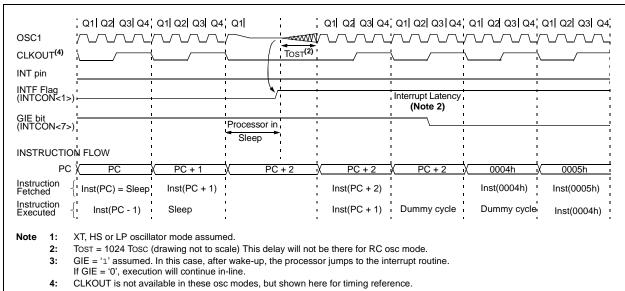

### 12.2 Oscillator Configurations

#### 12.2.1 OSCILLATOR TYPES

The PIC16CR7X can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low-Power CrystalXT Crystal/Resonator

- HS High-Speed Crystal/Resonator

- RC Resistor/Capacitor

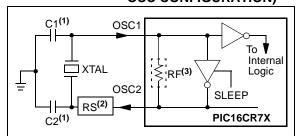

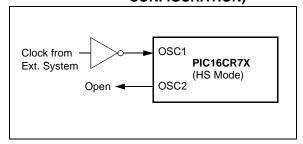

## 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16CR7X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS mode, the device can accept an external clock source to drive the OSC1/CLKIN pin (Figure 12-2). See Figure 15-1 or Figure 15-2 (depending on the part number and VDD range) for valid external clock frequencies.

FIGURE 12-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

OSC CONFIGURATION)

- Note 1: See Table 12-1 and Table 12-2 for recommended values of C1 and C2.

- **2:** A series resistor (RS) may be required for AT strip cut crystals.

- 3: RF varies with the crystal chosen.

FIGURE 12-2: EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

TABLE 12-1: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|--|

| Mode Freq. OSC1 OSC2           |          |       |       |  |  |  |  |  |

| XT                             | 455 kHz  | 56 pF | 56 pF |  |  |  |  |  |

|                                | 2.0 MHz  | 47 pF | 47 pF |  |  |  |  |  |

|                                | 4.0 MHz  | 33 pF | 33 pF |  |  |  |  |  |

| HS                             | 8.0 MHz  | 27 pF | 27 pF |  |  |  |  |  |

|                                | 16.0 MHz | 22 pF | 22 pF |  |  |  |  |  |

### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes at the bottom of page 92 for additional information.

| Resonators Used:                |  |  |  |  |  |  |

|---------------------------------|--|--|--|--|--|--|

| 455 kHz Panasonic EFO-A455K04B  |  |  |  |  |  |  |

| 2.0 MHz Murata Erie CSA2.00MG   |  |  |  |  |  |  |

| 4.0 MHz Murata Erie CSA4.00MG   |  |  |  |  |  |  |

| 8.0 MHz Murata Erie CSA8.00MT   |  |  |  |  |  |  |

| 16.0 MHz Murata Erie CSA16.00MX |  |  |  |  |  |  |

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been enabled, the on-chip program memory can be read out for verification purposes.

### 12.16 ID Locations

Four memory locations (2000h-2002h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable for program verification. It is recommended that only the 4 Least Significant bits of the ID location are used.

### 12.17 User Code

PIC16CR7X microcontrollers are ROM-based, thus user programming is not possible. Please contact your Microchip sales representitive for details on how to submit your final code. This information can also be found in Application Note AN1010, "PIC16CR ROM Code Submission Process".

| MOVF             | Move f                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are moved to a destination dependant upon the status of 'd'. If 'd' = 0, destination is W register. If 'd' = 1, the destination is file register 'f' itself. 'd' = 1 is useful to test a file register, since status flag Z is affected. |  |  |  |  |  |  |

| NOP              | No Operation  |  |

|------------------|---------------|--|

| Syntax:          | [label] NOP   |  |

| Operands:        | None          |  |

| Operation:       | No operation  |  |

| Status Affected: | None          |  |

| Description:     | No operation. |  |

|                  |               |  |

|                  |               |  |

|                  |               |  |

|                  |               |  |

|                  |               |  |

| MOVLW            | Move Literal to W                                                                             |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] MOVLW k                                                                             |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                             |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                          |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                      |

|------------------|--------------------------------------------|

| Syntax:          | [label] RETFIE                             |

| Operands:        | None                                       |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$ |

| Status Affected: | None                                       |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [label] MOVWF f                            |

| Operands:        | $0 \le f \le 127$                          |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| RETLW            | Return with Literal in W                                                                                                                                                        |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETLW k                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                               |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                    |  |  |  |  |

| Status Affected: | None                                                                                                                                                                            |  |  |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

### 15.2 DC Characteristics: PIC16CR73/74/76/77 (Industrial, Extended)

| DC CHARACTERISTICS               |       |                             | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended Operating voltage VDD range as described in DC Specification, Section 15.1 "DC Characteristics: PIC16CR73/74/76/77 (Industrial, Extended)". |      |         |       |                                                                                                           |

|----------------------------------|-------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|-----------------------------------------------------------------------------------------------------------|

| Param<br>No.                     | Sym   | Characteristic              | Min                                                                                                                                                                                                                                                                                                                                                                            | Тур† | Max     | Units | Conditions                                                                                                |

|                                  | VIL   | Input Low Voltage           |                                                                                                                                                                                                                                                                                                                                                                                | 1    |         |       | <del>,</del>                                                                                              |

|                                  |       | I/O ports:                  |                                                                                                                                                                                                                                                                                                                                                                                |      |         |       |                                                                                                           |

| D030                             |       | with TTL buffer             | Vss                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.15VDD | V     | For entire VDD range                                                                                      |

| D030A                            |       |                             | Vss                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.8V    | V     | 4.5V ≤ VDD ≤ 5.5V                                                                                         |

| D031                             |       | with Schmitt Trigger buffer | Vss                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.2Vdd  | V     |                                                                                                           |

| D032                             |       | MCLR, OSC1 (in RC mode)     | Vss                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.2Vdd  | V     | (Note 1)                                                                                                  |

| D033                             |       | OSC1 (in XT and LP mode)    | Vss                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.3V    | V     |                                                                                                           |

|                                  |       | OSC1 (in HS mode)           | Vss                                                                                                                                                                                                                                                                                                                                                                            | _    | 0.3VDD  | V     |                                                                                                           |

|                                  | VIH   | Input High Voltage          | T                                                                                                                                                                                                                                                                                                                                                                              | 1    | 1       | T     |                                                                                                           |

|                                  |       | I/O ports:                  |                                                                                                                                                                                                                                                                                                                                                                                |      |         |       |                                                                                                           |

| D040                             |       | with TTL buffer             | 2.0                                                                                                                                                                                                                                                                                                                                                                            | _    | VDD     | V     | 4.5V ≤ VDD ≤ 5.5V                                                                                         |

| D040A                            |       |                             | 0.25VDD<br>+ 0.8V                                                                                                                                                                                                                                                                                                                                                              | _    | VDD     | V     | For entire VDD range                                                                                      |

| D041                             |       | with Schmitt Trigger buffer | 0.8VDD                                                                                                                                                                                                                                                                                                                                                                         | _    | VDD     | V     | For entire VDD range                                                                                      |

| D042                             |       | MCLR                        | 0.8VDD                                                                                                                                                                                                                                                                                                                                                                         | _    | VDD     | V     |                                                                                                           |

| D042A                            |       | OSC1 (in XT and LP mode)    | 1.6V                                                                                                                                                                                                                                                                                                                                                                           | _    | VDD     | V     |                                                                                                           |

|                                  |       | OSC1 (in HS mode)           | 0.7Vdd                                                                                                                                                                                                                                                                                                                                                                         | _    | VDD     | V     |                                                                                                           |

| D043                             |       | OSC1 (in RC mode)           | 0.9Vdd                                                                                                                                                                                                                                                                                                                                                                         | _    | VDD     | V     | (Note 1)                                                                                                  |

| D070                             | IPURB | PORTB Weak Pull-up Current  | 50                                                                                                                                                                                                                                                                                                                                                                             | 250  | 400     | μΑ    | VDD = 5V, VPIN = VSS                                                                                      |

| IIL Input Leakage Current (Notes |       | 2, 3)                       | •                                                                                                                                                                                                                                                                                                                                                                              |      | r       |       |                                                                                                           |

| D060                             |       | I/O ports                   | _                                                                                                                                                                                                                                                                                                                                                                              | _    | ±1      | μΑ    | $\label{eq:VSS} \begin{tabular}{ll} $VSS \leq VPIN \leq VDD, \ pin \ at \\ high-impendance \end{tabular}$ |

| D061                             |       | MCLR, RA4/T0CKI             | _                                                                                                                                                                                                                                                                                                                                                                              | _    | ±5      | μΑ    | Vss ≤ Vpin ≤ Vdd                                                                                          |

| D063                             |       | OSC1                        |                                                                                                                                                                                                                                                                                                                                                                                | _    | ±5      | μΑ    | $\label{eq:VSS}  \mbox{$V$PIN$} \le \mbox{$V$DD, XT, HS and LP} \\ \mbox{osc configuration} $             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16CR7X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

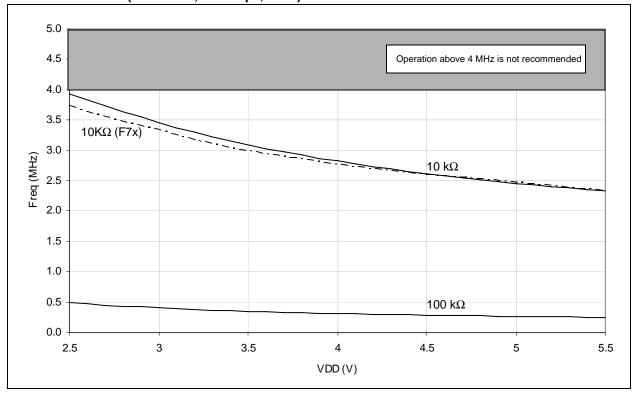

FIGURE 16-7: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 20 pF, 25°C)

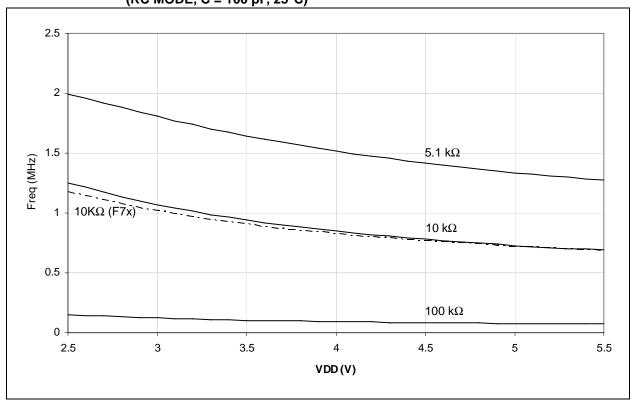

FIGURE 16-8: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, 25°C)

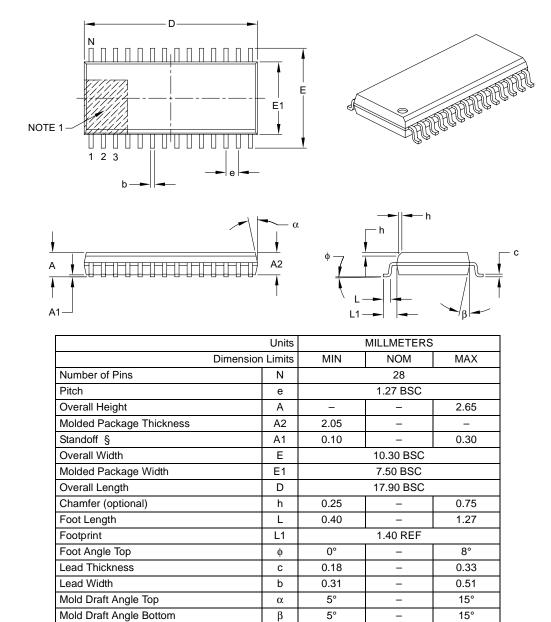

### 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

β

5°

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

15°

### APPENDIX A: REVISION HISTORY

### Revision A (March 2006)

This is a new data sheet. However, these devices are similar to the PIC16F7X devices found in the PIC16F7X Data Sheet (DS30325B).

### Revision B (December 2006)

Revised 15.1 DC Characteristics Param. No. D005, D020, D021, D021A; 15.2 DC Characteristics Param. No. D070; Table 15-3, Param. No. 30. Replaced Package drawings.

### Revision C (January 2007)

This revision includes updates to the packaging diagrams.

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Difference                           | PIC16CR73                                               | PIC16CR74                                 | PIC16CR76                                               | PIC16CR77                                 |

|--------------------------------------|---------------------------------------------------------|-------------------------------------------|---------------------------------------------------------|-------------------------------------------|