Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | ROM                                                                      |

| EEPROM Size                |                                                                          |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr76-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16CR7X

## 28/40-Pin, 8-Bit CMOS ROM Microcontrollers

#### **Devices Included in this Data Sheet:**

- PIC16CR73PIC16CR74

- PIC16CR77

PIC16CR76

### **High-Performance RISC CPU:**

- High-performance RISC CPU

- Only 35 single-word instructions to learn

- All single-cycle instructions except for program branches which are two-cycle

- Operating speed: DC 20 MHz clock input DC – 200 ns instruction cycle

- Up to 8K x 14 words of ROM Program Memory, Up to 368 x 8 bytes of Data Memory (RAM)

- Function compatible to the PIC16F73/74/76/77

- Pinout compatible to the PIC16F873/874/876/877

- Interrupt capability (up to 12 sources)

- Eight-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- Processor read access to program memory

#### **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Power-Saving Sleep mode

- Selectable oscillator options

#### **Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler, can be incremented during Sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Two Capture, Compare, PWM modules:

- Capture is 16-bit, max. resolution is 12.5 ns

- Compare is 16-bit, max. resolution is 200 ns

- PWM max. resolution is 10-bit

- 8-bit, up to 8-channel Analog-to-Digital converter

- Synchronous Serial Port (SSP) with SPI (Master mode) and I<sup>2</sup>C<sup>™</sup> (Slave)

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

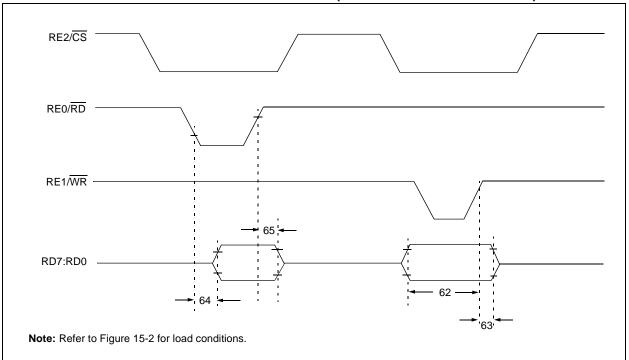

- Parallel <u>Slave Port</u> (P<u>SP</u>), 8-bits wide with external <u>RD</u>, <u>WR</u> and <u>CS</u> controls (40/44-pin only)

- Brown-out detection circuitry for Brown-out Reset (BOR)

## **CMOS Technology:**

- Low-power, high-speed CMOS ROM technology

- · Fully static design

- Wide operating voltage range: 2.0V to 5.5V

- High Sink/Source Current: 25 mA

- Industrial temperature range

- Low power consumption:

- < 2 mA typical @ 5V, 4 MHz TBD

- 20 μA typical @ 3V, 32 kHz TBD

- <1  $\mu$ A typical standby current TBD

|           | Program                                   | Data            |     |            |                   |              |                 | SS                           | P     |                    |  |

|-----------|-------------------------------------------|-----------------|-----|------------|-------------------|--------------|-----------------|------------------------------|-------|--------------------|--|

| Device    | Memory<br>(# Single Word<br>Instructions) | SRAM<br>(Bytes) | I/O | Interrupts | 8-bit<br>A/D (ch) | CCP<br>(PWM) | SPI<br>(Master) | l <sup>2</sup> C™<br>(Slave) | USART | Timers<br>8/16-bit |  |

| PIC16CR73 | 4096                                      | 192             | 22  | 11         | 5                 | 2            | Yes             | Yes                          | Yes   | 2/1                |  |

| PIC16CR74 | 4096                                      | 192             | 33  | 12         | 8                 | 2            | Yes             | Yes                          | Yes   | 2/1                |  |

| PIC16CR76 | 8192                                      | 368             | 22  | 11         | 5                 | 2            | Yes             | Yes                          | Yes   | 2/1                |  |

| PIC16CR77 | 8192                                      | 368             | 33  | 12         | 8                 | 2            | Yes             | Yes                          | Yes   | 2/1                |  |

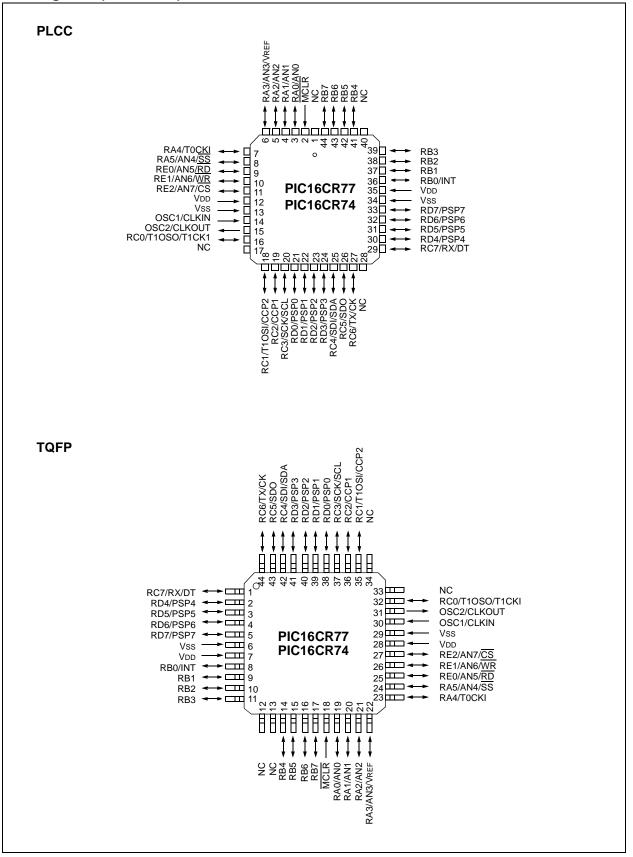

## **Pin Diagrams (Continued)**

### TABLE 1-2:PIC16CR73 AND PIC16CR76 PINOUT DESCRIPTION

| Pin Name            | PDIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                      |

|---------------------|------------------------------|-------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN<br>OSC1  | 9                            | 6           | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input. ST<br>buffer when configured in RC mode. Otherwise CMOS. |

| CLKIN               |                              |             | Ι             |                        | External clock source input. Always associated with pin<br>function OSC1 (see OSC1/CLKIN, OSC2/CLKOUT pins).                                                     |

| OSC2/CLKOUT<br>OSC2 | 10                           | 7           | 0             | _                      | Oscillator crystal or clock output.<br>Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator<br>mode.                             |

| CLKOUT              |                              |             | 0             |                        | In RC mode, OSC2 pin outputs CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                 |

| MCLR                | 1                            | 26          | Ι             | ST                     | Master Clear (Reset) input. This pin is an active low Reset to the device.                                                                                       |

|                     |                              |             |               |                        | PORTA is a bidirectional I/O port.                                                                                                                               |

| RA0/AN0             | 2                            | 27          |               | TTL                    |                                                                                                                                                                  |

| RA0                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN0                 |                              |             | I             |                        | Analog input 0.                                                                                                                                                  |

| RA1/AN1             | 3                            | 28          |               | TTL                    |                                                                                                                                                                  |

| RA1                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN1                 |                              |             | I             |                        | Analog input 1.                                                                                                                                                  |

| RA2/AN2             | 4                            | 1           | 1/0           | TTL                    |                                                                                                                                                                  |

| RA2<br>AN2          |                              |             | I/O           |                        | Digital I/O.<br>Analog input 2.                                                                                                                                  |

| RA3/AN3/VREF        | 5                            | 2           | 1             | TTL                    | Analog input 2.                                                                                                                                                  |

| RA3/AN3/VREF        | 5                            | 2           | I/O           | 116                    | Digital I/O.                                                                                                                                                     |

| AN3                 |                              |             | 1/C           |                        | Analog input 3.                                                                                                                                                  |

| VREF                |                              |             | I             |                        | A/D reference voltage input.                                                                                                                                     |

| RA4/T0CKI           | 6                            | 3           |               | ST                     |                                                                                                                                                                  |

| RA4                 |                              |             | I/O           |                        | Digital I/O – Open drain when configured as output.                                                                                                              |

| TOCKI               |                              |             | I             |                        | Timer0 external clock input.                                                                                                                                     |

| RA5/AN4/SS          | 7                            | 4           |               | TTL                    |                                                                                                                                                                  |

| RA5                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| AN4                 |                              |             |               |                        | Analog input 4.                                                                                                                                                  |

| SS                  |                              |             |               |                        | SPI slave select input.                                                                                                                                          |

|                     |                              |             |               |                        | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                     |

| RB0/INT             | 21                           | 18          |               | TTL/ST <sup>(1)</sup>  |                                                                                                                                                                  |

| RB0                 |                              |             | I/O           |                        | Digital I/O.                                                                                                                                                     |

| INT                 |                              |             | I             |                        | External interrupt.                                                                                                                                              |

| RB1                 | 22                           | 19          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| RB2                 | 23                           | 20          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| RB3                 | 24                           | 21          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| RB4                 | 25                           | 22          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| RB5                 | 26                           | 23          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| RB6                 | 27                           | 24          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

| RB7                 | 28                           | 25          | I/O           | TTL                    | Digital I/O.                                                                                                                                                     |

|                     | 1                            | 1           |               | 1                      |                                                                                                                                                                  |

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

| Pin Name        | PDIP<br>Pin# | PLCC<br>Pin#    | QFP<br>Pin#      | I/O/P<br>Type | Buffer<br>Type        | Description                                                                     |

|-----------------|--------------|-----------------|------------------|---------------|-----------------------|---------------------------------------------------------------------------------|

|                 |              |                 |                  |               |                       | PORTD is a bidirectional I/O port or parallel slave port                        |

|                 |              |                 |                  |               | (2)                   | when interfacing to a microprocessor bus.                                       |

| RD0/PSP0        | 19           | 21              | 38               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD0<br>PSP0     |              |                 |                  | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                       |

|                 | 20           | 00              | 20               |               | ST/TTL <sup>(3)</sup> | Paraller Slave Port data.                                                       |

| RD1/PSP1<br>RD1 | 20           | 22              | 39               | I<br>I/O      | 51/1124               | Digital I/O.                                                                    |

| PSP1            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD2/PSP2        | 21           | 23              | 40               | 1             | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD2             |              |                 |                  | I/O           | 0.,                   | Digital I/O.                                                                    |

| PSP2            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD3/PSP3        | 22           | 24              | 41               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD3             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP3            |              |                 |                  | I/O           | (2)                   | Parallel Slave Port data.                                                       |

| RD4/PSP4        | 27           | 30              | 2                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD4<br>PSP4     |              |                 |                  | I/O<br>I/O    |                       | Digital I/O.<br>Parallel Slave Port data.                                       |

| -               | 20           | 24              | 2                | 1/0           | ST/TTL <sup>(3)</sup> | Paraller Slave Port data.                                                       |

| RD5/PSP5<br>RD5 | 28           | 31              | 3                | I/O           | 51/1124               | Digital I/O.                                                                    |

| PSP5            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD6/PSP6        | 29           | 32              | 4                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD6             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP6            |              |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

| RD7/PSP7        | 30           | 33              | 5                |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RD7             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| PSP7            | _            |                 |                  | I/O           |                       | Parallel Slave Port data.                                                       |

|                 |              |                 |                  |               | (2)                   | PORTE is a bidirectional I/O port.                                              |

| RE0/AN5/RD/     | 8            | 9               | 25               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE0<br>AN5      |              |                 |                  | I/O<br>I      |                       | Digital I/O.<br>Analog input 5.                                                 |

|                 |              |                 |                  | 1             |                       | Read control for parallel slave port .                                          |

| RE1/AN6/WR/     | 9            | 10              | 26               | -             | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE1             | °,           |                 |                  | I/O           | 0.,                   | Digital I/O.                                                                    |

| AN6             |              |                 |                  | I             |                       | Analog input 6.                                                                 |

| WR              |              |                 |                  | I             |                       | Write control for parallel slave port .                                         |

| RE2/AN7/CS      | 10           | 11              | 27               |               | ST/TTL <sup>(3)</sup> |                                                                                 |

| RE2             |              |                 |                  | I/O           |                       | Digital I/O.                                                                    |

| AN7<br>CS       |              |                 |                  |               |                       | Analog input 7.<br>Chip Select control for parallel slave port .                |

| Vss             | 12,31        | 13,34           | 6,29             | P             |                       | Ground reference for logic and I/O pins.                                        |

| VSS<br>VDD      | 12,31        | 12,35           | 7,28             | <br>Р         |                       | Positive supply for logic and I/O pins.                                         |

| NC              | 11,52        |                 |                  | Г             |                       |                                                                                 |

|                 |              | 1,17,<br>28, 40 | 12,13,<br>33, 34 |               |                       | These pins are not internally connected. These pins should be left unconnected. |

#### TABLE 1-3: PIC16CR74 AND PIC16CR77 PINOUT DESCRIPTION (CONTINUED)

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Verify mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

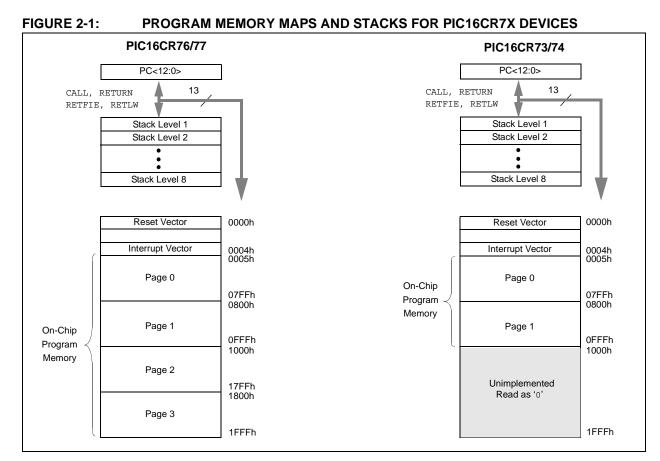

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The Program Memory can be read internally by user code (see Section 3.0 "Reading Program Memory").

Additional information on device memory may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

## 2.1 Program Memory Organization

The PIC16CR7X devices have a 13-bit program counter capable of addressing an 8K word x 14-bit program memory space. The PIC16CR77/76 devices have 8K words of ROM program memory and the PIC16CR73/74 devices have 4K words. The program memory maps for PIC16CR7X devices are shown in Figure 2-1. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

## 2.2 Data Memory Organization

The Data Memory is partitioned into multiple banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits:

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file (shown in Figure 2-2 and Figure 2-3) can be accessed either directly, or indirectly, through the File Select Register (FSR).

#### FIGURE 2-2: PIC16CR77/76 REGISTER FILE MAP

| F                                          | File<br>\ddress | P                                          | File<br>Address |                                            | File<br>Address |                                            | File<br>Addres |

|--------------------------------------------|-----------------|--------------------------------------------|-----------------|--------------------------------------------|-----------------|--------------------------------------------|----------------|

| Indirect addr.(*)                          | 00h             | Indirect addr.(*)                          | 80h             | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180h           |

| TMR0                                       | 01h             | OPTION_REG                                 | 81h             | TMR0                                       | 101h            | OPTION_REG                                 | 181h           |

| PCL                                        | 02h             | PCL                                        | 82h             | PCL                                        | 102h            | PCL                                        | 182h           |

| STATUS                                     | 03h             | STATUS                                     | 83h             | STATUS                                     | 103h            | STATUS                                     | 183h           |

| FSR                                        | 04h             | FSR                                        | 84h             | FSR                                        | 104h            | FSR                                        | 184h           |

| PORTA                                      | 05h             | TRISA                                      | 85h             |                                            | 105h            |                                            | 185h           |

| PORTB                                      | 06h             | TRISB                                      | 86h             | PORTB                                      | 106h            | TRISB                                      | 186h           |

| PORTC                                      | 07h             | TRISC                                      | 87h             |                                            | 107h            |                                            | 187h           |

| PORTD <sup>(1)</sup>                       | 08h             | TRISD <sup>(1)</sup>                       | 88h             |                                            | 108h            |                                            | 188h           |

| PORTE <sup>(1)</sup>                       | 09h             | TRISE <sup>(1)</sup>                       | 89h             |                                            | 109h            |                                            | 189h           |

| PCLATH                                     | 0Ah             | PCLATH                                     | 8Ah             | PCLATH                                     | 10Ah            | PCLATH                                     | 18Ah           |

| INTCON                                     | 0Bh             | INTCON                                     | 8Bh             | INTCON                                     | 10Bh            | INTCON                                     | 18Bh           |

| PIR1                                       | 0Ch             | PIE1                                       | 8Ch             | PMDATA                                     | 10Ch            | PMCON1                                     | 18Ch           |

| PIR2                                       | 0Dh             | PIE2                                       | 8Dh             | PMADR                                      | 10Dh            |                                            | 18Dh           |

| TMR1L                                      | 0Eh             | PCON                                       | 8Eh             | PMDATH                                     | 10Eh            |                                            | 18Eh           |

| TMR1H                                      | 0Fh             |                                            | 8Fh             | PMADRH                                     | 10Fh            |                                            | 18Fh           |

| T1CON                                      | 10h             |                                            | 90h             |                                            | 110h            |                                            | 190h           |

| TMR2                                       | 11h             | -                                          | 91h             |                                            | 111h            |                                            | 191h           |

| T2CON                                      | 12h             | PR2                                        | 92h             |                                            | 112h            |                                            | 192h           |

| SSPBUF                                     | 13h             | SSPADD                                     | 93h             |                                            | 113h            |                                            | 193h           |

| SSPCON                                     | 14h             | SSPSTAT                                    | 94h             |                                            | 114h            |                                            | 194h           |

| CCPR1L                                     | 15h             |                                            | 95h             |                                            | 115h            |                                            | 195h           |

| CCPR1H                                     | 16h             |                                            | 96h             |                                            | 116h            |                                            | 196h           |

| CCP1CON                                    | 17h             |                                            | 97h             | General                                    | 117h            | General                                    | 197h           |

| RCSTA                                      | 18h             | TXSTA                                      | 98h             | Purpose<br>Register                        | 118h            | Purpose<br>Register                        | 198h           |

| TXREG                                      | 19h             | SPBRG                                      | 99h             | 16 Bytes                                   | 119h            | 16 Bytes                                   | 199h           |

| RCREG                                      | 1Ah             |                                            | 9Ah             | ,                                          | 11Ah            | ,                                          | 19Ah           |

| CCPR2L                                     | 1Bh             |                                            | 9Bh             |                                            | 11Bh            |                                            | 19Bh           |

| CCPR2H                                     | 1Ch             |                                            | 9Ch             |                                            | 11Ch            |                                            | 19Ch           |

| CCP2CON                                    | 1Dh             |                                            | 9Dh             |                                            | 11Dh            |                                            | 19Dh           |

| ADRES                                      | 1Eh             |                                            | 9Eh             |                                            | 11Eh            |                                            | 19Eh           |

| ADCON0                                     | 1Fh             | ADCON1                                     | 9Fh             |                                            | 11Fh            |                                            | 19Fh           |

|                                            | 20h             |                                            | A0h             |                                            | 120h            |                                            | 1A0h           |

| General<br>Purpose<br>Register<br>96 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes | EFh             | General<br>Purpose<br>Register<br>80 Bytes | 16Fh            | General<br>Purpose<br>Register<br>80 Bytes | 1EFh           |

|                                            | 7Fh             | accesses<br>70h-7Fh                        | FOh<br>FFh      | accesses<br>70h-7Fh                        | 170h<br>17Fh    | accesses<br>70h-7Fh                        | 1F0h           |

| Bank 0                                     |                 | Bank 1                                     |                 | Bank 2                                     |                 | Bank 3                                     |                |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

**Note 1:** These registers are not implemented on 28-pin devices.

## PIC16CR7X

#### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt.

### REGISTER 2-6: PIE2: (ADDRESS 8Dh)

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| —       | —   | —   | _   | —   | —   | —   | CCP2IE |

| bit 7   |     |     |     |     |     |     | bit 0  |

|         |     |     |     |     |     |     |        |

| Legend: |     |     |     |     |     |     |        |

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7-1 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt.

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>). User soft-       |

|       | ware should ensure the appropriate inter-     |

|       | rupt flag bits are clear prior to enabling an |

|       | interrupt.                                    |

#### REGISTER 2-7: PIR2: (ADDRESS 0Dh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

|       |     |     |     |     |     |     | CCP2IF |

| bit 7 |     |     |     |     |     |     | bit 0  |

Ν

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-1 Unimplemented: Read as '0'

| bit 0 | CCP2IF: CCP2 Interrupt Flag bit                                          |

|-------|--------------------------------------------------------------------------|

|       | Capture mode:                                                            |

|       | 1 = A TMR1 register capture occurred (must be cleared in software)       |

|       | 0 = No TMR1 register capture occurred                                    |

|       | Compare mode:                                                            |

|       | 1 = A TMR1 register compare match occurred (must be cleared in software) |

|       | 0 = No TMR1 register compare match occurred                              |

|       | PWM mode:                                                                |

|       | Unused                                                                   |

## 2.2.2.8 PCON Register

The Power Control (PCON) register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT) and an external MCLR Reset.

| Note: | BOR is unknown on POR. It must be set by        |

|-------|-------------------------------------------------|

|       | the user and checked on subsequent              |

|       | Resets to see if BOR is clear, indicating a     |

|       | brown-out has occurred. The BOR Status          |

|       | bit is not predictable if the brown-out circuit |

|       | is disabled (by clearing the BOREN bit in       |

|       | the Configuration Word).                        |

## REGISTER 2-8: PCON: (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                              |

|---------|-----------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                          |

|         | 1 = No Power-on Reset occurred                                                          |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)   |

| bit 0   | BOR: Brown-out Reset Status bit                                                         |

|         | 1 = No Brown-out Reset occurred                                                         |

|         | 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs) |

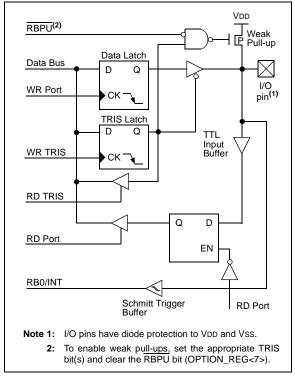

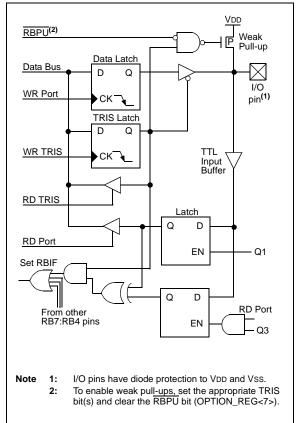

## 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impendance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "*Implementing Wake-up on Key Stroke*" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in **Section 12.11.1 "INT Interrupt"**.

#### BLOCK DIAGRAM OF RB7:RB4 PINS

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 and CCP2 special event triggers.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

|            | Frequency | Capacitors Used: |       |  |  |

|------------|-----------|------------------|-------|--|--|

| Osc Type   | Frequency | OSC1             | OSC2  |  |  |

| LP         | 32 kHz    | 47 pF            | 47 pF |  |  |

|            | 100 kHz   | 33 pF            | 33 pF |  |  |

|            | 200 kHz   | 15 pF            | 15 pF |  |  |

| <b>A 1</b> |           |                  |       |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

| e notes (below) table for additional information. |

|---------------------------------------------------|

|---------------------------------------------------|

|                                                                                                                                                                                                                 | Commonly Used Crystals:                                                                                 |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 32.768 kHz                                                                                                                                                                                                      | Epson C-001R32.768K-A                                                                                   |  |  |  |  |  |  |  |  |

| 100 kHz                                                                                                                                                                                                         | Epson C-2 100.00 KC-P                                                                                   |  |  |  |  |  |  |  |  |

| 200 kHz                                                                                                                                                                                                         | STD XTL 200.000 kHz                                                                                     |  |  |  |  |  |  |  |  |

| 0                                                                                                                                                                                                               | ligher capacitance increases the stability<br>f the oscillator, but also increases the<br>tart-up time. |  |  |  |  |  |  |  |  |

| <ul> <li>Start-up time.</li> <li>Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                                                                                         |  |  |  |  |  |  |  |  |

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name   | Bit 7                                                                      | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|--------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|-----------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                                                                        | PEIE                                                                        | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF   | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup>                                                       | ADIF                                                                        | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF    | 0000 0000               | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup>                                                       | ADIE                                                                        | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE    | 0000 0000               | 0000 0000                       |

| 0Eh                   | TMR1L  | Holding Reg                                                                | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |           | xxxx xxxx               | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                                                                             |         |         |         |        |        | xxxx xxxx | uuuu uuuu               |                                 |

| 10h                   | T1CON  | —                                                                          | _                                                                           | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N    | 00 0000                 | uu uuuu                         |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

|               |                                                      |                  | •             |                  | -                |                 |         |  |

|---------------|------------------------------------------------------|------------------|---------------|------------------|------------------|-----------------|---------|--|

| U-0           | R/W-0                                                | R/W-0            | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |

| —             | TOUTPS3                                              | TOUTPS2          | TOUTPS1       | TOUTPS0          | TMR2ON           | T2CKPS1         | T2CKPS0 |  |

| bit 7         |                                                      |                  |               |                  |                  |                 | bit 0   |  |

|               |                                                      |                  |               |                  |                  |                 |         |  |

| Legend:       |                                                      |                  |               |                  |                  |                 |         |  |

| R = Readable  | e bit                                                | W = Writable     | bit           | U = Unimpler     | mented bit, read | l as '0'        |         |  |

| -n = Value at | POR                                                  | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |

|               |                                                      |                  |               |                  |                  |                 |         |  |

| bit 7         | Unimplemen                                           | ted: Read as '   | 0'            |                  |                  |                 |         |  |

| bit 6-3       | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |                  |               |                  |                  |                 |         |  |

|               | 0000 = 1:1 P                                         | ostscale         |               |                  |                  |                 |         |  |

|               | 0001 = 1:2 P                                         |                  |               |                  |                  |                 |         |  |

|               | 0010 = 1:3 P                                         | ostscale         |               |                  |                  |                 |         |  |

|               | •                                                    |                  |               |                  |                  |                 |         |  |

|               | •                                                    |                  |               |                  |                  |                 |         |  |

|               | 1111 <b>= 1:16</b>                                   | Postscale        |               |                  |                  |                 |         |  |

| bit 2         | TMR2ON: Tir                                          | ner2 On bit      |               |                  |                  |                 |         |  |

|               | 1 = Timer2 is                                        | on               |               |                  |                  |                 |         |  |

|               | 0 = Timer2 is                                        | off              |               |                  |                  |                 |         |  |

| bit 1-0       | T2CKPS1:T2                                           | CKPS0: Timer     | 2 Clock Presc | ale Select bits  |                  |                 |         |  |

|               | 00 = Prescale                                        |                  |               |                  |                  |                 |         |  |

|               | 01 = Prescale                                        |                  |               |                  |                  |                 |         |  |

|               | 1x = Prescale                                        | er is 16         |               |                  |                  |                 |         |  |

## REGISTER 7-1: T2CON: TIMER2 CONTROL (ADDRESS 12h)

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                    | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------------------------|------------------------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                      | PEIE                   | TMR0IE  | INTE    | RBIE    | TMR0IF | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>     | ADIF                   | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>     | ADIE                   | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000               | 0000 0000                       |

| 11h                    | TMR2   | Timer2 Mc                | Fimer2 Module Register |         |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h                    | T2CON  | _                        | TOUTPS3                | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h                    | PR2    | 2 Timer2 Period Register |                        |         |         |         |        |         |         |                         | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

**Note** 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

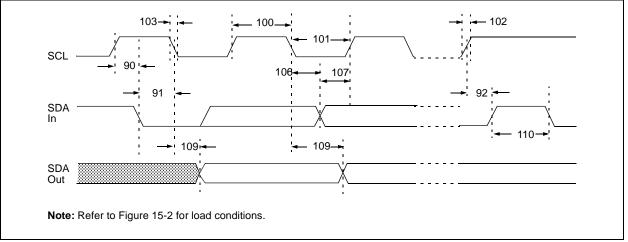

## 9.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

### 9.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

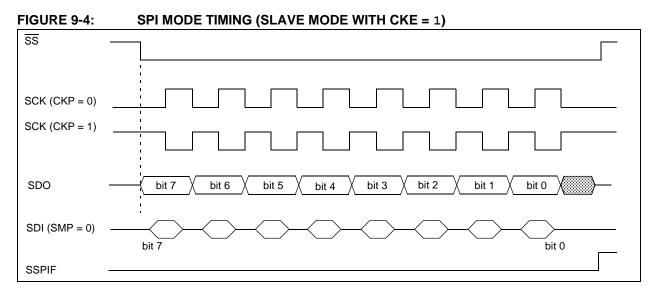

## 9.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module. Additional information on the SPI module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

# PIC16CR7X

| Address               | Name    | Bit 7                | Bit 6       | Bit 5                         | Bit 4      | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR |      | Value on<br>all other<br>Resets |      |

|-----------------------|---------|----------------------|-------------|-------------------------------|------------|-----------|-------------|--------|--------|-------------------------|------|---------------------------------|------|

| 0Bh,8Bh.<br>10Bh,18Bh | INTCON  | GIE                  | PEIE        | TMR0IE                        | INTE       | RBIE      | TMR0IF      | INTF   | RBIF   | 0000                    | 000x | 0000                            | 000u |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF                          | TXIF       | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000                    | 0000 | 0000                            | 0000 |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE                          | TXIE       | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000                    | 0000 | 0000                            | 0000 |

| 87h                   | TRISC   | PORTC Da             | ta Directio | on Registe                    | n Register |           |             | 1111   | 1111   | 1111                    | 1111 |                                 |      |

| 13h                   | SSPBUF  | Synchrono            | us Serial I | Port Recei                    | ve Buff    | er/Transm | nit Registe | r      |        | xxxx                    | xxxx | uuuu                            | uuuu |

| 14h                   | SSPCON  | WCOL                 | SSPOV       | SSPEN                         | CKP        | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000                    | 0000 | 0000                            | 0000 |

| 85h                   | TRISA   | _                    | _           | PORTA Data Direction Register |            |           | 11          | 1111   | 11     | 1111                    |      |                                 |      |

| 94h                   | SSPSTAT | SMP                  | CKE         | D/A                           | Ρ          | S         | R/W         | UA     | BF     | 0000                    | 0000 | 0000                            | 0000 |

Legend:x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.Note1:Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

DS21993C-page 64

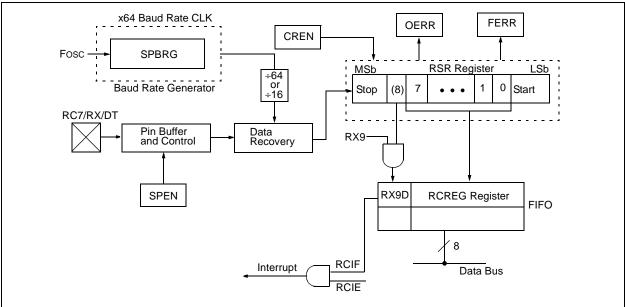

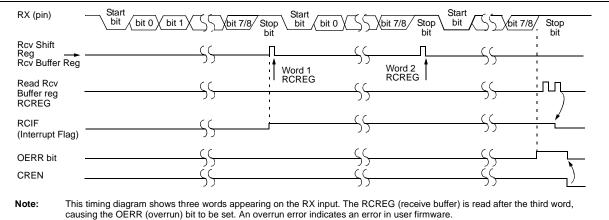

Steps to follow when setting up an Asynchronous Reception:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

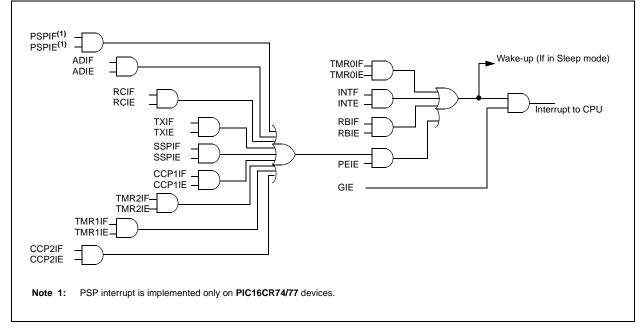

### 12.11 Interrupts

The PIC16CR7X family has up to 12 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual                        | interrup | t flag | bits  | are   | set,  |

|-------|-----------------------------------|----------|--------|-------|-------|-------|

|       | regardless                        | of the   | status | of th | eir c | orre- |

|       | sponding mask bit or the GIE bit. |          |        |       |       |       |

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit or the GIE bit.

#### FIGURE 12-10: INTERRUPT LOGIC

## 13.0 INSTRUCTION SET SUMMARY

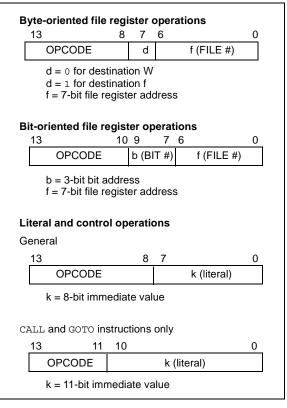

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> Assembler. A complete description of each instruction is also available in the " $PIC^{\mbox{\ensuremath{\mathbb{R}}}}$  Mid-Range MCU Family Reference Manual" (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight- or eleven-bit constant or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16CR7X products, do not use |

|       | the OPTION and TRIS instructions.     |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 13.1 Read-Modify-Write operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

## TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

#### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                        |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

## SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                           |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \underline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                        |

| Status Affected: | TO, PD                                                                                                                                                                                                                                         |

| Description:     | The power-down Status bit $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |