Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ROM                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr76t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

PIC16CR73 AND PIC16CR76 PINOUT DESCRIPTION (CONTINUED) **TABLE 1-2:**

| Pin Name        | PDIP<br>SSOP<br>SOIC<br>Pin# | MLF<br>Pin# | I/O/P<br>Type | Buffer<br>Type | Description                                                       |

|-----------------|------------------------------|-------------|---------------|----------------|-------------------------------------------------------------------|

|                 |                              |             |               |                | PORTC is a bidirectional I/O port.                                |

| RC0/T1OSO/T1CKI | 11                           | 8           |               | ST             |                                                                   |

| RC0             |                              |             | I/O           |                | Digital I/O.                                                      |

| T1OSO           |                              |             | 0             |                | Timer1 oscillator output.                                         |

| T1CKI           |                              |             | I             |                | Timer1 external clock input.                                      |

| RC1/T1OSI/CCP2  | 12                           | 9           |               | ST             |                                                                   |

| RC1             |                              |             | I/O           |                | Digital I/O.                                                      |

| T1OSI           |                              |             | ı             |                | Timer1 oscillator input.                                          |

| CCP2            |                              |             | I/O           |                | Capture2 input, Compare2 output, PWM2 output.                     |

| RC2/CCP1        | 13                           | 10          |               | ST             |                                                                   |

| RC2             |                              |             | I/O           |                | Digital I/O.                                                      |

| CCP1            |                              |             | I/O           |                | Capture1 input/Compare1 output/PWM1 output.                       |

| RC3/SCK/SCL     | 14                           | 11          |               | ST             |                                                                   |

| RC3             |                              |             | I/O           |                | Digital I/O.                                                      |

| SCK             |                              |             | I/O           |                | Synchronous serial clock input/output for SPI mode.               |

| SCL             |                              |             | I/O           |                | Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |

| RC4/SDI/SDA     | 15                           | 12          |               | ST             |                                                                   |

| RC4             |                              |             | I/O           |                | Digital I/O.                                                      |

| SDI             |                              |             | I             |                | SPI data in.                                                      |

| SDA             |                              |             | I/O           |                | I <sup>2</sup> C™ data I/O.                                       |

| RC5/SDO         | 16                           | 13          |               | ST             |                                                                   |

| RC5             |                              |             | I/O           |                | Digital I/O.                                                      |

| SDO             |                              |             | 0             |                | SPI data out.                                                     |

| RC6/TX/CK       | 17                           | 14          |               | ST             |                                                                   |

| RC6             |                              |             | I/O           |                | Digital I/O.                                                      |

| TX              |                              |             | 0             |                | USART asynchronous transmit.                                      |

| CK              |                              |             | I/O           |                | USART 1 synchronous clock.                                        |

| RC7/RX/DT       | 18                           | 15          |               | ST             |                                                                   |

| RC7             |                              |             | I/O           |                | Digital I/O.                                                      |

| RX              |                              |             | I             |                | USART asynchronous receive.                                       |

| DT              |                              |             | I/O           |                | USART synchronous data.                                           |

| Vss             | 8, 19                        | 5, 16       | Р             | _              | Ground reference for logic and I/O pins.                          |

| VDD             | 20                           | 17          | Р             | _              | Positive supply for logic and I/O pins.                           |

Legend:

I = input

O = output

I/O = input/output

P = power

TTL = TTL input

ST = Schmitt Trigger input

This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Verify mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

FIGURE 2-2: PIC16CR77/76 REGISTER FILE MAP

| £                    | File<br>Address | A                    | File<br>Address |                      | File<br>Address |                     | File<br>Addre |

|----------------------|-----------------|----------------------|-----------------|----------------------|-----------------|---------------------|---------------|

| Indirect addr.(*)    | 00h             | Indirect addr.(*)    | 80h             | Indirect addr.(*)    | 100h            | Indirect addr.(*)   | 180           |

| TMR0                 | 01h             | OPTION_REG           | 81h             | TMR0                 | 101h            | OPTION_REG          | 181           |

| PCL                  | 02h             | PCL                  | 82h             | PCL                  | 102h            | PCL                 | 182           |

| STATUS               | 03h             | STATUS               | 83h             | STATUS               | 103h            | STATUS              | 183           |

| FSR                  | 04h             | FSR                  | 84h             | FSR                  | 104h            | FSR                 | 184           |

| PORTA                | 05h             | TRISA                | 85h             |                      | 105h            |                     | 185           |

| PORTB                | 06h             | TRISB                | 86h             | PORTB                | 106h            | TRISB               | 186           |

| PORTC                | 07h             | TRISC                | 87h             |                      | 107h            |                     | 187           |

| PORTD <sup>(1)</sup> | 08h             | TRISD <sup>(1)</sup> | 88h             |                      | 108h            |                     | 188           |

| PORTE <sup>(1)</sup> | 09h             | TRISE <sup>(1)</sup> | 89h             |                      | 109h            |                     | 189           |

| PCLATH               | 0Ah             | PCLATH               | 8Ah             | PCLATH               | 10Ah            | PCLATH              | 18/           |

| INTCON               | 0Bh             | INTCON               | 8Bh             | INTCON               | 10Bh            | INTCON              | 18E           |

| PIR1                 | 0Ch             | PIE1                 | 8Ch             | PMDATA               | 10Ch            | PMCON1              | 180           |

| PIR2                 | 0Dh             | PIE2                 | 8Dh             | PMADR                | 10Dh            |                     | 18[           |

| TMR1L                | 0Eh             | PCON                 | 8Eh             | PMDATH               | 10Eh            |                     | 18E           |

| TMR1H                | 0Fh             | . 55.1               | 8Fh             | PMADRH               | 10Fh            |                     | 18F           |

| T1CON                | 10h             |                      | 90h             | 7 1111 12 1 11 1     | 110h            |                     | 190           |

| TMR2                 | 11h             |                      | 91h             |                      | 111h            |                     | 191           |

| T2CON                | 12h             | PR2                  | 92h             |                      | 112h            |                     | 192           |

| SSPBUF               | 13h             | SSPADD               | 93h             |                      | 113h            |                     | 193           |

| SSPCON               | 14h             | SSPSTAT              | 94h             |                      | 114h            |                     | 194           |

| CCPR1L               | 15h             | 001 01741            | 95h             |                      | 115h            |                     | 195           |

| CCPR1H               | 16h             |                      | 96h             |                      | 116h            |                     | 196           |

| CCP1CON              | 17h             |                      | 97h             | General              | 117h            | General             | 197           |

| RCSTA                | 18h             | TXSTA                | 98h             | Purpose              | 118h            | Purpose<br>Register | 198           |

| TXREG                | 19h             | SPBRG                | 99h             | Register<br>16 Bytes | 119h            | 16 Bytes            | 199           |

| RCREG                | 1Ah             | OI BIXO              | 9Ah             |                      | 11Ah            |                     | 19/           |

| CCPR2L               | 1Bh             |                      | 9Bh             |                      | 11Bh            |                     | 19E           |

| CCPR2H               | 1Ch             |                      | 9Ch             |                      | 11Ch            |                     | 190           |

| CCP2CON              | 1Dh             |                      | 9Dh             |                      | 11Dh            |                     | 190           |

| ADRES                | 1Eh             |                      | 9Eh             |                      | 11Eh            |                     | 19E           |

| ADCON0               | 1Fh             | ADCON1               | 9Fh             |                      | 11Fh            |                     | 19F           |

| 71200110             | 20h             | 7.000111             | A0h             |                      | 120h            |                     | 1A(           |

| General              | 2011            | General              | AUN             | General              |                 | General             | IAC           |

| Purpose              |                 | Purpose              |                 | Purpose              |                 | Purpose             |               |

| Register             |                 | Register             |                 | Register             |                 | Register            |               |

| 96 Bytes             |                 | 80 Bytes             | EFh             | 80 Bytes             | 16Fh            | 80 Bytes            | 1EF           |

|                      | 7Fh             | accesses<br>70h-7Fh  | F0h<br>FFh      | accesses<br>70h-7Fh  | 170h<br>17Fh    | accesses<br>70h-7Fh | 1F0           |

| Bank 0               | 1111            | Bank 1               | 1 1 11          | Bank 2               | 17111           | Bank 3              |               |

Unimplemented data memory locations, read as '0'.

Note 1: These registers are not implemented on 28-pin devices.

<sup>\*</sup> Not a physical register.

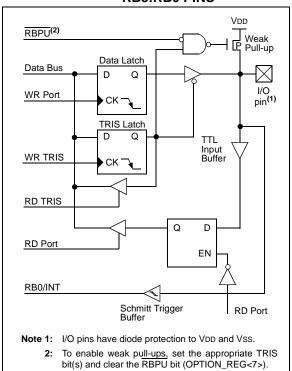

### 4.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impendance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{RBPU}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

FIGURE 4-3: BLOCK DIAGRAM OF RB3:RB0 PINS

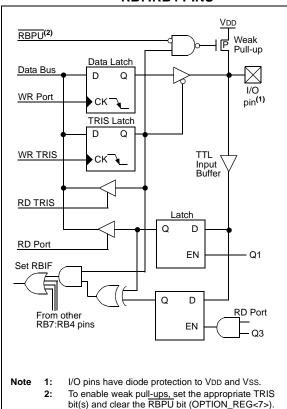

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt on mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, "Implementing Wake-up on Key Stroke" (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in **Section 12.11.1 "INT Interrupt"**.

FIGURE 4-4: BLOCK DIAGRAM OF RB7:RB4 PINS

### REGISTER 4-1: TRISE: (ADDRESS 89h)

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | Bit 2 | Bit 1 | Bit 0 |

| bit 7 |     |       |         |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Parallel Slave Port Status/Control bits:

**IBF:** Input Buffer Full Status bit

1 = A word has been received and is waiting to be read by the CPU

0 = No word has been received

bit 6 OBF: Output Buffer Full Status bit

1 = The output buffer still holds a previously written word

0 = The output buffer has been read

bit 5 IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)

1 = A write occurred when a previously input word has not been read

(must be cleared in software)

0 = No overflow occurred

bit 4 **PSPMODE**: Parallel Slave Port Mode Select bit

1 = Parallel Slave Port mode

0 = General Purpose I/O mode

bit 3 Unimplemented: Read as '0'

bit 2 PORTE Data Direction bits:

Bit 2: Direction Control bit for pin RE2/CS/AN7

1 = Input

0 = Output

bit 1 Bit 1: Direction Control bit for pin RE1/WR/AN6

1 = Input

0 = Output

bit 0: Direction Control bit for pin RE0/RD/AN5

1 = Input

0 = Output

### 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode, to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

# 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 and CCP2 special event triggers.

TABLE 6-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Oce Type | Eroguenov | Capacito | ors Used: |

|----------|-----------|----------|-----------|

| Osc Type | Frequency | OSC1     | OSC2      |

| LP       | 32 kHz    | 47 pF    | 47 pF     |

|          | 100 kHz   | 33 pF    | 33 pF     |

|          | 200 kHz   | 15 pF    | 15 pF     |

### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes (below) table for additional information.

| Commonly Used Crystals: |                       |  |  |  |  |  |  |  |

|-------------------------|-----------------------|--|--|--|--|--|--|--|

| 32.768 kHz              | Epson C-001R32.768K-A |  |  |  |  |  |  |  |

| 100 kHz                 | Epson C-2 100.00 KC-P |  |  |  |  |  |  |  |

| 200 kHz                 | STD XTL 200.000 kHz   |  |  |  |  |  |  |  |

**Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address               | Name   | Bit 7                | Bit 6                                                                      | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|--------|----------------------|----------------------------------------------------------------------------|---------|-----------|-----------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                                                       | TMR0IE  | INTE      | RBIE      | TMR0IF | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                       | RCIF    | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                       | RCIE    | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 0Eh                   | TMR1L  | Holding Reg          | gister for th                                                              |         | xxxx xxxx | uuuu uuuu |        |        |        |                         |                                 |

| 0Fh                   | TMR1H  | Holding Reg          | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |         |           |           |        |        |        |                         | uuuu uuuu                       |

| 10h                   | T1CON  | _                    | _                                                                          | T1CKPS1 | T1CKPS0   | T1OSCEN   | T1SYNC | TMR1CS | TMR10N | 00 0000                 | uu uuuu                         |

$\textbf{Legend:} \qquad \textbf{x} = \text{unknown, } \textbf{u} = \text{unchanged, } \textbf{-} = \text{unimplemented, read as '0'}. \textbf{Shaded cells are not used by the Timer1 module.}$

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

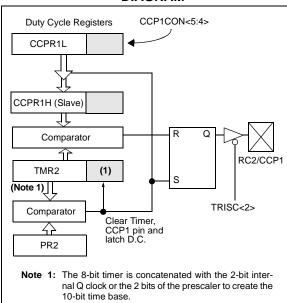

### 8.5 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 8.5.3** "**SetUp for PWM Operation**".

FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

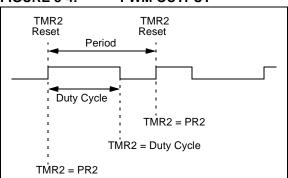

A PWM output (Figure 8-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 8-4: PWM OUTPUT

#### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =

$$[(PR2) + 1] \cdot 4 \cdot TOSC \cdot$$

(TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 8.3 "Capture Mode") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution =

$$\frac{\log(\frac{\text{Fosc}}{\text{Fpwm}})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

### 9.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 9-7). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- Receive first (high) byte of address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- Update the SSPADD register with the first (high) byte of address, if match releases SCL line, this will clear bit UA.

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- Receive first (high) byte of address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| TARI F 9-2. | DATA TRANSFER RECEIVED BYT | F ACTIONS |

|-------------|----------------------------|-----------|

| Status Bits as Data<br>Transfer is Received |       | SSPSR → SSPBUF | Generate ACK Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|---------------------------------------------|-------|----------------|--------------------|----------------------------------------|--|--|

| BF                                          | SSPOV |                | Pulse              | if enabled)                            |  |  |

| 0                                           | 0     | Yes            | Yes                | Yes                                    |  |  |

| 1                                           | 0     | No             | No                 | Yes                                    |  |  |

| 1                                           | 1     | No             | No                 | Yes                                    |  |  |

| 0                                           | 1     | No             | No                 | Yes                                    |  |  |

**Note:** Shaded cells show the conditions where the user software did not properly clear the overflow condition.

### 9.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

### 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-to-zero (NRZ) format (one Start bit, eight or nine data bits, and one Stop bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- · Sampling Circuit

- · Asynchronous Transmitter

- Asynchronous Receiver

## 10.2.1 USART ASYNCHRONOUS TRANSMITTER

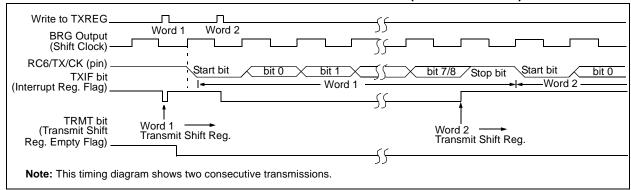

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the Transmit (serial) Shift Register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data by firmware. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register, the TXREG register is empty. One instruction cycle later, flag bit TXIF (PIR1<4>) and flag bit TRMT (TXSTA<1>) are set. The TXIF interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read-only bit, which is set one instruction cycle after the TSR register becomes empty, and is cleared one instruction cycle after the TSR register is loaded. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to high-impendance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK-TO-BACK)

TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | ansmit Da | ta Registe | er    |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  | or Registe | r     |       |        |        |        | 0000 0000               | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76; always maintain these bits clear.

## 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate, or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in

the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received, therefore, it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading RCREG register, in order not to lose the old FERR and RX9D information.

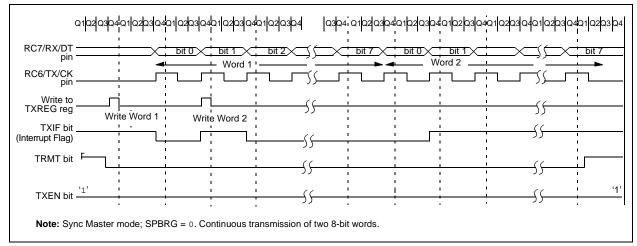

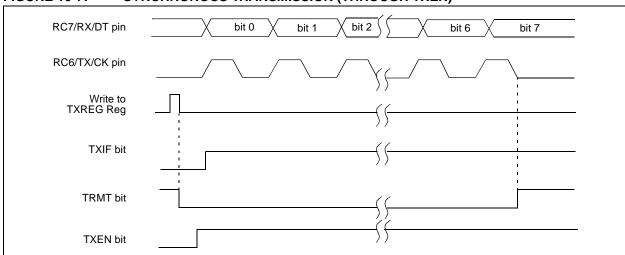

FIGURE 10-6: SYNCHRONOUS TRANSMISSION

FIGURE 10-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

TABLE 10-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5      | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------|------------|-----------|-------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TMR0IE     | INTE      | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN       | CREN      | _     | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit D | ata Regist | er        |       |        |        |        | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN       | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010               | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat  | 0000 0000  | 0000 0000 |       |        |        |        |                         |                                 |

**Legend:** x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76 devices; always maintain these bits clear.

### REGISTER 11-2: ADCON1: (ADDRESS 1Fh)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-3 **Unimplemented**: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | VDD  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | VDD  |

A = Analog input D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16CR74/77 only.

### REGISTER 12-1: CONFIGURATION WORD: (ADDRESS 2007h<sup>(1)</sup>)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _     |

| bit 13 |     |     |     |     |     | bit 7 |

| R/P-1 | U-0 | R/P-1 | R/P-1  | R/P-1 | R/P-1 | R/P-1 |

|-------|-----|-------|--------|-------|-------|-------|

| BOREN | _   | CP0   | PWRTEN | WDTEN | FOSC1 | FOSC0 |

| bit 6 |     |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 13-7 Unimplemented: Read as '1'

bit 6 BOREN: Brown-out Reset Enable bit

1 = BOR enabled0 = BOR disabled

bit 5 Unimplemented: Read as '1'

bit 4 CP0: ROM Program Memory Code Protection bit

1 = Code protection off

0 = All memory locations code protected

bit 3 **PWRTEN**: Power-up Timer Enable bit

1 = PWRT disabled0 = PWRT enabled

bit 2 WDTEN: Watchdog Timer Enable bit

1 = WDT enabled0 = WDT disabled

bit 1-0 FOSC1:FOSC0: Oscillator Selection bits

11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator

**Note 1:** The erased (unprogrammed) value of the Configuration Word is 3FFFh.

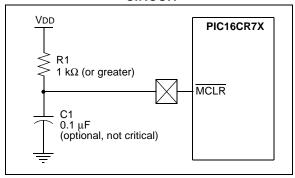

### 12.4 MCLR

PIC16CR7X devices have a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

FIGURE 12-5: RECOMMENDED MCLR CIRCUIT

### 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V-1.7V). To take advantage of the POR, tie the MCLR pin to VDD as described in **Section 12.4 "MCLR"**. A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. For additional information, refer to Application Note AN607, "Power-up Trouble Shooting" (DS00607).

### 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A Configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

### 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from Sleep.

### 12.8 Brown-out Reset (BOR)

The Configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a Reset may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in Reset for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT Configuration bit.

### 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16CR7X device operating in parallel.

Table 12-5 shows the Reset conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the Reset conditions for all the registers.

## 12.10 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset Status bit,  $\overline{BOR}$ . Bit  $\overline{BOR}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if

bit  $\overline{\mathsf{BOR}}$  cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the  $\overline{\mathsf{BOR}}$  bit is unpredictable.

Bit 1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

| One illeton One film metion | Power-            | -up       | D                 | Wake-up from |

|-----------------------------|-------------------|-----------|-------------------|--------------|

| Oscillator Configuration    | PWRTE = 0         | PWRTE = 1 | Brown-out         | Sleep        |

| XT, HS, LP                  | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc    |

| RC                          | 72 ms             | _         | 72 ms             | _            |

TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR<br>(PCON<1>) | BOR<br>(PCON<0>) | TO<br>(STATUS<4>) | PD<br>(STATUS<3>) | Significance                                            |

|------------------|------------------|-------------------|-------------------|---------------------------------------------------------|

| 0                | х                | 1                 | 1                 | Power-on Reset                                          |

| 0                | Х                | 0                 | x                 | Illegal, TO is set on POR                               |

| 0                | х                | х                 | 0                 | Illegal, PD is set on POR                               |

| 1                | 0                | 1                 | 1                 | Brown-out Reset                                         |

| 1                | 1                | 0                 | 1                 | WDT Reset                                               |

| 1                | 1                | 0                 | 0                 | WDT Wake-up                                             |

| 1                | 1                | u                 | u                 | MCLR Reset during normal operation                      |

| 1                | 1                | 1                 | 0                 | MCLR Reset during Sleep or interrupt wake-up from Sleep |

TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

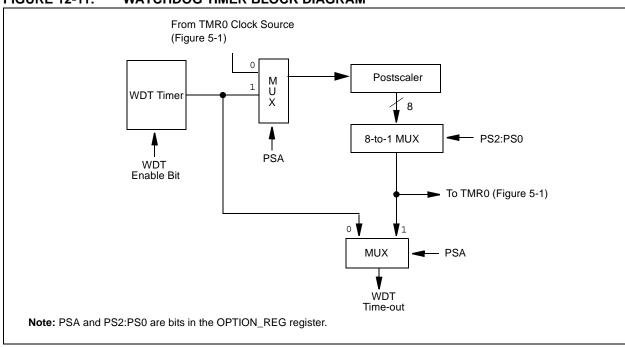

### 12.13 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing Configuration bit, WDTE (Section 12.1 "Configuration Bits").

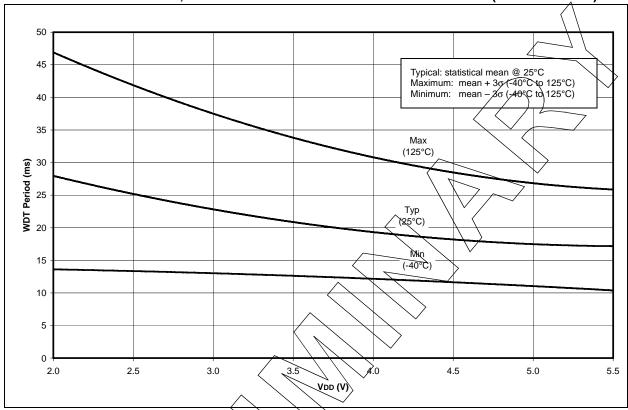

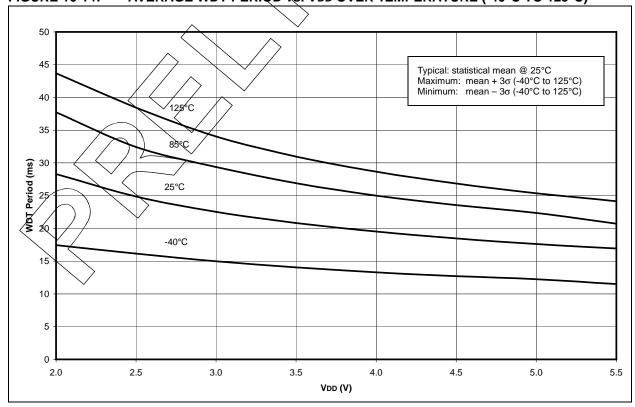

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler), may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 12-11: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|-----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BOREN <sup>(1)</sup> | _     | CP0   | PWRTEN <sup>(1)</sup> | WDTEN | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | T0CS  | TOSE  | PSA                   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

FIGURE 16-14: AVERAGE WDT PERIOD VS. VDD OVER TEMPERATURE (-40°C TO 125°C)

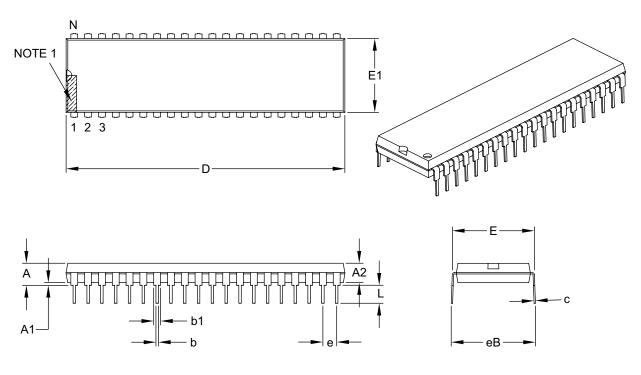

### 40-Lead Plastic Dual In-Line (P) - 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

| Dimensi                    | Dimension Limits |       | NOM      | MAX   |

| Number of Pins             | N                |       | 40       |       |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | А                | _     | _        | .250  |

| Molded Package Thickness   | A2               | .125  | _        | .195  |

| Base to Seating Plane      | A1               | .015  | _        | _     |

| Shoulder to Shoulder Width | Е                | .590  | _        | .625  |

| Molded Package Width       | E1               | .485  | _        | .580  |

| Overall Length             | D                | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                | .115  | _        | .200  |

| Lead Thickness             | С                | .008  | _        | .015  |

| Upper Lead Width           | b1               | .030  | _        | .070  |

| Lower Lead Width           | b                | .014  | _        | .023  |

| Overall Row Spacing §      | eB               | _     | _        | .700  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

### **INDEX**

| A                                                    |        | PORTE (In I/O Port Mode)                   |           |

|------------------------------------------------------|--------|--------------------------------------------|-----------|

| A/D                                                  |        | PWM Mode                                   |           |

| A/D Conversio Status (GO/DONE Bit)                   | 83     | RC Oscillator Mode                         | 92        |

| Acquisition Requirements                             |        | Recommended MCLR Circuit                   |           |

| ADCON0 Register                                      |        | Reset Circuit                              |           |

| ADCON1 Register                                      |        | SSP (I <sup>2</sup> C Mode)                | 65        |

| ADRES Register                                       |        | SSP (SPI Mode)                             | 62        |

|                                                      |        | Timer0/WDT Prescaler                       | 43        |

| Analog Port Pins                                     |        | Timer1                                     | 48        |

| Analog-to-Digital Converter                          |        | Timer2                                     |           |

| Associated Registers                                 |        | USART                                      |           |

| Configuring Analog Port Pins                         |        | Receive                                    | 76        |

| Configuring the Interrupt                            |        | USART Transmit                             |           |

| Configuring the Module                               |        | Watchdog Timer (WDT)                       |           |

| Conversion Clock                                     |        | BOR. See Brown-out Reset                   | 101       |

| Conversion Requirements                              | 137    | BRGH bit                                   | 71        |

| Conversions                                          | 87     |                                            |           |

| Converter Characteristics                            | 136    | Brown-out Reset (BOR) 89, 93, 94           | 4, 95, 96 |

| Effects of a RESET                                   | 87     | С                                          |           |

| Faster Conversion - Lower Resolution Trade-          | off 87 | _                                          |           |

| Internal Sampling Switch (Rss) Impedance             | 86     | C Compilers                                |           |

| Operation During SLEEP                               |        | MPLAB C18                                  |           |

| Source Impedance                                     |        | MPLAB C30                                  | 114       |

| Using the CCP Trigger                                |        | Capture/Compare/PWM (CCP)                  |           |

| Absolute Maximum Ratings                             |        | Associated Registers                       | 56, 58    |

| ACK pulse                                            |        | Capture Mode                               | 55        |

| •                                                    | •      | Prescaler                                  | 55        |

| ADCONO Register                                      |        | CCP Pin Configuration                      | 55, 56    |

| GO/DONE Bit                                          |        | CCP1                                       |           |

| ADCON1 Register                                      |        | RC2/CCP1 Pin                               | 9, 11     |

| ADRES Register                                       | 83     | CCP2                                       | ,         |

| Analog Port Pins. See A/D                            |        | RC1/T1OSI/CCP2 Pin                         | 9. 11     |

| Application Notes                                    |        | Compare Mode                               |           |

| AN552 (Implementing Wake-up on Key Stroke            |        | Software Interrupt Mode                    |           |

| Using PIC16F7X)                                      |        | Special Trigger Output                     |           |

| AN556 (Implementing a Table Read)                    | 26     | Timer1 Mode Selection                      |           |

| AN578 (Use of the SSP Module in the I <sup>2</sup> C |        | Example PWM Frequencies and Resolutions    |           |

| Multi-Master Environment)                            | 59     | ·                                          |           |

| AN607 (Power-up Trouble Shooting)                    | 94     | Interaction of Two CCP Modules             |           |

| Assembler                                            |        | PWM Duty Cycle                             |           |

| MPASM Assembler                                      | 114    | PWM Mode                                   |           |

| _                                                    |        | PWM Period                                 |           |

| В                                                    |        | Setup for PWM Operation                    |           |

| Banking, Data Memory                                 | 13     | Special Event Trigger and A/D Conversions  |           |

| BF bit                                               |        | Timer Resources                            |           |

| Block Diagrams                                       |        | CCP1 Module                                | 53        |

| A/D                                                  | 85     | CCP2 Module                                |           |

| Analog Input Model                                   |        | CCPR1H Register                            | 53        |

| · · · · · · · · · · · · · · · · · · ·                |        | CCPR1L Register                            |           |

| Capture Mode Operation                               |        | CCPxM<3:0> bits                            | 54        |

| Compare                                              |        | CCPxX and CCPxY bits                       |           |

| Crystal/Ceramic Resonator Operation (HS, XT          |        | CKE bit                                    |           |

| or LP Osc Configuration)                             | 91     | CKP bit                                    |           |

| External Clock Input Operation                       |        | Code Examples                              | 01        |

| (HS Osc Configuration)                               | 91     | Call of a Subroutine in Page 1 from Page 0 | 26        |

| Interrupt Logic                                      | 99     |                                            |           |

| PIC16CR73 and PIC16CR76                              | 6      | Changing Between Capture Prescalers        |           |

| PIC16CR74 and PIC16CR77                              | 7      | Changing Prescaler Assignment to Timer0    |           |

| PORTA                                                |        | Changing Prescaler Assignment to WDT       |           |

| RA3:RA0 and RA5 Port Pins                            | 31     | Indirect Addressing                        |           |

| RA4/T0CKI Pin                                        |        | Initializing PORTA                         |           |

| PORTB                                                |        | Reading a 16-bit Free-Running Timer        | 49        |

| RB3:RB0 Port Pins                                    | 33     | ROM Program Read                           | 30        |

| RB7:RB4 Port Pins                                    |        | Saving STATUS, W, and PCLATH Registers     |           |

| PORTC (Peripheral Output Override)                   |        | in RAM                                     | 100       |

|                                                      |        | Writing a 16-bit Free-Running Timer        | 49        |

| PORTD and PORTE (Portly) Slave Port)                 |        | Code Protection                            |           |

| PORTD and PORTE (Parallel Slave Port)                | 40     |                                            |           |

## PIC18FXXXX

| Operation During Code Protect          | 30       | ADRES (A/D Result)                         | 83     |

|----------------------------------------|----------|--------------------------------------------|--------|

| Organization                           | 13       | CCP1CON/CCP2CON Register                   | 54     |

| Paging                                 | 26       | Configuration Word Register                |        |

| PMADR Register                         | 29       | Initialization Conditions (table)          | 96–97  |

| PMADRH Register                        | 29       | INTCON (Interrupt Control)                 |        |

| Reading ROM                            | 30       | INTCON Register                            | 21     |

| Reading, PMADR Register                | 29       | OPTION_REG                                 | 20     |

| Reading, PMADRH Register               | 29       | OPTION_REG Register                        |        |

| Reading, PMCON1 Register               |          | PCON (Power Control)                       |        |

| Reading, PMDATA Register               |          | PCON Register                              |        |

| Reading, PMDATH Register               |          | PIE1 (Peripheral Interrupt Enable 1)       |        |

| RESET Vector                           |          | PIE1 Register                              |        |

| Program Verification                   |          | PIE2 (Peripheral Interrupt Enable 2)       |        |

| Programming, Device Instructions       |          | PIE2 Register                              |        |

| PUSH                                   |          | PIR1 (Peripheral Interrupt Request 1)      |        |

|                                        | 20       | PIR1 Register                              |        |

| R                                      |          | PIR2 (Peripheral Interrupt Request 2)      |        |

| R/W bit                                | 60 66 67 | PIR2 Register                              |        |

| RA0/AN0 Pin                            | , ,      | PMCON1 (Program Memory Control 1) Register |        |

| RA1/AN1 Pin                            | •        |                                            |        |

| RA2/AN2 Pin                            | ·        | RCSTA Register                             |        |

| RA3/AN3/VREF Pin                       | ·        | Special Function, Summary                  |        |

|                                        | •        | SSPCON Register                            |        |

| RA4/T0CKI Pin                          |          | SSPSTAT Register                           |        |

| RA5/SS/AN4 Pin                         | 8, 10    | STATUS Register                            |        |

| RAM. See Data Memory                   |          | T1CON Register                             |        |

| RB0/INT Pin                            |          | T2CON Register                             |        |

| RB1 Pin                                |          | TRISE Register                             | 38     |

| RB2 Pin                                |          | TXSTA Register                             | 69     |

| RB3 Pin                                | 8, 11    | RESET                                      | 89, 93 |

| RB4 Pin                                | ,        | Brown-out Reset (BOR). See Brown-out Reset | (BOR)  |

| RB5 Pin                                | 8, 11    | MCLR Reset. See MCLR                       |        |

| RB6 Pin                                | 8, 11    | Power-on Reset (POR). See Power-on Reset ( | (POR)  |

| RB7 Pin                                | 8, 11    | RESET Conditions for All Registers         | 96     |

| RC0/T1OSO/T1CKI Pin                    | 9, 11    | RESET Conditions for PCON Register         |        |

| RC1/T1OSI/CCP2 Pin                     | 9, 11    | RESET Conditions for Program Counter       |        |

| RC2/CCP1 Pin                           | 9, 11    | RESET Conditions for STATUS Register       |        |

| RC3/SCK/SCL Pin                        |          | Reset                                      |        |

| RC4/SDI/SDA Pin                        |          | WDT Reset. See Watchdog Timer (WDT)        |        |

| RC5/SDO Pin                            | · ·      | Revision History                           | 150    |

| RC6/TX/CK Pin                          | ·        |                                            |        |

| RC7/RX/DT Pin                          |          | S                                          |        |

| RCSTA Register                         |          | S (START) bit                              | 60     |

| CREN Bit                               | 70       | SCI. See USART                             |        |

| OERR Bit                               |          | SCL                                        | 65     |

| SPEN Bit                               |          | Serial Communication Interface. See USART  |        |

| SREN Bit                               |          | SLEEP89                                    | 02 102 |

| RD0/PSP0 Pin                           |          |                                            | ' '    |

|                                        |          | SMP bit                                    |        |

| RD1/PSP1 Pin                           |          | Software Simulator (MPLAB SIM)             |        |

| RD2/PSP2 Pin                           |          | Special Features of the CPU                |        |

| RD3/PSP3 Pin                           |          | Special Function Registers 1               |        |

| RD4/PSP4 Pin                           |          | Speed, Operating                           |        |

| RD5/PSP5 Pin                           |          | SPI Mode                                   |        |

| RD6/PSP6 Pin                           |          | Associated Registers                       |        |

| RD7/ <u>PS</u> P7 Pin                  |          | Serial Clock (SCK pin)                     | 59     |

| RE0/ <u>RD/</u> AN5 Pin                |          | Serial Data In (SDI pin)                   |        |

| RE1/WR/AN6 Pin                         | 12       | Serial Data Out (SDO pin)                  | 59     |

| RE2/CS/AN7 Pin                         | 12       | Slave Select                               | 59     |

| Reader Response                        | 168      | SSP                                        |        |

| Read-Modify-Write Operations           |          | Overview                                   |        |

| Receive Overflow Indicator bit (SSPOV) |          | RA5/SS/AN4 Pin                             | 8. 10  |

| Register File                          |          | RC3/SCK/SCL Pin                            |        |

| Registers                              |          | RC4/SDI/SDA Pin                            | ,      |

| ADCON0 (A/D Control 0)                 | ጸጓ       | RC5/SDO Pin                                | ,      |

| ADCONO (A/D Control o)                 |          | SSP I <sup>2</sup> C Operation             |        |

| ADCONO Register                        |          | Slave Mode                                 |        |

| ADCON1 (A/D Control 1)                 |          | SSPEN bit                                  |        |

| ADOON I REGISTEL                       | 04       | OOI EN DIL                                 | 01     |

# PIC16CR7X

| SSPIF bit                                       | 23    | I <sup>2</sup> C Bus Start/Stop Bits             | 132     |

|-------------------------------------------------|-------|--------------------------------------------------|---------|

| SSPM<3:0> bits                                  |       | I <sup>2</sup> C Reception (7-bit Address)       | 132     |

| SSPOV bit                                       |       | I <sup>2</sup> C Transmission (7-bit Address)    |         |

| Stack                                           |       | Parallel Slave Port                              |         |

| Overflows                                       | _     | Parallel Slave Port Read Waveforms               |         |

| Underflow                                       |       | Parallel Slave Port Write Waveforms              |         |

| STATUS Register                                 | 20    | Power-up Timer                                   |         |

| DC Bit                                          | 19    | PWM Output                                       |         |

| IRP Bit                                         |       | RESET                                            |         |

| PD Bit                                          |       | Slow Rise Time (MCLR Tied to VDD                 | 0       |

| TO Bit                                          |       | Through RC Network)                              | 98      |

| Z Bit                                           |       | SPI Master Mode (CKE = 0, SMP = 0)               |         |

| Synchronous Serial Port Enable bit (SSPEN)      | 61    | SPI Master Mode (CKE = 1, SMP = 1)               | 130     |

| Synchronous Serial Port Interrupt bit (SSPIF)   |       | SPI Mode (Master Mode)                           |         |

| Synchronous Serial Port Mode Select bits (SSPM- |       | SPI Mode (Slave Mode with CKE = 0)               |         |

| Synchronous Serial Port. See SSP                | ,     | SPI Mode (Slave Mode with CKE = 1)               |         |

|                                                 |       | SPI Slave Mode (CKE = 0)                         |         |

| Т                                               |       | SPI Slave Mode (CKE = 1)                         | 131     |

| T1CKPS0 bit                                     | 47    | Start-up Timer                                   | 126     |

| T1CKPS1 bit                                     | 47    | Time-out Sequence on Power-up                    |         |

| T10SCEN bit                                     |       | (MCLR Not Tied to VDD)                           |         |

| T1SYNC bit                                      |       | Case 1                                           | 98      |

| T2CKPS0 bit                                     | _     | Case 2                                           | 98      |

| T2CKPS1 bit                                     | _     | Time-out Sequence on Power-up                    |         |

| TAD                                             |       | (MCLR Tied to VDD Through RC Network)            |         |

| Time-out Sequence                               |       | Timer0                                           |         |

| Timer0                                          |       | Timer1                                           |         |

| Associated Registers                            |       | USART Asynchronous Master Transmission           | 74      |

| Clock Source Edge Select (T0SE Bit)             |       | USART Asynchronous Master Transmission           |         |