#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ROM                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr76t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

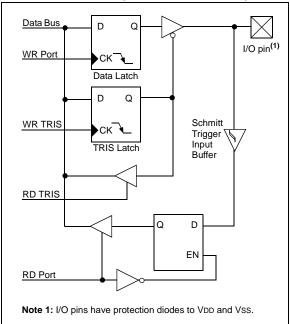

## 4.4 PORTD and TRISD Registers

This section is not applicable to the PIC16CR73 or PIC16CR76.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 4-6: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit#  | Buffer Type           | Function                                           |  |  |  |  |  |

|----------|-------|-----------------------|----------------------------------------------------|--|--|--|--|--|

| RD0/PSP0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 0 |  |  |  |  |  |

| RD1/PSP1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 1 |  |  |  |  |  |

| RD2/PSP2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 2 |  |  |  |  |  |

| RD3/PSP3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 3 |  |  |  |  |  |

| RD4/PSP4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 4 |  |  |  |  |  |

| RD5/PSP5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 5 |  |  |  |  |  |

| RD6/PSP6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit 6 |  |  |  |  |  |

| RD7/PSP7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit   |  |  |  |  |  |

## TABLE 4-7:PORTD FUNCTIONS

**Legend:** ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

| TABLE 4-8: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Address | Name  | Bit 7 | Bit 6    | Bit 5     | Bit 4                         | Bit 3    | Bit 2       | Bit 1        | Bit 0      | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |  |

|---------|-------|-------|----------|-----------|-------------------------------|----------|-------------|--------------|------------|-------------------------|---------------------------------|--|

| 08h     | PORTD | RD7   | RD6      | RD5       | RD4                           | RD3      | RD2         | RD1          | RD0        | xxxx xxxx               | uuuu uuuu                       |  |

| 88h     | TRISD | PORT  | D Data D | Direction | irection Register 1111 1111 1 |          |             |              |            |                         |                                 |  |

| 89h     | TRISE | IBF   | OBF      | IBOV      | PSPMODE                       | —        | PORTE Da    | ata Directio | on bits    | 0000 -111               | 0000 -111                       |  |

| Logondu |       |       | unahan   | and -     | unimplomonto                  | d rood a | ha 'a' Shad | od oollo or  | o pot upod |                         |                                 |  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

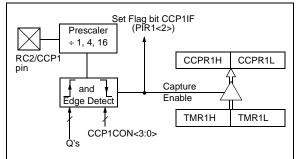

## 8.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following and is configured by CCPxCON<3:0>:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

## 8.3.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 pin is configured as an |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|

|       | output, a write to the port can cause a |  |  |  |  |  |  |  |  |

|       | capture condition.                      |  |  |  |  |  |  |  |  |

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

## 8.3.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ;the new prescaler      |

|       |             | ;move value and CCP ON  |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ;value                  |

|       |             |                         |

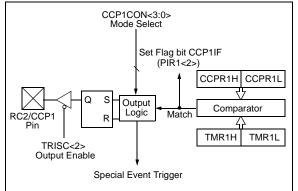

## 8.4 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- clear TMR1H and TMR1L registers

- NOT set interrupt flag bit TMR1F (PIR1<0>)

- (for CCP2 only) set the GO/DONE bit (ADCON0<2>)

## 8.5 PWM Mode (PWM)

FIGURE 8-3:

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 8.5.3** "**SetUp for PWM Operation**".

SIMPLIFIED PWM BLOCK

| DIAGRAM        |                               |                                         |  |  |  |  |  |  |  |

|----------------|-------------------------------|-----------------------------------------|--|--|--|--|--|--|--|

| Duty Cycle Reg | isters                        | CCP1CON<5:4>                            |  |  |  |  |  |  |  |

| CCPR1L         |                               | $\leftarrow$                            |  |  |  |  |  |  |  |

|                | (1)<br>Clear<br>CCP1<br>latch | is concatenated with the 2-bit inter-   |  |  |  |  |  |  |  |

|                | ime base                      | e 2 bits of the prescaler to create the |  |  |  |  |  |  |  |

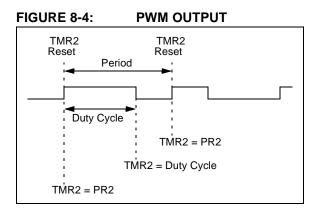

A PWM output (Figure 8-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 8.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period =  $[(PR2) + 1] \cdot 4 \cdot TOSC \cdot$

(TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

## 8.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

|           | 0,                                                                                                                  |

|-----------|---------------------------------------------------------------------------------------------------------------------|

| Resolutio | $\operatorname{pn} = \frac{\log\left(\frac{\operatorname{Fosc}}{\operatorname{FpWM}}\right)}{\log(2)} \text{ bits}$ |

| Note:     | If the PWM duty cycle value is longer than<br>the PWM period, the CCP1 pin will not be<br>cleared.                  |

Note: The Timer2 postscaler (see Section 8.3 "Capture Mode") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

## 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode Idle (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

## 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions, allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

| ABLE 3-3. REGISTERS ASSOCIATED WITH C OF ERATION |         |                      |                                              |                                     |           |           |             |        |        |                         |                                 |

|--------------------------------------------------|---------|----------------------|----------------------------------------------|-------------------------------------|-----------|-----------|-------------|--------|--------|-------------------------|---------------------------------|

| Address                                          | Name    | Bit 7                | Bit 6                                        | Bit 5                               | Bit 4     | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

| 0Bh, 8Bh,<br>10Bh,18Bh                           | INTCON  | GIE                  | PEIE                                         | TMR0IE                              | INTE      | RBIE      | TMR0IF      | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                                              | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                         | RCIF                                | TXIF      | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 8Ch                                              | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                         | RCIE                                | TXIE      | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 13h                                              | SSPBUF  | Synchrono            | us Serial                                    | Port Rece                           | eive Buff | er/Transn | nit Registe | er     |        | xxxx xxxx               | uuuu uuuu                       |

| 93h                                              | SSPADD  | Synchrono            | us Serial                                    | Port (I <sup>2</sup> C <sup>1</sup> | ™ mode)   | Address   | Register    |        |        | 0000 0000               | 0000 0000                       |

| 14h                                              | SSPCON  | WCOL                 | WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1 SSPM0 |                                     |           |           |             |        |        | 0000 0000               | 0000 0000                       |

| 94h                                              | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup>                           | D/A                                 | Р         | S         | R/W         | UA     | BF     | 0000 0000               | 0000 0000                       |

| 87h                                              | TRISC   | PORTC Da             | ata Direct                                   | ion Regist                          | er        | •         | •           |        | •      | 1111 1111               | 1111 1111                       |

TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:**  $x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in <math>l^2C^{TM}$  mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16CR73/76; always maintain these bits clear.

**2:** Maintain these bits clear in I<sup>2</sup>C mode.

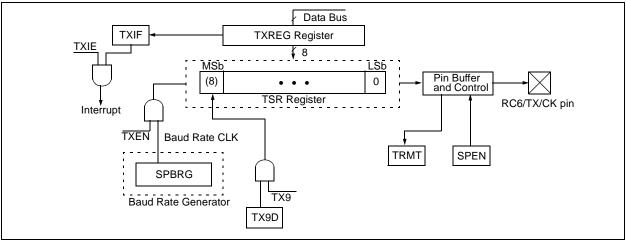

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

Steps to follow when setting up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

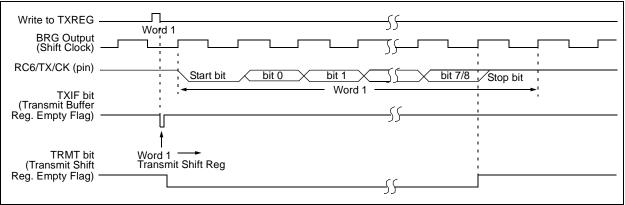

## FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

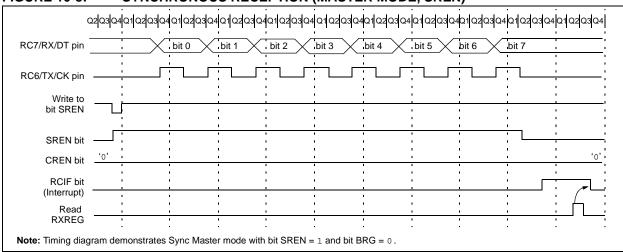

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG, in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 7. Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

## FIGURE 10-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| Address                | Name   | Bit 7                | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|-----------|------------|-------|-------|--------|--------|--------|----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TMR0IE     | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN       | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x            | 0000 -00x                       |

| 1Ah                    | RCREG  | USART Re             | eceive Da | ta Registe | r     |       |        |        |        | 0000 0000            | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generat   | or Registe | r     |       |        |        |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16CR73/76 devices; always maintain these bits clear.

## 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode, in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit when the master device drives the CK line.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from Sleep and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Follow these steps when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

## REGISTER 11-2: ADCON1: (ADDRESS 1Fh)

| U-0         U-0         U-0         U-0         R/W-0         R/W-0           -         -         -         -         PCFG2         PCFG1         PCFG0           bit 7         -         -         bit 7         -         bit 7         -         -         -         -         -         bit 7         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </th <th>Lanandi</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> | Lanandi |     |     |     |     |       |       |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|-----|-----|-------|-------|-------|

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |     |     |     |     |       |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 7   |     |     |     |     |       |       | bit 0 |

| U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —       |     |     | —   |     | PCFG2 | PCFG1 | PCFG0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0     | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | Vdd  |

| 001         | Α   | А   | Α   | Α   | VREF | Α                  | Α                  | А                  | RA3  |

| 010         | Α   | А   | Α   | А   | А    | D                  | D                  | D                  | Vdd  |

| 011         | Α   | А   | Α   | Α   | Vref | D                  | D                  | D                  | RA3  |

| 100         | А   | Α   | D   | D   | А    | D                  | D                  | D                  | Vdd  |

| 101         | Α   | А   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | Vdd  |

A = Analog input

D = Digital I/O

Note 1: RE0, RE1 and RE2 are implemented on the PIC16CR74/77 only.

| REGISTER 12-1: | <b>CONFIGURATION WORD:</b> | (ADDRESS 2007h <sup>(1)</sup> ) |

|----------------|----------------------------|---------------------------------|

|                |                            |                                 |

| U-0             | U-0                                                                                                                            | U-0              | U-0    | U-0                | U-0               | U-0                   |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|--------|--------------------|-------------------|-----------------------|--|

|                 | _                                                                                                                              | —                | —      | —                  | _                 | —                     |  |

| bit 13          |                                                                                                                                | ·                |        | •                  |                   | bit                   |  |

|                 |                                                                                                                                |                  |        |                    |                   |                       |  |

| R/P-1           | U-0                                                                                                                            | R/P-1            | R/P-1  | R/P-1              | R/P-1             | R/P-1                 |  |

| BOREN           | —                                                                                                                              | CP0              | PWRTEN | WDTEN              | FOSC1             | FOSC0                 |  |

| bit 6           |                                                                                                                                |                  |        |                    |                   | bit                   |  |

| Legend:         |                                                                                                                                |                  |        |                    |                   |                       |  |

| R = Readable    | bit                                                                                                                            | W = Writable bi  | t      | U = Unimpleme      | ented bit, read a | s '0'                 |  |

| -n = Value at P | POR                                                                                                                            | '1' = Bit is set |        | ʻ0' = Bit is clear | ed                | x = Bit is<br>unknown |  |

| bit 13-7        | Unimplemente                                                                                                                   | ed: Read as '1'  |        |                    |                   |                       |  |

| bit 6           | BOREN: Brown-out Reset Enable bit<br>1 = BOR enabled<br>0 = BOR disabled                                                       |                  |        |                    |                   |                       |  |

| bit 5           | Unimplemente                                                                                                                   | ed: Read as '1'  |        |                    |                   |                       |  |

| bit 4           | <b>CP0:</b> ROM Program Memory Code Protection bit<br>1 = Code protection off<br>0 = All memory locations code protected       |                  |        |                    |                   |                       |  |

| bit 3           | <b>PWRTEN</b> : Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                             |                  |        |                    |                   |                       |  |

| bit 2           | WDTEN: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                        |                  |        |                    |                   |                       |  |

| bit 1-0         | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator |                  |        |                    |                   |                       |  |

**Note 1:** The erased (unprogrammed) value of the Configuration Word is 3FFFh.

## 12.3 Reset

The PIC16CR7X differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 12-4. These bits are used in software to determine the nature of the Reset. See Table 12-6 for a full description of Reset states of all registers.

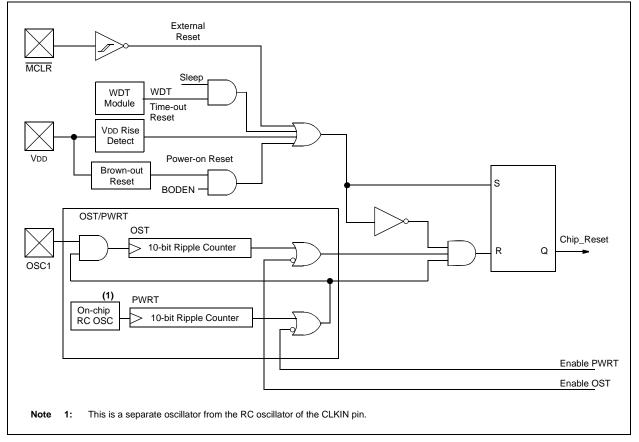

A simplified block diagram of the on-chip Reset circuit is shown in Figure 12-4.

## FIGURE 12-4: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Register |    | Dev | ices |    | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------|----|-----|------|----|------------------------------------|--------------------------|---------------------------------|

| PIE1     | 73 | 74  | 76   | 77 | r000 0000                          | r000 0000                | ruuu uuuu                       |

|          | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| PIE2     | 73 | 74  | 76   | 77 | 0                                  | 0                        | u                               |

| PCON     | 73 | 74  | 76   | 77 | dd                                 | uu                       | uu                              |

| PR2      | 73 | 74  | 76   | 77 | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPSTAT  | 73 | 74  | 76   | 77 | 00 0000                            | 00 0000                  | uu uuuu                         |

| SSPADD   | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| TXSTA    | 73 | 74  | 76   | 77 | 0000 -010                          | 0000 -010                | uuuu -uuu                       |

| SPBRG    | 73 | 74  | 76   | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADCON1   | 73 | 74  | 76   | 77 | 000                                | 000                      | uuu                             |

| PMDATA   | 73 | 74  | 76   | 77 | 0 0000                             | 0 0000                   | u uuuu                          |

| PMADR    | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMDATH   | 73 | 74  | 76   | 77 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PMADRH   | 73 | 74  | 76   | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PMCON1   | 73 | 74  | 76   | 77 | 1 0                                | 10                       | 1u                              |

|          |    |     |      |    |                                    |                          | 1 11.0                          |

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for Reset value for specific condition.

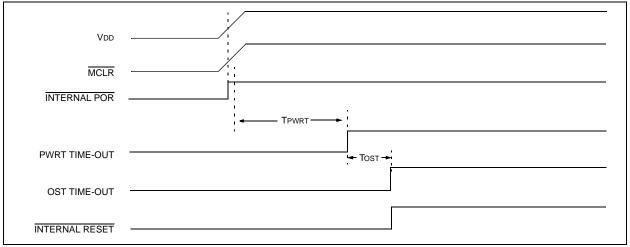

## FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK)

## 13.0 INSTRUCTION SET SUMMARY

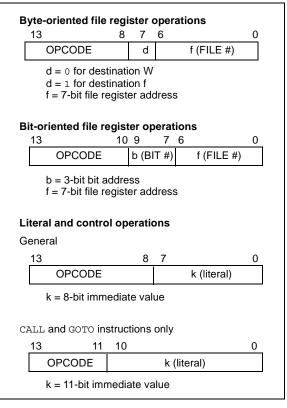

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> Assembler. A complete description of each instruction is also available in the " $PIC^{\mbox{\ensuremath{\mathbb{R}}}}$  Mid-Range MCU Family Reference Manual" (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight- or eleven-bit constant or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16CR7X products, do not use |

|       | the OPTION and TRIS instructions.     |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 13.1 Read-Modify-Write operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared for pins configured as inputs and using the PORTB interrupt-on-change feature.

## TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

#### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16CR7X

| CALL             | Call Subroutine                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                         |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                              |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                                            |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                            |

| Operands:                      | None                                                                                                                                                                      |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow PD \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set.                                            |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                        |

| Operands:        | $0 \le f \le 127$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                              |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| Param<br>No. | Sym  | Characteristic                                 | Min        | Тур†       | Max        | Units    | Conditions                                                           |

|--------------|------|------------------------------------------------|------------|------------|------------|----------|----------------------------------------------------------------------|

| A01          | Nr   | Resolution                                     | _          | -          | 8 bits     | bit      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$ |

| A02          | Eabs | Total absolute error                           | —          | _          | < ±1       | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$ |

| A03          | EIL  | Integral linearity error                       | —          | _          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                       |

| A04          | Edl  | Differential linearity error                   | —          | _          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                       |

| A05          | Efs  | Full scale error                               | —          | _          | < ±1       | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$ |

| A06          | EOFF | Offset error                                   | —          | —          | < ±1       | LSb      | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                       |

| A10          | —    | Monotonicity (Note 3)                          | —          | guaranteed | _          | _        | $VSS \le VAIN \le VREF$                                              |

| A20          | Vref | Reference voltage                              | 2.5<br>2.2 |            | 5.5<br>5.5 | V<br>V   | -40°C to +125°C<br>0°C to +125°C                                     |

| A25          | VAIN | Analog input voltage                           | Vss - 0.3  | _          | Vref + 0.3 | V        |                                                                      |

| A30          | ZAIN | Recommended impedance of analog voltage source | —          | _          | 10.0       | kΩ       |                                                                      |

| A40          | IAD  | A/D conversion current (VDD)                   | —          | 180        | —          | μA       | Average current<br>consumption when A/D<br>is on (Note 1).           |

| A50          | IREF | VREF input current (Note 2)                    | N/A<br>—   | _          | ±5<br>500  | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D Conversion<br>cycle.          |

#### TABLE 15-12: A/D CONVERTER CHARACTERISTICS:PIC16CR7X (INDUSTRIAL, EXTENDED)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from the RA3 pin or the VDD pin, whichever is selected as a reference input.

**3:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

## PIC16CR7X

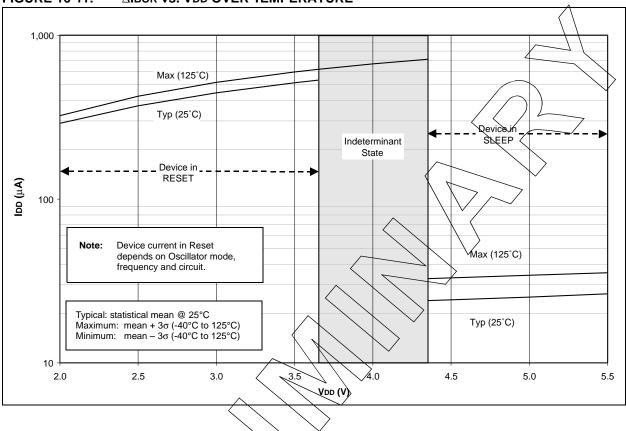

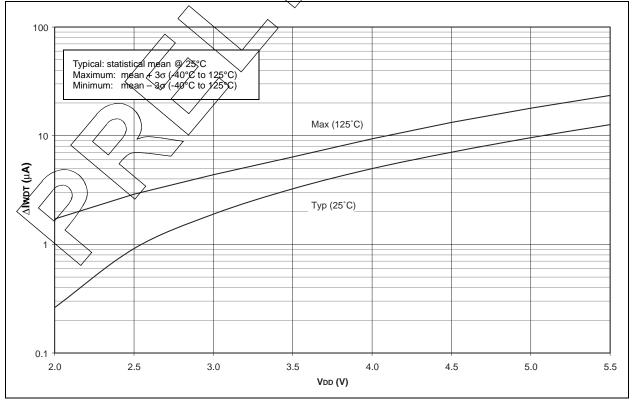

## FIGURE 16-11: △IBOR vs. VDD OVER TEMPERATURE

## PIC16CR7X

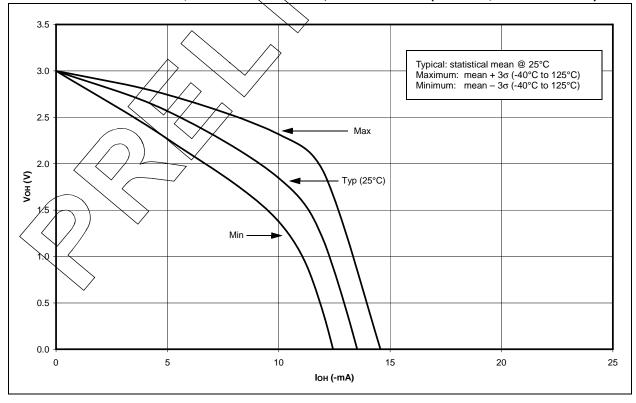

FIGURE 16-16: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 3V, -40°C TO 125°C)

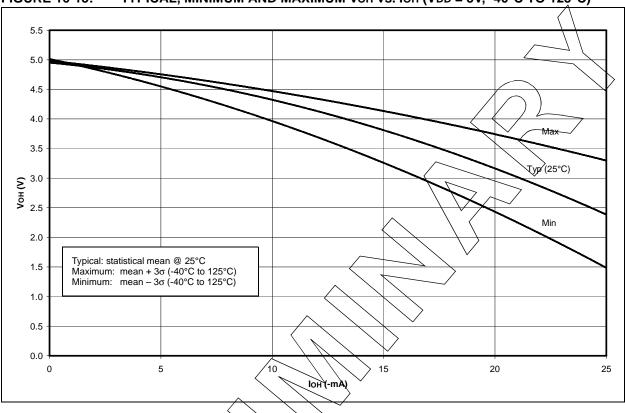

FIGURE 16-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

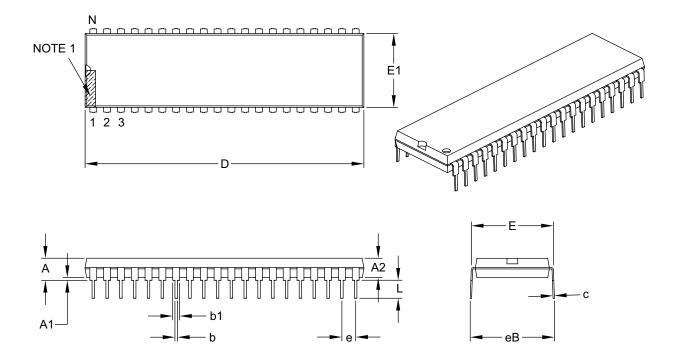

## 40-Lead Plastic Dual In-Line (P) – 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units                   |       | INCHES   |       |

|----------------------------|-------------------------|-------|----------|-------|

|                            | <b>Dimension Limits</b> | MIN   | NOM      | MAX   |

| Number of Pins             | N                       |       | 40       |       |

| Pitch                      | e                       |       | .100 BSC |       |

| Top to Seating Plane       | A                       | -     | -        | .250  |

| Molded Package Thickness   | A2                      | .125  | -        | .195  |

| Base to Seating Plane      | A1                      | .015  | -        | -     |

| Shoulder to Shoulder Width | E                       | .590  | -        | .625  |

| Molded Package Width       | E1                      | .485  | -        | .580  |

| Overall Length             | D                       | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                       | .115  | -        | .200  |

| Lead Thickness             | С                       | .008  | -        | .015  |

| Upper Lead Width           | b1                      | .030  | -        | .070  |

| Lower Lead Width           | b                       | .014  | -        | .023  |

| Overall Row Spacing §      | eB                      | -     | -        | .700  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

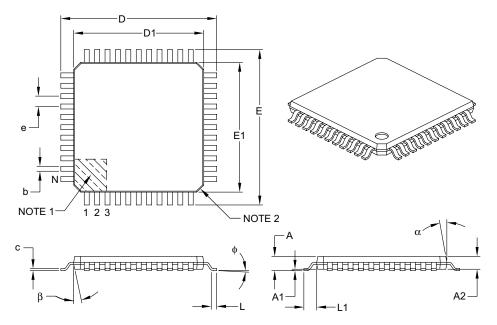

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS | 6    |

|--------------------------|------------------|-----------|-------------|------|

|                          | Dimension Limits | MIN       | NOM         | MAX  |

| Number of Leads          | N                | 44        |             |      |

| Lead Pitch               | е                | 0.80 BSC  |             |      |

| Overall Height           | A                | -         | -           | 1.20 |

| Molded Package Thickness | A2               | 0.95      | 1.00        | 1.05 |

| Standoff                 | A1               | 0.05      | -           | 0.15 |

| Foot Length              | L                | 0.45      | 0.60        | 0.75 |

| Footprint                | L1               |           | 1.00 REF    |      |

| Foot Angle               | ¢                | 0°        | 3.5°        | 7°   |

| Overall Width            | E                |           | 12.00 BSC   |      |

| Overall Length           | D                |           | 12.00 BSC   |      |

| Molded Package Width     | E1               | 10.00 BSC |             |      |

| Molded Package Length    | D1               |           | 10.00 BSC   |      |

| Lead Thickness           | С                | 0.09      | -           | 0.20 |

| Lead Width               | b                | 0.30      | 0.37        | 0.45 |

| Mold Draft Angle Top     | α                | 11°       | 12°         | 13°  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°         | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

## INDEX

| - 1 | L |

|-----|---|

| -   | • |

|     |   |

| A/D Conversio Status (GO/DONE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83                                                                               |

| Acquisition Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| ADCON0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83                                                                               |

| ADCON1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83                                                                               |

| ADRES Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83                                                                               |

| Analog Port Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Analog-to-Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83                                                                               |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                                                                               |

| Configuring Analog Port Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87                                                                               |

| Configuring the Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| Configuring the Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85                                                                               |

| Conversion Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 87                                                                               |

| Conversion Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 137                                                                              |

| Conversions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87                                                                               |

| Converter Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 136                                                                              |

| Effects of a RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87                                                                               |

| Faster Conversion – Lower Resolution Trade-off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87                                                                               |