Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

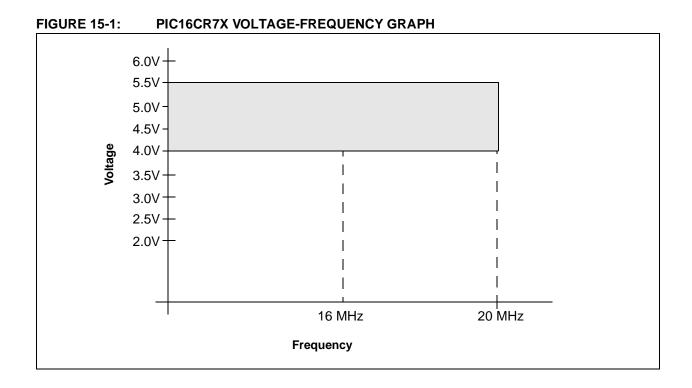

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ROM                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16cr77t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

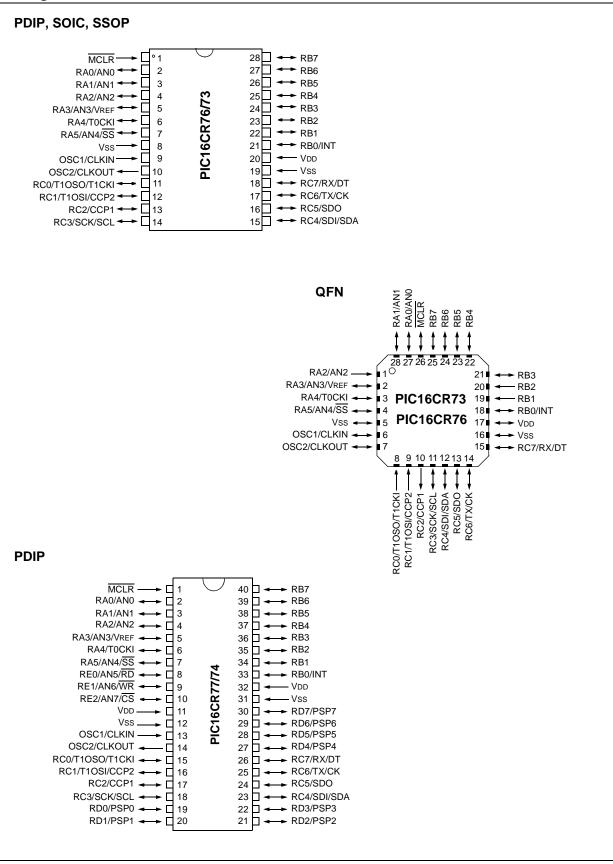

### **Pin Diagrams**

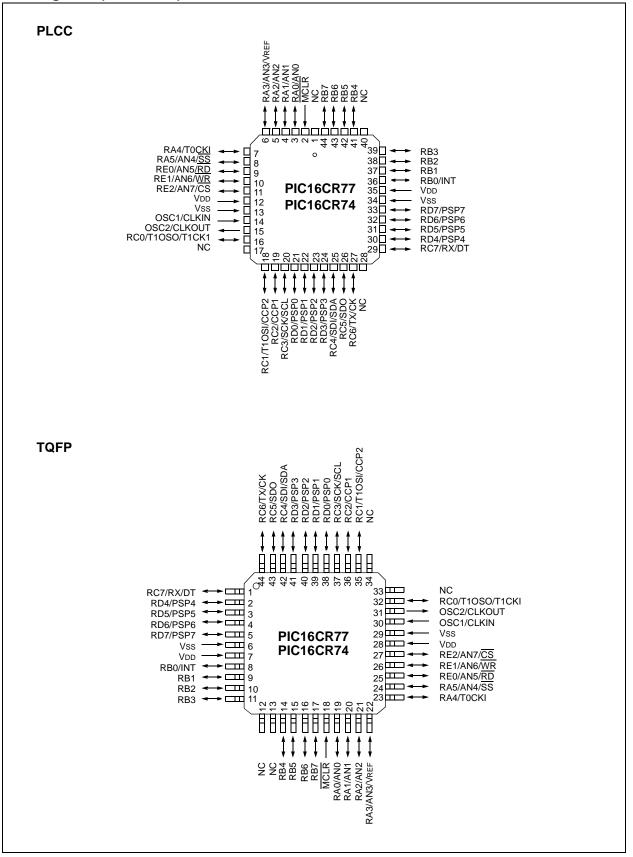

## **Pin Diagrams (Continued)**

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Address              | Name    | Bit 7                                | Bit 6                 | Bit 5         | Bit 4           | Bit 3           | Bit 2         | Bit 1         | Bit 0            | Value on<br>POR,<br>BOR | Details<br>on page |

|----------------------|---------|--------------------------------------|-----------------------|---------------|-----------------|-----------------|---------------|---------------|------------------|-------------------------|--------------------|

| Bank 0               |         |                                      |                       |               |                 |                 |               |               |                  |                         |                    |

| 00h <sup>(4)</sup>   | INDF    | Addressing                           | g this locatio        | n uses conte  | ents of FSR to  | address dat     | a memory (r   | not a physica | al register)     | 0000 0000               | 27, 96             |

| 01h                  | TMR0    | Timer0 Mc                            | ïmer0 Module Register |               |                 |                 |               |               |                  | XXXX XXXX               | 45, 96             |

| 02h <sup>(4)</sup>   | PCL     | Program C                            | Counter (PC)          | Least Signif  | icant Byte      |                 |               |               |                  | 0000 0000               | 26, 96             |

| 03h <sup>(4)</sup>   | STATUS  | IRP                                  | RP1                   | RP0           | TO              | PD              | Z             | DC            | C <sup>(2)</sup> | 0001 1xxx               | 19, 96             |

| 04h <sup>(4)</sup>   | FSR     | Indirect Da                          | ata Memory            | Address Poir  | nter            |                 |               |               |                  | xxxx xxxx               | 27, 96             |

| 05h                  | PORTA   |                                      | _                     | PORTA Dat     | a Latch when    | written: POF    | RTA pins wh   | en read       |                  | 0x 0000                 | 32, 96             |

| 06h                  | PORTB   | PORTB D                              | ata Latch wh          | en written: P | ORTB pins w     | /hen read       |               |               |                  | xxxx xxxx               | 34, 96             |

| 07h                  | PORTC   | PORTC D                              | ata Latch wh          | en written: P | ORTC pins v     | vhen read       |               |               |                  | XXXX XXXX               | 35, 96             |

| 08h <b>(5)</b>       | PORTD   | PORTD D                              | ata Latch wh          | en written: F | ORTD pins v     | vhen read       |               |               |                  | xxxx xxxx               | 36, 96             |

| 09h <b>(5)</b>       | PORTE   | _                                    | _                     | _             |                 | _               | RE2           | RE1           | RE0              | xxx                     | 39, 96             |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                                    |                       | _             | Write Buffer    | for the upper   | 5 bits of the | Program C     | ounter           | 0 0000                  | 26, 96             |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                                  | PEIE                  | TMR0IE        | INTE            | RBIE            | <b>TMR0IF</b> | INTF          | RBIF             | 0000 000x               | 21, 96             |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup>                 | ADIF                  | RCIF          | TXIF            | SSPIF           | CCP1IF        | TMR2IF        | TMR1IF           | 0000 0000               | 23, 96             |

| 0Dh                  | PIR2    | _                                    |                       | _             | _               | _               | _             | _             | CCP2IF           | 0                       | 24, 96             |

| 0Eh                  | TMR1L   | Holding Re                           | egister for th        | e Least Sign  | ificant Byte of | f the 16-bit TM | MR1 Registe   | er            |                  | xxxx xxxx               | 50, 96             |

| 0Fh                  | TMR1H   | Holding Re                           | egister for the       | e Most Signi  | ficant Byte of  | the 16-bit TN   | IR1 Registe   | r             |                  | XXXX XXXX               | 50, 96             |

| 10h                  | T1CON   | _                                    |                       | T1CKPS1       | T1CKPS0         | T1OSCEN         | T1SYNC        | TMR1CS        | TMR10N           | 00 0000                 | 47, 96             |

| 11h                  | TMR2    | Timer2 Mc                            | dule Registe          | er            |                 |                 |               |               |                  | 0000 0000               | 52, 96             |

| 12h                  | T2CON   |                                      | TOUTPS3               | TOUTPS2       | TOUTPS1         | TOUTPS0         | TMR2ON        | T2CKPS1       | T2CKPS0          | -000 0000               | 52, 96             |

| 13h                  | SSPBUF  | Synchrono                            | ous Serial Po         | ort Receive B | uffer/Transmi   | it Register     |               |               |                  | xxxx xxxx               | 64, 68, 96         |

| 14h                  | SSPCON  | WCOL                                 | SSPOV                 | SSPEN         | CKP             | SSPM3           | SSPM2         | SSPM1         | SSPM0            | 0000 0000               | 61, 96             |

| 15h                  | CCPR1L  | Capture/C                            | ompare/PWI            | M Register 1  | (LSB)           |                 |               |               |                  | xxxx xxxx               | 56, 96             |

| 16h                  | CCPR1H  | Capture/C                            | ompare/PWI            | M Register 1  | (MSB)           | T               | 1             | r             |                  | xxxx xxxx               | 56, 96             |

| 17h                  | CCP1CON |                                      | _                     | CCP1X         | CCP1Y           | CCP1M3          | CCP1M2        | CCP1M1        | CCP1M0           | 00 0000                 | 54, 96             |

| 18h                  | RCSTA   | SPEN                                 | RX9                   | SREN          | CREN            | —               | FERR          | OERR          | RX9D             | 0000 -00x               | 70, 96             |

| 19h                  | TXREG   | USART Transmit Data Register         |                       |               |                 |                 | 0000 0000     | 75, 96        |                  |                         |                    |

| 1Ah                  | RCREG   | USART Receive Data Register          |                       |               |                 |                 | 0000 0000     | 77, 96        |                  |                         |                    |

| 1Bh                  | CCPR2L  | Capture/Compare/PWM Register 2 (LSB) |                       |               |                 |                 |               | xxxx xxxx     | 58, 96           |                         |                    |

| 1Ch                  | CCPR2H  | Capture/C                            | ompare/PWI            | M Register 2  | (MSB)           | 1               | 1             | 1             | I                | xxxx xxxx               | 58, 96             |

| 1Dh                  | CCP2CON | —                                    | _                     | CCP2X         | CCP2Y           | CCP2M3          | CCP2M2        | CCP2M1        | CCP2M0           | 00 0000                 | 54, 96             |

| 1Eh                  | ADRES   | A/D Resul                            | t Register By         | /te           | T               | 1               | 1             |               | 1                | xxxx xxxx               | 88, 96             |

| 1Fh                  | ADCON0  | ADCS1                                | ADCS0                 | CHS2          | CHS1            | CHS0            | GO/<br>DONE   | —             | ADON             | 0000 00-0               | 83, 96             |

TABLE 2-1:SPECIAL FUNCTION REGISTER SUMMARY

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

**6:** This bit always reads as a '1'.

| Address              | Name       | Bit 7                        | Bit 6                                       | Bit 5                     | Bit 4          | Bit 3        | Bit 2         | Bit 1         | Bit 0            | Value on<br>POR,<br>BOR | Details<br>on page |

|----------------------|------------|------------------------------|---------------------------------------------|---------------------------|----------------|--------------|---------------|---------------|------------------|-------------------------|--------------------|

| Bank 1               |            |                              |                                             |                           |                |              |               |               |                  |                         |                    |

| 80h <sup>(4)</sup>   | INDF       | Addressin                    | g this locatio                              | n uses conte              | ents of FSR to | address dat  | a memory (r   | not a physica | al register)     | 0000 0000               | 27, 96             |

| 81h                  | OPTION_REG | RBPU                         | INTEDG                                      | TOCS                      | T0SE           | PSA          | PS2           | PS1           | PS0              | 1111 1111               | 20, 44, 96         |

| 82h <sup>(4)</sup>   | PCL        | Program C                    | Program Counter (PC) Least Significant Byte |                           |                |              |               |               |                  | 0000 0000               | 26, 96             |

| 83h <sup>(4)</sup>   | STATUS     | IRP                          | RP1                                         | RP0                       | TO             | PD           | Z             | DC            | C <sup>(2)</sup> | 0001 1xxx               | 19, 96             |

| 84h <sup>(4)</sup>   | FSR        | Indirect da                  | ata memory a                                | ddress poin               | ter            |              |               |               |                  | xxxx xxxx               | 27, 96             |

| 85h                  | TRISA      |                              | _                                           | PORTA Dat                 | a Direction Re | egister      |               |               |                  | 11 1111                 | 32, 96             |

| 86h                  | TRISB      | PORTB D                      | ata Direction                               |                           |                | •            |               |               |                  | 1111 1111               | 34, 96             |

| 87h                  | TRISC      | PORTC D                      | ata Direction                               | Register                  |                |              |               |               |                  | 1111 1111               | 35, 96             |

| 88h <b>(5)</b>       | TRISD      | PORTD D                      | ata Direction                               | Register                  |                |              |               |               |                  | 1111 1111               | 36, 96             |

| 89h <b>(5)</b>       | TRISE      | IBF                          | OBF                                         | IBOV                      | PSPMODE        | —            | PORTE Da      | ata Direction | Bits             | 0000 -111               | 38, 96             |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                            | —                                           | —                         | Write Buffer f | or the upper | 5 bits of the | Program C     | ounter           | 0 0000                  | 26, 96             |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                          | PEIE                                        | TMR0IE                    | INTE           | RBIE         | TMR0IF        | INTF          | RBIF             | 0000 000x               | 21, 96             |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup>         | ADIE                                        | RCIE                      | TXIE           | SSPIE        | CCP1IE        | TMR2IE        | TMR1IE           | 0000 0000               | 22, 97             |

| 8Dh                  | PIE2       | _                            | —                                           | —                         | _              |              | _             | —             | CCP2IE           | 0                       | 24, 97             |

| 8Eh                  | PCON       | _                            | _                                           | _                         | _              | _            | _             | POR           | BOR              | dd                      | 22, 97             |

| 8Fh                  | _          | Unimplem                     | ented                                       |                           |                |              |               |               |                  | _                       | _                  |

| 90h                  | _          | Unimplem                     | ented                                       |                           |                |              |               |               |                  | _                       | _                  |

| 91h                  | —          | Unimplem                     | ented                                       |                           |                |              |               |               |                  | _                       | _                  |

| 92h                  | PR2        | Timer2 Mo                    | Timer2 Module Period Register               |                           |                |              |               |               | 1111 1111        | 52, 97                  |                    |

| 93h                  | SSPADD     | Synchrono                    | ous Serial Po                               | ort (l <sup>2</sup> C™ mo | de) Address F  | Register     |               |               |                  | 0000 0000               | 68, 97             |

| 94h                  | SSPSTAT    | SMP                          | CKE                                         | D/A                       | Р              | S            | R/W           | UA            | BF               | 0000 0000               | 60, 97             |

| 95h                  | —          | Unimplem                     | ented                                       |                           |                |              |               |               |                  | _                       | —                  |

| 96h                  | —          | Unimplem                     | Unimplemented                               |                           |                |              |               | _             | _                |                         |                    |

| 97h                  | —          | Unimplemented                |                                             |                           |                | _            | _             |               |                  |                         |                    |

| 98h                  | TXSTA      | CSRC                         | TX9                                         | TXEN                      | SYNC           |              | BRGH          | TRMT          | TX9D             | 0000 -010               | 69, 97             |

| 99h                  | SPBRG      | Baud Rate Generator Register |                                             |                           |                |              | 0000 0000     | 71, 97        |                  |                         |                    |

| 9Ah                  | —          | Unimplemented                |                                             |                           |                |              | _             |               |                  |                         |                    |

| 9Bh                  | _          | Unimplemented                |                                             |                           |                |              | _             |               |                  |                         |                    |

| 9Ch                  | —          | Unimplemented                |                                             |                           |                |              |               | _             |                  |                         |                    |

| 9Dh                  | —          | Unimplem                     | ented                                       |                           |                |              |               |               |                  | _                       |                    |

| 9Eh                  | _          | Unimplem                     | ented                                       |                           |                |              |               |               |                  | _                       |                    |

| 9Fh                  | ADCON1     | _                            | _                                           | _                         | _              | _            | PCFG2         | PCFG1         | PCFG0            | 000                     | 84, 97             |

| TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (C | CONTINUED) |

|-------------------------------------------------|------------|

|-------------------------------------------------|------------|

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter during branches (CALL or GOTO).

2: Other (non Power-up) Resets include external Reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices; always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD, PORTE, TRISD and TRISE are not physically implemented on the 28-pin devices, read as '0'.

6: This bit always reads as a '1'.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## REGISTER 2-2: OPTION\_REG: (ADDRESS 81h, 181h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | RBPU: PORTB Pull-up Enable bit                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 1 = PORTB pull-ups are disabled                                                                                       |

|         | 0 = PORTB pull-ups are enabled by individual PORT latch values                                                        |

| bit 6   | INTEDG: Interrupt Edge Select bit                                                                                     |

|         | <ul> <li>1 = Interrupt on rising edge of RB0/INT pin</li> <li>0 = Interrupt on falling edge of RB0/INT pin</li> </ul> |

| bit 5   | TOCS: TMR0 Clock Source Select bit                                                                                    |

|         | 1 = Transition on RA4/T0CKI pin                                                                                       |

|         | 0 = Internal instruction cycle clock (CLKOUT)                                                                         |

| bit 4   | T0SE: TMR0 Source Edge Select bit                                                                                     |

|         | 1 = Increment on high-to-low transition on RA4/T0CKI pin                                                              |

|         | 0 = Increment on low-to-high transition on RA4/T0CKI pin                                                              |

| bit 3   | PSA: Prescaler Assignment bit                                                                                         |

|         | 1 = Prescaler is assigned to the WDT                                                                                  |

|         | 0 = Prescaler is assigned to the Timer0 module                                                                        |

| bit 2-0 | PS2:PS0: Prescaler Rate Select bits                                                                                   |

|         | Bit Value TMR0 Rate WDT Rate                                                                                          |

|         |                                                                                                                       |

| 000 | 1:2     | 1:1     |

|-----|---------|---------|

| 001 | 1:4     | 1:2     |

| 010 | 1:8     | 1:4     |

| 011 | 1:16    | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1 : 128 | 1:64    |

| 111 | 1 : 256 | 1 : 128 |

#### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt.

### REGISTER 2-6: PIE2: (ADDRESS 8Dh)

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| —       | —   | —   | _   | —   | —   | —   | CCP2IE |

| bit 7   |     |     |     |     |     |     | bit 0  |

|         |     |     |     |     |     |     |        |

| Legend: |     |     |     |     |     |     |        |

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as 'O'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-1 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt.

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>). User soft-       |

|       | ware should ensure the appropriate inter-     |

|       | rupt flag bits are clear prior to enabling an |

|       | interrupt.                                    |

#### REGISTER 2-7: PIR2: (ADDRESS 0Dh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

|       |     |     |     |     |     |     | CCP2IF |

| bit 7 |     |     |     |     |     |     | bit 0  |

Ν

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-1 Unimplemented: Read as '0'

| bit 0 | CCP2IF: CCP2 Interrupt Flag bit                                          |  |  |  |  |

|-------|--------------------------------------------------------------------------|--|--|--|--|

|       | Capture mode:                                                            |  |  |  |  |

|       | 1 = A TMR1 register capture occurred (must be cleared in software)       |  |  |  |  |

|       | 0 = No TMR1 register capture occurred                                    |  |  |  |  |

|       | Compare mode:                                                            |  |  |  |  |

|       | 1 = A TMR1 register compare match occurred (must be cleared in software) |  |  |  |  |

|       | 0 = No TMR1 register compare match occurred                              |  |  |  |  |

|       | PWM mode:                                                                |  |  |  |  |

|       | Unused                                                                   |  |  |  |  |

#### TABLE 4-1:PORTA FUNCTIONS

| Name         | Bit#  | Buffer | Function                                                                        |

|--------------|-------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit 0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit 1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit 2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit 3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit 4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/AN4/SS   | bit 5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on<br>POR,<br>BOR | Value on all<br>other<br>Resets |

|---------|--------|-------|-------|-------------------------------|-------|-------|-------|-------|---------|-------------------------|---------------------------------|

| 05h     | PORTA  | _     | _     | RA5                           | RA4   | RA3   | RA2   | RA1   | RA0     | 0x 0000                 | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA Data Direction Register |       |       |       |       | 11 1111 | 11 1111                 |                                 |

| 9Fh     | ADCON1 |       | —     |                               | —     |       | PCFG2 | PCFG1 | PCFG0   | 000                     | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note:** When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes where PCFG2:PCFG0 = 100, 101, 11x.

#### 9.3.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode Idle (SSPM3:SSPM0 = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 9.3.3 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions, allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

|                        | ABLE 3-3. REGISTERS ASSOCIATED WITH COPERATION |                      |                                                                   |        |       |       |        |        |        |                         |                                 |

|------------------------|------------------------------------------------|----------------------|-------------------------------------------------------------------|--------|-------|-------|--------|--------|--------|-------------------------|---------------------------------|

| Address                | Name                                           | Bit 7                | Bit 6                                                             | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                         | GIE                  | PEIE                                                              | TMR0IE | INTE  | RBIE  | TMR0IF | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch                    | PIR1                                           | PSPIF <sup>(1)</sup> | ADIF                                                              | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                       |

| 8Ch                    | PIE1                                           | PSPIE <sup>(1)</sup> | ADIE                                                              | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                       |

| 13h                    | SSPBUF                                         | Synchrono            | Synchronous Serial Port Receive Buffer/Transmit Register xxxx x   |        |       |       |        |        |        | xxxx xxxx               | uuuu uuuu                       |

| 93h                    | SSPADD                                         | Synchrono            | Synchronous Serial Port (I <sup>2</sup> C™ mode) Address Register |        |       |       |        |        |        | 0000 0000               | 0000 0000                       |

| 14h                    | SSPCON                                         | WCOL                 | SSPOV                                                             | SSPEN  | CKP   | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                       |

| 94h                    | SSPSTAT                                        | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup>                                                | D/A    | Р     | S     | R/W    | UA     | BF     | 0000 0000               | 0000 0000                       |

| 87h                    | TRISC                                          | PORTC Da             | PORTC Data Direction Register                                     |        |       |       |        |        | •      | 1111 1111               | 1111 1111                       |

TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:**  $x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in <math>l^2C^{TM}$  mode.

Note 1: PSPIF and PSPIE are reserved on the PIC16CR73/76; always maintain these bits clear.

**2:** Maintain these bits clear in I<sup>2</sup>C mode.

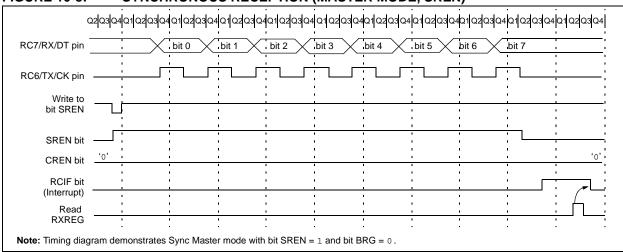

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a twodeep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG, in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- 7. Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE in the INTCON register are set.

## FIGURE 10-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## 12.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

These devices have a Watchdog Timer, which can be enabled or disabled, using a Configuration bit. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes, and is enabled or disabled, using a Configuration bit. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. Configuration bits are used to select the desired oscillator mode.

Additional information on special features is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

## **12.1** Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

## 12.4 MCLR

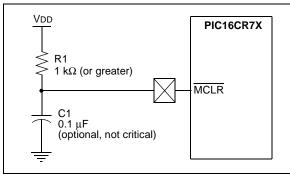

PIC16CR7X devices have a noise filter in the  $\overline{\text{MCLR}}$ Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the  $\overline{\text{MCLR}}$  pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both  $\overline{\text{MCLR}}$  Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the  $\overline{\text{MCLR}}$ pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-5, is suggested.

FIGURE 12-5: RECOMMENDED MCLR CIRCUIT

## 12.5 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V-1.7V). To take advantage of the POR, tie the  $\overline{\text{MCLR}}$  pin to VDD as described in **Section 12.4 "MCLR**". A maximum rise time for VDD is specified. See the Electrical Specifications for details.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*" (DS00607).

## 12.6 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A Configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip, due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.7 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from Sleep.

## 12.8 Brown-out Reset (BOR)

The Configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a Reset may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in Reset for TPWRT (parameter #33, about 72 mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR, with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT Configuration bit.

## 12.9 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR Reset occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16CR7X device operating in parallel.

Table 12-5 shows the Reset conditions for the STATUS, PCON and PC registers, while Table 12-6 shows the Reset conditions for all the registers.

NOTES:

## 14.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 14.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and the dsPIC30, dsPIC33 and PIC24 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 14.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- Support for fixed-point and floating-point data

- Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## 14.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 15.3 Timing Parameter Symbology

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2p              | pS                                    | 3. Tcc:st | (I <sup>2</sup> C <sup>™</sup> specifications only) |

|------------------------|---------------------------------------|-----------|-----------------------------------------------------|

| 2. TppS                |                                       | 4. Ts     | (I <sup>2</sup> C <sup>™</sup> specifications only) |

| Т                      |                                       |           | · · · · ·                                           |

| F                      | Frequency                             | Т         | Time                                                |

| Lowerca                | se letters (pp) and their meanings:   |           |                                                     |

| рр                     |                                       |           |                                                     |

| сс                     | CCP1                                  | OSC       | OSC1                                                |

| ck                     | CLKOUT                                | rd        | RD                                                  |

| CS                     | CS                                    | rw        | RD or WR                                            |

| di                     | SDI                                   | SC        | SCK                                                 |

| do                     | SDO                                   | SS        | SS                                                  |

| dt                     | Data in                               | tO        | ТОСКІ                                               |

| io                     | I/O port                              | t1        | T1CKI                                               |

| mc                     | MCLR                                  | wr        | WR                                                  |

|                        | se letters and their meanings:        |           |                                                     |

| S                      |                                       |           |                                                     |

| F                      | Fall                                  | Р         | Period                                              |

| Н                      | High                                  | R         | Rise                                                |

| I                      | Invalid (High-impendance)             | V         | Valid                                               |

| L                      | Low                                   | Z         | High-impendance                                     |

| I <sup>2</sup> C™ only | ,                                     |           |                                                     |

| AA                     | output access                         | High      | High                                                |

| BUF                    | Bus free                              | Low       | Low                                                 |

| Tcc:st (               | I <sup>2</sup> C specifications only) |           |                                                     |

| CC                     |                                       |           |                                                     |

| HD                     | Hold                                  | SU        | Setup                                               |

| ST                     |                                       |           |                                                     |

| DAT                    | DATA input hold                       | STO       | Stop condition                                      |

| STA                    | Start condition                       |           |                                                     |

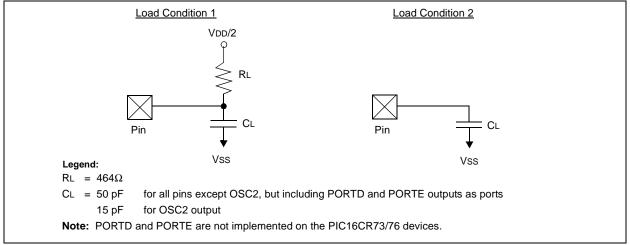

### FIGURE 15-2: LOAD CONDITIONS

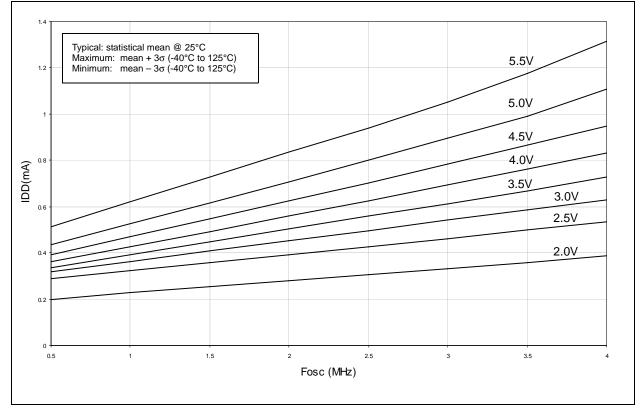

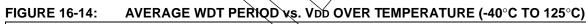

FIGURE 16-13: TYPICAL, MINIMUM AND MAXIMUM WDT PERIOD vs. Vdd (-40°C TO 125°C)

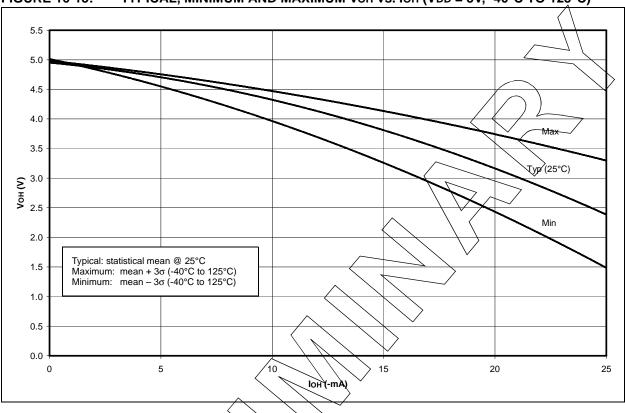

FIGURE 16-16: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 3V, -40°C TO 125°C)

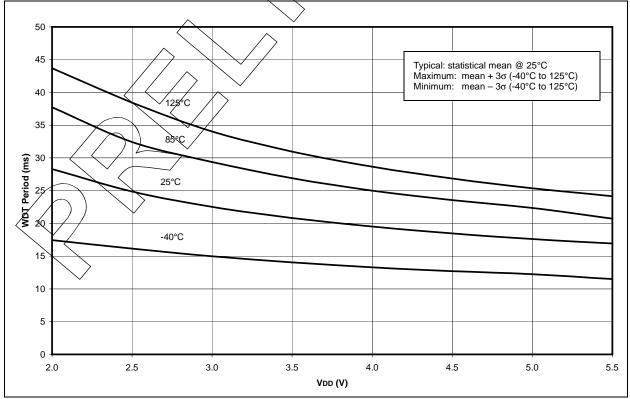

FIGURE 16-15: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD = 5V, -40°C TO 125°C)

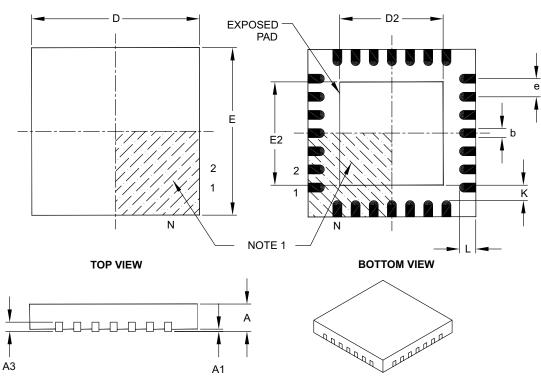

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          | MILLIMETERS | 6    |  |

|------------------------|------------------|----------|-------------|------|--|

| C                      | Dimension Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | N                |          | 28          |      |  |

| Pitch                  | е                |          | 0.65 BSC    |      |  |

| Overall Height         | А                | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF |             |      |  |

| Overall Width          | E                |          | 6.00 BSC    |      |  |

| Exposed Pad Width      | E2               | 3.65     | 3.70        | 4.20 |  |

| Overall Length         | D                |          | 6.00 BSC    |      |  |

| Exposed Pad Length     | D2               | 3.65     | 3.70        | 4.20 |  |

| Contact Width          | b                | 0.23     | 0.30        | 0.35 |  |

| Contact Length         | L                | 0.50     | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad | К                | 0.20     | -           | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:  | Technical Publications Manager          | Total Pages Sent                                       |

|------|-----------------------------------------|--------------------------------------------------------|

| RE:  | Reader Response                         |                                                        |

| Fror | n: Name                                 |                                                        |

|      | Company                                 |                                                        |

|      | Address                                 |                                                        |

|      |                                         |                                                        |

|      | Telephone: ()                           | FAX: ()                                                |

| Арр  | lication (optional):                    |                                                        |

| Wou  | Ild you like a reply?YN                 |                                                        |

| Dev  | ice: PIC16CR7X                          | Literature Number: DS21993C                            |

| Que  | stions:                                 |                                                        |

| 1.   | What are the best features of this do   | cument?                                                |

|      |                                         |                                                        |

|      |                                         |                                                        |

| 2.   | How does this document meet your        | hardware and software development needs?               |

|      |                                         |                                                        |

|      |                                         |                                                        |

| 3.   | Do you find the organization of this of | locument easy to follow? If not, why?                  |

|      |                                         |                                                        |

|      |                                         |                                                        |

| 4.   | What additions to the document do y     | you think would enhance the structure and subject?     |

|      |                                         |                                                        |

| _    |                                         |                                                        |

| 5.   | What deletions from the document c      | ould be made without affecting the overall usefulness? |

|      |                                         |                                                        |

| 0    |                                         | a formation (what and what and )                       |

| 6.   | Is there any incorrect or misleading i  | nformation (what and where)?                           |

|      |                                         |                                                        |

| 7.   | How would you improve this docume       | ent?                                                   |

|      |                                         |                                                        |

|      |                                         |                                                        |

|      |                                         |                                                        |