Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 24-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 24-QFN (4x4)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny817-mfr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 10. CLKCTRL - Clock Controller

# 10.1 Features

- All clocks and clock sources are automatically enabled when requested by peripherals

- Internal oscillators:

- 16/20MHz oscillator (OSC20M)

- 32KHz Ultra Low Power oscillator (OSCULP32K)

- External clock options:

- 32.768kHz crystal oscillator (XOSC32K)

- External clock

- Main clock features:

- Safe run-time switching

- Prescaler with 1x to 64x division in 12 different settings

# 10.2 Overview

The Clock Controller peripheral (CLKCTRL) controls, distributes, and prescales the clock signals from the available oscillators. The CLKCTRL supports internal and external clock sources.

The CLKCTRL is based on an automatic clock request system, implemented in all peripherals on the device. The peripherals will automatically request the clocks needed. If multiple clock sources are available, the request is routed to the correct clock source.

The Main Clock (CLK\_MAIN) is used by the CPU, RAM, and the IO bus. The Main Clock source can be selected and prescaled. Some peripherals can share the same clock source as the Main Clock, or run asynchronously to the Main Clock domain.

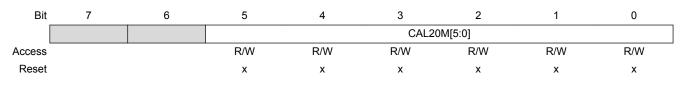

#### Bits 5:0 – CAL20M[5:0]: Calibration

These bits change the frequency around the current center frequency of the OSC20M for fine tuning.

At Reset factory calibrated values are loaded based on FREQSEL bits in FUSE.OSCCFG.

#### 10.5.7 16/20MHz Oscillator Calibration B

| Name:    | OSC20MCALIBB                      |

|----------|-----------------------------------|

| Offset:  | 0x12                              |

| Reset:   | Based on FUSE.OSCCFG              |

| Property | : Configuration Change Protection |

| Bit    | 7    | 6 | 5 | 4 | 3   | 2      | 1         | 0   |

|--------|------|---|---|---|-----|--------|-----------|-----|

|        | LOCK |   |   |   |     | TEMPCA | L20M[3:0] |     |

| Access | R    |   |   |   | R/W | R/W    | R/W       | R/W |

| Reset  | х    |   |   |   | x   | x      | x         | x   |

#### Bit 7 – LOCK: Oscillator Calibration Locked by Fuse

When this bit is set, the calibration settings in CLKCTRL.OSC20MCALIBA and CLKCTRL.OSC20MCALIBB cannot be changed. The Reset value is loaded from the OSCLOCK bit in the Oscillator Configuration fuse (FUSE.OSCCFG).

#### Bits 3:0 – TEMPCAL20M[3:0]: Oscillator Temperature Coefficient Calibration

These bits tune the slope of the temperature compensation.

At Reset factory calibrated values are loaded based on FREQSEL bits in FUSE.OSCCFG.

# 10.5.8 32KHz Oscillator Control A

Name:OSC32KCTRLAOffset:0x18Reset:0x00Property:Configuration Change Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1        | 0 |

|--------|---|---|---|---|---|---|----------|---|

|        |   |   |   |   |   |   | RUNSTDBY |   |

| Access | R | R | R | R | R | R | R/W      | R |

| Reset  | 0 | 0 | 0 | 0 | 0 | 0 | 0        | 0 |

# Bit 1 – RUNSTDBY: Run Standby

This bit force the oscillator on in all modes, even when unused by the system. In standby sleep mode this can be used to ensure immediate wake-up and not waiting for oscillator start-up time.

When not requested by peripherals, no oscillator output is provided.

# 12.4 Register Summary - RSTCTRL

| Offset | Name  | Bit Pos. |  |        |      |      |       |      |      |

|--------|-------|----------|--|--------|------|------|-------|------|------|

| 0x00   | RSTFR | 7:0      |  | UPDIRF | SWRF | WDRF | EXTRF | BORF | PORF |

| 0x01   | SWRR  | 7:0      |  |        |      |      |       |      | SWRE |

# 12.5 Register Description

# 12.5.1 Reset Flag Register

All flags are cleared by writing a '1' to them. They are also cleared by a Power-on Reset, with the exception of the Power-On Reset Flag (PORF).

Name: RSTFR Offset: 0x00 Reset: 0xXX Property: -

| Bit    | 7 | 6 | 5      | 4    | 3    | 2     | 1    | 0    |

|--------|---|---|--------|------|------|-------|------|------|

|        |   |   | UPDIRF | SWRF | WDRF | EXTRF | BORF | PORF |

| Access | R | R | R/W    | R/W  | R/W  | R/W   | R/W  | R/W  |

| Reset  | 0 | 0 | x      | х    | х    | x     | х    | х    |

# Bit 5 – UPDIRF: UPDI Reset Flag

This bit is set if a UPDI Reset occurs.

#### Bit 4 – SWRF: Software Reset Flag

This bit is set if a Software Reset occurs.

#### Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog Reset occurs.

# Bit 2 – EXTRF: External Reset Flag

This bit is set if an External reset occurs.

# Bit 1 – BORF: Brownout Reset Flag

This bit is set if a Brownout Reset occurs.

#### Bit 0 - PORF: Power-On Reset Flag

This bit is set if a Power-on Reset occurs.

This flag is only cleared by writing a '1' it.

After a POR, only the POR flag is set and all other flags are cleared. No other flag can be set before a full system boot is run after the POR.

#### 12.5.2 Software Reset Register

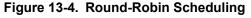

Round-robin scheduling for LVL0 interrupt requests is enabled by writing a '1' to the Round-Robin Priority Enable bit (LVL0RR) in the Control A register (CPUINT.CTRLA).

When round-robin scheduling is enabled, the interrupt vector address for the last acknowledged LVL0 interrupt will have the lowest priority the next time one or more LVL0 interrupts are requested, as illustrated in the figure below.

# **Compact Vector Table**

The Compact Vector Table (CVT) is a feature to allow for writing of compact code.

When CVT is enabled by writing a '1' to the CVT bit in the Control A register (CPUINT.CTRLA), the vector table contains these three interrupt vectors:

- 1. The non-maskable interrupts (NMI) at vector address 1

- 2. The priority level 1 (LVL1) interrupt at vector address 2

- 3. All priority level 0 (LVL0) interrupts share vector address 3.

This feature is most suitable for applications using a small number of interrupt generators.

#### 13.3.3 Events

Not applicable.

# 13.3.4 Sleep Mode Operation

Not applicable.

# 13.3.5 Configuration Change Protection

This peripheral has registers that are under Configuration Change Protection (CCP). In order to write to these, a certain key must be written to the CPU.CCP register first, followed by a write access to the protected bits within four CPU instructions.

It is possible to try writing to these registers any time, but the values are not altered.

The following registers are under CCP:

#### 16.5.2 Data Direction Set

|     | <b>me:</b> DI<br><b>set:</b> 0x | RSET<br>:01 |   |   |   |   |   |   |  |

|-----|---------------------------------|-------------|---|---|---|---|---|---|--|

| Re  | set: 0x                         | :00         |   |   |   |   |   |   |  |

| Pro | operty: -                       |             |   |   |   |   |   |   |  |

| Bit | 7                               | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

| [      | DIRSET[7:0] |     |     |     |     |     |     |     |  |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|--|

| Access | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

#### Bits 7:0 – DIRSET[7:0]: Data Direction Set

This bit field can be used instead of a read-modify-write to set individual pins as output. Writing a '1' to DIRSET[n] will set the corresponding PORT.DIR[n] bit.

Reading this bit field will always return the value of PORT.DIR.

#### 16.5.3 Data Direction Clear

| Name:            | DIRCLR |

|------------------|--------|

| Offset:          | 0x02   |

| Reset:           | 0x00   |

| <b>Property:</b> | -      |

| Bit    | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|--|

|        | DIRCLR[7:0] |     |     |     |     |     |     |     |  |

| Access | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

#### Bits 7:0 – DIRCLR[7:0]: Data Direction Clear

This register can be used instead of a read-modify-write to configure individual pins as input. Writing a '1' to DIRCLR[n] will clear the corresponding bit in PORT.DIR.

Reading this bit field will always return the value of PORT.DIR.

# 16.5.4 Data Direction Toggle

Name: DIRTGL Offset: 0x03 Reset: 0x00 Property: -

# 17. BOD - Brownout Detector

# 17.1 Features

- Brownout detection monitors the power supply to avoid operation below a programmable level

- Three modes:

- Enabled

- Sampled

- Disabled

- Separate selection of mode for Active mode and sleep modes

- Voltage level monitor (VLM) with interrupt

- Programmable VLM level relative to the BOD level

# 17.2 Overview

The Brownout Detector (BOD) monitors the power supply and compares the voltage with two programmable brownout threshold levels: the brownout threshold level defines when to generate a Reset. A voltage level monitor (VLM) monitors the power supply and compares it to a threshold higher than the BOD threshold. The VLM can then generate an interrupt request as an "early warning" when the supply voltage is about to drop below the VLM threshold. The VLM threshold level is expressed in percentage above the BOD threshold level.

The BOD is mainly controlled by fuses. The mode used in Standby sleep mode and Power Down sleep mode can be altered in normal program execution. The VLM part of the BOD is controlled by I/O registers as well.

When activated, The BOD can operate in Enabled mode, where the BOD is continuously active, and in Sampled mode, where the BOD is activated briefly at a given period to check the supply voltage level.

#### 17.2.2.3 Interrupts

Using the interrupts of this peripheral requires the Interrupt Controller to be configured first.

#### **Related Links**

CPUINT - CPU Interrupt Controller SREG Interrupts

#### 17.2.2.4 Events

Not applicable.

#### 17.2.2.5 Debug Operation

This peripheral is unaffected by entering debug mode.

The VLM interrupt will not be executed if the CPU is halted in debug mode.

If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during halted debugging.

# 17.3 Functional Description

#### 17.3.1 Initialization

The BOD settings are loaded from fuses during reset. The BOD level and operating mode in Active and Idle sleep mode are set by fuses and cannot be changed by the CPU. The operating mode in Standby and Power Down sleep mode is loaded from fuses and can be changed by software.

The Voltage Level Monitor function can be enabled by writing a '1' to the VLM Interrupt Enable bit (VLMIE) in the Interrupt Control register (BOD.INTCTRL). The VLM interrupt is configured by writing the VLM Configuration bits (VLMCFG) in BOD.INTCTRL. An interrupt is requested when the supply voltage crosses the VLM threshold either from above, from below, or from any direction.

The VLM functionality will follow the BOD mode. If the BOD is turned off, the VLM will not be enabled, even if the VLMIE is '1'. If the BOD is using sampled mode, the VLM will also be sampled. When enabling VLM interrupt, the interrupt flag will always be set if VLMCFG equals 0x2 and may be set if VLMCFG is configured to 0x0 or 0x1.

The VLM threshold is defined by writing the VLM Level bits (VLMLVL) in the Control A register (BOD.VLMCTRLA).

If the BOD/VLM is enabled in sampled mode, only VLMCFG=0x1 (crossing threshold from above) in BOD.INTCTRL will trigger an interrupt.

# 17.3.2 Interrupts

#### Table 17-2. Available Interrupt Vectors and Sources

| Offset | Name | Vector Description    | Conditions                                                                       |

|--------|------|-----------------------|----------------------------------------------------------------------------------|

| 0x00   | VLM  | Voltage Level Monitor | Supply voltage crossing the VLM threshold as configured by VLMCFG in BOD.INTCTRL |

When an interrupt condition occurs, the corresponding Interrupt Flag is set in the Interrupt Flags register of the peripheral (*peripheral*.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

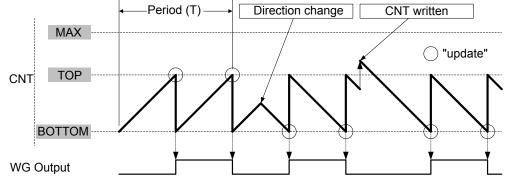

Figure 20-9. Frequency Waveform Generation

The waveform frequency ( $f_{FRQ}$ ) is defined by the following equation:

$$f_{\rm FRQ} = \frac{f_{\rm CLK\_PER}}{2N(\rm CMPn+1)}$$

where *N* represents the prescaler divider used (CLKSEL in TCA.CTRLA), and  $f_{CLK_PER}$  is the system clock for the peripherals.

The maximum frequency of the waveform generated is half of the peripheral clock frequency ( $f_{CLK\_PER}/2$ ) when TCA.CMPn is written to zero (0x0000) and no prescaling is used (N=1, CLKSEL=0x0 in TCA.CTRLA).

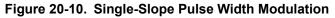

# Single-Slope PWM Generation

For single-slope Pulse Width Modulation (PWM) generation, the period (T) is controlled by TCA.PER, while the values of TCA.CMPn control the duty cycle of the WG output. The figure below shows how the counter counts from BOTTOM to TOP and then restarts from BOTTOM. The waveform generator (WO) output is set at TOP, and cleared on the compare match between the TCA.CNT and TCA.CMPn registers.

The TCA.PER register defines the PWM resolution. The minimum resolution is 2 bits (TCA.PER=0x0003), and the maximum resolution is 16 bits (TCA.PER=MAX).

The following equation calculates the exact resolution for single-slope PWM (R<sub>PWM\_SS</sub>):

$$R_{\rm PWM\_SS} = \frac{\log(\rm PER+1)}{\log(2)}$$

The single-slope PWM frequency ( $f_{PWM_SS}$ ) depends on the period setting (TCA\_PER), the system's peripheral clock frequency  $f_{CLK_PER}$ , the TCA prescaler (CLKSEL in TCA.CTRLA). It is calculated by the following equation:

$$f_{\text{PWM}\_\text{SS}} = \frac{f_{\text{CLK}\_\text{PER}}}{N(\text{PER}+1)}$$

© 2017 Microchip Technology Inc.

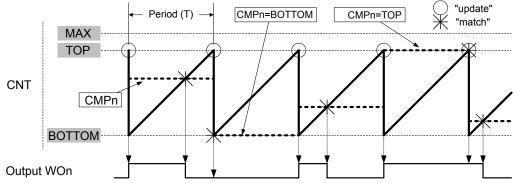

Name: INTFLAGS Offset: 0x0B Reset: 0x00 Property: -

# Bit 6 – LCMP2: Low-byte Compare Channel 0 Interrupt Flag

See LCMP0 flag description.

# Bit 5 – LCMP1: Low-byte Compare Channel 0 Interrupt Flag

See LCMP0 flag description.

# Bit 4 – LCMP0: Low-byte Compare Channel 0 Interrupt Flag

The compare interrupt flag (LCMPn) is set on a compare match on the corresponding compare channel.

For all modes of operation, the LCMPn flag will be set when a compare match occurs between the Lowbyte count register (LCNT) and the corresponding compare register (LCMPn). The LCMPn flag will not be cleared automatically and has to be cleared by software. This is done by writing a '1' to its bit location.

# Bit 1 – HUNF: High-byte Underflow Interrupt Flag

This flag is set on a high-byte timer BOTTOM (underflow) condition. HUNF is not automatically cleared and needs to be cleared by software. This is done by writing a '1' to its bit location.

# Bit 0 – LUNF: Low-byte Underflow Interrupt Flag

This flag is set on a low-byte timer BOTTOM (underflow) condition. LUNF is not automatically cleared and needs to be cleared by software. This is done by writing a '1' to its bit location.

# 20.7.9 Debug Control Register

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

# Bit 0 – DBGRUN: Run in Debug

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | The peripheral is halted in break debug mode and ignores events.                |

| 1     | The peripheral will continue to run in break debug mode when the CPU is halted. |

# 21. TCB - 16-bit Timer/Counter Type B

# 21.1 Features

- 16-bit counter operation modes:

- Periodic interrupt

- Timeout check

- Input capture

- On event

- Frequency measurement

- Pulse width measurement

- Frequency and pulse width measurement

- Single shot

- 8-bit Pulse Width Modulation (PWM)

- Noise canceler on event input

- Optional: Operation synchronous with TCA0

# 21.2 Overview

The capabilities of the 16-bit Timer/Counter type B (TCB) include frequency and waveform generation, and input capture on Event with time and frequency measurement of digital signals. The TCB consists of a base counter and control logic which can be set in one of eight different modes, each mode providing unique functionality. The base counter is clocked by the peripheral clock with optional prescaling.

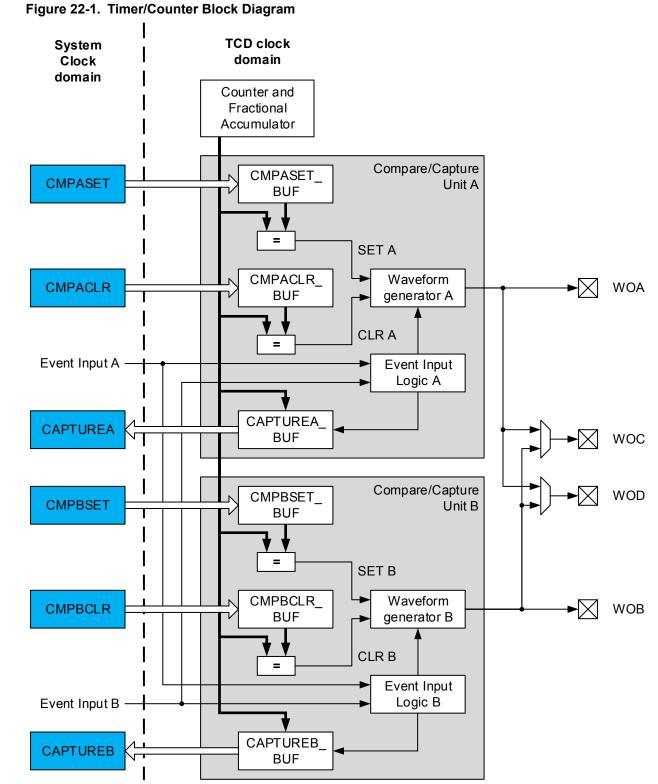

The TCD core is asynchronous to the system clock. The timer/counter consist of two compare/capture units, each with a separate waveform output. In addition there are two extra waveform outputs which can be equal to the output from one of the units. The compare registers CMPxSET, CMPxCLR are stored in

22.2.1

**Block Diagram**

# Bit 0 – ENABLE: Enable

When this bit is written to, it will automatically be synchronized to the TCD clock domain.

This bit can be changed as long as synchronization of this bit is not ongoing, see Enable Ready bit (ENRDY) in Status register (STATUS).

This bit is not enable-protected.

| Value | Description                     |

|-------|---------------------------------|

| 0     | The TCD is disabled.            |

| 1     | The TCD is enabled and running. |

#### 22.5.2 Control B

Name:

CTRLB

Offset:

0x01

Reset:

0x00

Property:

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0       |

|--------|---|---|---|---|---|---|------|---------|

|        |   |   |   |   |   |   | WGMC | DE[1:0] |

| Access |   |   |   |   |   |   | R/W  | R/W     |

| Reset  |   |   |   |   |   |   | 0    | 0       |

|        |   |   |   |   |   |   |      |         |

#### Bits 1:0 – WGMODE[1:0]: Waveform Generation Mode

These bits select the waveform generation

| Value | Name     | Description     |

|-------|----------|-----------------|

| 0x0   | ONERAMP  | One ramp mode   |

| 0x1   | TWORAMP  | Two ramp mode   |

| 0x2   | FOURRAMP | Four ramp mode  |

| 0x3   | DS       | Dual-slope mode |

# 22.5.3 Control C

| Name:            | CTRLC |

|------------------|-------|

| Offset:          | 0x02  |

| Reset:           | 0x00  |

| <b>Property:</b> | -     |

| Bit    | 7       | 6       | 5 | 4 | 3     | 2                                     | 1       | 0      |

|--------|---------|---------|---|---|-------|---------------------------------------|---------|--------|

|        | CMPDSEL | CMPCSEL |   |   | FIFTY |                                       | AUPDATE | CMPOVR |

| Access | R/W     | R/W     |   |   | R/W   | · · · · · · · · · · · · · · · · · · · | R/W     | R/W    |

| Reset  | 0       | 0       |   |   | 0     |                                       | 0       | 0      |

# Bit 7 – CMPDSEL: Compare D Output Select

| Value | Name | Description |

|-------|------|-------------|

| 0     | PWMA | Waveform A  |

| 1     | PWMB | Waveform B  |

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

An interrupt request is generated when the corresponding interrupt source is enabled and the Interrupt Flag is set. The interrupt request remains active until the Interrupt Flag is cleared. See the peripheral's INTFLAGS register for details on how to clear Interrupt Flags.

# **Related Links**

CPUINT - CPU Interrupt Controller INTCTRL PITINTCTRL

# 23.7 Sleep Mode Operation

The RTC will continue to operate in Idle sleep mode. It will run in Standby sleep mode if RTC.CTRLA.RUNSTDBY is set.

The PIT will continue to operate in any sleep mode.

# **Related Links**

CTRLA

# 23.8 Synchronization

Both the RTC and the PIT are asynchronous, operating from a different clock source (CLK\_RTC) independently of the main clock (CLK\_PER). For control and count register updates, it will take a number of RTC clock and/or peripheral clock cycles before an updated register value is available in a register or until a configuration change has effect on the RTC or PIT, respectively. This synchronization time is described for each register in the Register Description.

For some RTC registers, a Synchronization Busy flag is available (CMPBUSY, PERBUSY, CNTBUSY, CTRLABUSY) in the Status register (RTC.STATUS).

For the RTC.PITCTRLA register, a Synchronization Busy flag (SYNCBUSY) is available in the PIT Status register (RTC.PITSTATUS).

Check for busy should be performed before writing to the mentioned registers.

# **Related Links**

CLKCTRL - Clock Controller

# 23.9 Configuration Change Protection

Not applicable.

| Signal | Туре         | Description                     |

|--------|--------------|---------------------------------|

| XCK    | Input/output | Clock for synchronous operation |

| XDIR   | Output       | Transmit Enable for RS485       |

#### **Related Links**

I/O Multiplexing and Considerations

# 24.2.2 System Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### Table 24-1. USART System Dependencies

| Dependency                | Applicable | Peripheral |

|---------------------------|------------|------------|

| Clocks                    | Yes        | CLKCTRL    |

| I/O Lines and Connections | Yes        | PORT       |

| Interrupts                | Yes        | CPUINT     |

| Events                    | Yes        | EVSYS      |

| Debug                     | Yes        | UPDI       |

# **Related Links**

| Debug Operation           |

|---------------------------|

| Clocks                    |

| I/O Lines and Connections |

| Interrupts                |

| Events                    |

#### 24.2.2.1 Clocks

This peripheral depends on the peripheral clock.

# Related Links CLKCTRL - Clock Controller

#### 24.2.2.2 I/O Lines and Connections

Using the I/O lines of the peripheral requires configuration of the I/O pins.

#### **Related Links**

PORT - I/O Pin Configuration I/O Multiplexing and Considerations

#### 24.2.2.3 Interrupts

Using the interrupts of this peripheral requires the Interrupt Controller to be configured first.

#### **Related Links**

CPUINT - CPU Interrupt Controller SREG Interrupts

#### 24.2.2.4 Events

The events of this peripheral are connected to the Event System.

- 3. Each slave MCU determines if it has been selected.

- 4. The addressed MCU will disable MPCM and receive all data frames. The other slave MCUs will ignore the data frames.

- 5. When the addressed MCU has received the last data frame, it must enable MPCM again and wait for a new address frame from the master.

The process then repeats from step 2.

Using any of the 5- to 8-bit character frame formats is impractical, as the receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult, since the transmitter and receiver must use the same character size setting.

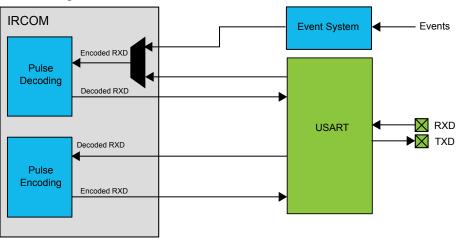

#### 24.3.2.11 IRCOM Mode of Operation

The IRCOM mode enables IrDA 1.4 compliant modulation and demodulation for baud rates up to 115.2kbps. When IRCOM mode is enabled, double speed mode cannot be used for the USART.

#### Overview

The device contains one infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2kbps.

The IRCOM is automatically enabled when the USART is set in IRCOM mode (by writing 0x2 to CTRLC.CMODE). The signals between the USART and the RX/TX pins are then routed through the module. The data on the TX/RX pins are the inverted value of the transmitted/received infrared pulse. It is also possible to select an event channel from the event system as input for the IRCOM receiver. This will disable the RX input from the USART pin.

For transmission, three pulse modulation schemes are available:

- 3/16 of the baud rate period

- Fixed programmable pulse time based on the peripheral clock frequency

- Pulse modulation disabled

For reception, a fixed programmable minimum high-level pulse width for the pulse to be decoded as a logical '0' is used. Shorter pulses will then be discarded, and the bit will be decoded to logical '1' as if no pulse was received.

# Block Diagram Figure 24-13. Block Diagram

When an interrupt condition occurs, the corresponding Interrupt Flag is set in the Interrupt Flags register of the peripheral (*peripheral*.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

An interrupt request is generated when the corresponding interrupt source is enabled and the Interrupt Flag is set. The interrupt request remains active until the Interrupt Flag is cleared. See the peripheral's INTFLAGS register for details on how to clear Interrupt Flags.

#### **Related Links**

SREG

**CPUINT - CPU Interrupt Controller**

#### 25.3.4 Sleep Mode Operation

The SPI will continue working in Idle sleep mode. When entering any deeper sleep mode, an active transaction will be stopped.

# **Related Links**

SLPCTRL - Sleep Controller

# 25.3.5 Configuration Change Protection

Not applicable.

| Bit    | 7    | 6    | 5 | 4    | 3     | 2       | 1    | 0      |

|--------|------|------|---|------|-------|---------|------|--------|

|        | RIEN | WIEN |   | QCEN | TIMEO | UT[1:0] | SMEN | ENABLE |

| Access | R/W  | R/W  |   | R/W  | R/W   | R/W     | R/W  | R/W    |

| Reset  | 0    | 0    |   | 0    | 0     | 0       | 0    | 0      |

# Bit 7 – RIEN: Read Interrupt Enable

Writing this bit to '1' enables interrupt on the Master Read Interrupt Flag (RIF) in the Master Status register (TWI.MSTATUS). A TWI Master read interrupt would be generated only if this bit, the RIF, and the Global Interrupt Flag (I) in CPU.SREG are all '1'.

# Bit 6 – WIEN: Write Interrupt Enable

Writing this bit to '1' enables interrupt on the Master Write Interrupt Flag (WIF) in the Master Status register (TWI.MSTATUS). A TWI Master write interrupt will be generated only if this bit, the WIF, and the Global Interrupt Flag (I) in CPU.SREG are all '1'.

# Bit 4 – QCEN: Quick Command Enable

Writing this bit to '1' enables Quick Command. When Quick Command is enabled, the corresponding interrupt flag is set immediately after the slave acknowledges the address. At this point the software can either issue a Stop command or a repeated Start by writing either the Command bits (CMD) in the Master Control B register (TWI.MCTRLB) or the Master Address register (TWI.MADDR).

# Bits 3:2 – TIMEOUT[1:0]: Inactive Bus Timeout

| Value | Name     | Description                                 |

|-------|----------|---------------------------------------------|

| 0x0   | DISABLED | Bus timeout disabled. I <sup>2</sup> C.     |

| 0x1   | 50US     | 50µs - SMBus (assume baud is set to 100kHz) |

| 0x2   | 100US    | 100µs (assume baud is set to 100kHz)        |

| 0x3   | 200US    | 200µs (assume baud is set to 100kHz)        |

# Bit 1 – SMEN: Smart Mode Enable

Writing this bit to '1' enables the Master smart mode. When smart mode is enabled, the acknowledge action is sent immediately after reading the Master Data (TWI.MDATA) register.

# Bit 0 – ENABLE: Enable TWI Master

Writing this bit to '1' enables the TWI as Master.

# 26.5.4 Master Control B

| Name:     | MCTRLB |

|-----------|--------|

| Offset:   | 0x04   |

| Reset:    | 0x00   |

| Property: | -      |

| Bit    | 7 | 6 | 5 | 4 | 3     | 2      | 1   | 0      |

|--------|---|---|---|---|-------|--------|-----|--------|

|        |   |   |   |   | FLUSH | ACKACT | CME | D[1:0] |

| Access |   |   |   |   | R/W   | R/W    | R/W | R/W    |

| Reset  |   |   |   |   | 0     | 0      | 0   | 0      |

# Bit 3 – FLUSH: Flush

Writing a '1' to this bit generates a strobe for one clock cycle disabling and then enabling the master.

| Name:     | SCTRLB |

|-----------|--------|

| Offset:   | 0x0A   |

| Reset:    | 0x00   |

| Property: | -      |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2      | 1   | 0      |

|--------|---|---|---|---|---|--------|-----|--------|

|        |   |   |   |   |   | ACKACT | CME | D[1:0] |

| Access |   |   |   |   |   | R/W    | R/W | R/W    |

| Reset  |   |   |   |   |   | 0      | 0   | 0      |

#### Bit 2 – ACKACT: Acknowledge Action

This bit defines the slave's behavior under certain conditions defined by the bus protocol state and software interaction. The table below lists the acknowledge procedure performed by the slave if action is initiated by software. The acknowledge action is performed when TWI.SDATA is read or written, or when an execute command is written to the CMD bits in this register.

The ACKACT bit is not a flag or strobe, but an ordinary read/write accessible register bit.

| Value | Name | Description |

|-------|------|-------------|

| 0     | ACK  | Send ACK    |

| 1     | NACK | Send NACK   |

#### Bits 1:0 – CMD[1:0]: Command

Unlike the acknowledge action bits, the slave command bits are strobes. These bits always read as zero. Writing to these bits trigger a slave operation as defined in the table below.

| CMD[1:0]        | DIR  | Description                                                                     |  |  |  |

|-----------------|------|---------------------------------------------------------------------------------|--|--|--|

| 0x0 - NOACT     | Х    | No action                                                                       |  |  |  |

| 0x1             | Х    | Reserved                                                                        |  |  |  |

| 0x2 - COMPTRANS | Used | d to complete a transaction.                                                    |  |  |  |

|                 | 0    | Execute Acknowledge Action succeeded by waiting for any START (S/Sr) condition. |  |  |  |

|                 | 1    | Wait for any START (S/Sr) condition.                                            |  |  |  |

| 0x3 - RESPONSE  | Used | Used in response to an address interrupt (APIF).                                |  |  |  |

|                 | 0    | Execute Acknowledge Action succeeded by reception of next byte.                 |  |  |  |

|                 | 1    | Execute Acknowledge Action succeeded by slave data interrupt.                   |  |  |  |

|                 | Used | Used in response to a data interrupt (DIF).                                     |  |  |  |

|                 | 0    | Execute Acknowledge Action succeeded by reception of next byte.                 |  |  |  |

|                 | 1    | Execute a byte read operation followed by Acknowledge Action.                   |  |  |  |

#### Table 26-5. Command Settings

The acknowledge action bits and command bits can be written at the same time.

#### 26.5.11 Slave Status

Enable-protection is denoted by the Enable-Protected property in the register description.

#### 28.3.2 Operation

#### 28.3.2.1 Enabling, Disabling and Resetting

The CCL is enabled by writing a '1' to the ENABLE bit in the Control register (CCL.CTRLA). The CCL is disabled by writing a '0' to that ENABLE bit.

Each LUT is enabled by writing a '1' to the LUT Enable bit (ENABLE) in the LUT n Control A register (CCL.LUTnCTRLA). Each LUT is disabled by writing a '0' to the ENABLE bit in CCL.LUTnCTRLA.

#### 28.3.2.2 Lookup Table Logic

The lookup table in each LUT unit can generate a combinational logic output as a function of up to three inputs IN[2:0]. Unused inputs can be masked (tied low). The truth table for the combinational logic expression is defined by the bits in the CCL.TRUTHn registers. Each combination of the input bits (IN[2:0]) corresponds to one bit in the TRUTHn register, as shown in the table:

| IN[2] | IN[1] | IN[0] | OUT      |

|-------|-------|-------|----------|

| 0     | 0     | 0     | TRUTH[0] |

| 0     | 0     | 1     | TRUTH[1] |

| 0     | 1     | 0     | TRUTH[2] |

| 0     | 1     | 1     | TRUTH[3] |

| 1     | 0     | 0     | TRUTH[4] |

| 1     | 0     | 1     | TRUTH[5] |

| 1     | 1     | 0     | TRUTH[6] |

| 1     | 1     | 1     | TRUTH[7] |

# Table 28-2. Truth Table of LUT

#### 28.3.2.3 Truth Table Inputs Selection

#### Input Overview

The inputs can be individually:

- Masked

- Driven by peripherals:

- Analog comparator output (AC)

- Timer/Counters waveform outputs (TC)

- Driven by internal events from Event System

- Driven by other CCL sub-modules

The Input Selection for each input y of LUT n is configured by writing the Input y Source Selection bit in the LUT n Control x=[B,C] registers

- INSEL0 in CCL.LUTnCTRLB

- INSEL1 in CCL.LUTnCTRLB

- INSEL2 in CCL.LUTnCTRLC.

# 38. Conventions

# 38.1 Numerical Notation

Table 38-1. Numerical Notation

| Symbol | Description                                                               |

|--------|---------------------------------------------------------------------------|

| 165    | Decimal number                                                            |

| 0b0101 | Binary number (example 0b0101 = 5 decimal)                                |

| '0101' | Binary numbers are given without prefix if unambiguous.                   |

| 0x3B24 | Hexadecimal number                                                        |

| X      | Represents an unknown or don't care value                                 |

| Z      | Represents a high-impedance (floating) state for either a signal or a bus |

# 38.2 Memory Size and Type Table 38-2. Memory Size and Bit Rate

| Symbol     | Description                                 |

|------------|---------------------------------------------|

| KB (kbyte) | kilobyte (2 <sup>10</sup> = 1024)           |

| MB (Mbyte) | megabyte (2 <sup>20</sup> = 1024*1024)      |

| GB (Gbyte) | gigabyte (2 <sup>30</sup> = 1024*1024*1024) |

| b          | bit (binary '0' or '1')                     |

| В          | byte (8 bits)                               |

| 1kbit/s    | 1,000 bit/s rate (not 1,024 bit/s)          |

| 1Mbit/s    | 1,000,000 bit/s rate                        |

| 1Gbit/s    | 1,000,000,000 bit/s rate                    |

| word       | 16 bit                                      |

# 38.3 Frequency and Time

| Symbol | Description                         |

|--------|-------------------------------------|

| kHz    | 1kHz = 10 <sup>3</sup> Hz = 1,000Hz |

| KHz    | 1KHz = 1,024Hz, 32KHz = 32,768Hz    |

| MHz    | 10 <sup>6</sup> = 1,000,000Hz       |

| GHz    | 10 <sup>9</sup> = 1,000,000,000Hz   |