#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 66MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                  |

| RAM Controllers                 | DRAM                                                                 |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10Mbps (2), 10/100Mbps (2)                                           |

| SATA                            | -                                                                    |

| USB                             | USB 2.0 (1)                                                          |

| Voltage - I/O                   | 3.3V                                                                 |

| Operating Temperature           | -40°C ~ 100°C (TA)                                                   |

| Security Features               | -                                                                    |

| Package / Case                  | 357-BBGA                                                             |

| Supplier Device Package         | 357-PBGA (25x25)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc880czp66 |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Provides enhanced ATM functionality found on the MPC862 and MPC866 families and includes the following:

- Improved operation, administration and maintenance (OAM) support

- OAM performance monitoring (PM) support

- Multiple APC priority levels available to support a range of traffic pace requirements

- Port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (100BaseT) and UTOPIA (half- or full -duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA L2-compliant interface with added FIFO buffering to reduce the total cell transmission time and multi-PHY support. (The earlier UTOPIA L1 specification is also supported.)

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA master (ATM side) and slave (PHY side) operations using a split bus

- AAL2/VBR functionality is ROM-resident

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROMs, Flash EPROMs, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting.

- Interrupt can be masked on reference match and event capture

- Two fast Ethernet controllers (FEC)—Two 10/100 Mbps Ethernet/IEEE Std. 802.3<sup>™</sup> CDMA/CS that interface through MII and/or RMII interfaces

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Clock synthesizer

- Decrementer and time base

- Reset controller

- IEEE Std 1149.1<sup>TM</sup> test access port (JTAG)

- Security engine is optimized to handle all the algorithms associated with IPsec, SSL/TLS, SRTP, IEEE Std 802.11i<sup>TM</sup>, and iSCSI processing. Available on the MPC885, the security engine contains a crypto-channel, a controller, and a set of crypto hardware accelerators (CHAs). The CHAs are:

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2, K1) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rijndael symmetric key cipher

- ECB, CBC, and counter modes

- 128-, 192-, and 256- bit key lengths

- Message digest execution unit (MDEU)

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Crypto-channel supporting multi-command descriptor chains

- Integrated controller managing internal resources and bus mastering

- Buffer size of 256 bytes for the DEU, AESU, and MDEU, with flow control for large data sizes

- Interrupts

- Six external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- 23 internal interrupt sources

- Programmable priority between SCCs

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- 8-Kbytes of dual-port RAM

- Several serial DMA (SDMA) channels to support the CPM

- Three parallel I/O registers with open-drain capability

Features

- Flexible data buffers with multiple buffers per frame

- Automatic retransmission upon transmit error

- The USB host controller has the following features:

- Supports control, bulk, interrupt, and isochronous data transfers

- CRC16 generation and checking

- NRZI encoding/decoding with bit stuffing

- Supports both 12- and 1.5-Mbps data rates (automatic generation of preamble token and data rate configuration). Note that low-speed operation requires an external hub.

- Flexible data buffers with multiple buffers per frame

- Supports local loop back mode for diagnostics (12 Mbps only)

- Serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multiple-master operation on the same bus

- Inter-integrated circuit (I<sup>2</sup>C) port

- Supports master and slave modes

- Supports a multiple-master environment

- Time-slot assigner (TSA)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

- Allows dynamic changes

- Can be internally connected to four serial channels (two SCCs and two SMCs)

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on MPC885/MPC880 and other MPC8xx devices

- PCMCIA interface

- Master (socket) interface, release 2.1-compliant

- Supports two independent PCMCIA sockets

- 8 memory or I/O windows supported

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- Supports conditions:  $= \neq < >$

- Each watchpoint can generate a break point internally.

- Normal high and normal low power modes to conserve power

- 1.8-V core and 3.3-V I/O operation

- The MPC885/MPC880 comes in a 357-pin ball grid array (PBGA) package

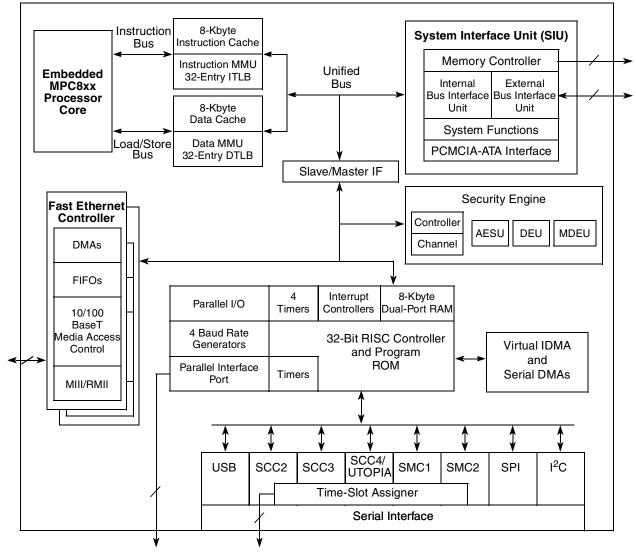

The MPC885 block diagram is shown in Figure 1.

Figure 1. MPC885 Block Diagram

## 7.6 References

Semiconductor Equipment and Materials International(415) 964-5111 805 East Middlefield Rd Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) specifications800-854-7179 or (Available from Global Engineering Documents)303-397-7956

JEDEC Specifications http://www.jedec.org

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 8 Power Supply and Power Sequencing

This section provides design considerations for the MPC885/MPC880 power supply. The MPC885/MPC880 has a core voltage ( $V_{DDL}$ ) and PLL voltage ( $V_{DDSYN}$ ), which both operate at a lower voltage than the I/O voltage  $V_{DDH}$ . The I/O section of the MPC885/MPC880 is supplied with 3.3 V across  $V_{DDH}$  and  $V_{SS}$  (GND).

The signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TCK, TRST\_B, TMS, MII\_TXEN, and MII\_MDIO are 5 V tolerant. All inputs cannot be more than 2.5 V greater than V<sub>DDH</sub>. In addition, 5-V tolerant pins cannot exceed 5.5 V and remaining input pins cannot exceed 3.465 V. This restriction applies to power up/down and normal operation.

One consequence of multiple power supplies is that when power is initially applied the voltage rails ramp up at different rates. The rates depend on the nature of the power supply, the type of load on each power supply, and the manner in which different voltages are derived. The following restrictions apply:

- $V_{DDL}$  must not exceed  $V_{DDH}$  during power up and power down.

- V<sub>DDL</sub> must not exceed 1.9 V, and V<sub>DDH</sub> must not exceed 3.465 V.

These cautions are necessary for the long-term reliability of the part. If they are violated, the electrostatic discharge (ESD) protection diodes are forward-biased, and excessive current can flow through these diodes. If the system power supply design does not control the voltage sequencing, the circuit shown Figure 5 can be added to meet these requirements. The MUR420 Schottky diodes control the maximum potential difference between the external bus and core power supplies on power up, and the 1N5820 diodes regulate the maximum potential difference on power down.

| Num  | Characteristic                                                                                                                         | 33    | MHz   | 40 I  | MHz   | 66 I  | MHz   | 80    | MHz   | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                         | Min   | Мах   | Min   | Мах   | Min   | Max   | Min   | Мах   | Unit |

| B16b | $\overline{BB}, \overline{BG}, \overline{BR}, \text{ valid to CLKOUT (setup time)}^2$<br>(4MIN = 0.00 × B1 + 0.00)                     | 4.00  | —     | 4.00  | _     | 4.00  | —     | 4.00  | _     | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time) (MIN = $0.00 \times B1 + 1.00^3$ )                                                 | 1.00  |       | 1.00  |       | 2.00  | _     | 2.00  |       | ns   |

| B17a | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00)    | 2.00  | —     | 2.00  | -     | 2.00  | —     | 2.00  |       | ns   |

| B18  | D(0:31) valid to CLKOUT rising edge (setup time) <sup>4</sup> (MIN = $0.00 \times B1 + 6.00$ )                                         | 6.00  | —     | 6.00  | _     | 6.00  | —     | 6.00  | _     | ns   |

| B19  | CLKOUT rising edge to D(0:31) valid (hold time) <sup>4</sup> (MIN = $0.00 \times B1 + 1.00^5$ )                                        | 1.00  | —     | 1.00  |       | 2.00  | —     | 2.00  |       | ns   |

| B20  | D(0:31) valid to CLKOUT falling edge (setup time) <sup>6</sup> (MIN = $0.00 \times B1 + 4.00$ )                                        | 4.00  | —     | 4.00  |       | 4.00  | _     | 4.00  |       | ns   |

| B21  | CLKOUT falling edge to D(0:31) valid (hold time) <sup>6</sup> (MIN = $0.00 \times B1 + 2.00$ )                                         | 2.00  | —     | 2.00  |       | 2.00  | —     | 2.00  |       | ns   |

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted GPCM<br>ACS = 00 (MAX = 0.25 × B1 + 6.3)                                                | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13  | 9.43  | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = [0 or 1]<br>(MAX = 0.00 × B1 + 8.00)                          |       | 8.00  |       | 8.00  | _     | 8.00  | _     | 8.00  | ns   |

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = [0 or 1], EBDF = 0<br>(MAX = 0.25 × B1 + 6.3)                 | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13  | 9.43  | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = [0 or 1], EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                | 10.90 | 18.00 | 10.90 | 16.00 | 5.20  | 12.30 | 4.69  | 10.93 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated GPCM read<br>access, GPCM write access ACS = 00 and CSNT<br>= 0 (MAX = 0.00 × B1 + 8.00) | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0<br>(MIN = $0.25 \times B1 - 2.00$ )                    | 5.60  |       | 4.30  |       | 1.80  |       | 1.13  |       | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 11 TRLX = 0<br>(MIN = 0.50 × B1 - 2.00)                             | 13.20 |       | 10.50 |       | 5.60  | _     | 4.25  |       | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}$ (0:3) asserted<br>(MAX = 0.00 × B1 + 9.00)                                     | _     | 9.00  | —     | 9.00  | —     | 9.00  | —     | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated<br>(MAX = 0.00 × B1 + 9.00)                                                              | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 1<br>(MIN = $1.25 \times B1 - 2.00$ )                    | 35.90 |       | 29.30 |       | 16.90 |       | 13.60 |       | ns   |

## Table 9. Bus Operation Timings (continued)

| Num  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 I  | MHz   | 40 I  | MHz   | 66 I  | MHz   | 80 I  | MHz   | Unit |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min   | Мах   | Min   | Мах   | Min   | Max   | Min   | Мах   | Unit |

| B29h | $\overline{\text{WE}}(0:3)$ negated to D(0:31) High-Z GPCM write<br>access, TRLX = 1, CSNT = 1, EBDF = 1<br>(MIN = 0.375 × B1 - 3.30)                                                                                                                                                                                                                                                                                                                                       | 38.40 |       | 31.10 |       | 17.50 | _     | 13.85 |       | ns   |

| B29i | $\overline{\text{CS}}$ negated to D(0:31) High-Z GPCM write<br>access, TRLX = 1, CSNT = 1, ACS = 10 or<br>ACS = 11, EBDF = 1 (MIN = 0.375 × B1 – 3.30)                                                                                                                                                                                                                                                                                                                      | 38.40 | _     | 31.10 |       | 17.50 | _     | 13.85 |       | ns   |

| B30  | $\label{eq:cs} \hline{\text{CS}}, \overline{\text{WE}}(0:3) \text{ negated to A}(0:31), \text{BADDR}(28:30) \\ \\ \text{Invalid GPCM read/write access}^8 \\ (\text{MIN} = 0.25 \times \text{B1} - 2.00) \\ \hline$                                                                                                                                                                                                                                                         | 5.60  |       | 4.30  |       | 1.80  | _     | 1.13  |       | ns   |

| B30a | $\label{eq:weighted_states} \hline \hline WE(0:3) \ \text{negated to } A(0:31), \ BADDR(28:30) \\ \hline \text{Invalid GPCM, write access, } TRLX = 0, \ CSNT = 1, \\ \hline CS \ \text{negated to } A(0:31) \ \text{invalid GPCM write access} \\ TRLX = 0, \ CSNT = 1 \ ACS = 10, \ \text{or } ACS = = 11, \\ \hline EBDF = 0 \ (MIN = 0.50 \times B1 - 2.00) \\ \hline \hline \end{array}$                                                                               | 13.20 |       | 10.50 | _     | 5.60  | _     | 4.25  | _     | ns   |

| B30b | $\label{eq:weighted_states} \hline \hline WE(0:3) \ \text{negated to } A(0:31) \ \text{invalid GPCM} \\ \hline BADDR(28:30) \ \text{invalid GPCM} \ \text{write access}, \\ \hline TRLX = 1, \ CSNT = 1. \ \overline{CS} \ \text{negated to } A(0:31) \\ \hline \text{invalid GPCM} \ \text{write access} \ TRLX = 1, \ CSNT = 1, \\ \hline ACS = 10, \ \text{or } ACS == 11 \ \text{EBDF} = 0 \\ \hline (MIN = 1.50 \times \text{B1} - 2.00) \\ \hline \hline \end{array}$ | 43.50 | _     | 35.50 | _     | 20.70 |       | 16.75 |       | ns   |

| B30c | $\label{eq:weighted_states} \begin{array}{ c c c c c } \hline \hline WE(0:3) \mbox{ negated to } A(0:31), \mbox{ BADDR}(28:30) \\ \hline \mbox{ invalid GPCM write access, TRLX = 0, CSNT = 1.} \\ \hline \hline CS \mbox{ negated to } A(0:31) \mbox{ invalid GPCM write access, TRLX = 0, CSNT = 1 ACS = 10,} \\ \hline ACS == 11, \mbox{ EBDF = 1 (MIN = 0.375 \times B1 - 3.00)} \end{array}$                                                                           | 8.40  | _     | 6.40  |       | 2.70  | _     | 1.70  |       | ns   |

| B30d | $\overline{\text{WE}}(0:3)$ negated to A(0:31), BADDR(28:30)<br>invalid GPCM write access TRLX = 1, CSNT =1,<br>$\overline{\text{CS}}$ negated to A(0:31) invalid GPCM write access<br>TRLX = 1, CSNT = 1, ACS = 10 or 11, EBDF = 1                                                                                                                                                                                                                                         | 38.67 |       | 31.38 |       | 17.83 | _     | 14.19 |       | ns   |

| B31  | CLKOUT falling edge to $\overline{\text{CS}}$ valid, as requested by control bit CST4 in the corresponding word in the UPM (MAX = $0.00 \times \text{B1} + 6.00$ )                                                                                                                                                                                                                                                                                                          | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

| B31a | CLKOUT falling edge to $\overline{\text{CS}}$ valid, as requested by control bit CST1 in the corresponding word in the UPM (MAX = $0.25 \times \text{B1} + 6.80$ )                                                                                                                                                                                                                                                                                                          | 7.60  | 14.30 | 6.30  | 13.00 | 3.80  | 10.50 | 3.13  | 10.00 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid, as requested by control bit CST2 in the corresponding word in the UPM (MAX = $0.00 \times B1 + 8.00$ )                                                                                                                                                                                                                                                                                                                         | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid, as requested by control bit CST3 in the corresponding word in the UPM (MAX = $0.25 \times B1 + 6.30$ )                                                                                                                                                                                                                                                                                                                         | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13  | 9.40  | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid, as requested by<br>control bit CST1 in the corresponding word in the<br>UPM EBDF = 1 (MAX = $0.375 \times B1 + 6.6$ )                                                                                                                                                                                                                                                                                                         | 13.30 | 18.00 | 11.30 | 16.00 | 7.60  | 12.30 | 4.69  | 11.30 | ns   |

## Table 9. Bus Operation Timings (continued)

| Num | Characteristic                                                                                                                                                      | 33   | MHz | 40 I | MHz | 66 I | MHz | 80   | Unit |      |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-----|------|-----|------|------|------|

| Num | Characteristic                                                                                                                                                      | Min  | Max | Min  | Max | Min  | Max | Min  | Max  | Unit |

| B36 | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{GPL}}$ valid, as requested by control bit GxT4 in the corresponding word in the UPM (MIN = 0.25 × B1 - 2.00) | 5.60 |     | 4.30 | _   | 1.80 |     | 1.13 |      | ns   |

| B37 | UPWAIT valid to CLKOUT falling edge <sup>9</sup><br>(MIN = $0.00 \times B1 + 6.00$ )                                                                                | 6.00 | —   | 6.00 |     | 6.00 | —   | 6.00 | _    | ns   |

| B38 | CLKOUT falling edge to UPWAIT valid $^9$<br>(MIN = 0.00 × B1 + 1.00)                                                                                                | 1.00 | —   | 1.00 |     | 1.00 | —   | 1.00 | _    | ns   |

| B39 | $\overline{\text{AS}}$ valid to CLKOUT rising edge <sup>10</sup><br>(MIN = 0.00 × B1 + 7.00)                                                                        | 7.00 | _   | 7.00 |     | 7.00 | _   | 7.00 |      | ns   |

| B40 | A(0:31), TSIZ(0:1), RD/ $\overline{WR}$ , $\overline{BURST}$ , valid to<br>CLKOUT rising edge (MIN = $0.00 \times B1 + 7.00$ )                                      | 7.00 | —   | 7.00 | -   | 7.00 | _   | 7.00 | —    | ns   |

| B41 | $\overline{\text{TS}}$ valid to CLKOUT rising edge (setup time)<br>(MIN = 0.00 × B1 + 7.00)                                                                         | 7.00 | —   | 7.00 |     | 7.00 | —   | 7.00 | _    | ns   |

| B42 | CLKOUT rising edge to $\overline{\text{TS}}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00)                                                                          | 2.00 | —   | 2.00 | _   | 2.00 | _   | 2.00 | _    | ns   |

| B43 | $\overline{\text{AS}}$ negation to memory controller signals negation (MAX = TBD)                                                                                   | —    | TBD | —    | TBD | _    | TBD | —    | TBD  | ns   |

#### Table 9. Bus Operation Timings (continued)

<sup>1</sup> For part speeds above 50 MHz, use 9.80 ns for B11a.

<sup>2</sup> The timing required for BR input is relevant when the MPC885/MPC880 is selected to work with the internal bus arbiter. The timing for BG input is relevant when the MPC885/MPC880 is selected to work with the external bus arbiter.

<sup>3</sup> For part speeds above 50 MHz, use 2 ns for B17.

<sup>4</sup> The D(0:31) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

<sup>5</sup> For part speeds above 50 MHz, use 2 ns for B19.

<sup>6</sup> The D(0:31) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read accesses controlled by chip-selects under control of the user-programmable machine (UPM) in the memory controller, for data beats where DLT3 = 1 in the RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

<sup>7</sup> This formula applies to bus operation up to 50 MHz.

<sup>8</sup> The timing B30 refers to  $\overline{CS}$  when ACS = 00 and to  $\overline{CS}$  and  $\overline{WE}(0:3)$  when CSNT = 0.

<sup>9</sup> The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 21.

<sup>10</sup> The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified in Figure 24.

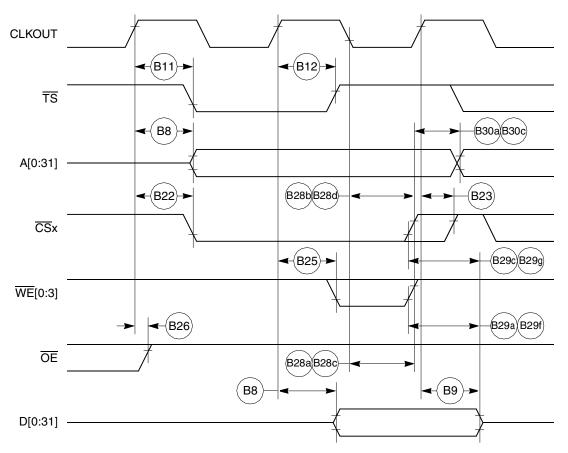

**Bus Signal Timing**

Figure 18. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 1)

Bus Signal Timing

## Table 12 shows the PCMCIA port timing for the MPC885/MPC880.

| Num | Characteristic                                                               | 33 MHz |       | 40 MHz |       | 66 MHz |       | 80 MHz |       | Unit |

|-----|------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Num | Unaracteristic                                                               | Min    | Мах   | Min    | Max   | Min    | Мах   | Min    | Max   | Unit |

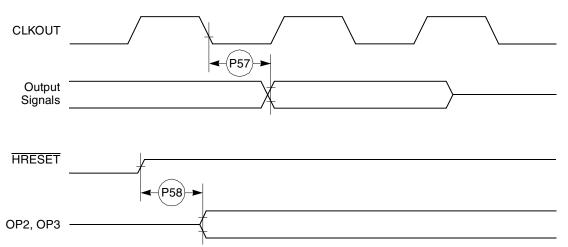

| P57 | CLKOUT to OPx valid<br>(MAX = $0.00 \times B1 + 19.00$ )                     | _      | 19.00 | _      | 19.00 | -      | 19.00 | -      | 19.00 | ns   |

| P58 | HRESET negated to OPx drive <sup>1</sup><br>(MIN = $0.75 \times B1 + 3.00$ ) | 25.70  | -     | 21.70  | _     | 14.40  | _     | 12.40  | _     | ns   |

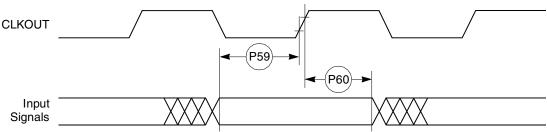

| P59 | IP_Xx valid to CLKOUT rising edge (MIN = $0.00 \times B1 + 5.00$ )           |        | _     | 5.00   | _     | 5.00   | —     | 5.00   | _     | ns   |

| P60 | CLKOUT rising edge to IP_Xx invalid<br>(MIN = $0.00 \times B1 + 1.00$ )      | 1.00   | _     | 1.00   |       | 1.00   |       | 1.00   |       | ns   |

#### Table 12. PCMCIA Port Timing

<sup>1</sup> OP2 and OP3 only.

## Figure 31 provides the PCMCIA output port timing for the MPC885/MPC880.

#### Figure 31. PCMCIA Output Port Timing

Figure 32 provides the PCMCIA input port timing for the MPC885/MPC880.

Figure 32. PCMCIA Input Port Timing

| Num | Characteristic                                                         | All Fre | equencies             | Unit   |

|-----|------------------------------------------------------------------------|---------|-----------------------|--------|

| Num | Characteristic                                                         | Min     | Max                   | Unit   |

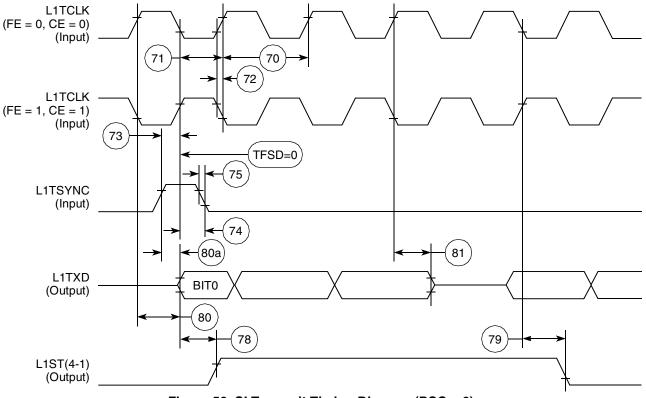

| 76  | L1RXD valid to L1CLK edge (L1RXD setup time)                           | 17.00   | _                     | ns     |

| 77  | L1CLK edge to L1RXD invalid (L1RXD hold time)                          | 13.00   | _                     | ns     |

| 78  | L1CLK edge to L1ST(1-4) valid <sup>4</sup>                             | 10.00   | 45.00                 | ns     |

| 78A | L1SYNC valid to L1ST(1-4) valid                                        | 10.00   | 45.00                 | ns     |

| 79  | L1CLK edge to L1ST(1-4) invalid                                        | 10.00   | 45.00                 | ns     |

| 80  | L1CLK edge to L1TXD valid                                              | 10.00   | 55.00                 | ns     |

| 80A | L1TSYNC valid to L1TXD valid <sup>4</sup>                              | 10.00   | 55.00                 | ns     |

| 81  | L1CLK edge to L1TXD high impedance                                     | 0.00    | 42.00                 | ns     |

| 82  | L1RCLK, L1TCLK frequency (DSC =1)                                      | _       | 16.00 or<br>SYNCCLK/2 | MHz    |

| 83  | L1RCLK, L1TCLK width low (DSC =1)                                      | P + 10  | —                     | ns     |

| 83a | L1RCLK, L1TCLK width high $(DSC = 1)^3$                                | P + 10  | —                     | ns     |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                   | —       | 30.00                 | ns     |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>                 | 1.00    | —                     | L1TCLK |

| 86  | L1GR setup time <sup>2</sup>                                           | 42.00   | —                     | ns     |

| 87  | L1GR hold time                                                         | 42.00   | —                     | ns     |

| 88  | L1CLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0,<br>DSC = 0) | -       | 0.00                  | ns     |

#### Table 21. SI Timing (continued)

The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

These specs are valid for IDL mode only.

<sup>3</sup> Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever comes later.

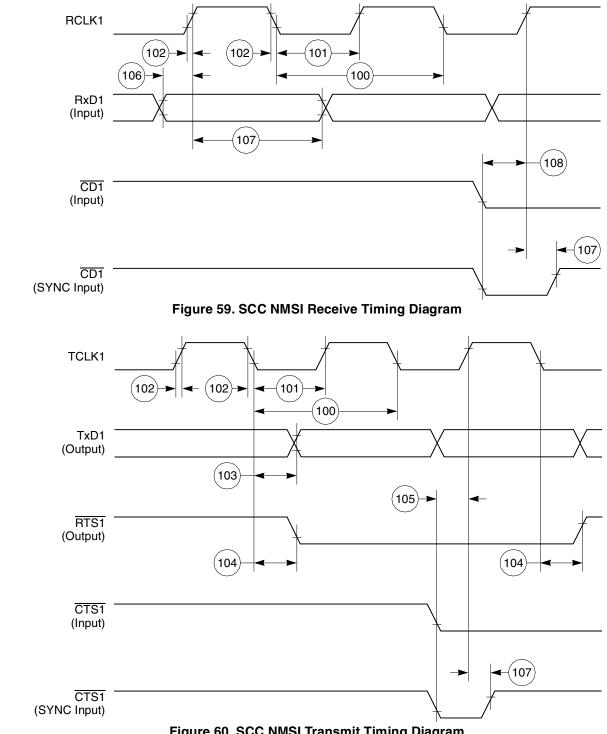

Figure 59 through Figure 61 show the NMSI timings.

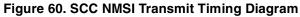

## 12.11 SPI Slave AC Electrical Specifications

Table 27 provides the SPI slave timings as shown in Figure 68 and Figure 69.

#### Table 27. SPI Slave Timing

| Num   | Characteristic                                              | All Freq | Unit |                  |

|-------|-------------------------------------------------------------|----------|------|------------------|

| Nulli |                                                             | Min      | Мах  | Onit             |

| 170   | Slave cycle time                                            | 2        | —    | t <sub>cyc</sub> |

| 171   | Slave enable lead time                                      | 15       | —    | ns               |

| 172   | Slave enable lag time                                       | 15       | —    | ns               |

| 173   | Slave clock (SPICLK) high or low time                       | 1        | —    | t <sub>cyc</sub> |

| 174   | Slave sequential transfer delay (does not require deselect) | 1        | —    | t <sub>cyc</sub> |

| 175   | Slave data setup time (inputs)                              | 20       | —    | ns               |

| 176   | Slave data hold time (inputs)                               | 20       | —    | ns               |

| 177   | Slave access time                                           | —        | 50   | ns               |

Mechanical Data and Ordering Information

## 16.1 Pin Assignments

Figure 77 shows the top-view pinout of the PBGA package. For additional information, see the *MPC885 PowerQUICC<sup>TM</sup> Family Reference Manual*.

| (         |            |               |           |            |              |            |            |            |            |            |            |            |            |            |            |            |           |            |   |

|-----------|------------|---------------|-----------|------------|--------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-----------|------------|---|

|           | O<br>TRST  | O<br>PA10     | O<br>PB23 | O<br>PA8   | O<br>PC8     | O<br>PA5   | O<br>PB17  | O<br>PA13  | O<br>PC4   | O<br>PA11  | O<br>PE17  | O<br>PE30  | O<br>PE15  | O<br>PD6   | O<br>PD4   | O<br>PD7   | O<br>PA3  |            | w |

| O<br>PB28 | O<br>TMS   | O<br>PB25     | O<br>PC11 | O<br>PB22  |              | O<br>PB19  | O<br>PC7   | O<br>PB16  | O<br>PC13  | O<br>PE21  | O<br>PE24  | O<br>PE14  | O<br>PD5   | O<br>PE28  | O<br>PE27  | О<br>РВ31  | O<br>PE23 | O<br>PE22  | v |

| O<br>PB27 | O<br>PB14  | О             | О<br>РВ24 | O<br>PC10  | O<br>PB21    | O<br>PA6   |            | O<br>PC6   | O<br>PB15  | O<br>PE31  | O<br>PD15  | O<br>PD14  | O<br>PD13  | O<br>PD12  | O<br>PA4   |            | O<br>PD9  | O<br>PA1   | U |

| O<br>PB29 | O<br>PC12  | О             |           | O<br>PA9   | O<br>PC9     | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | O<br>PD3   | O<br>PE29  | O<br>PE16  | $\bigcirc$ |            | $\bigcirc$ | O<br>PE25  | O<br>PD10 | O<br>PE26  | т |

| O<br>PC15 | O<br>PC14  | O<br>PB26     | O<br>GND  | O<br>VDDL  | 0            | 0          |            | 0          | 0          | O<br>VDDL  | 0          | 0          |            | VDDH       | O<br>PE20  |            | O<br>PD11 | O<br>PE18  | R |

|           | О<br>РВ30  | O<br>PA14     | O<br>PA12 |            | 0            |            | $\bigcirc$ |            | 0          |            | 0          | GND        | 0          | $\bigcirc$ |            |            | 0<br>D0   | О<br>D8    | Ρ |

| ()<br>A2  | ()<br>A1   | O<br>N/C      | O<br>PA15 | 0          | 0            | $\circ$    | $\bigcirc$ | $\bigcirc$ | GND        | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          |            |            | ()<br>D12  | O<br>D13  | 0<br>D4    | Ν |

| О<br>АЗ   | ()<br>A5   | ()<br>A4      | ()<br>A0  |            | $\bigcirc$   | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ |            | 0          | D17        | O<br>D23   | 0<br>D27  | O<br>D1    | М |

| ⊖<br>A7   | ()<br>A9   | ()<br>A8      | ()<br>A6  | 0          |              |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            | 0          |            | O<br>D9    | O<br>D10   | O<br>D11  | ()<br>D2   | L |

| O<br>A10  | O<br>A11   | ()<br>A12     | O<br>A13  |            | 0            | 0          | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            | 0          | 0<br>D5    | O<br>D14   | О         | O<br>D15   | к |

| A14       | A16        | A15           | A17       | 0          | 0            | 0          | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | VDDL       | D22        | D19        | D16       | D18        | J |

| A27       | ()<br>A19  | ()<br>A20     | O<br>A24  |            | 0            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | 0          | 0          | D28        | D6         | D20       | D21        | н |

| O<br>A21  | ()<br>A29  | ()<br>A23     |           |            |              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | 0          | $\bigcirc$ |            |            | CLKOUT     | O<br>D26   | O<br>D24  | O<br>D25   | G |

| A25       | ()<br>A30  | O<br>A22      | O<br>BSA3 | 0          | 0            | 0          | $\bigcirc$ | $\bigcirc$ |            | $\bigcirc$ | 0          | $\bigcirc$ | 0          | $\bigcirc$ |            | O<br>D31   | D7        | 0<br>D29   | F |

|           | ()<br>A28  |               |           | $\bigcirc$ | VDDL         | 0          | $\bigcirc$ | VDDL       | $\circ$    | VDDL       | 0          | $\bigcirc$ | 0          |            |            |            |           | O<br>D30   | Е |

|           | A31        | 0             | GPL AB2   |            |              |            |            |            |            |            | ALEB       |            |            |            |            | $\bigcirc$ |           |            | D |

| BSA2      | BSA1       |               |           |            |              | GPL_A5     |            |            | BURST      |            | IPB2       |            | 0          | BADDR2     | $\bigcirc$ | $\bigcirc$ |           |            | с |

|           |            |               |           |            |              |            |            |            |            |            |            |            | 0          | 0          | $\bigcirc$ | $\bigcirc$ |           | $\bigcirc$ | в |

| WES       | $\bigcirc$ | GPL_AU        |           | $\bigcirc$ |              |            |            |            |            |            |            | BADDR30    | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |           | IF AU      | А |

| 19        | 18         | брг_авз<br>17 | 16        | 15         | арс_в4<br>14 | 13         | 12         | 11         | 10         | 9          | 8          | 7<br>7     | 6          | 5          | 4          | 3          | 2         | 1          |   |

**NOTE:** This is the top view of the device.

Figure 77. Pinout of the PBGA Package

| Table 39. | Pin | Assignments | (continued) |

|-----------|-----|-------------|-------------|

|-----------|-----|-------------|-------------|

| Name                                                       | Pin Number         | Туре                      |

|------------------------------------------------------------|--------------------|---------------------------|

| WE0, BS_B0, IORD                                           | B18                | Output                    |

| WE1, BS_B1, IOWR                                           | E16                | Output                    |

| WE2, BS_B2, PCOE                                           | C17                | Output                    |

| WE3, BS_B3, PCWE                                           | B19                | Output                    |

| BS_A[0:3]                                                  | D17, C18, C19, F16 | Output                    |

| GPL_A0, GPL_B0                                             | B17                | Output                    |

| OE, GPL_A1, GPL_B1                                         | A18                | Output                    |

| <u>GPL_A[2:3]</u> , <u>GPL_B[2:3]</u> ,<br><u>CS</u> [2:3] | D16, A17           | Output                    |

| UPWAITA, GPL_A4                                            | B13                | Bidirectional             |

| UPWAITB, GPL_B4                                            | A14                | Bidirectional             |

| GPL_A5                                                     | C13                | Output                    |

| PORESET                                                    | B3                 | Input                     |

| RSTCONF                                                    | D4                 | Input                     |

| HRESET                                                     | B4                 | Open-drain                |

| SRESET                                                     | A3                 | Open-drain                |

| XTAL                                                       | A4                 | Analog output             |

| EXTAL                                                      | D5                 | Analog input (3.3 V only) |

| CLKOUT                                                     | G4                 | Output                    |

| EXTCLK                                                     | A5                 | Input (3.3 V only)        |

| TEXP                                                       | C4                 | Output                    |

| ALE_A                                                      | B7                 | Output                    |

| CE1_A                                                      | B15                | Output                    |

| CE2_A                                                      | C15                | Output                    |

| WAIT_A, SOC_Split <sup>1</sup>                             | A2                 | Input                     |

| WAIT_B                                                     | C3                 | Input                     |

| IP_A0, UTPB_Split0 <sup>1</sup>                            | B1                 | Input                     |

| IP_A1, UTPB_Split1 <sup>1</sup>                            | C1                 | Input                     |

| IP_A2, IOIS16_A,<br>UTPB_Split2 <sup>1</sup>               | F4                 | Input                     |

| IP_A3, UTPB_Split3 <sup>1</sup>                            | E3                 | Input                     |

| IP_A4, UTPB_Split4 <sup>1</sup>                            | D2                 | Input                     |

| IP_A5, UTPB_Split5 <sup>1</sup>                            | D1                 | Input                     |

| IP_A6, UTPB_Split6 <sup>1</sup>                            | E2                 | Input                     |

| IP_A7, UTPB_Split7 <sup>1</sup>                            | D3                 | Input                     |

## Table 39. Pin Assignments (continued)

| Name                                                                  | Pin Number | Туре                                    |

|-----------------------------------------------------------------------|------------|-----------------------------------------|

| PA4, CTS4, MII1-TXD1,<br>RMII1-TXD1                                   | U4         | Bidirectional                           |

| PA3, MII1-RXER,<br>RMII1-RXER, BRGO3                                  | W2         | Bidirectional                           |

| PA2, MII1-RXDV,<br>RMII1-CRS_DV, TXD4                                 | T4         | Bidirectional                           |

| PA1, MII1-RXD0,<br>RMII1-RXD0, BRGO4                                  | U1         | Bidirectional                           |

| PA0, MII1-RXD1,<br>RMII1-RXD1, TOUT4                                  | U3         | Bidirectional                           |

| PB31, <del>SPISEL</del> ,<br>MII1-TXCLK,<br>RMII1-REFCLK              | V3         | Bidirectional<br>(Optional: open-drain) |

| PB30, SPICLK                                                          | P18        | Bidirectional<br>(Optional: open-drain) |

| PB29, SPIMOSI                                                         | T19        | Bidirectional<br>(Optional: open-drain) |

| PB28, SPIMISO, BRGO4                                                  | V19        | Bidirectional<br>(Optional: open-drain) |

| PB27, I2CSDA, BRGO1                                                   | U19        | Bidirectional<br>(Optional: open-drain) |

| PB26, I2CSCL, BRGO2                                                   | R17        | Bidirectional<br>(Optional: open-drain) |

| PB25, RXADDR3 <sup>1</sup> ,<br>TXADDR3, SMTXD1                       | V17        | Bidirectional<br>(Optional: open-drain) |

| PB24, TXADDR3 <sup>1</sup> ,<br>RXADDR3, SMRXD1                       | U16        | Bidirectional<br>(Optional: open-drain) |

| PB23, TXADDR2 <sup>1</sup> ,<br>RXADDR2, SDACK1,<br>SMSYN1            | W16        | Bidirectional<br>(Optional: open-drain) |

| PB22, TXADDR4 <sup>1</sup> ,<br>RXADDR4, SDACK2,<br>SMSYN2            | V15        | Bidirectional<br>(Optional: open-drain) |

| PB21, SMTXD2,<br>TXADDR1 <sup>1</sup> , BRG01,<br>RXADDR1, PHSEL[1]   | U14        | Bidirectional<br>(Optional: open-drain) |

| PB20, SMRXD2,<br>L1CLKOA, TXADDR0 <sup>1</sup> ,<br>RXADDR0, PHSEL[0] | T13        | Bidirectional<br>(Optional: open-drain) |

| PB19, MII1-RXD3, RTS4                                                 | V13        | Bidirectional<br>(Optional: open-drain) |

| PB18, RXADDR4 <sup>1</sup> ,<br>TXADDR4, RTS2, L1ST2                  | T12        | Bidirectional<br>(Optional: open-drain) |

| Name                                 | Pin Number                                                                                                                                                                                                                                                          | Туре                        |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| PE14, RXD3, MII2-TXD0,<br>RMII2-TXD0 | V7                                                                                                                                                                                                                                                                  | Bidirectional               |

| TMS                                  | V18                                                                                                                                                                                                                                                                 | Input                       |

| TDI, DSDI                            | T16                                                                                                                                                                                                                                                                 | Input                       |

| TCK, DSCK                            | U17                                                                                                                                                                                                                                                                 | Input                       |

| TRST                                 | W18                                                                                                                                                                                                                                                                 | Input                       |

| TDO, DSDO                            | T17                                                                                                                                                                                                                                                                 | Output                      |

| MII1_CRS                             | T11                                                                                                                                                                                                                                                                 | Input                       |

| MII_MDIO                             | P19                                                                                                                                                                                                                                                                 | Bidirectional               |

| MII1_TXEN, RMII1_TXEN                | Т5                                                                                                                                                                                                                                                                  | Output                      |

| MII1_COL                             | U12                                                                                                                                                                                                                                                                 | Input                       |

| V <sub>SSSYN1</sub>                  | C2                                                                                                                                                                                                                                                                  | PLL analog $V_{DD}$ and GND |

| V <sub>SSSYN</sub>                   | E4                                                                                                                                                                                                                                                                  | Power                       |

| V <sub>DDLSYN</sub>                  | B2                                                                                                                                                                                                                                                                  | Power                       |

| GND                                  | G6, G7, G8, G9, G10, G11, G12, G13, H7, H8, H9, H10, H11, H12,<br>H13, H14, J7, J8, J9, J10, J11, J12, J13, K7, K8, K9, K10, K11, K12,<br>K13, L7, L8, L9, L10, L11, L12, L13, M7, M8, M9, M10, M11, M12,<br>M13, N7, N8, N9, N10, N11, N12, N13, N14, P7, P13, R16 | Power                       |

| V <sub>DDL</sub>                     | E5, E6, E9, E11, E14, G15, H5, J5, J15, K15, L5, M15, N5, R6, R9, R10, R12, R15                                                                                                                                                                                     | Power                       |

| V <sub>DDH</sub>                     | E7, E8, E10, E12, E13, E15, F5, F6, F7, F8, F9, F10, F11, F12, F13, F14, F15, G5, G14, H6, H15, J6, J14, K5, K6, K14, L6, L14, L15, M5, M6, M14, N6, N15, P5, P6, P8, P9, P10, P11, P12, P14, P15, R5, R7, R8, R11, R13, R14                                        | Power                       |

| N/C                                  | N17                                                                                                                                                                                                                                                                 | No connect                  |

## Table 39. Pin Assignments (continued)

<sup>1</sup> ESAR mode only.

# **17 Document Revision History**

Table 40 lists significant changes between revisions of this hardware specification.

| Revision<br>Number | Date      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                  | 07/2010   | <ul> <li>In Table 9, "Bus Operation Timings," changed the following:</li> <li>Updated TRLX condition value for B22a/b/c to "TRLX = [0 or 1]"</li> <li>Removed TRLX condition for B23</li> <li>Updated condition and equation for B30 to "Invalid GPCM read/write access (MIN = 0.25 × B1 - 2.00)"</li> <li>Updated note 8 to "The timing B30 refers to CS when ACS = 00 and to CS and WE(0:3) when CSNT = 0."</li> </ul>                                                                                                                                                   |

| 6                  | 05/2010   | Added minimum load for CLKOUT in Section 10, "Bus Signal Timing."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5                  | 03/2009   | Updated formatting of Table 12, "PCMCIA Port Timing," Table 13, "Debug Port Timing," Table 14, "Reset Timing," and Table 15, "JTAG Timing."                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4                  | 08/2007   | <ul> <li>On page 1, updated first paragraph and added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 3) and renumbered the rest of the figures.</li> <li>In Table 9, for reset timings B29f and B29g added footnote indicating that the formula only applies to bus operation up to 50 MHz.</li> <li>In Figure 6, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 18, changed num 46 description to read, "TA assertion to rising edge"</li> </ul> |

| 3.0                | 7/22/2004 | <ul> <li>Added sentence to Spec B1A about EXTCLK and CLKOUT being in Alignment for Integer Values</li> <li>Added a footnote to Spec 41 specifying that EDM = 1</li> <li>Added RMII1_EN under M1II_EN in Table 36 Pin Assignments</li> <li>Added a tablefootnote to Table 6 DC Electrical Specifications about meeting the VIL Max of the I2C Standard</li> <li>Put the new part numbers in the Ordering Information Section</li> </ul>                                                                                                                                     |

| 2.0                | 12/2003   | <ul> <li>Changed the maximum operating frequency to 133 MHz.</li> <li>Put in the orderable part numbers that are orderable.</li> <li>Put the timing in the 80 MHz column.</li> <li>Rounded the timings to hundredths in the 80 MHz column.</li> <li>Put the pin numbers in footnotes by the maximum currents in Table 6.</li> <li>Changed 22 and 41 in the Timing.</li> <li>Put in the Thermal numbers.</li> </ul>                                                                                                                                                         |

| 1.0                | 9/2003    | <ul> <li>Added the DSP information in the Features list</li> <li>Fixed table formatting.</li> <li>Nontechnical edits.</li> <li>Released to the external web.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.9                | 8/2003    | Changed the USB description to full-/low-speed compatible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.8                | 8/2003    | Added the Reference to USB 2.0 to the Features list and removed 1.1 from USB on the block diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0.7                | 7/2003    | Added the RxClav and TxClav signals to PC15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0.6                | 6/2003    | Changed the pin descriptions per the June 22 spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.5                | 5/2003    | Changed some more typos, put in the phsel and phreq pins. Corrected the USB timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## Table 40. Document Revision History

**Document Revision History**

| Revision<br>Number | Date    | Changes                                                                                                                                                                              |

|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.4                | 5/2003  | Changed the pin descriptions for PD8 and PD9.                                                                                                                                        |

| 0.3                | 05/2003 | Corrected the signals that had overlines on them.                                                                                                                                    |

| 0.2                | 05/2003 | Made the changes to the RMII Timing, Made sure all the $V_{DDL}$ , $V_{DDH}$ , and GND show up on the pinout diagram. Changed the SPI Master Timing Specs. 162 and 164.              |

| 0.1                | 04/2003 | Added pinout and pinout assignments table. Added the USB timing to Section 14. Added the Reduced MII to Section 15. Removed the Data Parity. Made some changes to the Features list. |

| 0                  | 02/2003 | Initial revision.                                                                                                                                                                    |

## Table 40. Document Revision History (continued)