#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 133MHz                                                                |

| Co-Processors/DSP               | Communications; CPM, Security; SEC                                    |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10Mbps (3), 10/100Mbps (2)                                            |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | -40°C ~ 100°C (TA)                                                    |

| Security Features               | Cryptography                                                          |

| Package / Case                  | 357-BBGA                                                              |

| Supplier Device Package         | 357-PBGA (25x25)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc885czp133 |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

The MPC885/MPC880 is a versatile single-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications and communications and networking systems. The MPC885/MPC880 provides enhanced ATM functionality, an additional fast Ethernet controller, a USB, and an encryption block.

Table 1 shows the functionality supported by MPC885/MPC880.

| Part   | Cache (         | Kbytes) | Ethe    | ernet  | scc | SMC  | USB | ATM Support                     | Security |

|--------|-----------------|---------|---------|--------|-----|------|-----|---------------------------------|----------|

| Fait   | I Cache D Cache |         | 10BaseT | 10/100 | 300 | SINC | 036 |                                 | Engine   |

| MPC885 | 8               | 8       | Up to 3 | 2      | 3   | 2    | 1   | Serial ATM and UTOPIA interface | Yes      |

| MPC880 | 8               | 8       | Up to 2 | 2      | 2   | 2    | 1   | Serial ATM and UTOPIA interface | No       |

Table 1. MPC885 Family

# 2 Features

The MPC885/MPC880 is comprised of three modules that each use the 32-bit internal bus: a MPC8xx core, a system integration unit (SIU), and a communications processor module (CPM).

The following list summarizes the key MPC885/MPC880 features:

- Embedded MPC8xx core up to 133 MHz

- Maximum frequency operation of the external bus is 80 MHz (in 1:1 mode)

- The 133-MHz core frequency supports 2:1 mode only.

- The 66-/80-MHz core frequencies support both the 1:1 and 2:1 modes.

- Single-issue, 32-bit core (compatible with the Power Architecture definition) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch and without conditional execution.

- 8-Kbyte data cache and 8-Kbyte instruction cache (see Table 1)

- Instruction cache is two-way, set-associative with 256 sets in 2 blocks

- Data cache is two-way, set-associative with 256 sets

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully associative instruction and data TLBs

- MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip emulation debug mode

#### Thermal Calculation and Measurement

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_{J} = T_{B} + (R_{\theta JB} \times P_{D})$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)

$T_{B}$  = board temperature (°C)

$P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and vias attaching the thermal balls to the ground plane.

# 7.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two resistor model can be used with the thermal simulation of the application [2], or a more accurate and complex model of the package can be used in the thermal simulation.

# 7.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$\Psi_{JT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per the JESD51-2 specification published by JEDEC using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by the cooling effects of the thermocouple wire.

| Part Frequency | 66 I | MHz   | 80 MHz |     |  |

|----------------|------|-------|--------|-----|--|

| r art requency | Min  | Мах   | Min    | Max |  |

| Core frequency | 40   | 66.67 | 40     | 80  |  |

| Bus frequency  | 40   | 66.67 | 40     | 80  |  |

### Table 7. Frequency Ranges for Standard Part Frequencies (1:1 Bus Mode)

## Table 8. Frequency Ranges for Standard Part Frequencies (2:1 Bus Mode)

| Part Frequency | 66 I | MHz   | 80  | MHz | 133 MHz |         |  |

|----------------|------|-------|-----|-----|---------|---------|--|

| Fait inequency | Min  | Мах   | Min | Мах | Min     | Max 133 |  |

| Core frequency | 40   | 66.67 | 40  | 80  | 40      | 133     |  |

| Bus frequency  | 20   | 33.33 | 20  | 40  | 20      | 66      |  |

Table 9 provides the timings for the MPC885/MPC880 at 33-, 40-, 66-, and 80-MHz bus operation.

The timing for the MPC885/MPC880 bus shown assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays. CLKOUT assumes a 100-pF load for maximum delays and a 50-pF load for minimum delays.

| Num | Characteristic                                                                                                                                                                                                                                                                                                              | 33   | MHz  | 40 I | MHz  | 66 I | MHz  | 80 MHz |      | Unit |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|--------|------|------|

| Num |                                                                                                                                                                                                                                                                                                                             |      | Max  | Min  | Max  | Min  | Max  | Min    | Max  | Unit |

| B1  | Bus period (CLKOUT), see Table 7                                                                                                                                                                                                                                                                                            | _    | —    | —    | —    |      | _    | _      | —    | ns   |

| B1a | EXTCLK to CLKOUT phase skew - If CLKOUT is<br>an integer multiple of EXTCLK, then the rising<br>edge of EXTCLK is aligned with the rising edge of<br>CLKOUT. For a non-integer multiple of EXTCLK,<br>this synchronization is lost, and the rising edges of<br>EXTCLK and CLKOUT have a continuously<br>varying phase skew. | -2   | +2   | -2   | +2   | -2   | +2   | -2     | +2   | ns   |

| B1b | CLKOUT frequency jitter peak-to-peak                                                                                                                                                                                                                                                                                        | _    | 1    | _    | 1    | _    | 1    | _      | 1    | ns   |

| B1c | Frequency jitter on EXTCLK                                                                                                                                                                                                                                                                                                  | _    | 0.50 | _    | 0.50 | _    | 0.50 | _      | 0.50 | %    |

| B1d | CLKOUT phase jitter peak-to-peak for<br>OSCLK $\geq$ 15 MHz                                                                                                                                                                                                                                                                 | —    | 4    | —    | 4    | _    | 4    | _      | 4    | ns   |

|     | CLKOUT phase jitter peak-to-peak for<br>OSCLK < 15 MHz                                                                                                                                                                                                                                                                      | —    | 5    | —    | 5    | _    | 5    | _      | 5    | ns   |

| B2  | CLKOUT pulse width low (MIN = $0.4 \times B1$ ,<br>MAX = $0.6 \times B1$ )                                                                                                                                                                                                                                                  | 12.1 | 18.2 | 10.0 | 15.0 | 6.1  | 9.1  | 5.0    | 7.5  | ns   |

| B3  | CLKOUT pulse width high (MIN = $0.4 \times B1$ ,<br>MAX = $0.6 \times B1$ )                                                                                                                                                                                                                                                 | 12.1 | 18.2 | 10.0 | 15.0 | 6.1  | 9.1  | 5.0    | 7.5  | ns   |

| B4  | CLKOUT rise time                                                                                                                                                                                                                                                                                                            | —    | 4.00 | —    | 4.00 |      | 4.00 |        | 4.00 | ns   |

#### **Table 9. Bus Operation Timings**

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                               | 33   | MHz   | 40   | MHz   | 66 I | MHz   | 80 MHz |       | Unit |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                               | Min  | Мах   | Min  | Мах   | Min  | Мах   | Min    | Мах   | Unit |

| B5   | CLKOUT fall time                                                                                                                                             | _    | 4.00  | _    | 4.00  | _    | 4.00  | _      | 4.00  | ns   |

| B7   | CLKOUT to A(0:31), BADDR(28:30), RD/ $\overline{WR}$ ,<br>BURST, D(0:31) output hold (MIN = 0.25 × B1)                                                       | 7.60 | —     | 6.30 |       | 3.80 | _     | 3.13   | —     | ns   |

| B7a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , $\overline{\text{BDIP}}$ , PTR output hold (MIN = 0.25 × B1)                        | 7.60 |       | 6.30 |       | 3.80 |       | 3.13   | _     | ns   |

| B7b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , FRZ, VFLS(0:1), VF(0:2)<br>IWP(0:2), LWP(0:1), $\overline{STS}$ output hold<br>(MIN = 0.25 × B1)               | 7.60 | —     | 6.30 | _     | 3.80 | —     | 3.13   | —     | ns   |

| B8   | CLKOUT to A(0:31), BADDR(28:30) RD/ $\overline{WR}$ ,<br>BURST, D(0:31) valid (MAX = 0.25 × B1 + 6.3)                                                        | —    | 13.80 | _    | 12.50 | _    | 10.00 | —      | 9.43  | ns   |

| B8a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , AT(0:3) $\overline{\text{BDIP}}$ ,<br>PTR valid (MAX = 0.25 × B1 + 6.3)             | —    | 13.80 |      | 12.50 |      | 10.00 | —      | 9.43  | ns   |

| B8b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1), VF(0:2),<br>IWP(0:2), FRZ, LWP(0:1), $\overline{STS}$ valid <sup>4</sup><br>(MAX = 0.25 × B1 + 6.3) | _    | 13.80 | _    | 12.50 | _    | 10.00 | _      | 9.43  | ns   |

| B9   | CLKOUT to A(0:31), BADDR(28:30), RD/WR,<br>BURST, D(0:31), TSIZ(0:1), REG, RSV, AT(0:3),<br>PTR High-Z (MAX = 0.25 × B1 + 6.3)                               | 7.60 | 13.80 | 6.30 | 12.50 | 3.80 | 10.00 | 3.13   | 9.43  | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion<br>(MAX = 0.25 × B1 + 6.0)                                                                             | 7.60 | 13.60 | 6.30 | 12.30 | 3.80 | 9.80  | 3.13   | 9.13  | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion (when driven by the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.30^{1}$ )     | 2.50 | 9.30  | 2.50 | 9.30  | 2.50 | 9.30  | 2.50   | 9.30  | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation<br>(MAX = 0.25 × B1 + 4.8)                                                                              | 7.60 | 12.30 | 6.30 | 11.00 | 3.80 | 8.50  | 3.13   | 7.92  | ns   |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when driven by the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.00$ )          | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00  | 2.5    | 9.00  | ns   |

| B13  | CLKOUT to $\overline{\text{TS}}$ , $\overline{\text{BB}}$ High-Z (MIN = 0.25 × B1)                                                                           | 7.60 | 21.60 | 6.30 | 20.30 | 3.80 | 14.00 | 3.13   | 12.93 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven by the memory controller or PCMCIA interface)<br>(MIN = 0.00 × B1 + 2.5)                     | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00 | 2.5    | 15.00 | ns   |

| B14  | CLKOUT to $\overline{\text{TEA}}$ assertion<br>(MAX = 0.00 × B1 + 9.00)                                                                                      | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00  | 2.50   | 9.00  | ns   |

| B15  | CLKOUT to TEA High-Z (MIN = $0.00 \times B1 + 2.50$ )                                                                                                        | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00 | 2.50   | 15.00 | ns   |

| B16  | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 × B1 + 6.00)                                                     | 6.00 | _     | 6.00 | _     | 6.00 | _     | 6      | _     | ns   |

| B16a | TEA, $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid to CLKOUT (setup time) (MIN = 0.00 × B1 + 4.5)                        | 4.50 | _     | 4.50 | _     | 4.50 | _     | 4.50   | _     | ns   |

# Table 9. Bus Operation Timings (continued)

| Num  | Characteristic                                                                                                                         | 33    | MHz   | 40 I  | MHz   | 66 I  | MHz   | 80 MHz |       | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                         | Min   | Мах   | Min   | Мах   | Min   | Max   | Min    | Мах   | Unit |

| B16b | $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ , valid to CLKOUT (setup time) <sup>2</sup><br>(4MIN = 0.00 × B1 + 0.00)           | 4.00  | —     | 4.00  | _     | 4.00  | —     | 4.00   | _     | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time) (MIN = $0.00 \times B1 + 1.00^3$ )                                                 | 1.00  |       | 1.00  |       | 2.00  | _     | 2.00   |       | ns   |

| B17a | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00)    | 2.00  | —     | 2.00  | -     | 2.00  | —     | 2.00   |       | ns   |

| B18  | D(0:31) valid to CLKOUT rising edge (setup time) <sup>4</sup> (MIN = $0.00 \times B1 + 6.00$ )                                         | 6.00  | —     | 6.00  | _     | 6.00  | —     | 6.00   | _     | ns   |

| B19  | CLKOUT rising edge to D(0:31) valid (hold time) <sup>4</sup> (MIN = $0.00 \times B1 + 1.00^5$ )                                        | 1.00  | —     | 1.00  |       | 2.00  | —     | 2.00   |       | ns   |

| B20  | D(0:31) valid to CLKOUT falling edge (setup time) <sup>6</sup> (MIN = $0.00 \times B1 + 4.00$ )                                        | 4.00  | —     | 4.00  |       | 4.00  | _     | 4.00   |       | ns   |

| B21  | CLKOUT falling edge to D(0:31) valid (hold time) <sup>6</sup> (MIN = $0.00 \times B1 + 2.00$ )                                         | 2.00  | —     | 2.00  |       | 2.00  | —     | 2.00   |       | ns   |

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted GPCM<br>ACS = 00 (MAX = 0.25 × B1 + 6.3)                                                | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13   | 9.43  | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = [0 or 1]<br>(MAX = 0.00 × B1 + 8.00)                          |       | 8.00  |       | 8.00  | _     | 8.00  | _      | 8.00  | ns   |

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = [0 or 1], EBDF = 0<br>(MAX = 0.25 × B1 + 6.3)                 | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13   | 9.43  | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = [0 or 1], EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                | 10.90 | 18.00 | 10.90 | 16.00 | 5.20  | 12.30 | 4.69   | 10.93 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated GPCM read<br>access, GPCM write access ACS = 00 and CSNT<br>= 0 (MAX = 0.00 × B1 + 8.00) | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | 2.00   | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0<br>(MIN = $0.25 \times B1 - 2.00$ )                    | 5.60  |       | 4.30  |       | 1.80  |       | 1.13   |       | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 11 TRLX = 0<br>(MIN = 0.50 × B1 - 2.00)                             | 13.20 |       | 10.50 |       | 5.60  | _     | 4.25   |       | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}$ (0:3) asserted<br>(MAX = 0.00 × B1 + 9.00)                                     | _     | 9.00  | —     | 9.00  | —     | 9.00  | —      | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated<br>(MAX = 0.00 × B1 + 9.00)                                                              | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | 2.00   | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 1<br>(MIN = $1.25 \times B1 - 2.00$ )                    | 35.90 |       | 29.30 |       | 16.90 |       | 13.60  |       | ns   |

# Table 9. Bus Operation Timings (continued)

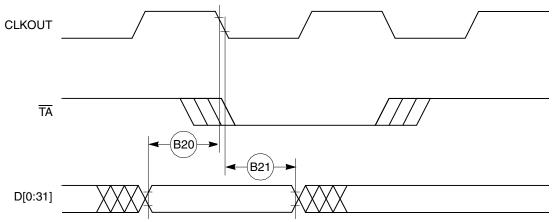

Figure 12 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 12. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

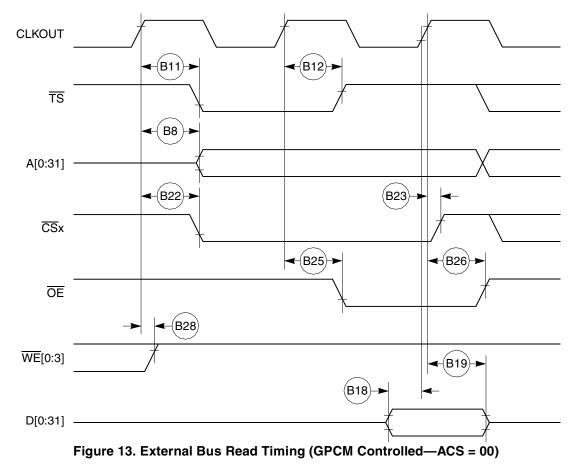

Figure 13 through Figure 16 provide the timing for the external bus read controlled by various GPCM factors.

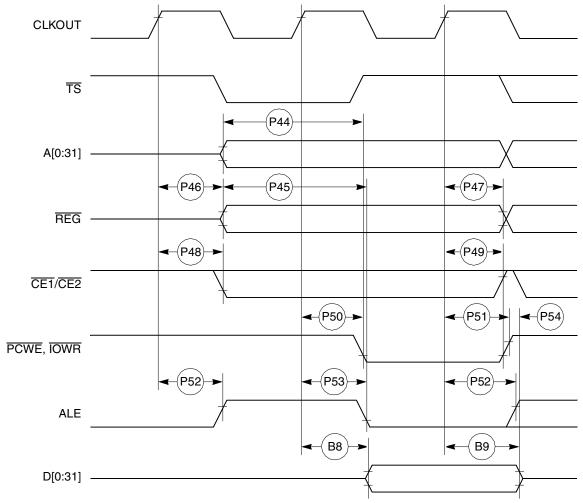

Table 11 shows the PCMCIA timing for the MPC885/MPC880.

| Num | Characteristic                                                                                                                   | 33    | MHz   | 40    | MHz   | 66 I  | MHz   | 80 MHz |       | Unit |

|-----|----------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num | Characteristic                                                                                                                   | Min   | Max   | Min   | Max   | Min   | Max   | Min    | Max   | Unit |

| P44 | A(0:31), $\overline{\text{REG}}$ valid to PCMCIA strobe<br>asserted <sup>1</sup> (MIN = 0.75 × B1 – 2.00)                        | 20.70 | _     | 16.70 | —     | 9.40  | _     | 7.40   |       | ns   |

| P45 | A(0:31), $\overline{\text{REG}}$ valid to ALE negation <sup>1</sup><br>(MIN = 1.00 × B1 – 2.00)                                  | 28.30 | _     | 23.00 | _     | 13.20 | _     | 10.50  |       | ns   |

| P46 | CLKOUT to $\overline{\text{REG}}$ valid<br>(MAX = 0.25 × B1 + 8.00)                                                              | 7.60  | 15.60 | 6.30  | 14.30 | 3.80  | 11.80 | 3.13   | 11.13 | ns   |

| P47 | CLKOUT to REG invalid<br>(MIN = 0.25 - B1 + 1.00)                                                                                | 8.60  | —     | 7.30  | —     | 4.80  | _     | 4.13   | —     | ns   |

| P48 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ asserted<br>(MAX = 0.25 × B1 + 8.00)                                               | 7.60  | 15.60 | 6.30  | 14.30 | 3.80  | 11.80 | 3.13   | 11.13 | ns   |

| P49 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ negated<br>(MAX = 0.25 × B1 + 8.00)                                                | 7.60  | 15.60 | 6.30  | 14.30 | 3.80  | 11.80 | 3.13   | 11.13 | ns   |

| P50 | CLKOUT to $\overline{PCOE}$ , $\overline{IORD}$ , $\overline{PCWE}$ , $\overline{IOWR}$<br>assert time (MAX = 0.00 × B1 + 11.00) | _     | 11.00 | —     | 11.00 | _     | 11.00 | _      | 11.00 | ns   |

| P51 | CLKOUT to $\overline{PCOE}$ , $\overline{IORD}$ , $\overline{PCWE}$ , $\overline{IOWR}$<br>negate time (MAX = 0.00 × B1 + 11.00) | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | 2.00   | 11.00 | ns   |

| P52 | CLKOUT to ALE assert time (MAX = $0.25 \times B1 + 6.30$ )                                                                       | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13   | 9.40  | ns   |

| P53 | CLKOUT to ALE negate time (MAX = $0.25 \times B1 + 8.00$ )                                                                       | _     | 15.60 | —     | 14.30 | _     | 11.80 |        | 11.13 | ns   |

| P54 | PCWE, IOWR negated to D(0:31) invalid 1(MIN = $0.25 \times B1 - 2.00)$                                                           | 5.60  | —     | 4.30  | —     | 1.80  | —     | 1.13   | _     | ns   |

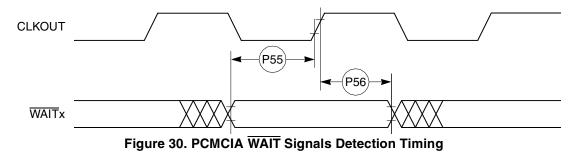

| P55 | $\overline{\text{WAITA}}$ and $\overline{\text{WAITB}}$ valid to CLKOUT rising edge <sup>1</sup> (MIN = 0.00 × B1 + 8.00)        | 8.00  | _     | 8.00  | —     | 8.00  | _     | 8.00   | _     | ns   |

| P56 | CLKOUT rising edge to $\overline{\text{WAITA}}$ and $\overline{\text{WAITB}}$ invalid <sup>1</sup> (MIN = 0.00 × B1 + 2.00)      | 2.00  | —     | 2.00  | —     | 2.00  | —     | 2.00   | —     | ns   |

PSST = 1. Otherwise add PSST times cycle time.

PSHT = 0. Otherwise add PSHT times cycle time.

These synchronous timings define when the WAITx signals are detected in order to freeze (or relieve) the PCMCIA current cycle. The WAITx assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See Chapter 16, "PCMCIA Interface," in the MPC885 PowerQUICC™ Family Reference Manual.

1

Figure 29 provides the PCMCIA access cycle timing for the external bus write.

Figure 29. PCMCIA Access Cycles Timing External Bus Write

Figure 30 provides the PCMCIA  $\overline{WAIT}$  signals detection timing.

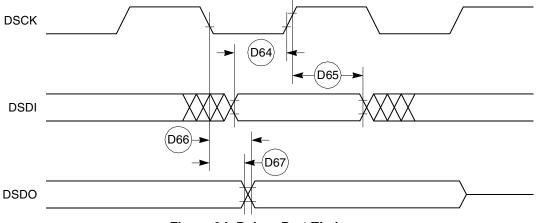

Table 13 shows the debug port timing for the MPC885/MPC880.

# Table 13. Debug Port Timing

| Num   | Characteristic              | All Frequer                | Unit  |      |

|-------|-----------------------------|----------------------------|-------|------|

| Nulli | Characteristic              | Min                        | Мах   | Unit |

| D61   | DSCK cycle time             | 3 × T <sub>CLOCKOUT</sub>  |       | _    |

| D62   | DSCK clock pulse width      | $1.25 \times T_{CLOCKOUT}$ | _     | —    |

| D63   | DSCK rise and fall times    | 0.00                       | 3.00  | ns   |

| D64   | DSDI input data setup time  | 8.00                       | _     | ns   |

| D65   | DSDI data hold time         | 5.00                       | _     | ns   |

| D66   | DSCK low to DSDO data valid | 0.00                       | 15.00 | ns   |

| D67   | DSCK low to DSDO invalid    | 0.00                       | 2.00  | ns   |

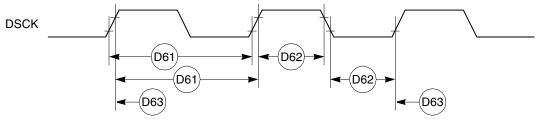

Figure 33 provides the input timing for the debug port clock.

Figure 33. Debug Port Clock Input Timing

Figure 34 provides the timing for the debug port.

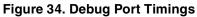

Figure 35 shows the reset timing for the data bus configuration.

Figure 35. Reset Timing—Configuration from Data Bus

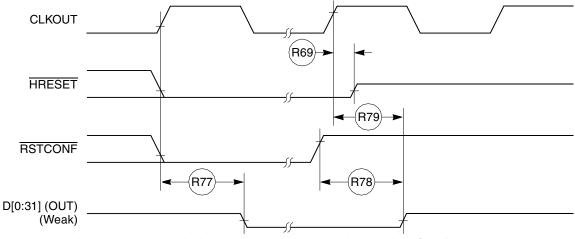

Figure 36 provides the reset timing for the data bus weak drive during configuration.

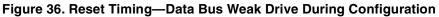

Figure 37 provides the reset timing for the debug port configuration.

IEEE 1149.1 Electrical Specifications

# 11 IEEE 1149.1 Electrical Specifications

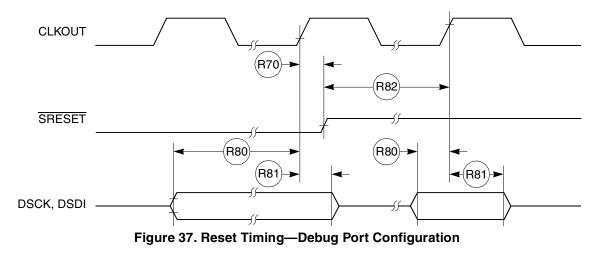

Table 15 provides the JTAG timings for the MPC885/MPC880 shown in Figure 38 through Figure 41.

# Table 15. JTAG Timing

| Num | Characteristic                                         | All Freq | uencies | l lucit |

|-----|--------------------------------------------------------|----------|---------|---------|

| Num | Characteristic                                         | Min      | Max     | Unit    |

| J82 | TCK cycle time                                         | 100.00   |         | ns      |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00    |         | ns      |

| J84 | TCK rise and fall times                                | 0.00     | 10.00   | ns      |

| J85 | TMS, TDI data setup time                               | 5.00     | _       | ns      |

| J86 | TMS, TDI data hold time                                | 25.00    | _       | ns      |

| J87 | TCK low to TDO data valid                              | —        | 27.00   | ns      |

| J88 | TCK low to TDO data invalid                            | 0.00     | _       | ns      |

| J89 | TCK low to TDO high impedance                          | _        | 20.00   | ns      |

| J90 | TRST assert time                                       | 100.00   | _       | ns      |

| J91 | TRST setup time to TCK low                             | 40.00    | _       | ns      |

| J92 | TCK falling edge to output valid                       | _        | 50.00   | ns      |

| J93 | TCK falling edge to output valid out of high impedance | _        | 50.00   | ns      |

| J94 | TCK falling edge to output high impedance              | _        | 50.00   | ns      |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00    | _       | ns      |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00    |         | ns      |

Figure 38. JTAG Test Clock Input Timing

**CPM Electrical Characteristics**

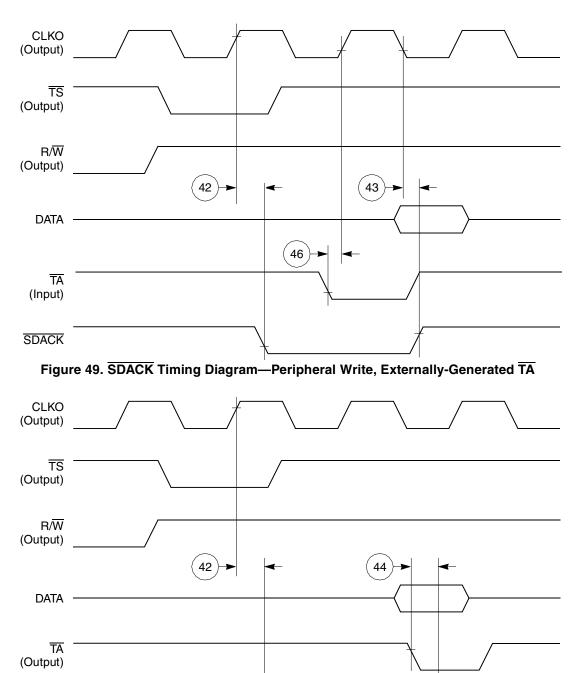

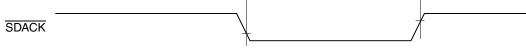

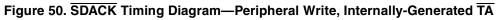

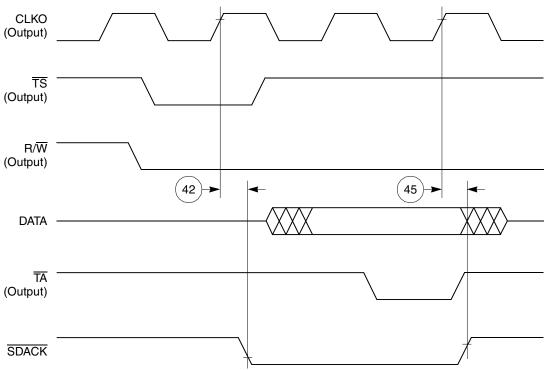

Figure 51. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

# 12.4 Baud Rate Generator AC Electrical Specifications

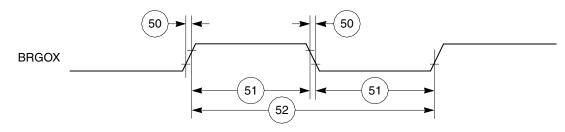

Table 19 provides the baud rate generator timings as shown in Figure 52.

| Num Characteristic |                         | All Frequencies |     | Unit |

|--------------------|-------------------------|-----------------|-----|------|

| Num                |                         |                 | Мах | Unit |

| 50                 | BRGO rise and fall time |                 | 10  | ns   |

| 51                 | BRGO duty cycle         |                 | 60  | %    |

| 52                 | BRGO cycle              |                 | —   | ns   |

Figure 52. Baud Rate Generator Timing Diagram

**CPM Electrical Characteristics**

#### SCC in NMSI Mode Electrical Specifications 12.7

Table 22 provides the NMSI external clock timing.

| Num   | Characteristic                                       | All Frequencies |       | Unit |

|-------|------------------------------------------------------|-----------------|-------|------|

| Nulli | Characteristic                                       | Min             | Мах   | Unit |

| 100   | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK       | _     | ns   |

| 101   | RCLK1 and TCLK1 width low                            | 1/SYNCCLK + 5   | _     | ns   |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —               | 15.00 | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00            | 50.00 | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00            | 50.00 | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 5.00            | _     | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 5.00            | —     | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00            | —     | ns   |

| 108   | CD1 setup time to RCLK1 rising edge                  | 5.00            | —     | ns   |

### Table 22. NMSI External Clock Timing

The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

Also applies to CD and CTS hold time when they are used as external sync signals.

## Table 23 provides the NMSI internal clock timing.

# Table 23. NMSI Internal Clock Timing

| Num   | Characteristic                                       | All Frequencies |           | Unit |  |

|-------|------------------------------------------------------|-----------------|-----------|------|--|

| Nulli |                                                      | Min             |           | Onit |  |

| 100   | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00            | SYNCCLK/3 | MHz  |  |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —               | —         | ns   |  |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00            | 30.00     | ns   |  |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00            | 30.00     | ns   |  |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 40.00           | —         | ns   |  |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 40.00           | —         | ns   |  |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00            | —         | ns   |  |

| 108   | CD1 setup time to RCLK1 rising edge                  | 40.00           | —         | ns   |  |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{CD}$  and  $\overline{CTS}$  hold time when they are used as external sync signals

**CPM Electrical Characteristics**

Figure 65. SMC Transparent Timing Diagram

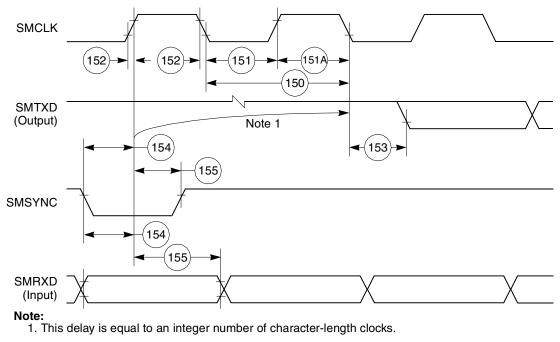

# 12.10 SPI Master AC Electrical Specifications

Table 26 provides the SPI master timings as shown in Figure 66 and Figure 67.

| Num | Characteristic                         | All Frequencies |      | Unit             |

|-----|----------------------------------------|-----------------|------|------------------|

| Num | Cildracteristic                        | Min             |      |                  |

| 160 | MASTER cycle time                      | 4               | 1024 | t <sub>cyc</sub> |

| 161 | MASTER clock (SCK) high or low time    | 2 512           |      | t <sub>cyc</sub> |

| 162 | 2 MASTER data setup time (inputs) 15 — |                 | —    | ns               |

| 163 | Master data hold time (inputs)         | 0               | —    | ns               |

| 164 | Master data valid (after SCK edge)     | — 10            |      | ns               |

| 165 | Master data hold time (outputs)        | 0               | —    | ns               |

| 166 | Rise time output                       | —               | 15   | ns               |

| 167 | Fall time output—15                    |                 | 15   | ns               |

| Table 39. | Pin | Assignments | (continued) |

|-----------|-----|-------------|-------------|

|-----------|-----|-------------|-------------|

| Name                                                       | Pin Number         | Туре                      |

|------------------------------------------------------------|--------------------|---------------------------|

| WE0, BS_B0, IORD                                           | B18                | Output                    |

| WE1, BS_B1, IOWR                                           | E16                | Output                    |

| WE2, BS_B2, PCOE                                           | C17                | Output                    |

| WE3, BS_B3, PCWE                                           | B19                | Output                    |

| BS_A[0:3]                                                  | D17, C18, C19, F16 | Output                    |

| GPL_A0, GPL_B0                                             | B17                | Output                    |

| OE, GPL_A1, GPL_B1                                         | A18                | Output                    |

| <u>GPL_A</u> [2:3], <u>GPL_B</u> [2:3],<br><u>CS</u> [2:3] | D16, A17           | Output                    |

| UPWAITA, GPL_A4                                            | B13                | Bidirectional             |

| UPWAITB, GPL_B4                                            | A14                | Bidirectional             |

| GPL_A5                                                     | C13                | Output                    |

| PORESET                                                    | B3                 | Input                     |

| RSTCONF                                                    | D4                 | Input                     |

| HRESET                                                     | B4                 | Open-drain                |

| SRESET                                                     | A3                 | Open-drain                |

| XTAL                                                       | A4                 | Analog output             |

| EXTAL                                                      | D5                 | Analog input (3.3 V only) |

| CLKOUT                                                     | G4                 | Output                    |

| EXTCLK                                                     | A5                 | Input (3.3 V only)        |

| TEXP                                                       | C4                 | Output                    |

| ALE_A                                                      | B7                 | Output                    |

| CE1_A                                                      | B15                | Output                    |

| CE2_A                                                      | C15                | Output                    |

| WAIT_A, SOC_Split <sup>1</sup>                             | A2                 | Input                     |

| WAIT_B                                                     | C3                 | Input                     |

| IP_A0, UTPB_Split0 <sup>1</sup>                            | B1                 | Input                     |

| IP_A1, UTPB_Split1 <sup>1</sup>                            | C1                 | Input                     |

| IP_A2, IOIS16_A,<br>UTPB_Split2 <sup>1</sup>               | F4                 | Input                     |

| IP_A3, UTPB_Split3 <sup>1</sup>                            | E3                 | Input                     |

| IP_A4, UTPB_Split4 <sup>1</sup>                            | D2                 | Input                     |

| IP_A5, UTPB_Split5 <sup>1</sup>                            | D1                 | Input                     |

| IP_A6, UTPB_Split6 <sup>1</sup>                            | E2                 | Input                     |

| IP_A7, UTPB_Split7 <sup>1</sup>                            | D3                 | Input                     |

# Table 39. Pin Assignments (continued)

| Name                                 | Pin Number | Туре                                    |

|--------------------------------------|------------|-----------------------------------------|

| ALE_B, DSCK/AT1                      | D8         | Bidirectional<br>Three-state            |

| IP_B[0:1], IWP[0:1],<br>VFLS[0:1]    | A9, D9     | Bidirectional                           |

| IP_B2, IOIS16_B, AT2                 | C8         | Bidirectional<br>Three-state            |

| IP_B3, IWP2, VF2                     | C9         | Bidirectional                           |

| IP_B4, LWP0, VF0                     | В9         | Bidirectional                           |

| IP_B5, LWP1, VF1                     | A10        | Bidirectional                           |

| IP_B6, DSDI, AT0                     | A8         | Bidirectional<br>Three-state            |

| IP_B7, PTR, AT3                      | B8         | Bidirectional<br>Three-state            |

| OP0, UtpClk_Split <sup>1</sup>       | B6         | Bidirectional                           |

| OP1                                  | C6         | Output                                  |

| OP2, MODCK1, STS                     | D6         | Bidirectional                           |

| OP3, MODCK2, DSDO                    | A6         | Bidirectional                           |

| BADDR30, REG                         | A7         | Output                                  |

| BADDR[28:29]                         | C5, B5     | Output                                  |

| ĀS                                   | D7         | Input                                   |

| PA15, USBRXD                         | N16        | Bidirectional                           |

| PA14, USBOE                          | P17        | Bidirectional<br>(Optional: open-drain) |

| PA13, RXD2                           | W11        | Bidirectional                           |

| PA12, TXD2                           | P16        | Bidirectional<br>(Optional: open-drain) |

| PA11, RXD4, MII1-TXD0, W9 Bidirec    |            | Bidirectional<br>(Optional: open-drain) |

| PA10, MII1-TXER, TIN4,<br>CLK7       | W17        | Bidirectional<br>(Optional: open-drain) |

| PA9, L1TXDA, RXD3                    | T15        | Bidirectional<br>(Optional: open-drain) |

| PA8, L1RXDA, TXD3                    | W15        | Bidirectional<br>(Optional: open-drain) |

| PA7, CLK1, L1RCLKA,<br>BRGO1, TIN1   | V14        | Bidirectional                           |

| PA6, CLK2, TOUT1                     | U13        | Bidirectional                           |

| PA5, CLK3, L1TCLKA, W13 Bidirectiona |            | Bidirectional                           |

| Name                                 | Pin Number                                                                                                                                                                                                                                                          | Туре                               |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| PE14, RXD3, MII2-TXD0,<br>RMII2-TXD0 | V7                                                                                                                                                                                                                                                                  | Bidirectional                      |

| TMS                                  | V18                                                                                                                                                                                                                                                                 | Input                              |

| TDI, DSDI                            | T16                                                                                                                                                                                                                                                                 | Input                              |

| TCK, DSCK                            | U17                                                                                                                                                                                                                                                                 | Input                              |

| TRST                                 | W18                                                                                                                                                                                                                                                                 | Input                              |

| TDO, DSDO                            | T17                                                                                                                                                                                                                                                                 | Output                             |

| MII1_CRS                             | T11                                                                                                                                                                                                                                                                 | Input                              |

| MII_MDIO                             | P19                                                                                                                                                                                                                                                                 | Bidirectional                      |

| MII1_TXEN, RMII1_TXEN                | Т5                                                                                                                                                                                                                                                                  | Output                             |

| MII1_COL                             | U12                                                                                                                                                                                                                                                                 | Input                              |

| V <sub>SSSYN1</sub>                  | C2                                                                                                                                                                                                                                                                  | PLL analog V <sub>DD</sub> and GND |

| V <sub>SSSYN</sub>                   | E4                                                                                                                                                                                                                                                                  | Power                              |

| V <sub>DDLSYN</sub>                  | B2                                                                                                                                                                                                                                                                  | Power                              |

| GND                                  | G6, G7, G8, G9, G10, G11, G12, G13, H7, H8, H9, H10, H11, H12,<br>H13, H14, J7, J8, J9, J10, J11, J12, J13, K7, K8, K9, K10, K11, K12,<br>K13, L7, L8, L9, L10, L11, L12, L13, M7, M8, M9, M10, M11, M12,<br>M13, N7, N8, N9, N10, N11, N12, N13, N14, P7, P13, R16 | Power                              |

| V <sub>DDL</sub>                     | E5, E6, E9, E11, E14, G15, H5, J5, J15, K15, L5, M15, N5, R6, R9, R10, R12, R15                                                                                                                                                                                     | Power                              |

| V <sub>DDH</sub>                     | E7, E8, E10, E12, E13, E15, F5, F6, F7, F8, F9, F10, F11, F12, F13, F14, F15, G5, G14, H6, H15, J6, J14, K5, K6, K14, L6, L14, L15, M5, M6, M14, N6, N15, P5, P6, P8, P9, P10, P11, P12, P14, P15, R5, R7, R8, R11, R13, R14                                        | Power                              |

| N/C                                  | N17                                                                                                                                                                                                                                                                 | No connect                         |

# Table 39. Pin Assignments (continued)

<sup>1</sup> ESAR mode only.

# **17 Document Revision History**

Table 40 lists significant changes between revisions of this hardware specification.

| Revision<br>Number | Date      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                  | 07/2010   | <ul> <li>In Table 9, "Bus Operation Timings," changed the following:</li> <li>Updated TRLX condition value for B22a/b/c to "TRLX = [0 or 1]"</li> <li>Removed TRLX condition for B23</li> <li>Updated condition and equation for B30 to "Invalid GPCM read/write access (MIN = 0.25 × B1 - 2.00)"</li> <li>Updated note 8 to "The timing B30 refers to CS when ACS = 00 and to CS and WE(0:3) when CSNT = 0."</li> </ul>                                                                                                                                                   |

| 6                  | 05/2010   | Added minimum load for CLKOUT in Section 10, "Bus Signal Timing."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5                  | 03/2009   | Updated formatting of Table 12, "PCMCIA Port Timing," Table 13, "Debug Port Timing," Table 14, "Reset Timing," and Table 15, "JTAG Timing."                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4                  | 08/2007   | <ul> <li>On page 1, updated first paragraph and added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 3) and renumbered the rest of the figures.</li> <li>In Table 9, for reset timings B29f and B29g added footnote indicating that the formula only applies to bus operation up to 50 MHz.</li> <li>In Figure 6, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 18, changed num 46 description to read, "TA assertion to rising edge"</li> </ul> |

| 3.0                | 7/22/2004 | <ul> <li>Added sentence to Spec B1A about EXTCLK and CLKOUT being in Alignment for Integer Values</li> <li>Added a footnote to Spec 41 specifying that EDM = 1</li> <li>Added RMII1_EN under M1II_EN in Table 36 Pin Assignments</li> <li>Added a tablefootnote to Table 6 DC Electrical Specifications about meeting the VIL Max of the I2C Standard</li> <li>Put the new part numbers in the Ordering Information Section</li> </ul>                                                                                                                                     |

| 2.0                | 12/2003   | <ul> <li>Changed the maximum operating frequency to 133 MHz.</li> <li>Put in the orderable part numbers that are orderable.</li> <li>Put the timing in the 80 MHz column.</li> <li>Rounded the timings to hundredths in the 80 MHz column.</li> <li>Put the pin numbers in footnotes by the maximum currents in Table 6.</li> <li>Changed 22 and 41 in the Timing.</li> <li>Put in the Thermal numbers.</li> </ul>                                                                                                                                                         |

| 1.0                | 9/2003    | <ul> <li>Added the DSP information in the Features list</li> <li>Fixed table formatting.</li> <li>Nontechnical edits.</li> <li>Released to the external web.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.9                | 8/2003    | Changed the USB description to full-/low-speed compatible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.8                | 8/2003    | Added the Reference to USB 2.0 to the Features list and removed 1.1 from USB on the block diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0.7                | 7/2003    | Added the RxClav and TxClav signals to PC15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0.6                | 6/2003    | Changed the pin descriptions per the June 22 spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.5                | 5/2003    | Changed some more typos, put in the phsel and phreq pins. Corrected the USB timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# Table 40. Document Revision History