#### NXP USA Inc. - KMPC885ZP80 Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                            |

|---------------------------------|---------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                      |

| Speed                           | 80MHz                                                               |

| Co-Processors/DSP               | Communications; CPM, Security; SEC                                  |

| RAM Controllers                 | DRAM                                                                |

| Graphics Acceleration           | No                                                                  |

| Display & Interface Controllers | · .                                                                 |

| Ethernet                        | 10Mbps (3), 10/100Mbps (2)                                          |

| SATA                            | · .                                                                 |

| USB                             | USB 2.0 (1)                                                         |

| Voltage - I/O                   | 3.3V                                                                |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                     |

| Security Features               | Cryptography                                                        |

| Package / Case                  | 357-BBGA                                                            |

| Supplier Device Package         | 357-PBGA (25x25)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc885zp80 |

|                                 |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Provides enhanced ATM functionality found on the MPC862 and MPC866 families and includes the following:

- Improved operation, administration and maintenance (OAM) support

- OAM performance monitoring (PM) support

- Multiple APC priority levels available to support a range of traffic pace requirements

- Port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (100BaseT) and UTOPIA (half- or full -duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA L2-compliant interface with added FIFO buffering to reduce the total cell transmission time and multi-PHY support. (The earlier UTOPIA L1 specification is also supported.)

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA master (ATM side) and slave (PHY side) operations using a split bus

- AAL2/VBR functionality is ROM-resident

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to DRAM, SIMMS, SRAM, EPROMs, Flash EPROMs, and other memory devices

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Gate mode can enable/disable counting.

- Interrupt can be masked on reference match and event capture

- Two fast Ethernet controllers (FEC)—Two 10/100 Mbps Ethernet/IEEE Std. 802.3<sup>™</sup> CDMA/CS that interface through MII and/or RMII interfaces

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- On-chip  $16 \times 16$  multiply accumulate controller (MAC)

- One operation per clock (two-clock latency, one-clock blockage)

- MAC operates concurrently with other instructions

- FIR loop—Four clocks per four multiplies

- Four baud rate generators

- Independent (can be connected to any SCC or SMC)

- Allow changes during operation

- Autobaud support option

- Up to three serial communication controllers (SCCs) supporting the following protocols:

- Serial ATM capability on SCCs

- Optional UTOPIA port on SCC4

- Ethernet/IEEE Std 802.3<sup>™</sup> optional on the SCC(s) supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support point-to-point protocol (PPP)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

- Up to two serial management channels (SMCs) supporting the following protocols:

- UART (low-speed operation)

- Transparent

- General circuit interface (GCI) controller

- Provide management for BRI devices as GCI controller in time-division multiplexed (TDM) channels

- Universal serial bus (USB)—Supports operation as a USB function endpoint, a USB host controller, or both for testing purposes (loop-back diagnostics)

- USB 2.0 full-/low-speed compatible

- The USB function mode has the following features:

- Four independent endpoints support control, bulk, interrupt, and isochronous data transfers.

- CRC16 generation and checking

- CRC5 checking

- NRZI encoding/decoding with bit stuffing

- 12- or 1.5-Mbps data rate

**Maximum Tolerated Ratings**

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC885/MPC880. Table 2 displays the maximum tolerated ratings, and Table 3 displays the operating temperatures.

| Rating                      | Symbol                                                                                                                                                                                                                                      | Value                         | Unit |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|

| Supply voltage <sup>1</sup> | V <sub>DDH</sub>                                                                                                                                                                                                                            | -0.3 to 4.0                   | V    |

|                             | V <sub>DDL</sub>                                                                                                                                                                                                                            | -0.3 to 2.0                   | V    |

|                             | V         V         -0.3 to 4.0           V         V         -0.3 to 2.0           VDDSYN         -0.3 to 2.0           Difference between V         -0.3 to 2.0           Vin         GND - 0.3 to V           Vin         GND - 0.3 to V | V                             |      |

|                             | Difference between $V_{\text{DDL}}$ and $V_{\text{DDSYN}}$                                                                                                                                                                                  | <100                          | mV   |

| Input voltage <sup>2</sup>  | V <sub>in</sub>                                                                                                                                                                                                                             | GND – 0.3 to V <sub>DDH</sub> | V    |

| Storage temperature range   | T <sub>stg</sub>                                                                                                                                                                                                                            | -55 to +150                   | °C   |

#### Table 2. Maximum Tolerated Ratings

$^{1}\,$  The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device. See Section 8, "Power Supply and Power Sequencing." Caution: All inputs that tolerate 5 V cannot be more than 2.5 V greater than V<sub>DDH</sub>. This restriction applies to power up and normal operation (that is, if the MPC885/MPC880 is unpowered, a voltage greater than 2.5 V must not be applied to its inputs).

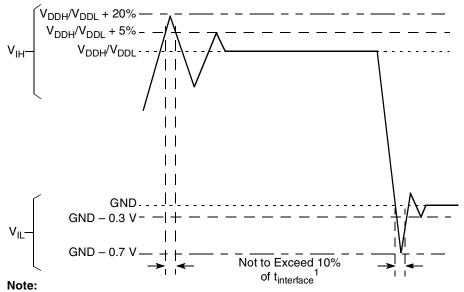

Figure 3 shows the undershoot and overshoot voltages at the interfaces of the MPC885/MPC880.

1. t<sub>interface</sub> refers to the clock period associated with the bus clock interface.

Figure 3. Undershoot/Overshoot Voltage for  $\rm V_{DDH}$  and  $\rm V_{DDL}$

## 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta IA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the airflow around the device, add a heat sink, change the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

## 7.3 Estimation with Junction-to-Board Thermal Resistance

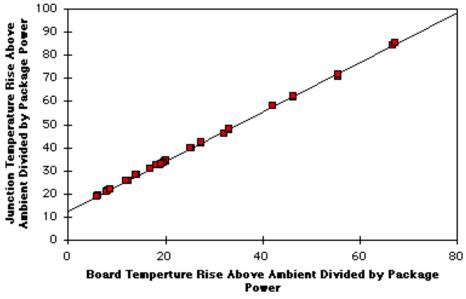

A simple package thermal model that has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed-circuit board. It has been observed that the thermal performance of most plastic packages and especially PBGA packages is strongly dependent on the board temperature; see Figure 4.

Figure 4. Effect of Board Temperature Rise on Thermal Behavior

V<sub>DDH</sub> V<sub>DDL</sub> MUR420 1N5820

Figure 5. Example Voltage Sequencing Circuit

# 9 Layout Practices

Each  $V_{DD}$  pin on the MPC885/MPC880 should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1 µF by-pass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and associated printed-circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC885/MPC880 have fast rise and fall times. Printed-circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{DD}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins. For more information, please refer to the *MPC885 PowerQUICC<sup>TM</sup> Family Reference Manual*, Section 14.4.3, "Clock Synthesizer Power ( $V_{DDSYN}$ ,  $V_{SSSYN}$ ,  $V_{SSSYN1}$ )."

# 10 Bus Signal Timing

The maximum bus speed supported by the MPC885/MPC880 is 80 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC885/MPC880 used at 133 MHz must be configured for a 66 MHz bus). Table 7 shows the frequency ranges for standard part frequencies in 1:1 bus mode, and Table 8 shows the frequency ranges for standard part frequencies in 2:1 bus mode.

| Part Frequency Core frequency | 66 I | MHz   | 80 MHz |     |  |

|-------------------------------|------|-------|--------|-----|--|

| r art requency                | Min  | Мах   | Min    | Max |  |

| Core frequency                | 40   | 66.67 | 40     | 80  |  |

| Bus frequency                 | 40   | 66.67 | 40     | 80  |  |

#### Table 7. Frequency Ranges for Standard Part Frequencies (1:1 Bus Mode)

#### Table 8. Frequency Ranges for Standard Part Frequencies (2:1 Bus Mode)

| Part Frequency | 66 I | MHz   | 80  | MHz | 133 MHz |     |  |

|----------------|------|-------|-----|-----|---------|-----|--|

| Fait inequency | Min  | Мах   | Min | Мах | Min     | Max |  |

| Core frequency | 40   | 66.67 | 40  | 80  | 40      | 133 |  |

| Bus frequency  | 20   | 33.33 | 20  | 40  | 20      | 66  |  |

Table 9 provides the timings for the MPC885/MPC880 at 33-, 40-, 66-, and 80-MHz bus operation.

The timing for the MPC885/MPC880 bus shown assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays. CLKOUT assumes a 100-pF load for maximum delays and a 50-pF load for minimum delays.

| Num | Characteristic                                                                                                                                                                                                                                                                                                              | 33   | MHz  | 40 I | MHz  | 66 I | MHz  | 80 I | MHz                                     | Unit |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|-----------------------------------------|------|

| Num | Characteristic                                                                                                                                                                                                                                                                                                              | Min  | Max  | Min  | Max  | Min  | Max  | Min  | HHZ Max +2 +2 0 1 0.50 4 5 7.5 7.5 4.00 | Unit |

| B1  | Bus period (CLKOUT), see Table 7                                                                                                                                                                                                                                                                                            | _    | —    | —    | —    |      | _    | _    | —                                       | ns   |

| B1a | EXTCLK to CLKOUT phase skew - If CLKOUT is<br>an integer multiple of EXTCLK, then the rising<br>edge of EXTCLK is aligned with the rising edge of<br>CLKOUT. For a non-integer multiple of EXTCLK,<br>this synchronization is lost, and the rising edges of<br>EXTCLK and CLKOUT have a continuously<br>varying phase skew. | -2   | +2   | -2   | +2   | -2   | +2   | -2   | +2                                      | ns   |

| B1b | CLKOUT frequency jitter peak-to-peak                                                                                                                                                                                                                                                                                        | _    | 1    | _    | 1    | _    | 1    | _    | 1                                       | ns   |

| B1c | Frequency jitter on EXTCLK                                                                                                                                                                                                                                                                                                  | _    | 0.50 | _    | 0.50 | _    | 0.50 | _    | 0.50                                    | %    |

| B1d | CLKOUT phase jitter peak-to-peak for<br>OSCLK $\geq$ 15 MHz                                                                                                                                                                                                                                                                 | —    | 4    | —    | 4    | _    | 4    | _    | 4                                       | ns   |

|     | CLKOUT phase jitter peak-to-peak for<br>OSCLK < 15 MHz                                                                                                                                                                                                                                                                      | —    | 5    | —    | 5    | _    | 5    | _    | 5                                       | ns   |

| B2  | CLKOUT pulse width low (MIN = $0.4 \times B1$ ,<br>MAX = $0.6 \times B1$ )                                                                                                                                                                                                                                                  | 12.1 | 18.2 | 10.0 | 15.0 | 6.1  | 9.1  | 5.0  | 7.5                                     | ns   |

| B3  | CLKOUT pulse width high (MIN = $0.4 \times B1$ ,<br>MAX = $0.6 \times B1$ )                                                                                                                                                                                                                                                 | 12.1 | 18.2 | 10.0 | 15.0 | 6.1  | 9.1  | 5.0  | 7.5                                     | ns   |

| B4  | CLKOUT rise time                                                                                                                                                                                                                                                                                                            | —    | 4.00 | —    | 4.00 |      | 4.00 |      | 4.00                                    | ns   |

#### **Table 9. Bus Operation Timings**

| Num  | Characteristic                                                                                                                         | 33    | MHz   | 40 I  | MHz   | 66 I  | MHz   | 80 MHz |       | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                         | Min   | Мах   | Min   | Мах   | Min   | Max   | Min    | Мах   | Unit |

| B16b | $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ , valid to CLKOUT (setup time) <sup>2</sup><br>(4MIN = 0.00 × B1 + 0.00)           | 4.00  | —     | 4.00  | _     | 4.00  | —     | 4.00   | _     | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time) (MIN = $0.00 \times B1 + 1.00^3$ )                                                 | 1.00  |       | 1.00  |       | 2.00  | _     | 2.00   |       | ns   |

| B17a | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time)<br>(MIN = 0.00 × B1 + 2.00)    | 2.00  | —     | 2.00  | -     | 2.00  | —     | 2.00   | -     | ns   |

| B18  | D(0:31) valid to CLKOUT rising edge (setup time) <sup>4</sup> (MIN = $0.00 \times B1 + 6.00$ )                                         | 6.00  | —     | 6.00  | _     | 6.00  | —     | 6.00   | _     | ns   |

| B19  | CLKOUT rising edge to D(0:31) valid (hold time) <sup>4</sup> (MIN = $0.00 \times B1 + 1.00^5$ )                                        | 1.00  | —     | 1.00  | -     | 2.00  | —     | 2.00   |       | ns   |

| B20  | D(0:31) valid to CLKOUT falling edge (setup time) <sup>6</sup> (MIN = $0.00 \times B1 + 4.00$ )                                        | 4.00  | —     | 4.00  |       | 4.00  | _     | 4.00   |       | ns   |

| B21  | CLKOUT falling edge to D(0:31) valid (hold time) <sup>6</sup> (MIN = $0.00 \times B1 + 2.00$ )                                         | 2.00  | —     | 2.00  |       | 2.00  | —     | 2.00   |       | ns   |

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted GPCM<br>ACS = 00 (MAX = 0.25 × B1 + 6.3)                                                | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13   | 9.43  | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = [0 or 1]<br>(MAX = 0.00 × B1 + 8.00)                          |       | 8.00  |       | 8.00  | _     | 8.00  | _      | 8.00  | ns   |

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = [0 or 1], EBDF = 0<br>(MAX = 0.25 × B1 + 6.3)                 | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13   | 9.43  | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = [0 or 1], EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                | 10.90 | 18.00 | 10.90 | 16.00 | 5.20  | 12.30 | 4.69   | 10.93 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated GPCM read<br>access, GPCM write access ACS = 00 and CSNT<br>= 0 (MAX = 0.00 × B1 + 8.00) | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | 2.00   | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0<br>(MIN = $0.25 \times B1 - 2.00$ )                    | 5.60  |       | 4.30  |       | 1.80  |       | 1.13   |       | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 11 TRLX = 0<br>(MIN = 0.50 × B1 - 2.00)                             | 13.20 |       | 10.50 |       | 5.60  | _     | 4.25   |       | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}$ (0:3) asserted<br>(MAX = 0.00 × B1 + 9.00)                                     | _     | 9.00  | —     | 9.00  | —     | 9.00  | —      | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated<br>(MAX = 0.00 × B1 + 9.00)                                                              | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | 2.00   | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 1<br>(MIN = $1.25 \times B1 - 2.00$ )                    | 35.90 |       | 29.30 |       | 16.90 |       | 13.60  |       | ns   |

### Table 9. Bus Operation Timings (continued)

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33 I  | MHz   | 40 I  | MHz   | 66 I  | MHz   | 80 I  | MHz   | Unit |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min   | Мах   | Min   | Мах   | Min   | Max   | Min   | Мах   | Unit |

| B29h | $\overline{\text{WE}}(0:3)$ negated to D(0:31) High-Z GPCM write<br>access, TRLX = 1, CSNT = 1, EBDF = 1<br>(MIN = 0.375 × B1 - 3.30)                                                                                                                                                                                                                                                                                                                                       | 38.40 |       | 31.10 |       | 17.50 | _     | 13.85 |       | ns   |

| B29i | $\overline{\text{CS}}$ negated to D(0:31) High-Z GPCM write<br>access, TRLX = 1, CSNT = 1, ACS = 10 or<br>ACS = 11, EBDF = 1 (MIN = 0.375 × B1 – 3.30)                                                                                                                                                                                                                                                                                                                      | 38.40 | _     | 31.10 |       | 17.50 | _     | 13.85 |       | ns   |

| B30  | $\label{eq:cs} \hline{\text{CS}}, \overline{\text{WE}}(0:3) \text{ negated to A}(0:31), \text{BADDR}(28:30) \\ \\ \text{Invalid GPCM read/write access}^8 \\ (\text{MIN} = 0.25 \times \text{B1} - 2.00) \\ \hline$                                                                                                                                                                                                                                                         | 5.60  |       | 4.30  |       | 1.80  | _     | 1.13  |       | ns   |

| B30a | $\label{eq:weighted_states} \hline \hline WE(0:3) \ \text{negated to } A(0:31), \ BADDR(28:30) \\ \hline \text{Invalid GPCM, write access, } TRLX = 0, \ CSNT = 1, \\ \hline CS \ \text{negated to } A(0:31) \ \text{invalid GPCM write access} \\ TRLX = 0, \ CSNT = 1 \ ACS = 10, \ \text{or } ACS = = 11, \\ \hline EBDF = 0 \ (MIN = 0.50 \times B1 - 2.00) \\ \hline \hline \end{array}$                                                                               | 13.20 |       | 10.50 | _     | 5.60  | _     | 4.25  | _     | ns   |

| B30b | $\label{eq:weighted_states} \hline \hline WE(0:3) \ \text{negated to } A(0:31) \ \text{invalid GPCM} \\ \hline BADDR(28:30) \ \text{invalid GPCM} \ \text{write access}, \\ \hline TRLX = 1, \ CSNT = 1. \ \overline{CS} \ \text{negated to } A(0:31) \\ \hline \text{invalid GPCM} \ \text{write access} \ TRLX = 1, \ CSNT = 1, \\ \hline ACS = 10, \ \text{or } ACS == 11 \ \text{EBDF} = 0 \\ \hline (MIN = 1.50 \times \text{B1} - 2.00) \\ \hline \hline \end{array}$ | 43.50 | _     | 35.50 | _     | 20.70 |       | 16.75 |       | ns   |

| B30c | $\label{eq:weighted_states} \begin{array}{ c c c c c } \hline \hline WE(0:3) \mbox{ negated to } A(0:31), \mbox{ BADDR}(28:30) \\ \hline \mbox{ invalid GPCM write access, TRLX = 0, CSNT = 1.} \\ \hline \hline CS \mbox{ negated to } A(0:31) \mbox{ invalid GPCM write access, TRLX = 0, CSNT = 1 ACS = 10, } \\ \hline ACS == 11, \mbox{ EBDF = 1 (MIN = 0.375 \times B1 - 3.00)} \end{array}$                                                                          | 8.40  | _     | 6.40  |       | 2.70  | _     | 1.70  |       | ns   |

| B30d | $\overline{\text{WE}}(0:3)$ negated to A(0:31), BADDR(28:30)<br>invalid GPCM write access TRLX = 1, CSNT =1,<br>$\overline{\text{CS}}$ negated to A(0:31) invalid GPCM write access<br>TRLX = 1, CSNT = 1, ACS = 10 or 11, EBDF = 1                                                                                                                                                                                                                                         | 38.67 |       | 31.38 |       | 17.83 | _     | 14.19 |       | ns   |

| B31  | CLKOUT falling edge to $\overline{\text{CS}}$ valid, as requested by control bit CST4 in the corresponding word in the UPM (MAX = $0.00 \times \text{B1} + 6.00$ )                                                                                                                                                                                                                                                                                                          | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

| B31a | CLKOUT falling edge to $\overline{\text{CS}}$ valid, as requested by control bit CST1 in the corresponding word in the UPM (MAX = $0.25 \times \text{B1} + 6.80$ )                                                                                                                                                                                                                                                                                                          | 7.60  | 14.30 | 6.30  | 13.00 | 3.80  | 10.50 | 3.13  | 10.00 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid, as requested by control bit CST2 in the corresponding word in the UPM (MAX = $0.00 \times B1 + 8.00$ )                                                                                                                                                                                                                                                                                                                         | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid, as requested by control bit CST3 in the corresponding word in the UPM (MAX = $0.25 \times B1 + 6.30$ )                                                                                                                                                                                                                                                                                                                         | 7.60  | 13.80 | 6.30  | 12.50 | 3.80  | 10.00 | 3.13  | 9.40  | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid, as requested by<br>control bit CST1 in the corresponding word in the<br>UPM EBDF = 1 (MAX = $0.375 \times B1 + 6.6$ )                                                                                                                                                                                                                                                                                                         | 13.30 | 18.00 | 11.30 | 16.00 | 7.60  | 12.30 | 4.69  | 11.30 | ns   |

### Table 9. Bus Operation Timings (continued)

**Bus Signal Timing**

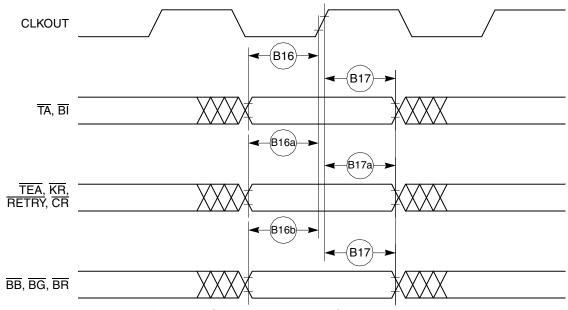

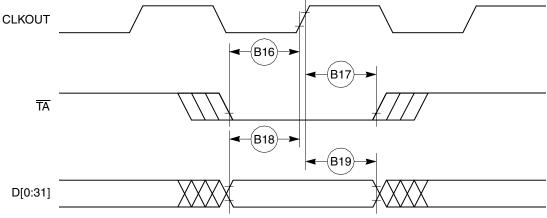

Figure 10 provides the timing for the synchronous input signals.

Figure 11 provides normal case timing for input data. It also applies to normal read accesses under the control of the user-programmable machine (UPM) in the memory controller.

Figure 11. Input Data Timing in Normal Case

1

**Bus Signal Timing**

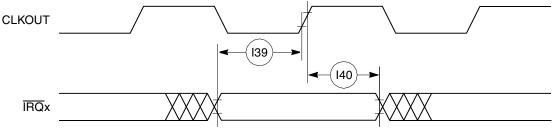

#### Table 10 provides the interrupt timing for the MPC885/MPC880.

| Num | Characteristic <sup>1</sup>                   | All Freq                  | Unit |      |

|-----|-----------------------------------------------|---------------------------|------|------|

| Num | Characteristic                                | Min                       | Мах  | Onit |

| 139 | IRQx valid to CLKOUT rising edge (setup time) | 6.00                      |      | ns   |

| 140 | IRQx hold time after CLKOUT                   | 2.00                      |      | ns   |

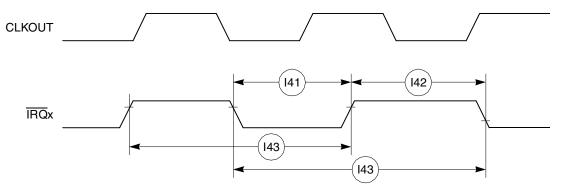

| l41 | IRQx pulse width low                          | 3.00                      |      | ns   |

| 142 | IRQx pulse width high                         | 3.00                      |      | ns   |

| 143 | IRQx edge-to-edge time                        | 4 × T <sub>CLOCKOUT</sub> |      | —    |

#### Table 10. Interrupt Timing

The I39 and I40 timings describe the testing conditions under which the IRQ lines are tested when being defined as level sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT. The I41, I42, and I43 timings are specified to allow correct functioning of the IRQ lines detection circuitry and have no direct relation with the total system interrupt latency that the MPC885/MPC880 is able to support.

Figure 26 provides the interrupt detection timing for the external level-sensitive lines.

Figure 26. Interrupt Detection Timing for External Level Sensitive Lines

Figure 27 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 27. Interrupt Detection Timing for External Edge Sensitive Lines

**Bus Signal Timing**

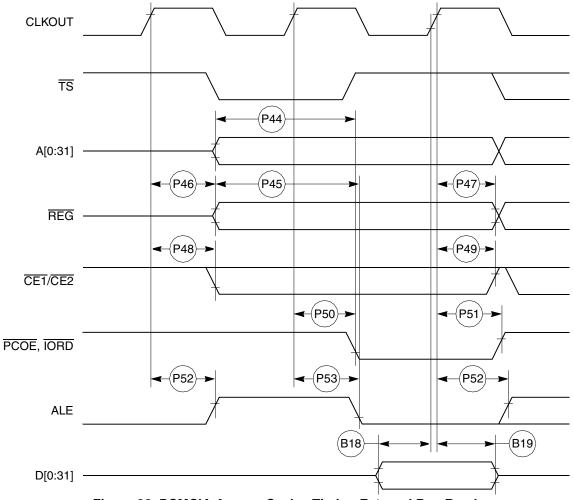

Figure 28 provides the PCMCIA access cycle timing for the external bus read.

Figure 28. PCMCIA Access Cycles Timing External Bus Read

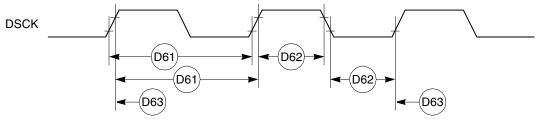

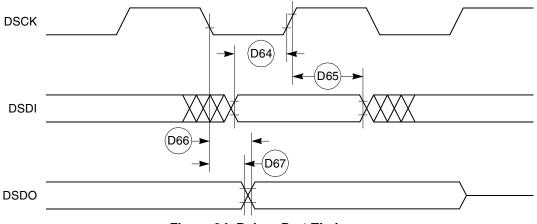

Table 13 shows the debug port timing for the MPC885/MPC880.

#### Table 13. Debug Port Timing

| Num   | Characteristic              | All Frequer                | Unit  |      |

|-------|-----------------------------|----------------------------|-------|------|

| Nulli | Characteristic              | Min                        | Мах   | Unit |

| D61   | DSCK cycle time             | 3 × T <sub>CLOCKOUT</sub>  |       | _    |

| D62   | DSCK clock pulse width      | $1.25 \times T_{CLOCKOUT}$ | _     | —    |

| D63   | DSCK rise and fall times    | 0.00                       | 3.00  | ns   |

| D64   | DSDI input data setup time  | 8.00                       | _     | ns   |

| D65   | DSDI data hold time         | 5.00                       | _     | ns   |

| D66   | DSCK low to DSDO data valid | 0.00                       | 15.00 | ns   |

| D67   | DSCK low to DSDO invalid    | 0.00                       | 2.00  | ns   |

Figure 33 provides the input timing for the debug port clock.

Figure 33. Debug Port Clock Input Timing

Figure 34 provides the timing for the debug port.

## Table 14 shows the reset timing for the MPC885/MPC880.

Table 14. Reset Timing

| Num | Ohennesterrietie                                                                                                                                           | 33 1   | MHz   | 40 MHz |       | 66 MHz |       | 80 MHz |       | Unit |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Num | Characteristic                                                                                                                                             | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to $\overline{\text{HRESET}}$ high impedance<br>(MAX = 0.00 × B1 + 20.00)                                                                           | —      | 20.00 | —      | 20.00 | -      | 20.00 | —      | 20.00 | ns   |

| R70 | CLKOUT to $\overline{\text{SRESET}}$ high impedance<br>(MAX = 0.00 × B1 + 20.00)                                                                           | —      | 20.00 | —      | 20.00 | —      | 20.00 | —      | 20.00 | ns   |

| R71 | $\frac{RSTCONF}{(MIN = 17.00 \times B1)}$                                                                                                                  | 515.20 | _     | 425.00 | _     | 257.60 | _     | 212.50 | _     | ns   |

| R72 | —                                                                                                                                                          | —      |       | —      |       | —      |       | —      |       | —    |

| R73 | Configuration data to HRESET rising<br>edge setup time<br>(MIN = $15.00 \times B1 + 50.00$ )                                                               | 504.50 | _     | 425.00 | _     | 277.30 | _     | 237.50 | _     | ns   |

| R74 | Configuration data to $\overline{\text{RSTCONF}}$ rising<br>edge setup time<br>(MIN = 0.00 × B1 + 350.00)                                                  | 350.00 | _     | 350.00 | _     | 350.00 | _     | 350.00 | _     | ns   |

| R75 | Configuration data hold time after $\overrightarrow{\text{RSTCONF}}$ negation (MIN = 0.00 × B1 + 0.00)                                                     | 0.00   | _     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| R76 | Configuration data hold time after<br>HRESET negation<br>(MIN = $0.00 \times B1 + 0.00$ )                                                                  | 0.00   | _     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| R77 | HRESET and RSTCONF asserted to<br>data out drive<br>(MAX = $0.00 \times B1 + 25.00$ )                                                                      | _      | 25.00 | _      | 25.00 | _      | 25.00 | —      | 25.00 | ns   |

| R78 | $\frac{RSTCONF}{Impedance} \text{ negated to data out high}$<br>impedance (MAX = 0.00 × B1 + 25.00)                                                        | —      | 25.00 | —      | 25.00 | —      | 25.00 | —      | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip<br>three-states $\overrightarrow{\text{HRESET}}$ to data out high<br>impedance (MAX = 0.00 × B1 + 25.00)            | —      | 25.00 | _      | 25.00 | _      | 25.00 | —      | 25.00 | ns   |

| R80 | DSDI, DSCK setup (MIN = $3.00 \times B1$ )                                                                                                                 | 90.90  |       | 75.00  |       | 45.50  |       | 37.50  |       | ns   |

| R81 | DSDI, DSCK hold time (MIN = $0.00 \times B1 + 0.00$ )                                                                                                      | 0.00   |       | 0.00   |       | 0.00   |       | 0.00   | _     | ns   |

| R82 | $\frac{\text{SRESET}}{\text{SRESET}} \text{ negated to CLKOUT rising}$ $\frac{\text{edge for DSDI and DSCK sample}}{(\text{MIN} = 8.00 \times \text{B1})}$ | 242.40 | _     | 200.00 |       | 121.20 | _     | 100.00 | —     | ns   |

**CPM Electrical Characteristics**

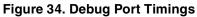

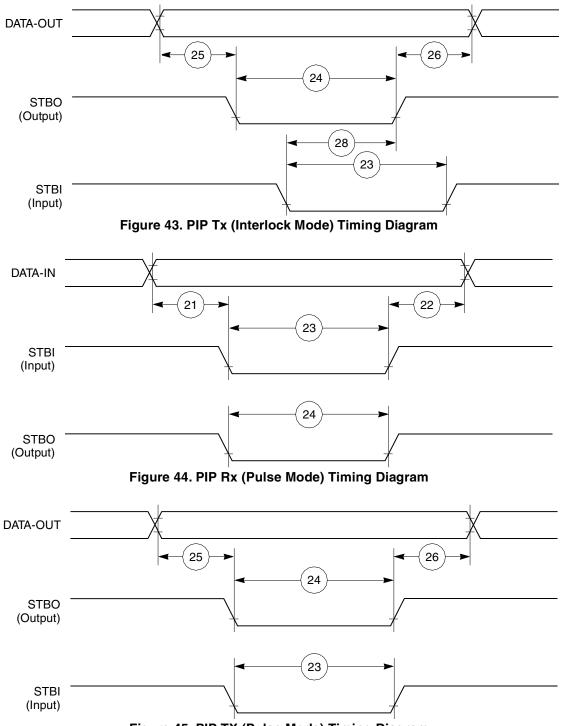

Figure 45. PIP TX (Pulse Mode) Timing Diagram

**CPM Electrical Characteristics**

**CPM Electrical Characteristics**

**CPM Electrical Characteristics**

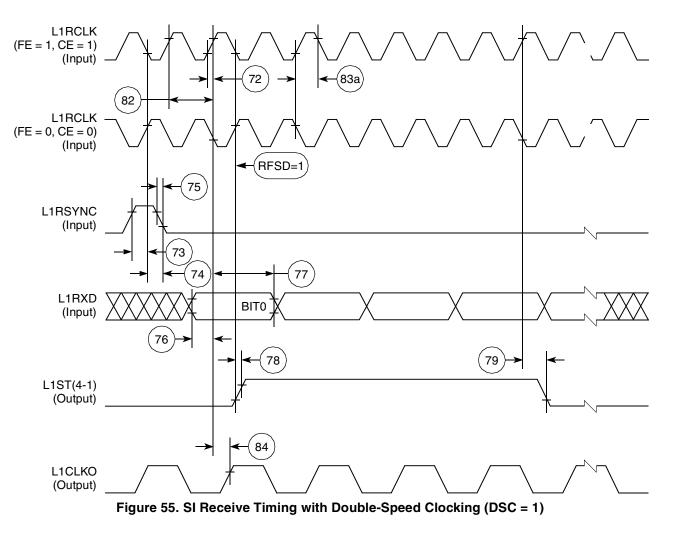

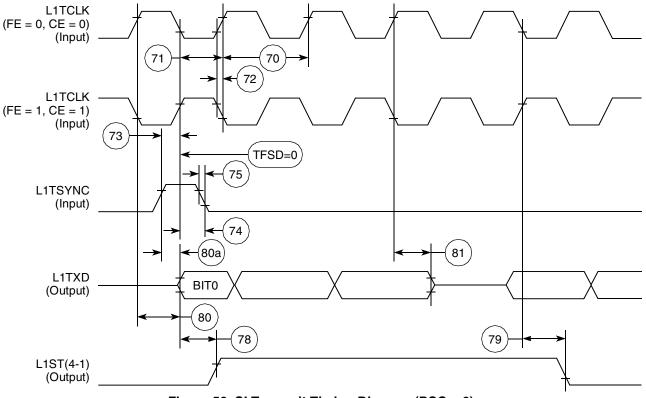

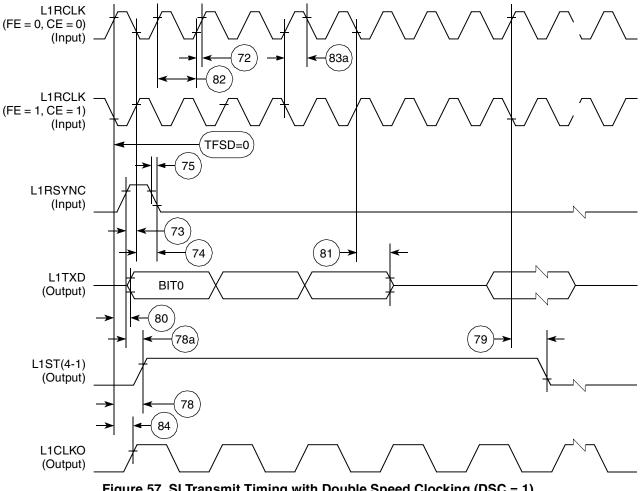

Figure 57. SI Transmit Timing with Double Speed Clocking (DSC = 1)

#### **CPM Electrical Characteristics**

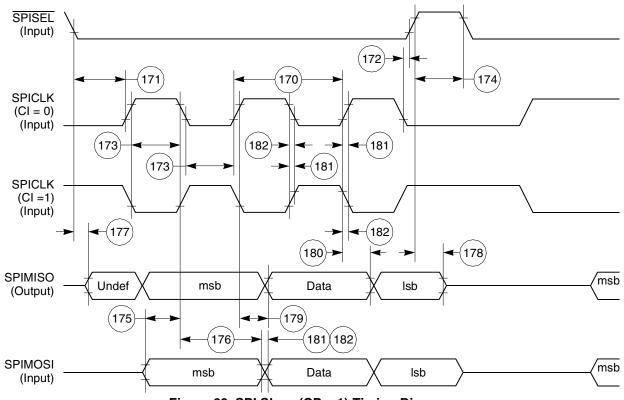

## Figure 69. SPI Slave (CP = 1) Timing Diagram

## 12.12 I<sup>2</sup>C AC Electrical Specifications

Table 28 provides the  $I^2C$  (SCL < 100 kHz) timings.

Table 28.  $I^2C$  Timing (SCL < 100 kHz)

| Num | Characteristic                            | All Freq | uencies                                                          | Unit |

|-----|-------------------------------------------|----------|------------------------------------------------------------------|------|

| Num | Cildiacteristic                           | Min      | Max       100       100                            100       100 | Unit |

| 200 | SCL clock frequency (slave)               | 0        | 100                                                              | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100                                                              | kHz  |

| 202 | Bus free time between transmissions       | 4.7      | _                                                                | μs   |

| 203 | Low period of SCL                         | 4.7      | _                                                                | μs   |

| 204 | High period of SCL                        | 4.0      | _                                                                | μs   |

| 205 | Start condition setup time                | 4.7      | _                                                                | μs   |

| 206 | Start condition hold time                 | 4.0      | _                                                                | μs   |

| 207 | Data hold time                            | 0        | _                                                                | μs   |

| 208 | Data setup time                           | 250      | _                                                                | ns   |

| 209 | SDL/SCL rise time                         | —        | 1                                                                | μs   |

# 14 USB Electrical Characteristics

This section provides the AC timings for the USB interface.

## 14.1 USB Interface AC Timing Specifications

The USB Port uses the transmit clock on SCC1. Table 33 lists the USB interface timings.

#### Table 33. USB Interface AC Timing Specifications

| Name | Characteristic                                                        | h <sup>1</sup><br>6<br>48 | uencies | Unit       |

|------|-----------------------------------------------------------------------|---------------------------|---------|------------|

| Hame |                                                                       | Min                       | Max     | <b>O</b>   |

| US1  | USBCLK frequency of operation <sup>1</sup><br>Low speed<br>Full speed |                           |         | MHz<br>MHz |

| US4  | USBCLK duty cycle (measured at 1.5 V)                                 | 45                        | 55      | %          |

<sup>1</sup> USBCLK accuracy should be ±500 ppm or better. USBCLK may be stopped to conserve power.

# **15 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 or 3.3 V.

## 15.1 MII and Reduced MII Receive Signal Timing

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25 MHz + 1%. The reduced MII (RMII) receiver functions correctly up to a RMII\_REFCLK maximum frequency of 50 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency – 1%.

Table 34 provides information on the MII and RMII receive signal timing.

| Num     | Characteristic                                               | Min                                          | Max                   | Unit |

|---------|--------------------------------------------------------------|----------------------------------------------|-----------------------|------|

| M1      | MII_RXD[3:0], MII_RX_DV, MII_RX_ERR to MII_RX_CLK setup      | 5                                            | — ns                  |      |

| M2      | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold        | C_ER hold 5 — ns                             |                       |      |

| М3      | MII_RX_CLK pulse width high                                  | 35%                                          | 65% MII_RX_CLK period |      |

| M4      | MII_RX_CLK pulse width low                                   | 35%                                          | 65% MII_RX_CLK period |      |

| M1_RMII | RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR to RMII_REFCLK setup | II_CRS_DV, RMII_RX_ERR to RMII_REFCLK 4 — ns |                       |      |

| M2_RMII | RMII_REFCLK to RMII_RXD[1:0], RMII_CRS_DV, RMII_RX_ERR hold  | 2                                            | — ns                  |      |

#### Table 34. MII Receive Signal Timing

# **17 Document Revision History**

Table 40 lists significant changes between revisions of this hardware specification.

| Revision<br>Number | Date      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7                  | 07/2010   | <ul> <li>In Table 9, "Bus Operation Timings," changed the following:</li> <li>Updated TRLX condition value for B22a/b/c to "TRLX = [0 or 1]"</li> <li>Removed TRLX condition for B23</li> <li>Updated condition and equation for B30 to "Invalid GPCM read/write access (MIN = 0.25 × B1 - 2.00)"</li> <li>Updated note 8 to "The timing B30 refers to CS when ACS = 00 and to CS and WE(0:3) when CSNT = 0."</li> </ul>                                                                                                                                                                                                                              |  |

| 6                  | 05/2010   | Added minimum load for CLKOUT in Section 10, "Bus Signal Timing."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 5                  | 03/2009   | Updated formatting of Table 12, "PCMCIA Port Timing," Table 13, "Debug Port Timing," Table 14, "Reset Timing," and Table 15, "JTAG Timing."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 4                  | 08/2007   | <ul> <li>On page 1, updated first paragraph and added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 3) and renumbered the rest of the figures.</li> <li>In Table 9, for reset timings B29f and B29g added footnote indicating that the formula only applies to bus operation up to 50 MHz.</li> <li>In Figure 6, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 18, changed num 46 description to read, "TA assertion to rising edge"</li> <li>In Figure 49, changed TA to reflect the rising edge of the clock.</li> </ul> |  |

| 3.0                | 7/22/2004 | <ul> <li>Added sentence to Spec B1A about EXTCLK and CLKOUT being in Alignment for Integer Values</li> <li>Added a footnote to Spec 41 specifying that EDM = 1</li> <li>Added RMII1_EN under M1II_EN in Table 36 Pin Assignments</li> <li>Added a tablefootnote to Table 6 DC Electrical Specifications about meeting the VIL Max of the I2C Standard</li> <li>Put the new part numbers in the Ordering Information Section</li> </ul>                                                                                                                                                                                                                |  |

| 2.0                | 12/2003   | <ul> <li>Changed the maximum operating frequency to 133 MHz.</li> <li>Put in the orderable part numbers that are orderable.</li> <li>Put the timing in the 80 MHz column.</li> <li>Rounded the timings to hundredths in the 80 MHz column.</li> <li>Put the pin numbers in footnotes by the maximum currents in Table 6.</li> <li>Changed 22 and 41 in the Timing.</li> <li>Put in the Thermal numbers.</li> </ul>                                                                                                                                                                                                                                    |  |

| 1.0                | 9/2003    | <ul> <li>Added the DSP information in the Features list</li> <li>Fixed table formatting.</li> <li>Nontechnical edits.</li> <li>Released to the external web.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 0.9                | 8/2003    | Changed the USB description to full-/low-speed compatible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 0.8                | 8/2003    | Added the Reference to USB 2.0 to the Features list and removed 1.1 from USB on the block diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 0.7                | 7/2003    | Added the RxClav and TxClav signals to PC15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 0.6                | 6/2003    | Changed the pin descriptions per the June 22 spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0.5                | 5/2003    | Changed some more typos, put in the phsel and phreq pins. Corrected the USB timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

### Table 40. Document Revision History