## NXP USA Inc. - MPC885CVR66 Datasheet

#### Welcome to E-XFL.COM

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                            |

|---------------------------------|---------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                      |

| Speed                           | 66MHz                                                               |

| Co-Processors/DSP               | Communications; CPM, Security; SEC                                  |

| RAM Controllers                 | DRAM                                                                |

| Graphics Acceleration           | No                                                                  |

| Display & Interface Controllers | -                                                                   |

| Ethernet                        | 10Mbps (3), 10/100Mbps (2)                                          |

| SATA                            | -                                                                   |

| USB                             | USB 2.0 (1)                                                         |

| Voltage - I/O                   | 3.3V                                                                |

| Operating Temperature           | -40°C ~ 100°C (TA)                                                  |

| Security Features               | Cryptography                                                        |

| Package / Case                  | 357-BBGA                                                            |

| Supplier Device Package         | 357-PBGA (25x25)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc885cvr66 |

|                                 |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

The MPC885/MPC880 is a versatile single-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications and communications and networking systems. The MPC885/MPC880 provides enhanced ATM functionality, an additional fast Ethernet controller, a USB, and an encryption block.

Table 1 shows the functionality supported by MPC885/MPC880.

| Part   | Cache (Kbytes) |         | Ethernet |        | scc | SMC  | USB | ATM Support                     | Security |

|--------|----------------|---------|----------|--------|-----|------|-----|---------------------------------|----------|

| Fait   | I Cache        | D Cache | 10BaseT  | 10/100 | 300 | SINC | 036 |                                 | Engine   |

| MPC885 | 8              | 8       | Up to 3  | 2      | 3   | 2    | 1   | Serial ATM and UTOPIA interface | Yes      |

| MPC880 | 8              | 8       | Up to 2  | 2      | 2   | 2    | 1   | Serial ATM and UTOPIA interface | No       |

Table 1. MPC885 Family

# 2 Features

The MPC885/MPC880 is comprised of three modules that each use the 32-bit internal bus: a MPC8xx core, a system integration unit (SIU), and a communications processor module (CPM).

The following list summarizes the key MPC885/MPC880 features:

- Embedded MPC8xx core up to 133 MHz

- Maximum frequency operation of the external bus is 80 MHz (in 1:1 mode)

- The 133-MHz core frequency supports 2:1 mode only.

- The 66-/80-MHz core frequencies support both the 1:1 and 2:1 modes.

- Single-issue, 32-bit core (compatible with the Power Architecture definition) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch and without conditional execution.

- 8-Kbyte data cache and 8-Kbyte instruction cache (see Table 1)

- Instruction cache is two-way, set-associative with 256 sets in 2 blocks

- Data cache is two-way, set-associative with 256 sets

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully associative instruction and data TLBs

- MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip emulation debug mode

- On-chip  $16 \times 16$  multiply accumulate controller (MAC)

- One operation per clock (two-clock latency, one-clock blockage)

- MAC operates concurrently with other instructions

- FIR loop—Four clocks per four multiplies

- Four baud rate generators

- Independent (can be connected to any SCC or SMC)

- Allow changes during operation

- Autobaud support option

- Up to three serial communication controllers (SCCs) supporting the following protocols:

- Serial ATM capability on SCCs

- Optional UTOPIA port on SCC4

- Ethernet/IEEE Std 802.3<sup>™</sup> optional on the SCC(s) supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support point-to-point protocol (PPP)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

- Up to two serial management channels (SMCs) supporting the following protocols:

- UART (low-speed operation)

- Transparent

- General circuit interface (GCI) controller

- Provide management for BRI devices as GCI controller in time-division multiplexed (TDM) channels

- Universal serial bus (USB)—Supports operation as a USB function endpoint, a USB host controller, or both for testing purposes (loop-back diagnostics)

- USB 2.0 full-/low-speed compatible

- The USB function mode has the following features:

- Four independent endpoints support control, bulk, interrupt, and isochronous data transfers.

- CRC16 generation and checking

- CRC5 checking

- NRZI encoding/decoding with bit stuffing

- 12- or 1.5-Mbps data rate

| Characteristic                                                           | Symbol          | Min | Max | Unit |

|--------------------------------------------------------------------------|-----------------|-----|-----|------|

| Output high voltage, $I_{OH} = -2.0$ mA, except XTAL and open-drain pins | V <sub>OH</sub> | 2.4 | _   | V    |

|                                                                          | V <sub>OL</sub> | _   | 0.5 | V    |

### Table 6. DC Electrical Specifications (continued)

<sup>1</sup> The difference between  $V_{DDL}$  and  $V_{DDSYN}$  cannot be more than 100 mV.

<sup>2</sup> The signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], PE(14:31), TDI, TDO, TCK, TRST, TMS, MII1\_TXEN, MII\_MDIO are 5-V tolerant. The minimum voltage is still 2.0 V.

$^{3}$  V<sub>IL</sub>(max) for the I<sup>2</sup>C interface is 0.8 V rather than the 1.5 V as specified in the I<sup>2</sup>C standard.

<sup>4</sup> Input capacitance is periodically sampled.

<sup>5</sup> A(0:31), TSIZ0/REG, TSIZ1, D(0:31), IRQ(2:4), IRQ6, RD/WR, BURST, IP\_B(3:7), PA(0:11), PA13, PA15, PB(14:31),

PC(4:15), PD(3:15), PE(14:31), MII1\_CRS, MII\_MDIO, MII1\_TXEN, and MII1\_COL.

<sup>6</sup> BDIP/GPL\_B(5), BR, BG, FRZ/IRQ6, CS(0:7), WE(0:3), BS\_A(0:3), GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A(2:3)/GPL\_B(2:3)/CS(2:3), UPWAITA/GPL\_A4, UPWAITB/GPL\_B4, GPL\_A5, ALE\_A, CE1\_A, CE2\_A, OP(0:3), and BADDR(28:30).

## 7 Thermal Calculation and Measurement

For the following discussions,  $P_D = (V_{DDL} \times I_{DDL}) + PI/O$ , where PI/O is the power dissipation of the I/O drivers.

## NOTE

The V<sub>DDSYN</sub> power dissipation is negligible.

## 7.1 Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, in °C can be obtained from the following equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_A$  = ambient temperature (°C)

$R_{\theta IA}$  = package junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in package

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. However, the answer is only an estimate; test cases have demonstrated that errors of a factor of two (in the quantity  $T_J - T_A$ ) are possible.

## 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta IA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the airflow around the device, add a heat sink, change the mounting arrangement on the printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

## 7.3 Estimation with Junction-to-Board Thermal Resistance

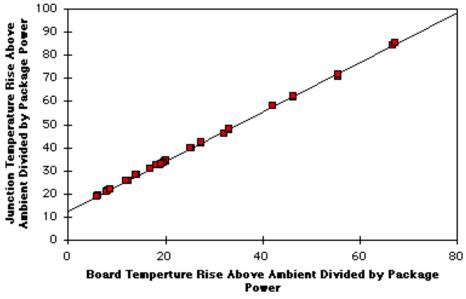

A simple package thermal model that has demonstrated reasonable accuracy (about 20%) is a two-resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed-circuit board. It has been observed that the thermal performance of most plastic packages and especially PBGA packages is strongly dependent on the board temperature; see Figure 4.

Figure 4. Effect of Board Temperature Rise on Thermal Behavior

| Num  | Characteristic                                                                                                                                               | 33 MHz |       | 40 MHz |       | 66 MHz |       | 80 MHz |       | Unit |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Num  |                                                                                                                                                              | Min    | Мах   | Min    | Мах   | Min    | Мах   | Min    | Мах   | Unit |

| B5   | CLKOUT fall time                                                                                                                                             | _      | 4.00  | _      | 4.00  | _      | 4.00  | _      | 4.00  | ns   |

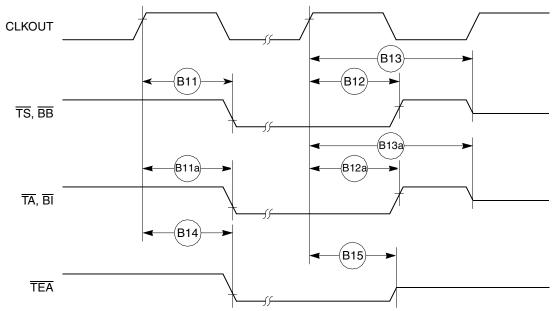

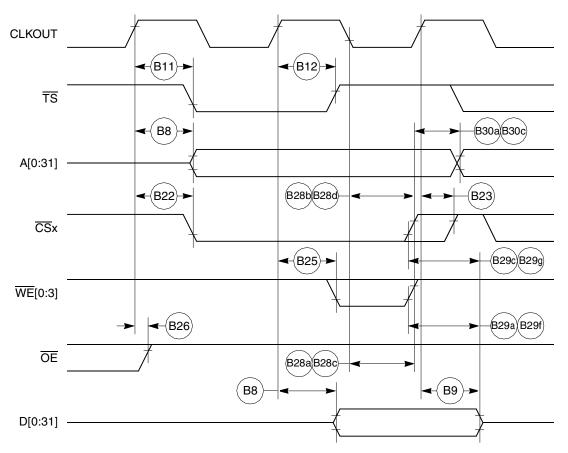

| B7   | CLKOUT to A(0:31), BADDR(28:30), RD/ $\overline{WR}$ ,<br>BURST, D(0:31) output hold (MIN = 0.25 × B1)                                                       | 7.60   | —     | 6.30   |       | 3.80   | _     | 3.13   | —     | ns   |

| B7a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , $\overline{\text{BDIP}}$ , PTR output hold (MIN = 0.25 × B1)                        | 7.60   |       | 6.30   |       | 3.80   |       | 3.13   | _     | ns   |

| B7b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , FRZ, VFLS(0:1), VF(0:2)<br>IWP(0:2), LWP(0:1), $\overline{STS}$ output hold<br>(MIN = 0.25 × B1)               | 7.60   | —     | 6.30   | _     | 3.80   | —     | 3.13   | —     | ns   |

| B8   | CLKOUT to A(0:31), BADDR(28:30) RD/ $\overline{WR}$ ,<br>BURST, D(0:31) valid (MAX = 0.25 × B1 + 6.3)                                                        | —      | 13.80 | _      | 12.50 | _      | 10.00 | —      | 9.43  | ns   |

| B8a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ , AT(0:3) $\overline{\text{BDIP}}$ ,<br>PTR valid (MAX = 0.25 × B1 + 6.3)             | —      | 13.80 |        | 12.50 |        | 10.00 | —      | 9.43  | ns   |

| B8b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1), VF(0:2),<br>IWP(0:2), FRZ, LWP(0:1), $\overline{STS}$ valid <sup>4</sup><br>(MAX = 0.25 × B1 + 6.3) | _      | 13.80 | _      | 12.50 | _      | 10.00 | _      | 9.43  | ns   |

| B9   | CLKOUT to A(0:31), BADDR(28:30), RD/WR,<br>BURST, D(0:31), TSIZ(0:1), REG, RSV, AT(0:3),<br>PTR High-Z (MAX = 0.25 × B1 + 6.3)                               | 7.60   | 13.80 | 6.30   | 12.50 | 3.80   | 10.00 | 3.13   | 9.43  | ns   |

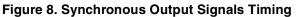

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion<br>(MAX = 0.25 × B1 + 6.0)                                                                             | 7.60   | 13.60 | 6.30   | 12.30 | 3.80   | 9.80  | 3.13   | 9.13  | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion (when driven by the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.30^{1}$ )     | 2.50   | 9.30  | 2.50   | 9.30  | 2.50   | 9.30  | 2.50   | 9.30  | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation<br>(MAX = 0.25 × B1 + 4.8)                                                                              | 7.60   | 12.30 | 6.30   | 11.00 | 3.80   | 8.50  | 3.13   | 7.92  | ns   |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when driven by the memory controller or PCMCIA interface)<br>(MAX = $0.00 \times B1 + 9.00$ )          | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | 2.5    | 9.00  | ns   |

| B13  | CLKOUT to $\overline{\text{TS}}$ , $\overline{\text{BB}}$ High-Z (MIN = 0.25 × B1)                                                                           | 7.60   | 21.60 | 6.30   | 20.30 | 3.80   | 14.00 | 3.13   | 12.93 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven by the memory controller or PCMCIA interface)<br>(MIN = 0.00 × B1 + 2.5)                     | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.5    | 15.00 | ns   |

| B14  | CLKOUT to $\overline{\text{TEA}}$ assertion<br>(MAX = 0.00 × B1 + 9.00)                                                                                      | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |

| B15  | CLKOUT to TEA High-Z (MIN = $0.00 \times B1 + 2.50$ )                                                                                                        | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns   |

| B16  | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 × B1 + 6.00)                                                     | 6.00   | _     | 6.00   | _     | 6.00   | _     | 6      | _     | ns   |

| B16a | TEA, $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid to CLKOUT (setup time) (MIN = 0.00 × B1 + 4.5)                        | 4.50   | _     | 4.50   | _     | 4.50   | _     | 4.50   | _     | ns   |

## Table 9. Bus Operation Timings (continued)

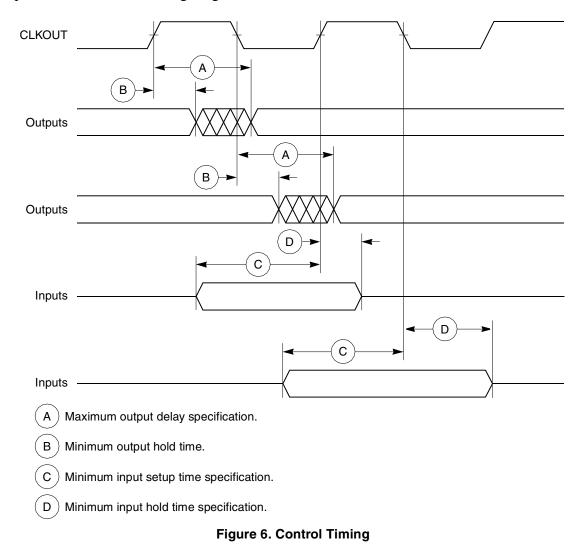

Figure 6 provides the control timing diagram.

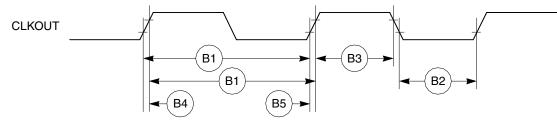

Figure 7 provides the timing for the external clock.

Figure 7. External Clock Timing

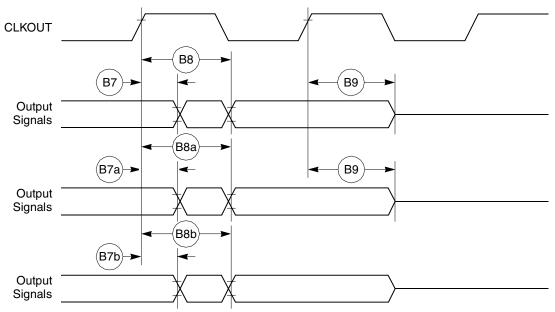

Figure 8 provides the timing for the synchronous output signals.

Figure 9 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 9. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

Figure 18. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 1)

Figure 19. External Bus Write Timing (GPCM Controlled—TRLX = 1, CSNT = 1)

## Table 12 shows the PCMCIA port timing for the MPC885/MPC880.

| Num | Characteristic                                                               | 33 MHz |       | 40 MHz |       | 66 MHz |       | 80 MHz |       | Unit |

|-----|------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

|     | Unaracteristic                                                               | Min    | Мах   | Min    | Max   | Min    | Мах   | Min    | Max   | Unit |

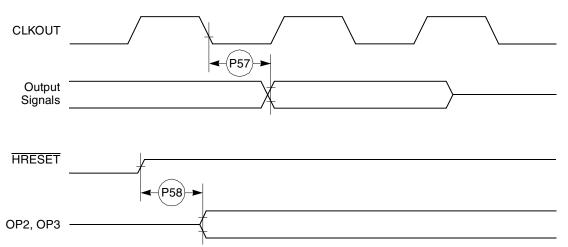

| P57 | CLKOUT to OPx valid<br>(MAX = $0.00 \times B1 + 19.00$ )                     | _      | 19.00 | -      | 19.00 | -      | 19.00 | -      | 19.00 | ns   |

| P58 | HRESET negated to OPx drive <sup>1</sup><br>(MIN = $0.75 \times B1 + 3.00$ ) | 25.70  |       | 21.70  | _     | 14.40  | _     | 12.40  | _     | ns   |

| P59 | IP_Xx valid to CLKOUT rising edge (MIN = $0.00 \times B1 + 5.00$ )           | 5.00   | _     | 5.00   | _     | 5.00   | —     | 5.00   | _     | ns   |

| P60 | CLKOUT rising edge to IP_Xx invalid<br>(MIN = $0.00 \times B1 + 1.00$ )      | 1.00   | _     | 1.00   |       | 1.00   |       | 1.00   |       | ns   |

## Table 12. PCMCIA Port Timing

<sup>1</sup> OP2 and OP3 only.

## Figure 31 provides the PCMCIA output port timing for the MPC885/MPC880.

## Figure 31. PCMCIA Output Port Timing

Figure 32 provides the PCMCIA input port timing for the MPC885/MPC880.

Figure 32. PCMCIA Input Port Timing

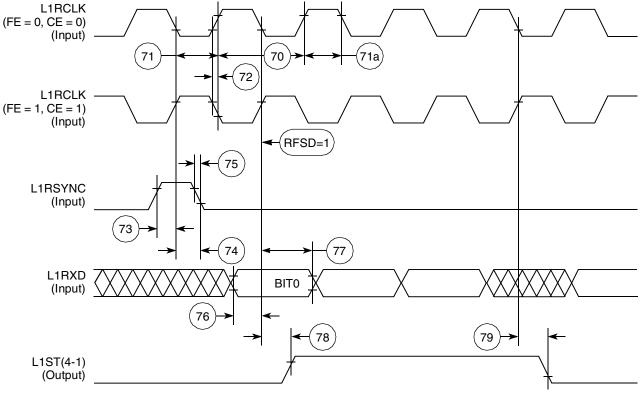

**CPM Electrical Characteristics**

# **12 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC885/MPC880.

Table 16. PIP/PIO Timing

## 12.1 PIP/PIO AC Electrical Specifications

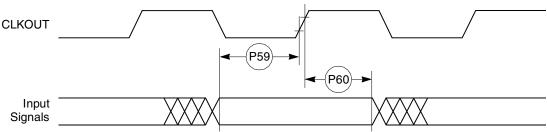

Table 16 provides the PIP/PIO AC timings as shown in Figure 42 through Figure 46.

#### **All Frequencies** Num Characteristic Unit Min Max 21 Data-in setup time to STBI low 0 \_\_\_\_ ns 22 Data-In hold time to STBI high 0 clk 23 STBI pulse width 1.5 clk 24 STBO pulse width 1 clk – 5 ns ns 25 Data-out setup time to STBO low 2 clk Data-out hold time from STBO high 5 26 clk STBI low to STBO low (Rx interlock) 27 4.5 clk 28 STBI low to STBO high (Tx interlock) 2 clk \_\_\_\_ 29 Data-in setup time to clock high 15 ns 30 Data-in hold time from clock high 7.5 ns Clock low to data-out valid (CPU writes data, control, or direction) 31 25 ns

Figure 42. PIP Rx (Interlock Mode) Timing Diagram

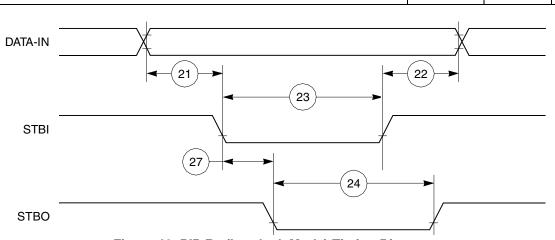

Figure 51. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

## 12.4 Baud Rate Generator AC Electrical Specifications

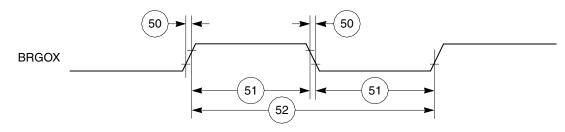

Table 19 provides the baud rate generator timings as shown in Figure 52.

| Num | Characteristic          |    | All Frequencies |      |  |

|-----|-------------------------|----|-----------------|------|--|

|     |                         |    | Мах             | Unit |  |

| 50  | BRGO rise and fall time |    | 10              | ns   |  |

| 51  | BRGO duty cycle         | 40 | 60              | %    |  |

| 52  | BRGO cycle              | 40 | —               | ns   |  |

Figure 52. Baud Rate Generator Timing Diagram

**CPM Electrical Characteristics**

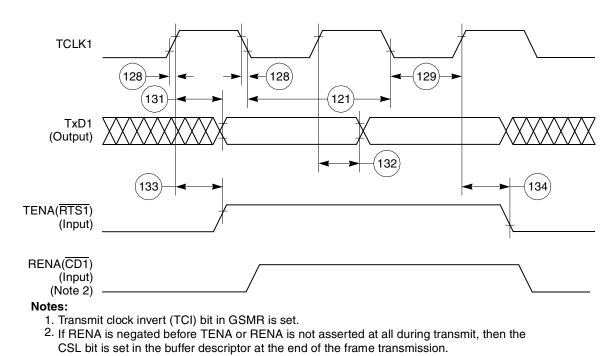

#### SCC in NMSI Mode Electrical Specifications 12.7

Table 22 provides the NMSI external clock timing.

| Num   | Characteristic                                       | All Frequ     | Unit  |      |

|-------|------------------------------------------------------|---------------|-------|------|

| Nulli | Characteristic                                       | Min           | Мах   | Unit |

| 100   | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK     | _     | ns   |

| 101   | RCLK1 and TCLK1 width low                            | 1/SYNCCLK + 5 | _     | ns   |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —             | 15.00 | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00          | 50.00 | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00          | 50.00 | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 5.00          | _     | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 5.00          | _     | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00          | —     | ns   |

| 108   | CD1 setup time to RCLK1 rising edge                  | 5.00          | —     | ns   |

## Table 22. NMSI External Clock Timing

The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

Also applies to CD and CTS hold time when they are used as external sync signals.

## Table 23 provides the NMSI internal clock timing.

## Table 23. NMSI Internal Clock Timing

| Num | Characteristic                                       | All Fre | Unit      |     |

|-----|------------------------------------------------------|---------|-----------|-----|

| Num |                                                      | Min     | Мах       | onn |

| 100 | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00    | SYNCCLK/3 | MHz |

| 102 | RCLK1 and TCLK1 rise/fall time                       | —       | —         | ns  |

| 103 | TXD1 active delay (from TCLK1 falling edge)          | 0.00    | 30.00     | ns  |

| 104 | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00    | 30.00     | ns  |

| 105 | CTS1 setup time to TCLK1 rising edge                 | 40.00   | —         | ns  |

| 106 | RXD1 setup time to RCLK1 rising edge                 | 40.00   | —         | ns  |

| 107 | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00    | —         | ns  |

| 108 | CD1 setup time to RCLK1 rising edge                  | 40.00   | —         | ns  |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{CD}$  and  $\overline{CTS}$  hold time when they are used as external sync signals

Figure 64. Ethernet Transmit Timing Diagram

## **12.9 SMC Transparent AC Electrical Specifications**

Table 25 provides the SMC transparent timings as shown in Figure 65.

| Table 25 | . SMC | Transparent | Timing |

|----------|-------|-------------|--------|

|----------|-------|-------------|--------|

| Num   | Characteristic                               |     | All Frequencies |      |  |

|-------|----------------------------------------------|-----|-----------------|------|--|

| Nulli |                                              |     | Мах             | Unit |  |

| 150   | SMCLK clock period <sup>1</sup>              | 100 | —               | ns   |  |

| 151   | SMCLK width low                              | 50  | —               | ns   |  |

| 151A  | SMCLK width high                             | 50  | —               | ns   |  |

| 152   | SMCLK rise/fall time                         | —   | 15              | ns   |  |

| 153   | SMTXD active delay (from SMCLK falling edge) | 10  | 50              | ns   |  |

| 154   | SMRXD/SMSYNC setup time                      | 20  | —               | ns   |  |

| 155   | RXD1/SMSYNC hold time                        | 5   | —               | ns   |  |

<sup>1</sup> SyncCLK must be at least twice as fast as SMCLK.

### **CPM Electrical Characteristics**

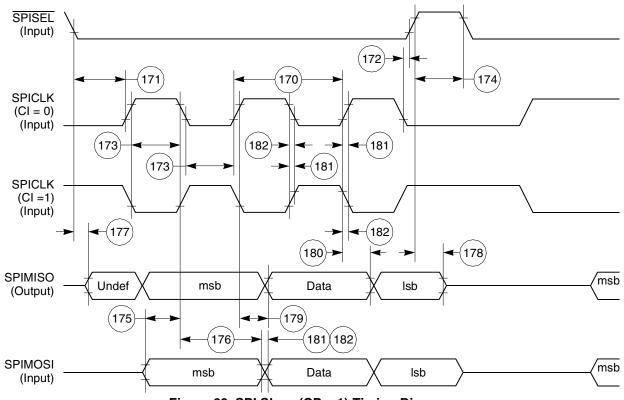

## Figure 69. SPI Slave (CP = 1) Timing Diagram

## 12.12 I<sup>2</sup>C AC Electrical Specifications

Table 28 provides the  $I^2C$  (SCL < 100 kHz) timings.

Table 28.  $I^2C$  Timing (SCL < 100 kHz)

| Num | Characteristic                            | All Freq | Unit |      |

|-----|-------------------------------------------|----------|------|------|

| Num | Cildiacteristic                           | Min      | Max  | Unit |

| 200 | SCL clock frequency (slave)               | 0        | 100  | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100  | kHz  |

| 202 | Bus free time between transmissions       | 4.7      | _    | μs   |

| 203 | Low period of SCL                         | 4.7      | _    | μs   |

| 204 | High period of SCL                        | 4.0      | _    | μs   |

| 205 | Start condition setup time                | 4.7      | _    | μs   |

| 206 | Start condition hold time                 | 4.0      | _    | μs   |

| 207 | Data hold time                            | 0        | _    | μs   |

| 208 | Data setup time                           | 250      | _    | ns   |

| 209 | SDL/SCL rise time                         | —        | 1    | μs   |

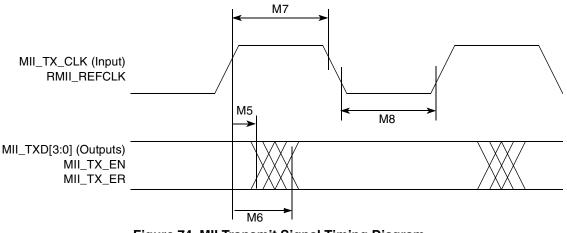

Figure 74 shows the MII transmit signal timing diagram.

Figure 74. MII Transmit Signal Timing Diagram

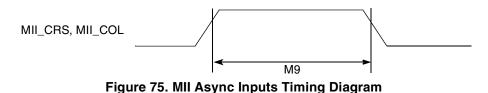

## 15.3 MII Async Inputs Signal Timing (MII\_CRS, MII\_COL)

Table 36 provides information on the MII async inputs signal timing.

## Table 36. MII Async Inputs Signal Timing

| Ĩ | Num | Characteristic                       | Min | Мах | Unit              |

|---|-----|--------------------------------------|-----|-----|-------------------|

|   | M9  | MII_CRS, MII_COL minimum pulse width | 1.5 | —   | MII_TX_CLK period |

Figure 75 shows the MII asynchronous inputs signal timing diagram.

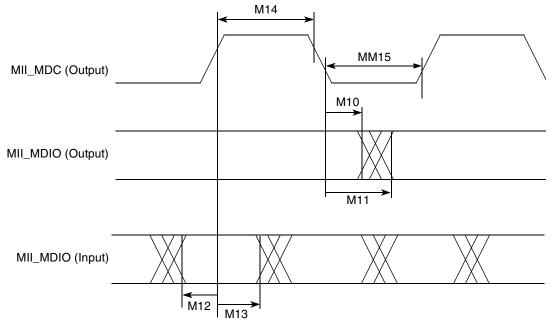

## 15.4 MII Serial Management Channel Timing (MII\_MDIO, MII\_MDC)

Table 37 provides information on the MII serial management channel signal timing. The FEC functions correctly with a maximum MDC frequency in excess of 2.5 MHz.

| Num | Characteristic                                                              | Min | Мах | Unit |

|-----|-----------------------------------------------------------------------------|-----|-----|------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | —   | ns   |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns   |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  |     | ns   |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | _   | ns   |

**FEC Electrical Characteristics**

| Num | Characteristic           | Min | Мах | Unit           |

|-----|--------------------------|-----|-----|----------------|

| M14 | MII_MDC pulse width high | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low  | 40% | 60% | MII_MDC period |

Figure 76 shows the MII serial management channel timing diagram.

Figure 76. MII Serial Management Channel Timing Diagram

## Table 39. Pin Assignments (continued)

| Name                                                                  | Pin Number | Туре                                    |  |  |

|-----------------------------------------------------------------------|------------|-----------------------------------------|--|--|

| PA4, CTS4, MII1-TXD1,<br>RMII1-TXD1                                   | U4         | Bidirectional                           |  |  |

| PA3, MII1-RXER,<br>RMII1-RXER, BRGO3                                  | W2         | Bidirectional                           |  |  |

| PA2, MII1-RXDV,<br>RMII1-CRS_DV, TXD4                                 | T4         | Bidirectional                           |  |  |

| PA1, MII1-RXD0,<br>RMII1-RXD0, BRGO4                                  | U1         | Bidirectional                           |  |  |

| PA0, MII1-RXD1,<br>RMII1-RXD1, TOUT4                                  | U3         | Bidirectional                           |  |  |

| PB31, <del>SPISEL</del> ,<br>MII1-TXCLK,<br>RMII1-REFCLK              | V3         | Bidirectional<br>(Optional: open-drain) |  |  |

| PB30, SPICLK                                                          | P18        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB29, SPIMOSI                                                         | T19        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB28, SPIMISO, BRGO4                                                  | V19        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB27, I2CSDA, BRGO1                                                   | U19        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB26, I2CSCL, BRGO2                                                   | R17        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB25, RXADDR3 <sup>1</sup> ,<br>TXADDR3, SMTXD1                       | V17        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB24, TXADDR3 <sup>1</sup> ,<br>RXADDR3, SMRXD1                       | U16        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB23, TXADDR2 <sup>1</sup> ,<br>RXADDR2, SDACK1,<br>SMSYN1            | W16        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB22, TXADDR4 <sup>1</sup> ,<br>RXADDR4, SDACK2,<br>SMSYN2            | V15        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB21, SMTXD2,<br>TXADDR1 <sup>1</sup> , BRG01,<br>RXADDR1, PHSEL[1]   | U14        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB20, SMRXD2,<br>L1CLKOA, TXADDR0 <sup>1</sup> ,<br>RXADDR0, PHSEL[0] | T13        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB19, MII1-RXD3, RTS4                                                 | V13        | Bidirectional<br>(Optional: open-drain) |  |  |

| PB18, RXADDR4 <sup>1</sup> ,<br>TXADDR4, RTS2, L1ST2                  | T12        | Bidirectional<br>(Optional: open-drain) |  |  |

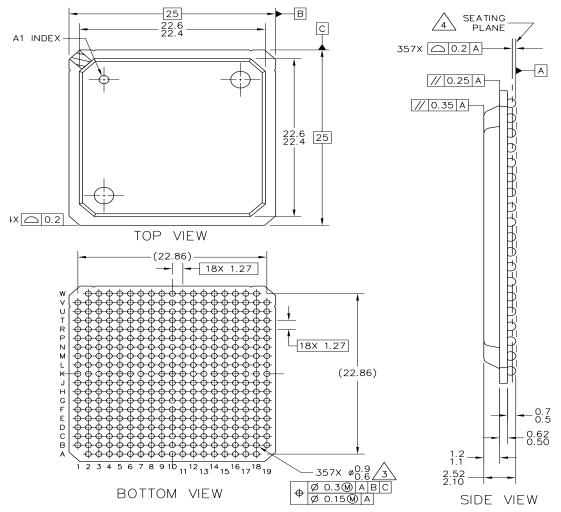

Mechanical Data and Ordering Information

## 16.2 Mechanical Dimensions of the PBGA Package

Figure 78 shows the mechanical dimensions of the PBGA package.

### NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

3. MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

4. DATUM A, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

## Figure 78. Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package