Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                                       |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 528MHz                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SAI, SPDIF, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 127                                                                                            |

| Program Memory Size        | -                                                                                              |

| Program Memory Type        | External Program Memory                                                                        |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 512K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                                      |

| Data Converters            | A/D 20x12b                                                                                     |

| Oscillator Type            | External, Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TJ)                                                                             |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 196-LFBGA                                                                                      |

| Supplier Device Package    | 196-LFBGA (10x10)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mimxrt1051cvl5a                        |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FlexIO1<br>FlexIO2                           | Flexible Input/output               | Connectivity and<br>Communications | The FlexIO is capable of supporting a wide range of<br>protocols including, but not limited to: UART, I2C, SPI,<br>I2S, camera interface, display interface, PWM<br>waveform generation, etc. The module can remain<br>functional when the chip is in a low power mode<br>provided the clock it is using remain active.                                                                       |

|----------------------------------------------|-------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FlexPWM1<br>FlexPWM2<br>FlexPWM3<br>FlexPWM4 | Pulse Width Modulation              | Timer Peripherals                  | The pulse-width modulator (PWM) contains four PWM<br>sub-modules, each of which is set up to control a single<br>half-bridge power stage. Fault channel support is<br>provided. The PWM module can generate various<br>switching patterns, including highly sophisticated<br>waveforms.                                                                                                       |

| FlexRAM                                      | RAM                                 | Memories                           | The i.MX RT1050 has 512 KB of on-chip RAM which<br>could be flexible allocated to I-TCM, D-TCM, and<br>on-chip RAM (OCRAM) in a 32 KB granularity. The<br>FlexRAM is the manager of the 512 KB on-chip RAM<br>array. Major functions of this blocks are: interfacing to<br>I-TCM and D-TCM of Arm core and OCRAM controller;<br>dynamic RAM arrays allocation for I-TCM, D-TCM, and<br>OCRAM. |

| FlexSPI                                      | Quad Serial Peripheral<br>Interface | Connectivity and<br>Communications | FlexSPI acts as an interface to one or two external serial flash devices, each with up to four bidirectional data lines.                                                                                                                                                                                                                                                                      |

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit:

- At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

- Higher accuracy than ring oscillator

- If no external crystal is present, then the ring oscillator is utilized

The decision of choosing a clock source should be taken based on real-time clock use and precision time-out.

### 4.1.5 Maximum supply currents

The data shown in Table 11 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention were to specifically show the worst case power consumption.

See the i.MX RT1050 Power Consumption Measurement Application Note for more details on typical power consumption under various use case definitions.

| Power Rail                                    | Conditions                                                                                                                                                                 | Max Current                                                                                       | Unit |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------|--|

| DCDC_IN                                       | Max power for FF chip at 105 °C                                                                                                                                            | 100                                                                                               | mA   |  |

| VDD_HIGH_IN                                   | Include internal loading in analog                                                                                                                                         | 50                                                                                                | mA   |  |

| VDD_SNVS_IN                                   | —                                                                                                                                                                          | 250                                                                                               | А    |  |

| USB_OTG1_VBUS<br>USB_OTG2_VBUS                | 25 mA for each active USB interface                                                                                                                                        | 50                                                                                                | mA   |  |

| VDDA_ADC_3P3                                  | <ul> <li>3.3 V power supply for 12-bit ADC, 600</li> <li>A typical, 750 A max, for each ADC.</li> <li>100 Ohm max loading for touch panel, cause 33 mA current.</li> </ul> | 40                                                                                                | mA   |  |

| NVCC_GPIO<br>NVCC_SD0<br>NVCC_SD1<br>NVCC_EMC | C—Equivalent external capacitive load<br>V—IO voltage<br>(0.5 x F)—Data change rate. Up to 0.5 of                                                                          | Where:<br>N—Number of IO pins supplied by the power line<br>C—Equivalent external capacitive load |      |  |

Table 11. Maximum supply currents

## NOTE

The currents on the VDD\_HIGH\_CAP and VDD\_USB\_CAP were identified to be the voltage divider circuits in the USB-specific level shifters.

# 4.2 System power and clocks

This section provide the information about the system power and clocks.

## 4.2.1 Power supplies requirements and restrictions

The system design must comply with power-up sequence, power-down sequence, and steady state guidelines as described in this section to guarantee the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the processor (worst-case scenario)

## 4.2.1.1 **Power-up sequence**

The below restrictions must be followed:

- VDD\_SNVS\_IN supply must be turned on before any other power supply or be connected (shorted) with VDD\_HIGH\_IN supply.

- If a coin cell is used to power VDD\_SNVS\_IN, then ensure that it is connected before any other supply is switched on.

- When internal DCDC is enabled, external delay circuit is required to delay the "DCDC\_PSWITCH" signal 1 ms after DCDC\_IN is stable.

- POR\_B should be held low during the entire power up sequence.

### NOTE

The POR\_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the POR\_B input, the internal POR module takes control. See the i.MX RT1050 Reference Manual (IMXRT1050\_RM) for further details and to ensure that all necessary requirements are being met.

### NOTE

Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

## NOTE

USB\_OTG1\_VBUS, USB\_OTG2\_VBUS, and VDDA\_ADC\_3P3 are not part of the power supply sequence and may be powered at any time.

#### i.MX RT1050 Crossover Processors for Industrial Products, Rev. 1, 03/2018

#### **Electrical characteristics**

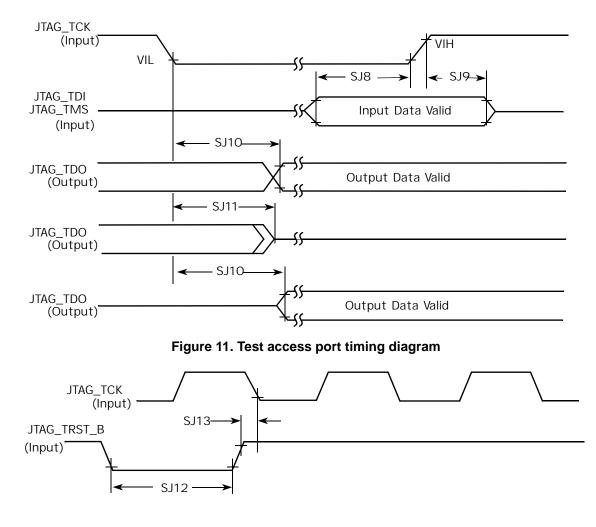

| Table 29 | JTAG | timing |

|----------|------|--------|

|----------|------|--------|

| ID  | Parameter <sup>1,2</sup>                                            | All Freq | Unit |      |

|-----|---------------------------------------------------------------------|----------|------|------|

|     |                                                                     | Min      | Мах  | onit |

| SJ0 | JTAG_TCK frequency of operation 1/(3•T <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22   | MHz  |

| SJ1 | JTAG_TCK cycle time in crystal mode                                 | 45       | —    | ns   |

| SJ2 | JTAG_TCK clock pulse width measured at $V_M^2$                      | 22.5     | —    | ns   |

| SJ3 | JTAG_TCK rise and fall times                                        | —        | 3    | ns   |

| SJ4 | Boundary scan input data set-up time                                | 5        | —    | ns   |

| SJ5 | Boundary scan input data hold time                                  | 24       | —    | ns   |

| SJ6 | JTAG_TCK low to output data valid                                   | —        | 40   | ns   |

| SJ7 | JTAG_TCK low to output high impedance                               | —        | 40   | ns   |

| SJ8 | JTAG_TMS, JTAG_TDI data set-up time                                 | 5        | —    | ns   |

#### i.MX RT1050 Crossover Processors for Industrial Products, Rev. 1, 03/2018

#### **Electrical characteristics**

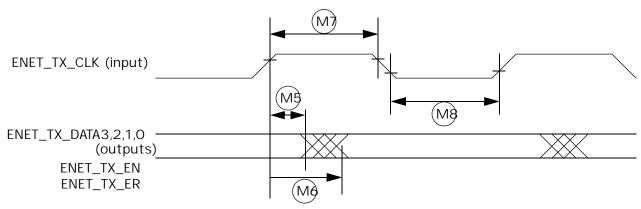

Figure 43 shows MII traints signal timing suble 63 describes the timing openators (M5 M8) shown in the figure.

Figure 43. MII transmit signal timing diagram

Table 63. MII transmit signal timing

| ID | Characteristic <sup>1</sup>                                           | Min. | Max. | Unit               |

|----|-----------------------------------------------------------------------|------|------|--------------------|

| M5 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER invalid | 5    | —    | ns                 |

| M6 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER valid   | —    | 20   | ns                 |

| M7 | ENET_TX_CLK pulse width high                                          | 35%  | 65%  | ENET_TX_CLK period |

| M8 | ENET_TX_CLK pulse width low                                           | 35%  | 65%  | ENET_TX_CLK period |

<sup>1</sup> ENET\_TX\_EN, ENET\_TX\_CLK, and ENET0\_TXD0 have the same timing in 10-Mbps 7-wire interface mode.

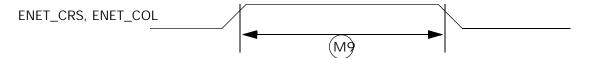

### 4.9.4.1.3 MII asynchronous inputs signal timing (ENET\_CRS and ENET\_COL)

Figure 44 shows MII asynchronous input til and the scribes the timing operator (M9) shown in the figure.

Figure 44. MII asynchronous inputs timing diagram

| ID              | Characteristic                           | Min. | Max. | Unit               |

|-----------------|------------------------------------------|------|------|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5  | _    | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.