Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 4              | -4. 000    | STAT: USCILL                                                  | AIUN SIA   | I US REGIST       |                    |                 |               |

|-------------------------|------------|---------------------------------------------------------------|------------|-------------------|--------------------|-----------------|---------------|

| R-q/q                   | R-q/q      | R-q/q                                                         | R-q/q      | R-q/q             | R-q/q              | U-0             | R-q/q         |

| EXTOR                   | HFOR       | MFOR                                                          | LFOR       | SOR               | ADOR               | _               | PLLR          |

| bit 7                   |            |                                                               |            |                   |                    |                 | bit           |

| Louand                  |            |                                                               |            |                   |                    |                 |               |

| Legend:<br>R = Readable | hit        | W = Writable                                                  | h it       |                   | mantad hit raad    | aa 'O'          |               |

|                         |            |                                                               |            |                   | mented bit, read   |                 | ath an Daaata |

| u = Bit is unch         | angeo      | x = Bit is unki                                               |            |                   | at POR and BOI     |                 |               |

| '1' = Bit is set        |            | '0' = Bit is cle                                              | ared       | q = Reset va      | lue is determine   | d by hardware   | 9             |

| bit 7                   | 1 = The o  | TOSC (external<br>scillator is ready<br>scillator is not en   | to be used |                   | be used            |                 |               |

| bit 6                   | 1 = The o  | NTOSC Oscillato<br>scillator is ready<br>scillator is not en  | to be used | ot yet ready to b | be used            |                 |               |

| bit 5                   | 1 = The os | INTOSC Oscillat<br>scillator is ready<br>scillator is not en  | to be used | ot yet ready to b | be used            |                 |               |

| bit 4                   | 1 = The o  | NTOSC Oscillato<br>scillator is ready<br>scillator is not en  | to be used | it yet ready to b | be used            |                 |               |

| bit 3                   | 1 = The o  | ndary (Timer1) C<br>scillator is ready<br>scillator is not er | to be used | -                 | be used            |                 |               |

| bit 2                   | 1 = The o  | C Oscillator Rea<br>scillator is ready<br>scillator is not er | to be used | ot yet ready to   | be used            |                 |               |

| bit 1                   | Unimpleme  | ented: Read as '                                              | 0'         | · -               |                    |                 |               |

| bit 0                   | 1 = The F  | is Ready bit<br>PLL is ready to be<br>LL is not enabled       |            | l input source is | s not ready, or th | e PLL is not lo | ocked.        |

#### REGISTER 4-4: OSCSTAT: OSCILLATOR STATUS REGISTER 1

| U-0 I           | R/W <sup>(3)</sup> -q/q <sup>(1)</sup>                       | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | U-0                                                   | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |  |

|-----------------|--------------------------------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--|

| —               |                                                              | WDTCS<2:0>                             |                                        | -                                                     |                                        | WINDOW<2:0>                            |                                        |  |

| bit 7           |                                                              |                                        |                                        |                                                       |                                        |                                        | bit 0                                  |  |

|                 |                                                              |                                        |                                        |                                                       |                                        |                                        |                                        |  |

| Legend:         |                                                              |                                        |                                        |                                                       |                                        |                                        |                                        |  |

| R = Readable    | able bit W = Writable bit U = Unimplemented bit, read as '0' |                                        | U = Unimplemented bit, read as '0'     |                                                       |                                        |                                        |                                        |  |

| u = Bit is unch | nanged                                                       | x = Bit is unk                         | nown                                   | -n/n = Value at POR and BOR/Value at all other Resets |                                        |                                        |                                        |  |

q = Value depends on condition

#### REGISTER 9-2: WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1

| bit 7 | Unimplemented: Read as '0' |

|-------|----------------------------|

|       | Unimplemented. Read as 0   |

'1' = Bit is set

bit 6-4 WDTCS<2:0>: Watchdog Timer Clock Select bits

'0' = Bit is cleared

- 111 = Reserved

- •

- •

- 010 = Reserved

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

- bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 62.5                            | 37.5                              |

| 001         | 75                              | 25                                |

| 000         | 87.5                            | 12.5                              |

- Note 1: If WDTCCS <2:0> in CONFIG3H = 111, the Reset value of WDTCS<2:0> is 000.

- 2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3H register.

- **3:** If WDTCCS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

- 4: If WDTCWS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

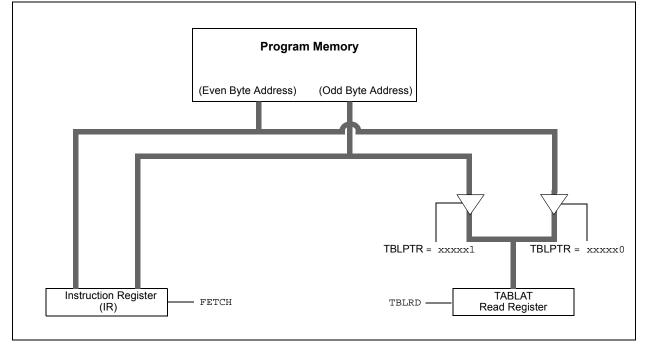

#### 11.1.3 READING THE PROGRAM FLASH MEMORY

The TBLRD instruction retrieves data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The CPU operation is suspended during the read, and it resumes immediately after. From the user point of view, TABLAT is valid in the next instruction cycle.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 11-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 11-4: READS FROM PROGRAM FLASH MEMORY

#### EXAMPLE 11-1: READING A PROGRAM FLASH MEMORY WORD

| MOVLW   | CODE_ADDR_UPPER                                                                  | ;                                                                                                                                                                            | Load TBLPTR with the base                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF   | TBLPTRU                                                                          | ;                                                                                                                                                                            | address of the word                                                                                                                                                                    |

| MOVLW   | CODE_ADDR_HIGH                                                                   |                                                                                                                                                                              |                                                                                                                                                                                        |

| MOVWF   | TBLPTRH                                                                          |                                                                                                                                                                              |                                                                                                                                                                                        |

| MOVLW   | CODE_ADDR_LOW                                                                    |                                                                                                                                                                              |                                                                                                                                                                                        |

| MOVWF   | TBLPTRL                                                                          |                                                                                                                                                                              |                                                                                                                                                                                        |

|         |                                                                                  |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+ |                                                                                  | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVF    | TABLAT, W                                                                        | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVWF   | WORD_EVEN                                                                        |                                                                                                                                                                              |                                                                                                                                                                                        |

| TBLRD*+ |                                                                                  | ;                                                                                                                                                                            | read into TABLAT and increment                                                                                                                                                         |

| MOVFW   | TABLAT, W                                                                        | ;                                                                                                                                                                            | get data                                                                                                                                                                               |

| MOVF    | WORD ODD                                                                         |                                                                                                                                                                              |                                                                                                                                                                                        |

|         | MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>TBLRD*+<br>MOVF<br>TBLRD*+<br>MOVFW | MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+<br>MOVF TABLAT, W<br>MOVWF WORD_EVEN<br>TBLRD*+<br>MOVFW TABLAT, W | MOVWF TBLPTRU ;<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL<br>TBLRD*+ ;<br>MOVF TABLAT, W ;<br>MOVWF WORD_EVEN<br>TBLRD*+ ;<br>MOVFW TABLAT, W ; |

#### 11.3 Data EEPROM Memory

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, which is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- NVMCON1

- NVMCON2

- NVMDAT

- NVMADRL

- NVMADRH(1)

Note 1: NVMADRH register is not implemented on PIC18(L)F45K40.

The data EEPROM allows byte read and write. When interfacing to the data memory block, NVMDAT holds the 8-bit data for read/write and the NVMADRH:NVMADRL register pair hold the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an internal programming timer; it will vary with voltage and temperature as well as from chip-to-chip. Please refer to the Data EEPROM Memory parameters in **Section 37.0 "Electrical Specifications"** for limits.

#### 11.3.1 NVMADRL AND NVMADRH REGISTERS

The NVMADRH:NVMADRL registers are used to address the data EEPROM for read and write operations.

#### 11.3.2 NVMCON1 AND NVMCON2 REGISTERS

Access to the data EEPROM is controlled by two registers: NVMCON1 and NVMCON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The NVMCON1 register (Register 11-1) is the control register for data and program memory access. Control bits NVMREG<1:0> determine if the access will be to program, Data EEPROM Memory or the User IDs, Configuration bits, Revision ID and Device ID.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

The WR control bit initiates write operations. The bit can be set but not cleared by software. It is cleared only by hardware at the completion of the write operation.

The NVMIF interrupt flag bit of the PIR7 register is set when the write is complete. It must be cleared by software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (NVMREG<1:0> = 0x10). Program memory is read using table read instructions. See **Section 11.1.1 "Table Reads and Table Writes"** regarding table reads.

#### 16.6 Register Definitions: Interrupt-on-Change Control

| R/W-0/0                                 | R/W-0/0 | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------------------------|---------|-------------------------------------------------------|------------------------------------|---------|---------|---------|---------|

| IOCxP7                                  | IOCxP6  | IOCxP5                                                | IOCxP4                             | IOCxP3  | IOCxP2  | IOCxP1  | IOCxP0  |

| bit 7                                   |         |                                                       | •                                  |         |         |         | bit 0   |

|                                         |         |                                                       |                                    |         |         |         |         |

| Legend:                                 |         |                                                       |                                    |         |         |         |         |

| R = Readable bit W = Writable bit       |         |                                                       | U = Unimplemented bit, read as '0' |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |         |

| '1' = Bit is set                        |         | '0' = Bit is clear                                    | ed                                 |         |         |         |         |

#### **REGISTER 16-1: IOCxP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER EXAMPLE**

bit 7-0

IOCxP<7:0>: Interrupt-on-Change Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a positive-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 16-2: IOCxN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER EXAMPLE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCxN7  | IOCxN6  | IOCxN5  | IOCxN4  | IOCxN3  | IOCxN2  | IOCxN1  | IOCxN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCxN<7:0>: Interrupt-on-Change Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a negative-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 16-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER EXAMPLE

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCxF7     | IOCxF6     | IOCxF5     | IOCxF4     | IOCxF3     | IOCxF2     | IOCxF1     | IOCxF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCxF<7:0>: Interrupt-on-Change Flag bits

1 = A enabled change was detected on the associated pin. Set when IOCP[n] = 1 and a positive edge was detected on the IOCn pin, or when IOCN[n] = 1 and a negative edge was detected on the IOCn pin

0 = No change was detected, or the user cleared the detected change

#### REGISTER 18-3: TMR0L: TIMER0 COUNT REGISTER

|                  | ••••••• |                   |         |                                                  |                  |          |              |

|------------------|---------|-------------------|---------|--------------------------------------------------|------------------|----------|--------------|

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                          | R/W-0/0          | R/W-0/0  | R/W-0/0      |

|                  |         |                   | TMR     | 0<7:0>                                           |                  |          |              |

| bit 7            |         |                   |         |                                                  |                  |          | bit 0        |

|                  |         |                   |         |                                                  |                  |          |              |

| Legend:          |         |                   |         |                                                  |                  |          |              |

| R = Readable b   | bit     | W = Writable      | bit     | U = Unimpler                                     | mented bit, read | l as '0' |              |

| u = Bit is uncha | inged   | x = Bit is unkr   | nown    | -n/n = Value at POR and BOR/Value at all other F |                  |          | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                  |                  |          |              |

bit 7-0 TMR0<7:0>:TMR0 Counter bits <7:0>

#### REGISTER 18-4: TMR0H: TIMER0 PERIOD REGISTER

| R/W-1/1 | R/W-1/1    | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|

|         | TMR0<15:8> |         |         |         |         |         |         |  |

| bit 7   |            |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 When T016BIT = 0 PR0<7:0>:TMR0 Period Register Bits <7:0> When T016BIT = 1 TMR0<15:8>: TMR0 Counter bits <15:8>

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name            | Bit 7      | Bit 6     | Bit 5  | Bit 4               | Bit 3                | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------|------------|-----------|--------|---------------------|----------------------|-----------|---------|---------|---------------------|

| TMR0L           | TMR0<7:0>  |           |        |                     |                      |           |         |         | 226                 |

| TMR0H           | TMR0<15:8> |           |        |                     |                      |           | 226     |         |                     |

| T0CON0          | T0EN       | —         | TOOUT  | T016BIT             | T016BIT T0OUTPS<3:0> |           |         |         |                     |

| T0CON1          |            | T0CS<2:0> |        | T0ASYNC T0CKPS<3:0> |                      |           |         |         | 225                 |

| <b>T0CKIPPS</b> | —          | —         | —      | T0CKIPPS<4:0>       |                      |           |         |         | 216                 |

| TMR0PPS         | _          | —         | _      |                     | TMRC                 | )PPS<4:0> |         |         | 216                 |

| INTCON          | GIE/GIEH   | PEIE/GIEL | IPEN   | —                   | —                    | INT2EDG   | INT1EDG | INT0EDG | 170                 |

| PIR0            | —          | —         | TMR0IF | IOCIF               | —                    | INT2IF    | INT1IF  | INT0IF  | 171                 |

| PIE0            | —          | —         | TMR0IE | IOCIE               | _                    | INT2IE    | INT1IE  | INT0IE  | 179                 |

| IPR0            | —          | —         | TMR0IP | IOCIP               | —                    | INT2IP    | INT1IP  | INT0IP  | 187                 |

| PMD1            | _          | TMR6MD    | TMR5MD | TMR4MD              | TMR3MD               | TMR2MD    | TMR1MD  | TMR0MD  | 69                  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

© 2015-2017 Microchip Technology Inc.

#### REGISTER 19-5: TMRxL: TIMERx LOW BYTE REGISTER

| R/W-x/x          | R/W-x/x | R/W-x/x            | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|------------------|---------|--------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                    | TMR     | «L<7:0>        |                  |                  |             |

| bit 7            |         |                    |         |                |                  |                  | bit 0       |

|                  |         |                    |         |                |                  |                  |             |

| Legend:          |         |                    |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable bit   |         | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unknown |         | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                |                  |                  |             |

bit 7-0 TMRxL<7:0>:Timerx Low Byte bits

#### **REGISTER 19-6: TMRxH: TIMERx HIGH BYTE REGISTER**

| R/W-x/x | R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|

|         | TMRxH<7:0> |         |         |         |         |         |         |  |

| bit 7   |            |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>:Timerx High Byte bits

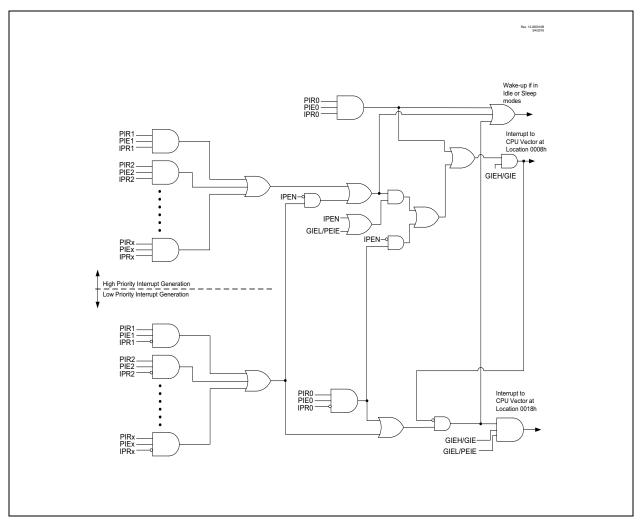

#### FIGURE 21-4: SIMPLIFIED PWM BLOCK DIAGRAM

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |  |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|--|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |  |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |  |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |  |

#### TABLE 21-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

#### TABLE 21-4:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 21.5.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 21.5.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 21.5.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

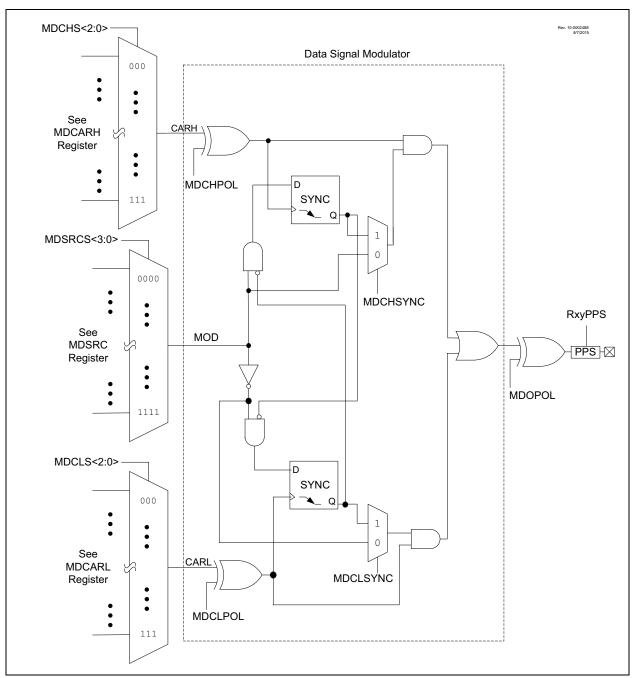

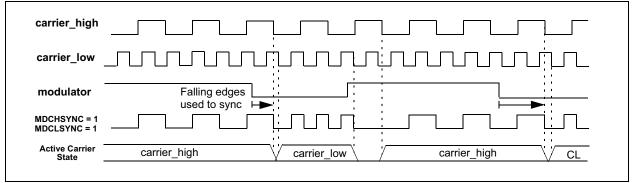

| FIGURE 25-5:                 | Carrier Low Synchronization (MDSHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| carrier_high                 |                                                          |

| carrier_low                  |                                                          |

| modulator                    |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State      | carrier_high                                             |

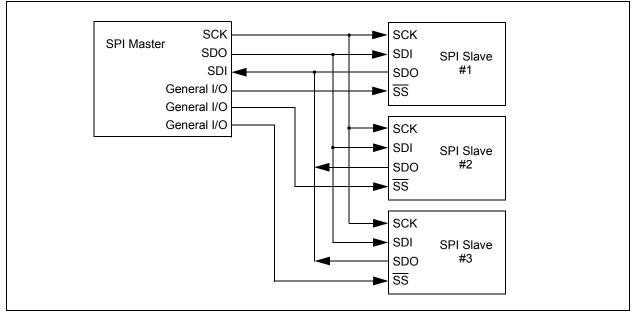

#### 26.3 SPI Mode Registers

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 26.11 "Baud Rate Generator"**.

SSPSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPxBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPSR.

© 2015-2017 Microchip Technology Inc.

#### 27.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 27.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 27.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode.

If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXxREG register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXxIF bit will now be set.

- 5. If the PEIE and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 27.5.2.2 Synchronous Slave Transmission Setup

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CKx pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

### 31.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Result formatting

- Conversion Trigger Selection

- ADC Acquisition Time

- ADC Precharge Time

- Additional Sample and Hold Capacitor

- Single/Double Sample Conversion

- Guard Ring Outputs

#### 31.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 15.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 31.1.2 CHANNEL SELECTION

There are several channel selections available:

- Eight PORTA pins (RA<7:0>)

- Eight PORTB pins (RB<7:0>)

- Eight PORTC pins (RC<7:0>)

- Eight PORTD pins (RD<7:0>), PIC18(L)F45/46K40 only)

- Three PORTE pins (RE<2:0>), PIC18(L)F45/46K40 only)

- Temperature Indicator

- DAC output

- Fixed Voltage Reference (FVR)

- AVss (ground)

The ADPCH register determines which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. 0

Refer to **Section 31.2 "ADC Operation**" for more information.

Note: It is recommended that when switching from an ADC channel of a higher voltage to a channel of a lower voltage, the software selects the Vss channel before switching. If the ADC does not have a dedicated Vss input channel, the Vss selection (DAC1R<4:0> = b'00000') through the DAC output channel can be used. If the DAC is in use, a free input channel can be connected to Vss, and can be used in place of the DAC.

#### REGISTER 31-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|---------|-----|-----|-----|-----|---------|

| ADPPOL  | ADIPEN  | ADGPOL  | -   | —   | -   | _   | ADDSEN  |

| bit 7   |         |         |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7 ADDPOL: Precharge Polarity bit If ADPRE>0x00:

| ADPPOL | Action During 1st Precharge Stage  |                                   |  |  |  |  |

|--------|------------------------------------|-----------------------------------|--|--|--|--|

| ADFFOL | External (selected analog I/O pin) | Internal (AD sampling capacitor)  |  |  |  |  |

| 1      | Shorted to AVDD                    | C <sub>HOLD</sub> shorted to Vss  |  |  |  |  |

| 0      | Shorted to Vss                     | C <sub>HOLD</sub> shorted to AVDD |  |  |  |  |

- Otherwise:

- The bit is ignored

#### bit 6 ADIPEN: A/D Inverted Precharge Enable bit

- If ADDSEN = 1

- 1 = The precharge and guard signals in the second conversion cycle are the opposite polarity of the first cycle

- 0 = Both Conversion cycles use the precharge and guards specified by ADPPOL and ADGPOL

#### Otherwise:

The bit is ignored

#### bit 5 ADGPOL: Guard Ring Polarity Selection bit

- 1 = ADC guard Ring outputs start as digital high during Precharge stage

- 0 = ADC guard Ring outputs start as digital low during Precharge stage

#### bit 4-1 Unimplemented: Read as '0'

#### bit 0 ADDSEN: Double-sample enable bit

- 1 = Two conversions are performed on each trigger. Data from the first conversion appears in ADPREV

- 0 = One conversion is performed for each trigger

#### **REGISTER 31-19:** ADRESL: ADC RESULT REGISTER LOW, ADFM = 1

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<7:0>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits. Lower eight bits of 10-bit conversion result.

#### REGISTER 31-20: ADPREVH: ADC PREVIOUS RESULT REGISTER

| R-x   | R-x | R-x | R-x   | R-x     | R-x | R-x | R-x   |

|-------|-----|-----|-------|---------|-----|-----|-------|

|       |     |     | ADPRE | /<15:8> |     |     |       |

| bit 7 |     |     |       |         |     |     | bit 0 |

|       |     |     |       |         |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADPREV<15:8>: Previous ADC Results bits If ADPSIS = 1: Upper byte of ADFLTR at the start of current ADC conversion If ADPSIS = 0: Upper bits of ADRES at the start of current ADC conversion<sup>(1)</sup>

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the ADFM bit.

| ANDWF                                                    | AND W w                                                                                                                                                                                    | ith f                                                                                                                                                                      |                                                                                                                                                                            | BC                                                           | Branch i                                                                                                                         | f Carry                                                                                                        |                                                                         |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Syntax:                                                  | ANDWF                                                                                                                                                                                      | f {,d {,a}}                                                                                                                                                                |                                                                                                                                                                            | Syntax:                                                      | BC n                                                                                                                             |                                                                                                                |                                                                         |

| Operands:                                                | $0 \le f \le 255$                                                                                                                                                                          |                                                                                                                                                                            |                                                                                                                                                                            | Operands:                                                    | -128 ≤ n ≤                                                                                                                       | 127                                                                                                            |                                                                         |

|                                                          | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                     |                                                                                                                                                                            |                                                                                                                                                                            | Operation:                                                   | if CARRY<br>(PC) + 2 +                                                                                                           |                                                                                                                |                                                                         |

| Operation:                                               | (W) .AND.                                                                                                                                                                                  | (f) $\rightarrow$ dest                                                                                                                                                     |                                                                                                                                                                            | Status Affected                                              | l: None                                                                                                                          |                                                                                                                |                                                                         |

| Status Affected:                                         | N, Z                                                                                                                                                                                       |                                                                                                                                                                            |                                                                                                                                                                            | Encoding:                                                    | 1110                                                                                                                             | 0010 nn:                                                                                                       | nn nnnn                                                                 |

| Encoding:<br>Description:                                | register 'f'.<br>in W. If 'd' is<br>in register '<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br><b>tion 35.2.3</b> | s '1', the result<br>f' (default).<br>he Access Ba<br>he BSR is use<br>nd the extend<br>led, this instru<br>Literal Offset /<br>never $f \le 95$ (5<br><b>"Byte-Orient</b> | ND'ed with<br>result is stored<br>is stored back<br>nk is selected.<br>ed to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See Sec-<br>red and Bit- | Words:<br>Cycles:<br>Q Cycle Activi<br>If Jump:              | If the CAR<br>will branch<br>The 2's co<br>added to the<br>incrementer<br>instruction<br>PC + 2 + 2<br>2-cycle inst<br>1<br>1(2) | RY bit is '1', the<br>mplement num<br>he PC. Since the<br>ed to fetch the<br>the new addre<br>n. This instruct | en the program<br>ber '2n' is<br>le PC will have<br>next<br>ess will be |

|                                                          |                                                                                                                                                                                            | Mode" for de                                                                                                                                                               | Indexed Lit-                                                                                                                                                               | Q1                                                           | Q2                                                                                                                               | Q3                                                                                                             | Q4                                                                      |

| Words:                                                   | 1                                                                                                                                                                                          |                                                                                                                                                                            |                                                                                                                                                                            | Decod                                                        | e Read literal<br>'n'                                                                                                            | Process<br>Data                                                                                                | Write to PC                                                             |

| Cycles:                                                  | 1                                                                                                                                                                                          |                                                                                                                                                                            |                                                                                                                                                                            | No                                                           | No                                                                                                                               | No                                                                                                             | No                                                                      |

| Q Cycle Activity:                                        | ·                                                                                                                                                                                          |                                                                                                                                                                            |                                                                                                                                                                            | operatio                                                     |                                                                                                                                  | operation                                                                                                      | operation                                                               |

| Q1                                                       | Q2                                                                                                                                                                                         | Q3                                                                                                                                                                         | Q4                                                                                                                                                                         | If No Jump:                                                  |                                                                                                                                  |                                                                                                                |                                                                         |

| Decode                                                   | Read                                                                                                                                                                                       | Process                                                                                                                                                                    | Write to                                                                                                                                                                   | Q1                                                           | Q2                                                                                                                               | Q3                                                                                                             | Q4                                                                      |

|                                                          | register 'f'                                                                                                                                                                               | Data                                                                                                                                                                       | destination                                                                                                                                                                | Decod                                                        | e Read literal<br>'n'                                                                                                            | Process<br>Data                                                                                                | No<br>operation                                                         |

| Example:<br>Before Instru<br>W<br>REG<br>After Instructi | = 17h<br>= C2h                                                                                                                                                                             | REG, 0, 0                                                                                                                                                                  |                                                                                                                                                                            | <u>Example</u> :<br>Before Ins<br>PC<br>After Instr<br>If CA | = ac<br>uction<br>\RRY = 1                                                                                                       | BC 5                                                                                                           |                                                                         |

| GOTO                             | Uncondit                                                                                                                                     | ional Branc           | h                                                                                                                                                                                                                                                                          | INCF                                                                                                                                                                             | Incremen                                      | tf             |           |                                                                                                                                       |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                          | GOTO k                                                                                                                                       |                       |                                                                                                                                                                                                                                                                            | Syntax:                                                                                                                                                                          | INCF f{,c                                     | 1 {,a}}        |           |                                                                                                                                       |  |

| Operands:                        | $0 \le k \le 104$                                                                                                                            | 8575                  |                                                                                                                                                                                                                                                                            | Operands:                                                                                                                                                                        | $0 \leq f \leq 255$                           |                |           |                                                                                                                                       |  |

| Operation:                       | $k \rightarrow PC<20$                                                                                                                        | ):1>                  |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  | d ∈ [0,1]                                     |                |           |                                                                                                                                       |  |

| Status Affected:                 | None                                                                                                                                         |                       |                                                                                                                                                                                                                                                                            | Operation:                                                                                                                                                                       | a ∈ [0,1]<br>(f) + 1 → d                      | oot            |           | result is<br>result is<br>efault).<br>is selected<br>o select the<br>instruction<br>in operate:<br>lressing<br>b. See Sec<br>and Bit- |  |

| Encoding:                        |                                                                                                                                              |                       |                                                                                                                                                                                                                                                                            | Status Affected:                                                                                                                                                                 | (f) + 1 $\rightarrow$ dest<br>C, DC, N, OV, Z |                |           |                                                                                                                                       |  |

| 1st word (k<7:0>)                |                                                                                                                                              | 1111 k <sub>7</sub> k | 0                                                                                                                                                                                                                                                                          |                                                                                                                                                                                  |                                               |                |           |                                                                                                                                       |  |

| 2nd word(k<19:8><br>Description: | ,                                                                                                                                            | 17                    | .9kkk kkkk kkkk kkkk   an unconditional branch Description: 10da ffff ffff   hin entire Incoding: Description: The contents of register 'f' are incremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). |                                                                                                                                                                                  |                                               |                |           |                                                                                                                                       |  |

|                                  | anywhere within entire<br>2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a 2-cycle<br>instruction. |                       |                                                                                                                                                                                                                                                                            | placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select th |                                               |                |           |                                                                                                                                       |  |

| Words:                           | 2                                                                                                                                            |                       |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  | GPR bank.<br>If 'a' is '0' a                  |                | ended ir  | o select the                                                                                                                          |  |

| Cycles:                          | 2                                                                                                                                            |                       |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  | set is enab                                   | led, this ins  | struction | operates                                                                                                                              |  |

| Q Cycle Activity:                |                                                                                                                                              |                       |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  | in Indexed                                    |                |           | •                                                                                                                                     |  |

| Q1                               | Q2                                                                                                                                           | Q3                    | Q4                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |                                               |                | • •       |                                                                                                                                       |  |

| Decode                           | Read literal<br>'k'<7:0>,                                                                                                                    | No<br>operation       | Read literal<br>'k'<19:8>,<br>Write to PC                                                                                                                                                                                                                                  |                                                                                                                                                                                  | Oriented In<br>eral Offset                    | nstruction     | s in Ind  | lexed Lit-                                                                                                                            |  |

| No                               | No                                                                                                                                           | No                    | No                                                                                                                                                                                                                                                                         | Words:                                                                                                                                                                           | 1                                             |                |           |                                                                                                                                       |  |

| operation                        | operation                                                                                                                                    | operation             | operation                                                                                                                                                                                                                                                                  | Cycles:                                                                                                                                                                          | 1                                             |                |           |                                                                                                                                       |  |

|                                  |                                                                                                                                              |                       |                                                                                                                                                                                                                                                                            | Q Cycle Activity:                                                                                                                                                                |                                               |                |           |                                                                                                                                       |  |