#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F26K40) (CONTINUED)

| IADLE              | 1. 20                    |               | LOOAI            |           | 1010(L)        | 1 201140)                                                          | (00111                       | NOLD,                            |     |           |                                                                                              |     |                                              |         |                 |

|--------------------|--------------------------|---------------|------------------|-----------|----------------|--------------------------------------------------------------------|------------------------------|----------------------------------|-----|-----------|----------------------------------------------------------------------------------------------|-----|----------------------------------------------|---------|-----------------|

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin (U)QFN | A/D              | Reference | Comparator     | Timers                                                             | CCP                          | CWG                              | ZCD | Interrupt | EUSART                                                                                       | MSQ | MSSP                                         | Pull-up | Basic           |

| RC0                | 11                       | 8             | ANC0             | Ι         | —              | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup> | _                            |                                  | -   | IOCC0     |                                                                                              | _   | _                                            | Y       | SOSCO           |

| RC1                | 12                       | 9             | ANC1             | _         | —              | —                                                                  | CCP2 <sup>(1)</sup>          | —                                | _   | IOCC1     | —                                                                                            | _   | —                                            | Y       | SOSCIN<br>SOSCI |

| RC2                | 13                       | 10            | ANC2             | _         | _              | T5CKI <sup>(1)</sup>                                               | CCP1 <sup>(1)</sup>          | _                                | _   | IOCC2     | _                                                                                            | _   | _                                            | Y       | _               |

| RC3                | 14                       | 11            | ANC3             | _         | —              | T2AIN <sup>(1)</sup>                                               | —                            | —                                | _   | IOCC3     | —                                                                                            | _   | SCK1 <sup>(1)</sup><br>SCL1 <sup>(3,4)</sup> | Y       | _               |

| RC4                | 15                       | 12            | ANC4             | _         | _              | —                                                                  | —                            | —                                | —   | IOCC4     | —                                                                                            | _   | SDI1 <sup>(1)</sup><br>SDA1 <sup>(3,4)</sup> | Y       | —               |

| RC5                | 16                       | 13            | ANC5             | _         | _              | T4AIN <sup>(1)</sup>                                               | _                            | _                                | —   | IOCC5     | —                                                                                            | _   | —                                            | Y       | _               |

| RC6                | 17                       | 14            | ANC6             | _         | _              | _                                                                  | _                            | _                                | _   | IOCC6     | CK1 <sup>(1)</sup>                                                                           | _   | —                                            | Y       | _               |

| RC7                | 18                       | 15            | ANC7             |           | _              | _                                                                  | —                            | _                                | —   | IOCC7     | RX1/DT1 <sup>(1)</sup>                                                                       | —   | —                                            | Y       | _               |

| RE3                | 1                        | 26            | —                | —         | _              | _                                                                  | _                            | _                                | —   | IOCE3     | _                                                                                            | _   | —                                            | Y       | VPP/MCLR        |

| Vss                | 19                       | 16            | —                | —         | _              | —                                                                  | —                            | —                                | —   | —         | —                                                                                            | _   | —                                            | _       | Vss             |

| VDD                | 20                       | 17            | _                | _         | —              | —                                                                  | —                            | _                                | —   | —         | —                                                                                            | —   | —                                            | _       | Vdd             |

| Vss                | 8                        | 5             | —                | —         | _              | —                                                                  | —                            | —                                | —   | —         | —                                                                                            | _   | —                                            | _       | Vss             |

| OUT <sup>(2)</sup> | _                        | —             | ADGRDA<br>ADGRDB | Ι         | C1OUT<br>C2OUT | TMR0                                                               | CCP1<br>CCP2<br>PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | _   | _         | TX1/CK1 <sup>(3)</sup><br>DT1 <sup>(3)</sup><br>TX2/CK2 <sup>(3)</sup><br>DT2 <sup>(3)</sup> | DSM | SDO1<br>SCK1<br>SDO2<br>SCK2                 | _       | _               |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I<sup>2</sup>C logic levels; The SCL/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18(L)F26/45/46K40 MICROCONTROLLERS

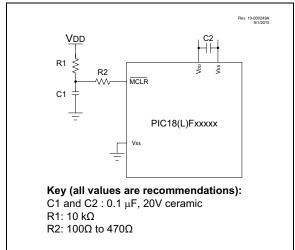

# 2.1 Basic Connection Requirements

Getting started with the PIC18(L)F26/45/46K40 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP<sup>™</sup> Pins"**)

- OSCI and OSCO pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

# 2.2 Power Supply Pins

# 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and VSS) is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

# 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 7.5 Register Definitions: Peripheral Module Disable

| R/W-0/0                 | R/W-0/0                         | R/W-0/0                                                                            | R/W-0/0                        | R/W-0/0                                       | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-------------------------|---------------------------------|------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|------------------|------------------|--------------|

| SYSCMD                  | FVRMD                           | HLVDMD                                                                             | CRCMD                          | SCANMD                                        | NVMMD            | CLKRMD           | IOCMD        |

| 7                       | •                               | •                                                                                  | •                              | •                                             |                  | •                |              |

|                         |                                 |                                                                                    |                                |                                               |                  |                  |              |

| Legend:<br>R = Readable | , hit                           | W = Writable                                                                       | hit                            | II – Unimplor                                 | nented bit, read |                  |              |

| u = Bit is uncl         |                                 | x = Bit is unkn                                                                    |                                | •                                             |                  | R/Value at all o | thar Pasata  |

| '1' = Bit is set        | •                               | 0' = Bit is clear                                                                  |                                |                                               |                  |                  |              |

|                         |                                 |                                                                                    | areu                           | q – value dep                                 | ends on condi    |                  |              |

| bit 7                   | See descript<br>1 = System      | isable Periphera<br>ion in <b>Section 7</b><br>clock network di<br>clock network e | .4 "System Cl<br>sabled (Fosc) | k Network bit <sup>(1)</sup><br>ock Disable". |                  |                  |              |

| bit 6                   | 1 = FVR mo                      | able Fixed Volta<br>dule disabled<br>dule enabled                                  | ge Reference                   | bit                                           |                  |                  |              |

| bit 5                   | 1 = HLVD m                      | isable Low-Volta<br>nodule disabled<br>nodule enabled                              | ige Detect bit                 |                                               |                  |                  |              |

| bit 4                   | 1 = CRC mc                      | able CRC Engir<br>odule disabled<br>odule enabled                                  | ne bit                         |                                               |                  |                  |              |

| bit 3                   | 1 = NVM M                       | isable NVM Me<br>emory Scan mo<br>emory Scan mo                                    | dule disabled                  | bit <sup>(2)</sup>                            |                  |                  |              |

| bit 2                   | 1 = All Mem                     | M Module Disal<br>ory reading and<br>odule enabled                                 |                                | bled; NVMCON                                  | registers canr   | not be written   |              |

| bit 1                   | 1 = CLKR m                      | isable Clock Re<br>odule disabled<br>odule enabled                                 | ference bit                    |                                               |                  |                  |              |

| bit 0                   | 1 = IOC mod                     | able Interrupt-on<br>dule(s) disabled<br>dule(s) enabled                           | -Change bit, A                 | ll Ports                                      |                  |                  |              |

|                         | earing the SYS<br>Fosc/4 are no | SCMD bit disable of affected.                                                      | es the system                  | clock (Fosc) to                               | peripherals, h   | owever periphe   | rals clocked |

# REGISTER 7-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

#### REGISTER 9-3: WDTPSL: WWDT PRESCALE SELECT LOW BYTE REGISTER (READ-ONLY)

|                  |                                   |                      |       |                                            |       | •     | ,     |  |

|------------------|-----------------------------------|----------------------|-------|--------------------------------------------|-------|-------|-------|--|

| R-0/0            | R-0/0                             | R-0/0                | R-0/0 | R-0/0                                      | R-0/0 | R-0/0 | R-0/0 |  |

|                  |                                   |                      | PSC   | NT<7:0>                                    |       |       |       |  |

| bit 7            |                                   |                      |       |                                            |       |       | bit 0 |  |

|                  |                                   |                      |       |                                            |       |       |       |  |

| Legend:          |                                   |                      |       |                                            |       |       |       |  |

| R = Readable b   | R = Readable bit W = Writable bit |                      |       | U = Unimplemented bit, read as '0'         |       |       |       |  |

| u = Bit is uncha | anged                             | x = Bit is unknow    | n     | -n/n = Value at POR and BOR/Value at all c |       |       |       |  |

| '1' = Bit is set |                                   | '0' = Bit is cleared | ł     |                                            |       |       |       |  |

#### bit 7-0 **PSCNT<7:0>:** Prescale Select Low Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-4: WDTPSH: WWDT PRESCALE SELECT HIGH BYTE REGISTER (READ-ONLY)

|       |       |       |       |        |       | · ·   |       |

|-------|-------|-------|-------|--------|-------|-------|-------|

| R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0  | R-0/0 | R-0/0 | R-0/0 |

|       |       |       | PSCNT | <15:8> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

|       |       |       |       |        |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

# bit 7-0 **PSCNT<15:8>:** Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

| Address | Name      | Bit 7  | Bit 6                                    | Bit 5      | Bit 4   | Bit 3    | Bit 2      | Bit 1      | Bit 0    | <u>Value on</u><br>POR, BOR |

|---------|-----------|--------|------------------------------------------|------------|---------|----------|------------|------------|----------|-----------------------------|

| F74h    | CRCDATL   |        | •                                        | •          | DATA    | A<7:0>   |            | •          |          | xxxxxxxx                    |

| F73h    | ADFLTRH   |        |                                          |            | ADFLTF  | RH<15:8> |            |            |          | xxxxxxxx                    |

| F72h    | ADFLTRL   |        |                                          |            | ADFLT   | RL<7:0>  |            |            |          | xxxxxxxx                    |

| F71h    | ADACCH    |        |                                          |            | ADACC   | H<15:8>  |            |            |          | xxxxxxxx                    |

| F70h    | ADACCL    |        |                                          |            | ADAC    | CL<7:0>  |            |            |          | xxxxxxxx                    |

| F6Fh    | ADERRH    |        |                                          |            | ADERF   | RH<15:8> |            |            |          | 00000000                    |

| F6Eh    | ADERRL    |        |                                          |            | ADER    | RL<7:0>  |            |            |          | 00000000                    |

| F6Dh    | ADUTHH    |        |                                          |            | ADUTH   | IH<15:8> |            |            |          | 00000000                    |

| F6Ch    | ADUTHL    |        |                                          |            | ADUT    | HL<7:0>  |            |            |          | 00000000                    |

| F6Bh    | ADLTHH    |        |                                          |            | ADLTH   | H<15:8>  |            |            |          | 00000000                    |

| F6Ah    | ADLTHL    |        |                                          |            | ADLTH   | HL<7:0>  |            |            |          | 00000000                    |

| F69h    | ADSTPTH   |        |                                          |            | ADSTP   | TH<15:8> |            |            |          | 00000000                    |

| F68h    | ADSTPTL   |        |                                          |            | ADSTF   | PTL<7:0> |            |            |          | 00000000                    |

| F67h    | ADCNT     |        |                                          |            | ADCN    | IT<7:0>  |            |            |          | 00000000                    |

| F66h    | ADRPT     |        |                                          |            | ADRF    | PT<7:0>  |            |            |          | 00000000                    |

| F65h    | ADSTAT    | ADAOV  | ADAOV ADUTHR ADLTHR ADMATH - ADSTAT<2:0> |            |         |          |            |            | >        | 0000-000                    |

| F64h    | ADRESH    |        |                                          |            | ADRE    | SH<7:0>  |            |            |          | 00000000                    |

| F63h    | ADRESL    |        |                                          |            | ADRE    | SL<7:0>  |            |            |          | 00000000                    |

| F62h    | ADPREVH   |        |                                          |            | ADPRE   | VH<15:8> |            |            |          | 00000000                    |

| F61h    | ADPREVL   |        |                                          |            | ADPRE   | VL<7:0>  |            |            |          | 00000000                    |

| F60h    | ADCON0    | ADON   | ADCONT                                   | —          | ADSC    | —        | ADFM       | —          | ADGO     | 00-000-0                    |

| F5Fh    | ADPCH     | —      | _                                        |            |         | ADPO     | CH<5:0>    |            |          | 000000                      |

| F5Eh    | ADPRE     |        | •                                        |            | ADPR    | E<7:0>   |            |            |          | 00000000                    |

| F5Dh    | ADCAP     | —      | _                                        | _          |         |          | ADCAP<4:0> |            |          | 00000                       |

| F5Ch    | ADACQ     |        | •                                        |            | ADAC    | Q<7:0>   |            |            |          | 00000000                    |

| F5Bh    | ADCON3    | —      |                                          | ADCALC<2:0 | >       | ADSOI    |            | ADTMD<2:0> | >        | -0000000                    |

| F5Ah    | ADCON2    | ADPSIS |                                          | ADCRS<2:0> | >       | ADACLR   |            | ADMD<2:0>  |          | 00000000                    |

| F59h    | ADCON1    | ADPPOL | ADIPEN                                   | ADGPOL     | —       | —        | —          | —          | ADDSEN   | 0000                        |

| F58h    | ADREF     | —      | _                                        | _          | ADNREF  | —        | —          | ADPF       | REF<1:0> | 0-00                        |

| F57h    | ADCLK     | —      | _                                        |            |         | ADC      | S<5:0>     |            |          | 000000                      |

| F56h    | ADACT     | —      | _                                        | _          |         |          | ADACT<4:0> |            |          | 00000                       |

| F55h    | MDCARH    | —      | -                                        | —          | —       | —        |            | CHS<2:0>   |          | 000                         |

| F54h    | MDCARL    | —      | -                                        | -          | —       | —        |            | CLS<2:0>   |          | 000                         |

| F53h    | MDSRC     | —      | —                                        | SRCS<3:0>  |         |          |            |            |          | 0000                        |

| F52h    | MDCON1    | —      | —                                        | CHPOL      | CHSYNC  | —        | —          | CLPOL      | CLSYNC   | 0000                        |

| F51h    | MDCON0    | EN     | —                                        | Ουτ        | OPOL    | —        | —          | —          | MDBIT    | 0-000                       |

| F50h    | SCANTRIG  | —      | -                                        | -          | —       |          | TSEL       | <3:0>      |          | 0000                        |

| F4Fh    | SCANCON0  | SCANEN | SCANGO                                   | BUSY       | INVALID | INTM     | —          | MOD        | E<1:0>   | 00000-00                    |

| F4Eh    | SCANHADRU | _      | _                                        |            |         | HADR     | <21:16>    |            |          | 111111                      |

# TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40 devices.

| Address | Name                   | Bit 7   | Bit 6   | Bit 5     | Bit 4   | Bit 3       | Bit 2       | Bit 1  | Bit 0    | <u>Value on</u><br>POR, BOR |

|---------|------------------------|---------|---------|-----------|---------|-------------|-------------|--------|----------|-----------------------------|

| EFFh    | RD0PPS <sup>(2)</sup>  | _       | —       | —         |         |             | RD0PPS<4:0> |        |          | 00000                       |

| EFEh    | RC7PPS                 | _       | _       | _         |         | RC7PPS<4:0> |             |        |          |                             |

| EFDh    | RC6PPS                 | _       | _       | _         |         |             | RC6PPS<4:0> |        |          | 00000                       |

| EFCh    | RC5PPS                 | _       | _       | _         |         |             | RC5PPS<4:0> |        |          | 00000                       |

| EFBh    | RC4PPS                 | _       | _       | _         |         |             | RC4PPS<4:0> |        |          | 00000                       |

| EFAh    | RC3PPS                 | _       | _       | _         |         |             | RC3PPS<4:0> |        |          | 00000                       |

| EF9h    | RC2PPS                 | _       | _       | _         |         |             | RC2PPS<4:0> |        |          | 00000                       |

| EF8h    | RC1PPS                 | _       | —       | —         |         |             | RC1PPS<4:0> |        |          | 00000                       |

| EF7h    | RC0PPS                 | _       | —       | _         |         |             | RC0PPS<4:0> | •      |          | 00000                       |

| EF6h    | RB7PPS                 | _       | —       | —         |         |             | RB7PPS<4:0> |        |          | 00000                       |

| EF5h    | RB6PPS                 | _       | —       | _         |         |             | RB6PPS<4:0> |        |          | 00000                       |

| EF4h    | RB5PPS                 | _       | —       | _         |         |             | RB5PPS<4:0> |        |          | 00000                       |

| EF3h    | RB4PPS                 | _       | —       | _         |         |             | RB4PPS<4:0> |        |          | 00000                       |

| EF2h    | RB3PPS                 | _       | —       | _         |         |             | RB3PPS<4:0> |        |          | 00000                       |

| EF1h    | RB2PPS                 | _       | —       | _         |         |             | RB2PPS<4:0> |        |          | 00000                       |

| EF0h    | RB1PPS                 | _       | —       | —         |         |             | RB1PPS<4:0> |        |          | 00000                       |

| EEFh    | RB0PPS                 | _       | —       | _         |         |             | RB0PPS<4:0> |        |          | 00000                       |

| EEEh    | RA7PPS                 | _       | —       | _         |         |             | RA7PPS<4:0> |        |          | 00000                       |

| EEDh    | RA6PPS                 | _       | —       | _         |         |             | RA6PPS<4:0> |        |          | 00000                       |

| EECh    | RA5PPS                 | _       | —       | —         |         |             | RA5PPS<4:0> |        |          | 00000                       |

| EEBh    | RA4PPS                 | _       | —       | _         |         |             | RA4PPS<4:0> |        |          | 00000                       |

| EEAh    | RA3PPS                 | _       | —       | —         |         |             | RA3PPS<4:0> |        |          | 00000                       |

| EE9h    | RA2PPS                 | _       | —       | —         |         |             | RA2PPS<4:0> |        |          | 00000                       |

| EE8h    | RA1PPS                 | _       | —       | —         |         |             | RA1PPS<4:0> |        |          | 00000                       |

| EE7h    | RA0PPS                 | _       | —       | _         |         |             | RA0PPS<4:0> |        |          | 00000                       |

| EE6h    | PMD5                   | _       | —       | —         | —       | —           | —           | —      | DSMMD    | 0                           |

| EE5h    | PMD4                   | UART2MD | UART1MD | MSSP2MD   | MSSP1MD | —           | —           | —      | CWG1MD   | 00000                       |

| EE4h    | PMD3                   | _       | —       | —         | —       | PWM4MD      | PWM3MD      | CCP2MD | CCP1MD   | 0000                        |

| EE3h    | PMD2                   | _       | DACMD   | ADCMD     | _       | —           | CMP2MD      | CMP1MD | ZCDMD    | -00000                      |

| EE2h    | PMD1                   | _       | TMR6MD  | TMR5MD    | TMR4MD  | TMR3MD      | TMR2MD      | TMR1MD | TMR0MD   | -0000000                    |

| EE1h    | PMD0                   | SYSCMD  | FVRMD   | HLVDMD    | CRCMD   | SCANMD      | NVMMD       | CLKRMD | IOCMD    | 00x00000                    |

| EE0h    | BORCON                 | SBOREN  | —       | —         | —       | —           | —           | —      | BORRDY   | 1q                          |

| EDFh    | VREGCON <sup>(1)</sup> | -       | —       | —         | _       | —           | —           | VREGPM | Reserved | 01                          |

| EDEh    | OSCFRQ                 | _       | —       | —         | —       |             | HFFR        | Q<3:0> |          | 1111                        |

| EDDh    | OSCTUNE                | _       | —       |           |         | HFTU        | JN<5:0>     |        |          | 100000                      |

| EDCh    | OSCEN                  | EXTOEN  | HFOEN   | MFOEN     | LFOEN   | SOSCEN      | ADOEN       |        | —        | 000000                      |

| EDBh    | OSCSTAT                | EXTOR   | HFOR    | MFOR      | LFOR    | SOR         | ADOR        |        | PLLR     | dddddd-d                    |

| EDAh    | OSCCON3                | CSWHOLD | SOSCPWR | —         | ORDY    | NOSCR       | _           | —      | _        | 00-00                       |

| ED9h    | OSCCON2                | _       |         | COSC<2:0> | 1       |             | CDIV        | /<3:0> |          | -ddddddd                    |

#### TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40 devices.

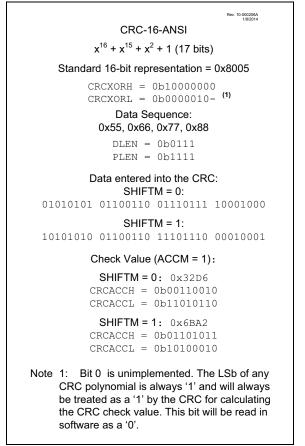

# 13.3 CRC Functional Overview

The CRC module can be used to detect bit errors in the Flash memory using the built-in memory scanner or through user input RAM memory. The CRC module can accept up to a 16-bit polynomial with up to a 16-bit seed value. A CRC calculated check value (or checksum) will then be generated into the CRCACC<15:0> registers for user storage. The CRC module uses an XOR shift register implementation to perform the polynomial division required for the CRC calculation.

# EXAMPLE 13-1: CRC EXAMPLE

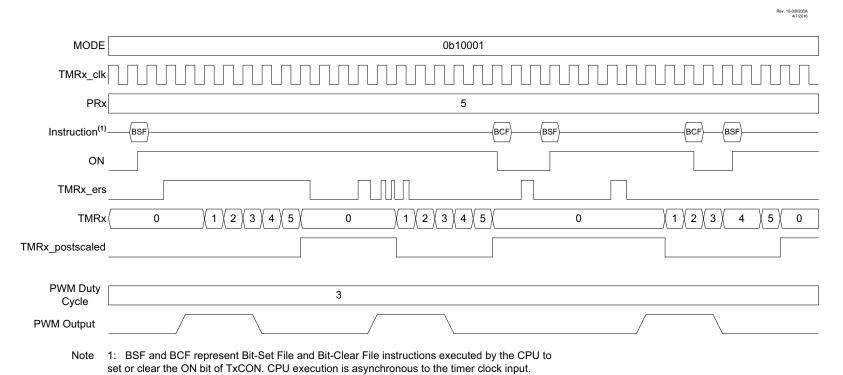

# FIGURE 20-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

# 24.14 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripheral is shown in Table 24-2. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

# TABLE 24-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CWG        | CWG             |

## I

## REGISTER 24-1: CWG1CON0: CWG CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> | _   | —   |     |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

| bit 7   | EN: CWG1 Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                                                                                                                                                                                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>LD: CWG1 Load Buffers bit<sup>(1)</sup></li> <li>1 = Dead-band count buffers to be loaded on CWG data rising edge, following first falling edge after this bit is set</li> <li>0 = Buffers remain unchanged</li> </ul>                                                                                                                                                                      |

| bit 5-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                           |

| bit 2-0 | MODE<2:0>: CWG1 Mode bits<br>111 = Reserved<br>100 = Reserved<br>101 = CWG outputs operate in Push-Pull mode<br>100 = CWG outputs operate in Half-Bridge mode<br>011 = CWG outputs operate in Reverse Full-Bridge mode<br>010 = CWG outputs operate in Forward Full-Bridge mode<br>001 = CWG outputs operate in Synchronous Steering mode<br>000 = CWG outputs operate in Asynchronous Steering mode |

| Note 1: | This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.                                                                                                                                                                                                                                                                                                            |

# 26.5.5 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

| Name       | Bit 7    | Bit 6     | Bit 5 | Bit 4         | Bit 3  | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|------------|----------|-----------|-------|---------------|--------|------------|---------|---------|---------------------|

| INTCON     | GIE/GIEH | PEIE/GIEL | IPEN  | _             | —      | INT2EDG    | INT1EDG | INT0EDG | 170                 |

| PIE3       | RC2IE    | TX2IE     | RC1IE | TX1IE         | BCL2IE | SSP2IE     | BCL1IE  | SSP1IE  | 182                 |

| PIR3       | RC2IF    | TX2IF     | RC1IF | TX1IF         | BCL2IF | SSP2IF     | BCL1IF  | SSP1IF  | 174                 |

| IPR3       | RC2IP    | TX2IP     | RC1IP | TX1IP         | BCL2IP | SSP2IP     | BCL1IP  | SSP1IP  | 190                 |

| RxyPPS     | —        | _         | _     |               |        | RxyPPS<4:0 | >       |         | 218                 |

| SSPxBUF    |          |           |       | BUF           | <7:0>  |            |         |         | 336*                |

| SSPxCLKPPS | —        | _         | _     |               | SS     | SPxCLKPPS< | 4:0>    |         | 216                 |

| SSPxCON1   | WCOL     | SSPOV     | SSPEN | CKP           |        | SSPN       | /<3:0>  |         | 338                 |

| SSPxCON3   | ACKTIM   | PCIE      | SCIE  | BOEN          | SDAHT  | SBCDE      | AHEN    | DHEN    | 339                 |

| SSPxDATPPS | —        | _         | _     |               | 216    |            |         |         |                     |

| SSPxSSPPS  | —        | _         | —     | SSPSSPPS<4:0> |        |            |         |         | 216                 |

| SSPxSTAT   | SMP      | CKE       | D/Ā   | Р             | S      | R/W        | UA      | BF      | 353                 |

### TABLE 26-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode. \* Page provides register information.

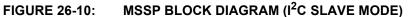

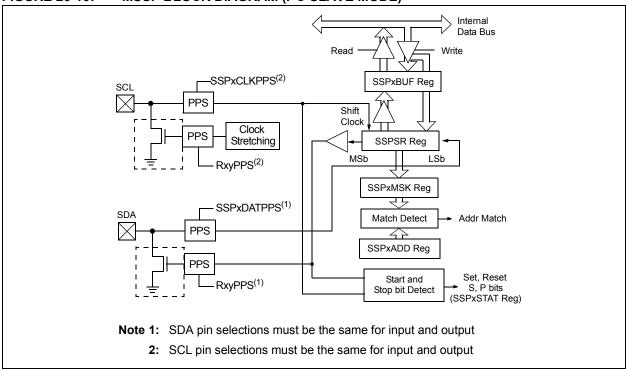

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- Serial Data (SDA)

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 26-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode

(master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode

- (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device. If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 26-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

© 2015-2017 Microchip Technology Inc.

| U-0                               | U-0                                     | R/W-0/0           | R/W-0/0       | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |

|-----------------------------------|-----------------------------------------|-------------------|---------------|----------------|------------------|----------------|--------------|--|

| _                                 | —                                       |                   | ADCS<5:0>     |                |                  |                |              |  |

| bit 7                             |                                         |                   |               |                |                  |                | bit 0        |  |

|                                   |                                         |                   |               |                |                  |                |              |  |

| Legend:                           |                                         |                   |               |                |                  |                |              |  |

| R = Readable bit W = Writable bit |                                         |                   |               | U = Unimplen   | nented bit, read | d as '0'       |              |  |

| u = Bit is unc                    | u = Bit is unchanged x = Bit is unknown |                   |               | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |  |

| '1' = Bit is se                   | t                                       | '0' = Bit is clea | ared          |                |                  |                |              |  |

|                                   |                                         |                   |               |                |                  |                |              |  |

| bit 7-6                           | Unimplemen                              | ited: Read as '   | 0'            |                |                  |                |              |  |

| bit 5-0                           | ADCS<5:0>:                              | ADC Conversi      | on Clock Sele | ect bits       |                  |                |              |  |

|                                   | 111111 <b>= F</b> o                     | sc/128            |               |                |                  |                |              |  |

|                                   | 111110 <b>= F</b> O                     | sc/126            |               |                |                  |                |              |  |

|                                   | 111101 <b>= F</b> O                     | sc/124            |               |                |                  |                |              |  |

|                                   | •                                       |                   |               |                |                  |                |              |  |

|                                   | •                                       |                   |               |                |                  |                |              |  |

|                                   | •                                       |                   |               |                |                  |                |              |  |

|                                   | 000000 <b>= F</b> C                     | osc/2             |               |                |                  |                |              |  |

# REGISTER 31-6: ADCLK: ADC CLOCK SELECTION REGISTER

# REGISTER 31-7: ADREF: ADC REFERENCE SELECTION REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|-----|-----|---------|---------|

| —     | —   | —   | ADNREF  | —   | —   | ADPRE   | F<1:0>  |

| bit 7 |     |     |         |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5<br>bit 4 | Unimplemented: Read as '0'<br>ADNREF: ADC Negative Voltage Reference Selection bit<br>1 = VREF- is connected to external VREF-<br>0 = VREF- is connected to AVss                                                                  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-2          | Unimplemented: Read as '0'                                                                                                                                                                                                        |

| bit 1-0          | ADPREF: ADC Positive Voltage Reference Selection bits<br>11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module<br>10 = VREF+ is connected to external VREF+<br>01 = Reserved<br>00 = VREF+ is connected to VDD |

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                         |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 1211 987 0                                                                                                                                                                                                                                         |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                      |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | BC MYFUNC            |

## TABLE 35-2: INSTRUCTION SET (CONTINUED)

| Mnemonic,<br>Operands |         | Description                     | Quality | 16-Bit Instruction Word |      |      |      | Status          | Neter |

|-----------------------|---------|---------------------------------|---------|-------------------------|------|------|------|-----------------|-------|

|                       |         | Description                     | Cycles  | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL (             | OPERAT  | IONS                            |         |                         |      |      |      |                 | _     |

| ADDLW                 | k       | Add literal and WREG            | 1       | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW                 | k       | AND literal with WREG           | 1       | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW                 | k       | Inclusive OR literal with WREG  | 1       | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR                  | f, k    | Move literal (12-bit) 2nd word  | 2       | 1110                    | 1110 | 00ff | kkkk | None            |       |

|                       |         | to FSR(f) 1st word              |         | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB                 | k       | Move literal to BSR<3:0>        | 1       | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW                 | k       | Move literal to WREG            | 1       | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW                 | k       | Multiply literal with WREG      | 1       | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW                 | k       | Return with literal in WREG     | 2       | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW                 | k       | Subtract WREG from literal      | 1       | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW                 | k       | Exclusive OR literal with WREG  | 1       | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN              | /IORY ↔ | PROGRAM MEMORY OPERATION        | IS      |                         |      |      |      |                 |       |

| TBLRD*                |         | Table Read                      | 2       | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+               |         | Table Read with post-increment  |         | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-               |         | Table Read with post-decrement  |         | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*               |         | Table Read with pre-increment   |         | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*                |         | Table Write                     | 2       | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+               |         | Table Write with post-increment |         | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-               |         | Table Write with post-decrement |         | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*               |         | Table Write with pre-increment  |         | 0000                    | 0000 | 0000 | 1111 | None            |       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

# PIC18(L)F26/45/46K40

| DECFSZ              | Decremer                                                                                                                                                                                                                                                 | nt f, skip if C                                                                                                                                            | )                                                                                                                                                                                                                                         | DCFSNZ                 | Decreme                                                                                                                                                                                                                                                                                         | nt f, skip if n                                                                                                                                                                                                                                                                                                                              | ot 0                                                                                                                                                                                                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | DECFSZ f                                                                                                                                                                                                                                                 | f {,d {,a}}                                                                                                                                                |                                                                                                                                                                                                                                           | Syntax:                | DCFSNZ                                                                                                                                                                                                                                                                                          | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                             |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                       |                                                                                                                                                            |                                                                                                                                                                                                                                           | Operands:              | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                             |

| Operation:          | (f) – 1 $\rightarrow$ de skip if resul                                                                                                                                                                                                                   |                                                                                                                                                            |                                                                                                                                                                                                                                           | Operation:             | (f) – 1 $\rightarrow$ de skip if resul                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                             |

| Status Affected:    | None                                                                                                                                                                                                                                                     |                                                                                                                                                            |                                                                                                                                                                                                                                           | Status Affected:       | None                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                             |

| Encoding:           | 0010                                                                                                                                                                                                                                                     | 11da ffi                                                                                                                                                   | ff ffff                                                                                                                                                                                                                                   | Encoding:              | 0100                                                                                                                                                                                                                                                                                            | 11da fff                                                                                                                                                                                                                                                                                                                                     | f ffff                                                                                                                                                                                                                      |