Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL/M/H and Secondary Oscillator).

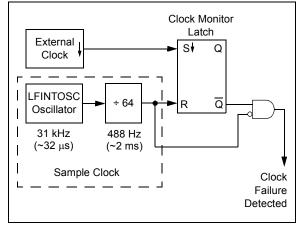

FIGURE 4-9: FSCM BLOCK DIAGRAM

#### 4.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 4-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 4.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM overwrites the COSC bits to select HFINTOSC (3'b110). The frequency of HFINTOSC would be determined by the previous state of the HFFRQ bits and the NDIV/CDIV bits. The bit flag OSCFIF of the PIR1 register is set. Setting this flag will generate an interrupt if the OSCFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

#### 4.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator or PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSCFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSCFIF flag will again become set by hardware.

| U-0                                                                                                                                                    | R/W-0/0    | R/W-0/0                  | R/W-0/0  | R/W-0/0       | R/W-0/0        | R/W-0/0 | R/W-0/0     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------|----------|---------------|----------------|---------|-------------|--|--|

|                                                                                                                                                        | TMR6MD     | TMR5MD                   | TMR4MD   | TMR3MD        | TMR2MD         | TMR1MD  | TMR0MD      |  |  |

| bit 7                                                                                                                                                  |            |                          |          |               |                |         | bit         |  |  |

| Legend:                                                                                                                                                |            |                          |          |               |                |         |             |  |  |

| R = Reada                                                                                                                                              | hla hit    | W = Writable             | bit      |               | optod bit road |         |             |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other |            |                          |          |               |                |         | thar Dagata |  |  |

| и – ысты и<br>'1' = Bit is s                                                                                                                           | •          |                          |          |               |                |         | iner Reseis |  |  |

|                                                                                                                                                        | Sel        | '0' = Bit is clea        | areu     | q = value dep | ends on condit | 1011    |             |  |  |

| bit 7                                                                                                                                                  | Unimplemer | ted: Read as '           | )'       |               |                |         |             |  |  |

| bit 6                                                                                                                                                  | TMR6MD: Di | sable Timer TM           | IR6 bit  |               |                |         |             |  |  |

|                                                                                                                                                        | 1 = TMR6 m | nodule disabled          |          |               |                |         |             |  |  |

|                                                                                                                                                        | 0 = TMR6 m | nodule enabled           |          |               |                |         |             |  |  |

| bit 5                                                                                                                                                  | TMR5MD: Di | sable Timer TM           | IR5 bit  |               |                |         |             |  |  |

|                                                                                                                                                        | 1 = TMR5 m | TMR5 module disabled     |          |               |                |         |             |  |  |

| (                                                                                                                                                      | 0 = TMR5 m | = TMR5 module enabled    |          |               |                |         |             |  |  |

| bit 4                                                                                                                                                  | TMR4MD: Di | sable Timer TM           | IR4 bit  |               |                |         |             |  |  |

|                                                                                                                                                        | 1 = TMR4 m | nodule disabled          |          |               |                |         |             |  |  |

|                                                                                                                                                        | 0 = TMR4 m | nodule enabled           |          |               |                |         |             |  |  |

| bit 3                                                                                                                                                  | TMR3MD: Di | sable Timer TM           | IR3 bit  |               |                |         |             |  |  |

|                                                                                                                                                        | -          | nodule disabled          |          |               |                |         |             |  |  |

|                                                                                                                                                        | 0 = TMR3 n | nodule enabled           |          |               |                |         |             |  |  |

| bit 2                                                                                                                                                  | TMR2MD: Di | sable Timer TM           | IR2 bit  |               |                |         |             |  |  |

|                                                                                                                                                        |            | 1 = TMR2 module disabled |          |               |                |         |             |  |  |

| L:1. A                                                                                                                                                 |            | odule enabled            |          |               |                |         |             |  |  |

| bit 1                                                                                                                                                  |            | sable Timer TM           | IR'I DIT |               |                |         |             |  |  |

|                                                                                                                                                        |            | odule disabled           |          |               |                |         |             |  |  |

| bit 0                                                                                                                                                  |            | isable Timer TM          | IR0 bit  |               |                |         |             |  |  |

|                                                                                                                                                        |            | odule disabled           |          |               |                |         |             |  |  |

|                                                                                                                                                        |            | odule enabled            |          |               |                |         |             |  |  |

#### REGISTER 7-2: PMD1: PMD CONTROL REGISTER 1

| R/W-0/0          | R/W-0/0     | R/W-0/0                             | R/W-0/0  | U-0            | U-0               | U-0            | R/W-0/0      |

|------------------|-------------|-------------------------------------|----------|----------------|-------------------|----------------|--------------|

| UART2MD          | UART1MD     | MSSP2MD                             | MSSP1MD  | —              | —                 | —              | CWG1MD       |

| bit 7            |             |                                     |          |                |                   |                | bit 0        |

|                  |             |                                     |          |                |                   |                |              |

| Legend:          |             |                                     |          |                |                   |                |              |

| R = Readable     | e bit       | W = Writable                        | bit      | U = Unimplem   | nented bit, read  | as '0'         |              |

| u = Bit is unc   | hanged      | x = Bit is unkn                     | iown     | -n/n = Value a | t POR and BOR     | R/Value at all | other Resets |

| '1' = Bit is set | t           | '0' = Bit is clea                   | ared     | q = Value dep  | ends on condition | on             |              |

|                  |             |                                     |          |                |                   |                |              |

| bit 7            | UART2MD: Di | isable EUSART2                      | 2 bit    |                |                   |                |              |

|                  |             | 2 module disable                    |          |                |                   |                |              |

|                  | 0 = EUSART2 | 2 module enable                     | ed       |                |                   |                |              |

| bit 6            | -           | isable EUSART                       |          |                |                   |                |              |

|                  |             | 1 module disable<br>1 module enable |          |                |                   |                |              |

| bit 5            |             | isable MSSP2 b                      | -        |                |                   |                |              |

| bit 5            |             | nodule disabled                     | it.      |                |                   |                |              |

|                  | 0 = MSSP2 m | nodule enabled                      |          |                |                   |                |              |

| bit 4            | MSSP1MD: D  | isable MSSP1 b                      | it       |                |                   |                |              |

|                  |             | nodule disabled                     |          |                |                   |                |              |

|                  |             | nodule enabled                      |          |                |                   |                |              |

| bit 3-1          | Unimplement | ed: Read as '0'                     |          |                |                   |                |              |

| bit 0            |             | sable CWG1 Mo                       | dule bit |                |                   |                |              |

|                  |             | odule disabled                      |          |                |                   |                |              |

|                  | 0 = CWG1 m  | odule enabled                       |          |                |                   |                |              |

#### REGISTER 7-5: PMD4: PMD CONTROL REGISTER 4

### 10.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 enhanced microcontroller devices:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate buses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Program Flash Memory and Data EEPROM Memory is provided in **Section 11.0 "Nonvolatile Memory (NVM) Control**".

#### 10.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2 Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2 Mbyte address will return all '0's (a NOP instruction).

These devices contains the following:

- PIC18(L)F45K40: 32 K bytes of Flash memory, up to 16,384 single-word instructions

- PIC18(L)F26K40, PIC18(L)F46K40: 64 Kbytes of Flash memory, up to 32,768 single-word instructions

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

**Note:** For memory information on this family of devices, see Table 10-1 and Table 10-2.

#### 11.1.5 ERASING PROGRAM FLASH MEMORY

The minimum erase block is 32 or 64 words (refer to Table 11-3). Only through the use of an external programmer, or through ICSP™ control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

For example, when initiating an erase sequence from a microcontroller with erase row size of 32 words, a block of 32 words (64 bytes) of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The NVMCON1 register commands the erase operation. The NVMREG<1:0> bits must be set to point to the Program Flash Memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The NVM unlock sequence described in **Section 11.1.4 "NVM Unlock Sequence"** should be used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

#### 11.1.5.1 Program Flash Memory Erase Sequence

The sequence of events for erasing a block of internal program memory is:

- 1. NVMREG bits of the NVMCON1 register point to PFM

- 2. Set the FREE and WREN bits of the NVMCON1 register

- 3. Perform the unlock sequence as described in Section 11.1.4 "NVM Unlock Sequence"

If the PFM address is write-protected, the WR bit will be cleared and the erase operation will not take place, WRERR is signaled in this scenario.

The operation erases the memory row indicated by masking the LSBs of the current TBLPTR.

While erasing PFM, CPU operation is suspended and it resumes when the operation is complete. Upon completion the WR bit is cleared in hardware, the NVMIF is set and an interrupt will occur if the NVMIE bit is also set.

Write latch data is not affected by erase operations and WREN will remain unchanged.

Note 1: If a write or erase operation is terminated by an unexpected event, WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

- 2: WRERR is set if WR is written to '1' while TBLPTR points to a write-protected address.

- **3:** WRERR is set if WR is written to '1' while TBLPTR points to an invalid address location (Table 10-2 and Table 11-1).

| U-0                                                                     | U-0                                                                          | U-0             | U-0 | U-0                                | U-0  | R/W-0/0         | R/W-0/0 |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------|-----|------------------------------------|------|-----------------|---------|--|

|                                                                         |                                                                              | —               |     | _                                  | —    | CCP2IE          | CCP1IE  |  |

| bit 7                                                                   |                                                                              |                 |     |                                    |      |                 | bit 0   |  |

|                                                                         |                                                                              |                 |     |                                    |      |                 |         |  |

| Legend:                                                                 |                                                                              |                 |     |                                    |      |                 |         |  |

| R = Readable bit W = Writable bit                                       |                                                                              |                 |     | U = Unimplemented bit, read as '0' |      |                 |         |  |

| -n = Value at POR '1' = Bit is set                                      |                                                                              |                 |     | '0' = Bit is cle                   | ared | x = Bit is unkr | nown    |  |

|                                                                         |                                                                              |                 |     |                                    |      |                 |         |  |

| bit 7-2                                                                 | Unimplemen                                                                   | ted: Read as 'd | )'  |                                    |      |                 |         |  |

| bit 1                                                                   | t 1 <b>CCP2IE:</b> ECCP2 Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                 |     |                                    |      |                 |         |  |

| bit 0 CCP1IE: ECCP1 Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                                                                              |                 |     |                                    |      |                 |         |  |

#### REGISTER 14-16: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

| R/W-0/0         R/W-0/0 <t< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<> |                                                       |         |              |                    |                                    |         |         |         |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|--------------|--------------------|------------------------------------|---------|---------|---------|--|--|--|

| bit 7     bit       Legend:     W = Writable bit     U = Unimplemented bit, read as '0'       '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0/0                                               | R/W-0/0 | R/W-0/0      | R/W-0/0            | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | WPUx7                                                 | WPUx6   | WPUx5        | WPUx4              | WPUx3                              | WPUx2   | WPUx1   | WPUx0   |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7                                                 |         |              |                    |                                    |         | •       | bit 0   |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |         |              |                    |                                    |         |         |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Legend:                                               |         |              |                    |                                    |         |         |         |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readable                                          | bit     | W = Writable | bit                | U = Unimplemented bit, read as '0' |         |         |         |  |  |  |

| -n/n = Value at POR and BOR/Value at all other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set '0' = Bit is cleared                 |         |              | x = Bit is unknown |                                    |         |         |         |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -n/n = Value at POR and BOR/Value at all other Resets |         |              |                    |                                    |         |         |         |  |  |  |

#### REGISTER 15-5: WPUx: WEAK PULL-UP REGISTER

bit 7-0

WPUx<7:0>: Weak Pull-up PORTx Control bits

1 = Weak Pull-up enabled

0 = Weak Pull-up disabled

|      | Dev        | /ice          |       |       |       |       |                      |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|----------------------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

| WPUA | Х          | Х             | WPUA7 | WPUA6 | WPUA5 | WPUA4 | WPUA3                | WPUA2 | WPUA1 | WPUA0 |

| WPUB | Х          | Х             | WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3                | WPUB2 | WPUB1 | WPUB0 |

| WPUC | Х          | Х             | WPUC7 | WPUC6 | WPUC5 | WPUC4 | WPUC3                | WPUC2 | WPUC1 | WPUC0 |

| WPUD | Х          |               | _     | _     | _     | _     | —                    | _     | _     | _     |

|      |            | Х             | WPUD7 | WPUD6 | WPUD5 | WPUD4 | WPUD3                | WPUD2 | WPUD1 | WPUD0 |

| WPUE | Х          |               | _     | _     | _     | _     | WPUE3 <sup>(1)</sup> | _     | _     | _     |

|      |            | Х             | —     | —     | —     | —     | WPUE3 <sup>(1)</sup> | WPUE2 | WPUE1 | WPUE0 |

#### TABLE 15-6: WEAK PULL-UP PORT REGISTERS

Note 1: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

| Mada              | MODE  | <4:0> | Output                            | On creation                                               |                                       | Timer Control |                                   |

|-------------------|-------|-------|-----------------------------------|-----------------------------------------------------------|---------------------------------------|---------------|-----------------------------------|

| Mode              | <4:3> | <2:0> | Operation                         | Operation                                                 | Start                                 | Reset         | Stop                              |

|                   |       | 000   |                                   | Software gate (Figure 20-4)                               | <b>ON =</b> 1                         | _             | ON = 0                            |

|                   |       | 001   | Period<br>Pulse                   | Hardware gate, active-high<br>(Figure 20-5)               | ON = 1 and<br>TMRx_ers = 1            | _             | ON = 0 or<br>TMRx_ers = 0         |

|                   |       | 010   | Fuise                             | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0            | _             | ON = 0 or<br>TMRx_ers = 1         |

| Free              | 0.0   | 011   |                                   | Rising or falling edge Reset                              |                                       | TMRx_ers      |                                   |

| Running<br>Period | 00    | 100   | Period                            | Rising edge Reset (Figure 20-6)                           |                                       | TMRx_ers ↑    | <b>ON =</b> 0                     |

|                   |       | 101   | Pulse                             | Falling edge Reset                                        |                                       | TMRx_ers ↓    |                                   |

|                   |       | 110   | with<br>Hardware                  | Low level Reset                                           | ON = 1                                | TMRx_ers = 0  | ON = 0 or<br>TMRx_ers = 0         |

|                   |       | 111   | Reset                             | High level Reset (Figure 20-7)                            |                                       | TMRx_ers = 1  | ON = 0 or<br>TMRx_ers = 1         |

|                   |       | 000   | One-shot                          | Software start (Figure 20-8)                              | <b>ON =</b> 1                         | _             |                                   |

|                   |       | 001   | Edge                              | Rising edge start (Figure 20-9)                           | ON = 1 and<br>TMRx_ers ↑              | _             |                                   |

|                   |       | 010   | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓              | _             |                                   |

|                   |       | 011   | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers                | _             | ON = 0<br>or                      |

| One-shot          | 01    | 100   | Edge                              | Rising edge start and<br>Rising edge Reset (Figure 20-10) | ON = 1 and<br>TMRx_ers ↑              | TMRx_ers ↑    | Next clock<br>after<br>TMRx = PRx |

|                   |       | 101   | triggered<br>start                | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓              | TMRx_ers ↓    | (Note 2)                          |

|                   |       | 110   | and<br>hardware<br>Reset          | Rising edge start and<br>Low level Reset (Figure 20-11)   | ON = 1 and<br>TMRx_ers ↑ TMRx_ers = 0 |               |                                   |

|                   |       | 111   | (Note 1)                          | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓              | TMRx_ers = 1  |                                   |

|                   |       | 000   |                                   | Rese                                                      | rved                                  |               |                                   |

|                   |       | 001   | Edge                              | Rising edge start<br>(Figure 20-12)                       | ON = 1 and<br>TMRx_ers ↑              | —             | ON = 0<br>or                      |

| Mono-stable       |       | 010   | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓              | _             | Next clock<br>after               |

|                   |       | 011   | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers                | _             | TMRx = PRx<br>( <b>Note 3</b> )   |

| Reserved          | 10    | 100   |                                   | Rese                                                      | rved                                  |               | •                                 |

| Reserved          |       | 101   |                                   | Rese                                                      | rved                                  |               |                                   |

|                   |       | 110   | Level<br>triggered                | High level start and<br>Low level Reset (Figure 20-13)    | ON = 1 and<br>TMRx_ers = 1            | TMRx_ers = 0  | ON = 0 or                         |

| One-shot          |       | 111   | start<br>and<br>hardware<br>Reset | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0            | TMRx_ers = 1  | Held in Reset<br>(Note 2)         |

| Reserved          | 11    | xxx   |                                   | Rese                                                      | rved                                  |               |                                   |

#### TABLE 20-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

#### 20.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in Section

21.0 "Capture/Compare/PWM Module".

The signals are not a part of the Timer2 module.

#### 20.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2 operation. The timer increments with each clock input when ON = 1 and does not increment when ON = 0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 20-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

| MODE                          | 0b00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRx_clk                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Instruction <sup>(1)</sup> —— | BSF BSF BSF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ON                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PRx                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TMRx 0                        | $\begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \begin{array}{c} \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} $ |

| TMRx_postscaled               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PWM Duty                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PWM Output                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R/W-x/x              | R/W-x/x      | R/W-x/x          | R/W-x/x                     | R/W-x/x                                         | R/W-x/x     | R/W-x/x                                                |  |

|----------------------|--------------|------------------|-----------------------------|-------------------------------------------------|-------------|--------------------------------------------------------|--|

|                      |              | CCPR             | x<15:8>                     |                                                 |             |                                                        |  |

|                      |              |                  |                             |                                                 |             | bit 0                                                  |  |

|                      |              |                  |                             |                                                 |             |                                                        |  |

|                      |              |                  |                             |                                                 |             |                                                        |  |

| it                   | W = Writable | bit              | U = Unimplem                | ented bit, read                                 | l as '0'    |                                                        |  |

| -n = Value at POR '1 |              | '1' = Bit is set |                             | '0' = Bit is cleared                            |             | x = Bit is unknown                                     |  |

|                      | it           | it W = Writable  | CCPR<br>it W = Writable bit | CCPRx<15:8><br>it W = Writable bit U = Unimplem | CCPRx<15:8> | it W = Writable bit U = Unimplemented bit, read as '0' |  |

#### REGISTER 21-5: CCPRxH: CCPx REGISTER HIGH BYTE

bit 7-0

MODE = Capture Mode:

CCPRxH<7:0>: MSB of captured TMR1 value

MODE = Compare Mode:

CCPRxH<7:0>: MSB compared to TMR1 value

MODE = PWM Mode && FMT = 0:

CCPRxH<7:2>: Not used

CCPRxH<7:2>: Not used

CCPRxH<1:0>: CCPW<9:8> – Pulse-Width MS 2 bits

MODE = PWM Mode && FMT = 1:

CCPRxH<7:0>: CCPW<9:2> – Pulse-Width MS 8 bits

#### 24.2.4.2 Asynchronous Steering Mode

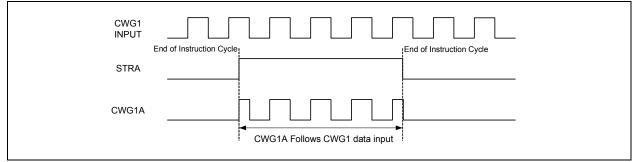

In Asynchronous mode (MODE<2:0> bits = 000, Register 24-1), steering takes effect at the end of the instruction cycle that writes to STR. In Asynchronous Steering mode, the output signal may be an incomplete waveform (Figure 24-10). This operation may be useful when the user firmware needs to immediately remove a signal from the output pin.

#### FIGURE 24-10: EXAMPLE OF ASYNCHRONOUS STEERING (MODE<2:0>= 000)

#### 24.2.4.3 Start-up Considerations

The application hardware must use the proper external pull-up and/or pull-down resistors on the CWG output pins. This is required because all I/O pins are forced to high-impedance at Reset.

The POLy bits (Register 24-2) allow the user to choose whether the output signals are active-high or active-low.

| U-0            | U-0                                                              | R/W-0/0                                                                                                                                                                                                          | R/W-0/0          | U-0             | U-0              | R/W-0/0          | R/W-0/0      |  |  |  |  |  |

|----------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|------------------|--------------|--|--|--|--|--|

| _              | _                                                                | CHPOL                                                                                                                                                                                                            | CHSYNC           | —               | —                | CLPOL            | CLSYNC       |  |  |  |  |  |

| bit 7          |                                                                  |                                                                                                                                                                                                                  |                  | ·               |                  |                  | bit (        |  |  |  |  |  |

|                |                                                                  |                                                                                                                                                                                                                  |                  |                 |                  |                  |              |  |  |  |  |  |

| Legend:        |                                                                  |                                                                                                                                                                                                                  |                  |                 |                  |                  |              |  |  |  |  |  |

| R = Reada      | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                                                                                                                                  |                  |                 |                  |                  |              |  |  |  |  |  |

| u = Bit is u   | nchanged                                                         | x = Bit is unkr                                                                                                                                                                                                  | iown             | -n/n = Value    | at POR and BC    | R/Value at all   | other Resets |  |  |  |  |  |

| '1' = Bit is s | set                                                              | '0' = Bit is clea                                                                                                                                                                                                | ared             |                 |                  |                  |              |  |  |  |  |  |

|                |                                                                  |                                                                                                                                                                                                                  |                  |                 |                  |                  |              |  |  |  |  |  |

| bit 7-6        | Unimplem                                                         | Unimplemented: Read as '0'                                                                                                                                                                                       |                  |                 |                  |                  |              |  |  |  |  |  |

| bit 5          | CHPOL: M                                                         | CHPOL: Modulator High Carrier Polarity Select bit                                                                                                                                                                |                  |                 |                  |                  |              |  |  |  |  |  |

|                | 1 = Select                                                       | 1 = Selected high carrier signal is inverted                                                                                                                                                                     |                  |                 |                  |                  |              |  |  |  |  |  |

|                | 0 = Select                                                       | 0 = Selected high carrier signal is not inverted                                                                                                                                                                 |                  |                 |                  |                  |              |  |  |  |  |  |

| bit 4          | CHSYNC:                                                          | CHSYNC: Modulator High Carrier Synchronization Enable bit                                                                                                                                                        |                  |                 |                  |                  |              |  |  |  |  |  |

|                |                                                                  | 1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the<br>low time carrier                                                                                       |                  |                 |                  |                  |              |  |  |  |  |  |

|                | 0 = Modula                                                       | 0 = Modulator output is not synchronized to the high time carrier signal <sup>(1)</sup>                                                                                                                          |                  |                 |                  |                  |              |  |  |  |  |  |