Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

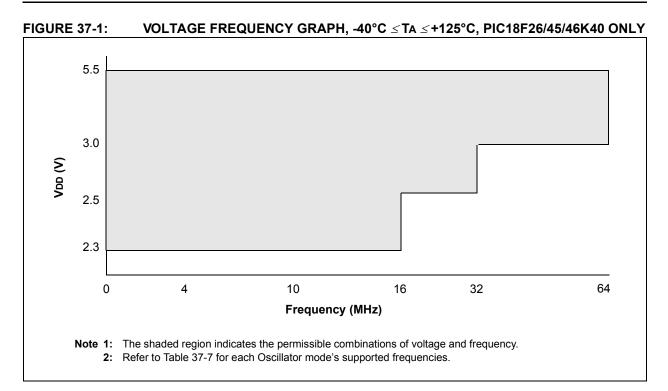

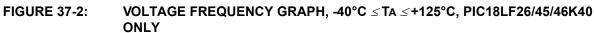

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F26/45/46K40

#### PIC18(L)F2x/4xK40 Family Types

| Device         | Data Sheet Index | Program Memory Flash<br>(bytes) | Data SRAM<br>(bytes) | Data EEPROM<br>(bytes) | I/O Pins | 16-bit Timers | Comparators | 10-bit ADC <sup>2</sup> with<br>Computation (ch) | 5-bit DAC | Zero-Cross Detect | CCP/10-bit PWM | CWG | 8-bit TMR with HLT | Windowed Watchdog<br>Timer | <b>CRC</b> with Memory Scan | EUSART | I <sup>2</sup> C/SPI | Sdd | Peripheral Module Disable | Temperature Indicator | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------------|----------------------|------------------------|----------|---------------|-------------|--------------------------------------------------|-----------|-------------------|----------------|-----|--------------------|----------------------------|-----------------------------|--------|----------------------|-----|---------------------------|-----------------------|----------------------|

| PIC18(L)F24K40 | (1)              | 16k                             | 1024                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Y   | Y                         | Y                     | Ι                    |

| PIC18(L)F25K40 | (1)              | 32k                             | 2048                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 1      | 1                    | Y   | Y                         | Υ                     | Ι                    |

| PIC18(L)F26K40 | (2)              | 64k                             | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Y                         | Y                     | Ι                    |

| PIC18(L)F27K40 | (3)              | 128k                            | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F45K40 | (2)              | 32k                             | 2048                 | 256                    | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F46K40 | (2)              | 64k                             | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F47K40 | (3)              | 128k                            | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

**Note 1:** Debugging Methods: (I) – Integrated on Chip.

Data Sheet Index: (Unshaded devices are described in this document.)

1. DS40001843 PIC18(L)F24/25K40 Data Sheet, 28-Pin, 8-bit Flash Microcontrollers

2. DS40001816 PIC18(L)F26/45/46K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

3. DS40001844 PIC18(L)F27/47K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

#### Pin Allocation Tables

#### TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F26K40)

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin (U)QFN | AD   | Reference                              | Comparator       | Timers               | CCP | CWG                 | ZCD   | Interrupt                    | EUSART                 | WSQ                   | ASSM                                         | Pull-up | Basic          |

|--------------------|--------------------------|---------------|------|----------------------------------------|------------------|----------------------|-----|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|----------------|

| RA0                | 2                        | 27            | ANA0 | _                                      | C1IN0-<br>C2IN0- |                      |     |                     | _     | IOCA0                        | —                      | —                     | _                                            | Y       | —              |

| RA1                | 3                        | 28            | ANA1 | _                                      | C1IN1-<br>C2IN1- | _                    | _   | _                   | _     | IOCA1                        | —                      | —                     | _                                            | Y       | _              |

| RA2                | 4                        | 1             | ANA2 | DAC1OUT1<br>Vref- (DAC)<br>Vref- (ADC) | C1IN0+<br>C2IN0+ | -                    | -   | -                   | Ι     | IOCA2                        | _                      |                       |                                              | Y       | _              |

| RA3                | 5                        | 2             | ANA3 | Vref+ (DAC)<br>Vref+ (ADC)             | C1IN1+           | -                    | -   |                     | _     | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | _                                            | Y       | —              |

| RA4                | 6                        | 3             | ANA4 | _                                      | _                | T0CKI <sup>(1)</sup> | _   | _                   | -     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       | _              |

| RA5                | 7                        | 4             | ANA5 | _                                      | _                | _                    | _   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _              |

| RA6                | 10                       | 7             | ANA6 | _                                      | —                | -                    | —   | —                   | _     | IOCA6                        | —                      | —                     | _                                            | Y       | CLKOUT<br>OSC2 |

| RA7                | 9                        | 6             | ANA7 | _                                      | _                | _                    | _   | _                   | _     | IOCA7                        | —                      | —                     | _                                            | Y       | OSC1<br>CLKIN  |

| RB0                | 21                       | 18            | ANB0 | _                                      | C2IN1+           | _                    | —   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | —                     | SS2 <sup>(1)</sup>                           | Y       | —              |

| RB1                | 22                       | 19            | ANB1 | _                                      | C1IN3-<br>C2IN3- | _                    | _   | _                   | _     | IOCB1<br>INT1 <sup>(1)</sup> | —                      | —                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | —              |

| RB2                | 23                       | 20            | ANB2 | _                                      | _                | _                    | _   | _                   | _     | IOCB2<br>INT2 <sup>(1)</sup> | —                      | —                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | —              |

| RB3                | 24                       | 21            | ANB3 | _                                      | C1IN2-<br>C2IN2- | _                    | _   | _                   | _     | IOCB3                        | —                      | —                     | _                                            | Y       | —              |

| RB4                | 25                       | 22            | ANB4 | _                                      | _                | T5G <sup>(1)</sup>   | _   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Y       | —              |

| RB5                | 26                       | 23            | ANB5 | _                                      | _                | T1G <sup>(1)</sup>   | _   | _                   | _     | IOCB5                        | —                      | _                     | _                                            | Y       | _              |

| RB6                | 27                       | 24            | ANB6 | _                                      | _                | _                    |     |                     | _     | IOCB6                        | CK2 <sup>(1)</sup>     | _                     | _                                            | Y       | ICSPCLK        |

| RB7                | 28                       | 25            | ANB7 | DAC1OUT2                               |                  | T6AIN <sup>(1)</sup> | _   | _                   | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     | _                                            | Y       | ICSPDAT        |

PIC18(L)F26/45/46K40

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for 1<sup>2</sup>C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the 1<sup>2</sup>C specific or SMBus input buffer thresholds.

| TABLI              | E 2:        | 40/         | 44-PIN /   | ALLO        | CATION | N TABLE (PI                             | C18(L)F          | -45/46K4                                                           | 40)                 |                     |       |                              |                        |                       |                                              |         |                 |

|--------------------|-------------|-------------|------------|-------------|--------|-----------------------------------------|------------------|--------------------------------------------------------------------|---------------------|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|-----------------|

| I/O <sup>(2)</sup> | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | A/D    | Reference                               | Comparator       | Timers                                                             | ССР                 | CWG                 | ZCD   | Interrupt                    | EUSART                 | WSQ                   | ASSM                                         | Pull-up | Basic           |

| RA0                | 2           | 17          | 19         | 19          | ANA0   | _                                       | C1INO-<br>C2IN0- | _                                                                  | —                   | —                   | _     | IOCA0                        | _                      | _                     | _                                            | Y       | —               |

| RA1                | 3           | 18          | 20         | 20          | ANA1   | —                                       | C1IN1-<br>C2IN1- | -                                                                  | —                   | —                   | _     | IOCA1                        | -                      | —                     | _                                            | Y       | —               |

| RA2                | 4           | 19          | 21         | 21          | ANA2   | DAC1OUT1<br>VREF- (DAC5)<br>VREF- (ADC) | C1IN0+<br>C2IN0+ | -                                                                  | -                   | _                   | _     | IOCA2                        | -                      | —                     | _                                            | Y       | _               |

| RA3                | 5           | 20          | 22         | 22          | ANA3   | VREF+ (DAC5)<br>VREF+ (ADC)             | C1IN1+           | -                                                                  | _                   | _                   |       | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | _                                            | Y       | _               |

| RA4                | 6           | 21          | 23         | 23          | ANA4   | _                                       | _                | T0CKI <sup>(1)</sup>                                               | _                   | _                   | _     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       | _               |

| RA5                | 7           | 22          | 24         | 24          | ANA5   | _                                       | _                | _                                                                  | _                   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _               |

| RA6                | 14          | 29          | 33         | 31          | ANA6   | —                                       | —                | _                                                                  | _                   | —                   | _     | IOCA6                        | _                      | —                     | _                                            | Y       | CLKOUT<br>OSC2  |

| RA7                | 13          | 28          | 32         | 30          | ANA7   | —                                       | _                | -                                                                  | —                   | _                   |       | IOCA7                        | -                      | -                     | _                                            | Y       | OSC1<br>CLKIN   |

| RB0                | 33          | 8           | 9          | 8           | ANB0   | _                                       | C2IN1+           | -                                                                  | _                   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | _                     | SS2 <sup>(1)</sup>                           | Y       | _               |

| RB1                | 34          | 9           | 10         | 9           | ANB1   | —                                       | C1IN3-<br>C2IN3- | -                                                                  | —                   | —                   |       | IOCB1<br>INT1 <sup>(1)</sup> | -                      | -                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | -               |

| RB2                | 35          | 10          | 11         | 10          | ANB2   | —                                       | -                | -                                                                  | _                   | _                   |       | IOCB2<br>INT2 <sup>(1)</sup> | -                      | -                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | _               |

| RB3                | 36          | 11          | 12         | 11          | ANB3   | —                                       | C1IN2-<br>C2IN2- | -                                                                  | —                   | —                   | -     | IOCB3                        | -                      | —                     | _                                            | Y       | _               |

| RB4                | 37          | 12          | 14         | 14          | ANB4   | —                                       | _                | T5G <sup>(1)</sup>                                                 | _                   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Y       | _               |

| RB5                | 38          | 13          | 15         | 15          | ANB5   | _                                       | _                | T1G <sup>(1)</sup>                                                 | —                   | _                   | _     | IOCB5                        | _                      | _                     | _                                            | Y       | —               |

| RB6                | 39          | 14          | 16         | 16          | ANB6   | _                                       | _                | —                                                                  | _                   | _                   | _     | IOCB6                        | CK2 <sup>(1)</sup>     | _                     | _                                            | Y       | ICSPCLK         |

| RB7                | 40          | 15          | 17         | 17          | ANB7   | DAC1OUT2                                | _                | T6AIN <sup>(1)</sup>                                               | —                   | _                   | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     | _                                            | Y       | ICSPDAT         |

| RC0                | 15          | 30          | 34         | 32          | ANC0   | _                                       | -                | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup> | -                   | -                   | Ι     | IOCC0                        | -                      |                       | _                                            | Y       | SOSCO           |

| RC1                | 16          | 31          | 35         | 35          | ANC1   | —                                       | _                | —                                                                  | CCP2 <sup>(1)</sup> | —                   | _     | IOCC1                        | _                      | _                     | _                                            | Y       | SOSCIN<br>SOSCI |

#### TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC18(L)F45/46K40)

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

**3:** These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I2C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I2C specific or SMBus input buffer thresholds.

# 4.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 4.1 Overview

The oscillator module has multiple clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 4-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 (Register 3-1) determine the type of oscillator that will be used when the device runs after Reset, including when it is first powered up.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the External Clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 100 kHz)

- 2. ECM External Clock Medium Power mode (100 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 8 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS Clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 4-1). Multiple device clock frequencies may be derived from these clock sources.

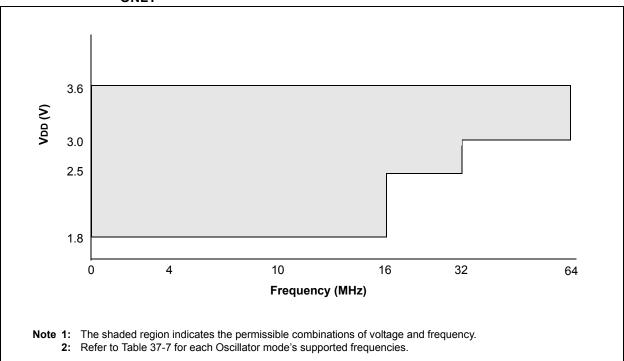

#### 4.3.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching. Refer to **Section 4.4 "Clock Switching"** for more information.

#### FIGURE 4-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for PIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

### 4.3.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 4.4 "Clock Switching" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory-calibrated and operates from 1 to 64 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

# PIC18(L)F26/45/46K40

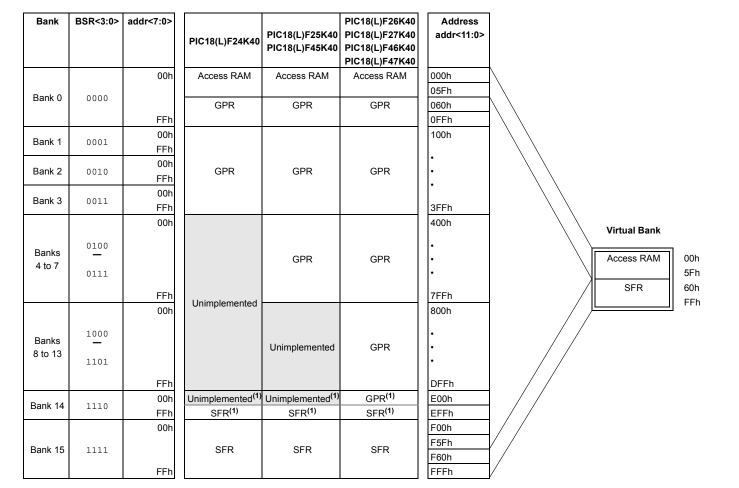

# FIGURE 10-4: DATA MEMORY MAP FOR PIC18(L)F2X/4XK40 DEVICES

Note 1: It depends on the number of SFRs. Refer to Table 10-3 and Table 10-4.

#### 10.4.5 STATUS REGISTER

The STATUS register, shown in Register 10-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu').

It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in **Section 35.0 "Instruction Set Summary"** and Table 35-3.

Note: The C and DC bits operate as the borrow and digit borrow bits, respectively, in subtraction.

| R/W-0/0                 | R/W/HC-0/0                               | R-0                             | R-1                         | R/W-0/0          | U-0                               | R/W-0/0         | R/W-0/0        |

|-------------------------|------------------------------------------|---------------------------------|-----------------------------|------------------|-----------------------------------|-----------------|----------------|

| SCANEN                  | SCANGO                                   | BUSY                            | INVALID                     | INTM             |                                   | MODE            | <1:0>          |

| bit 7                   |                                          |                                 |                             |                  |                                   |                 | bit            |

|                         |                                          |                                 |                             |                  |                                   |                 |                |

| Legend:<br>R = Readable | h:t                                      |                                 | h it                        | II – I Inimalan  | nantad hit raad                   | aa 'O'          |                |

| u = Bit is unch         |                                          | W = Writable<br>x = Bit is unkr |                             | •                | nented bit, read<br>at POR and BO |                 | thar Pasata    |

| '1' = Bit is set        | angeu                                    | 0' = Bit is clear               |                             |                  | eared by hardw                    |                 |                |

|                         |                                          |                                 | areu                        |                  | ealed by hardw                    | ale             |                |

| bit 7                   | SCANEN: Sca                              | anner Enable k                  | <sub>oit</sub> (1)          |                  |                                   |                 |                |

|                         | 1 = Scanner is                           |                                 |                             |                  |                                   |                 |                |

|                         |                                          |                                 | rnal states are             | reset            |                                   |                 |                |

| bit 6                   | SCANGO: Sc                               |                                 |                             |                  |                                   |                 |                |

|                         |                                          | peripheral.                     | ready signal, N             | IVM will be acc  | essed accordin                    | g to MDx and c  | lata passed    |

|                         | 0 = Scanner o                            |                                 | not occur                   |                  |                                   |                 |                |

| bit 5                   | BUSY: Scann                              | er Busy Indica                  | tor bit <sup>(4)</sup>      |                  |                                   |                 |                |

|                         | 1 = Scanner c                            |                                 |                             | (                |                                   |                 |                |

|                         |                                          |                                 | te (or never sta            | irted)           |                                   |                 |                |

| bit 4                   | INVALID: Sca                             |                                 |                             | n invalid addree | ss <sup>(6)</sup> or the scan     | ner was not set |                |

|                         |                                          |                                 | to a valid addr             |                  |                                   |                 | up conectly    |

| bit 3                   |                                          |                                 | pt Managemen                |                  | oit                               |                 |                |

|                         | If MODE = 10:                            |                                 |                             |                  |                                   |                 |                |

|                         | This bit is igno                         |                                 |                             |                  |                                   |                 |                |

|                         |                                          |                                 | until all data is t         |                  | ration; scanner                   | resumes after   | returning fro  |

|                         | interrupt                                |                                 |                             |                  |                                   |                 | returning no   |

|                         |                                          |                                 | by interrupts, t            | he interrupt res | sponse will be a                  | ffected         |                |

|                         | $\frac{\text{If MODE} = 00}{1 = SCANGO}$ |                                 | (to zoro) during            | interrunt oper   | ation; scan oper                  | ations resume   | aftar raturnir |

|                         | from inter                               |                                 | (to zero) during            |                  | allon, scan oper                  | allons resume   |                |

|                         | 0 = Interrupts                           | do not prevent                  | NVM access                  |                  |                                   |                 |                |

| bit 2                   | Unimplement                              |                                 |                             |                  |                                   |                 |                |

| bit 1-0                 |                                          |                                 | ss Mode bits <sup>(5)</sup> |                  |                                   |                 |                |

|                         | 11 = Triggered<br>10 = Peek mo           |                                 |                             |                  |                                   |                 |                |

|                         | 01 = Burst mc                            |                                 |                             |                  |                                   |                 |                |

|                         | 00 = Concurre                            | ent mode                        |                             |                  |                                   |                 |                |

| Note 1: Set             | ting SCANEN =                            |                                 | I0 register) doe            | s not affect any | y other register                  | content.        |                |

|                         | s bit is cleared v                       |                                 |                             | -                |                                   |                 |                |

|                         | NTM = 1, this bit<br>SY = 1 when the     |                                 | •                           | ,                | •                                 |                 |                |

|                         | e Table 13-2 for                         |                                 |                             |                  | serius a reauy                    | signai.         |                |

|                         | invalid address                          |                                 |                             | ige of PFM is s  | canned and the                    | value of LADR   | rolls over. A  |

| inva                    | alid address car                         | also occur if t                 | he value in the             |                  |                                   |                 |                |

|                         | pped in the mer<br>CEN and CRCG          |                                 |                             | ting SCANGO      | nit Refer to Soo                  | tion 13 9 "Proc | Iram Memor     |

|                         | an Configuratio                          |                                 | 5 301 0010 0010 301         |                  |                                   |                 |                |

#### REGISTER 13-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

| R/W-x/u                                               | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u         | R/W-x/u          | R/W-x/u  | R/W-x/u |  |  |  |  |

|-------------------------------------------------------|---------|-------------------|---------|-----------------|------------------|----------|---------|--|--|--|--|

| LATx7                                                 | LATx6   | LATx5             | LATx4   | LATx3           | LATx2            | LATx1    | LATx0   |  |  |  |  |

| bit 7                                                 |         |                   |         |                 |                  |          | bit 0   |  |  |  |  |

|                                                       |         |                   |         |                 |                  |          |         |  |  |  |  |

| Legend:                                               |         |                   |         |                 |                  |          |         |  |  |  |  |

| R = Readable                                          | bit     | W = Writable      | bit     | U = Unimpler    | nented bit, read | 1 as '0' |         |  |  |  |  |

| '1' = Bit is set                                      |         | '0' = Bit is clea | ared    | x = Bit is unkr | nown             |          |         |  |  |  |  |

| -n/n = Value at POR and BOR/Value at all other Resets |         |                   |         |                 |                  |          |         |  |  |  |  |

#### REGISTER 15-3: LATx: LATx REGISTER<sup>(1)</sup>

bit 7-0 LATx<7:0>: Rx7:Rx0 Output Latch Value bits

**Note 1:** Writes to LATx are equivalent with writes to the corresponding PORTx register. Reads from LATx register return register values, not I/O pin values.

|      | Dev        | vice          |       |       |       |       |       |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| LATA | Х          | Х             | LATA7 | LATA6 | LATA5 | LATA4 | LATA3 | LATA2 | LATA1 | LATA0 |

| LATB | Х          | Х             | LATB7 | LATB6 | LATB5 | LATB4 | LATB3 | LATB2 | LATB1 | LATB0 |

| LATC | Х          | Х             | LATC7 | LATC6 | LATC5 | LATC4 | LATC3 | LATC2 | LATC1 | LATC0 |

| LATD | Х          |               | _     | _     | _     | _     | —     | _     | —     | _     |

|      |            | Х             | LATD7 | LATD6 | LATD5 | LATD4 | LATD3 | LATD2 | LATD1 | LATD0 |

| LATE | Х          |               | _     | —     | —     | —     | —     | _     | —     | _     |

|      |            | Х             | _     | _     | —     | _     | —     | LATE2 | LATE1 | LATE0 |

#### TABLE 15-4: LAT REGISTERS

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSELx7 | ANSELx6 | ANSELx5 | ANSELx4 | ANSELx3 | ANSELx2 | ANSELx1 | ANSELx0 |

| bit 7   |         |         |         |         | •       | •       | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

#### REGISTER 15-4: ANSELX: ANALOG SELECT REGISTER

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0

- ANSELx<7:0>: Analog Select on Pins Rx<7:0>

- 1 = Digital Input buffers are disabled.

- 0 = ST and TTL input devices are enabled

|        | Dev        | /ice          |         |         |         |         |         |         |         |         |

|--------|------------|---------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Name   | 28<br>Pins | 40/44<br>Pins | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

| ANSELA | Х          | Х             | ANSELA7 | ANSELA6 | ANSELA5 | ANSELA4 | ANSELA3 | ANSELA2 | ANSELA1 | ANSELA0 |

| ANSELB | Х          | Х             | ANSELB7 | ANSELB6 | ANSELB5 | ANSELB4 | ANSELB3 | ANSELB2 | ANSELB1 | ANSELB0 |

| ANSELC | Х          | Х             | ANSELC7 | ANSELC6 | ANSELC5 | ANSELC4 | ANSELC3 | ANSELC2 | ANSELC1 | ANSELC0 |

| ANSELD | Х          |               | _       | _       | _       | _       | _       | _       | _       | —       |

|        |            | Х             | ANSELD7 | ANSELD6 | ANSELD5 | ANSELD4 | ANSELD3 | ANSELD2 | ANSELD1 | ANSELD0 |

| ANSELE | Х          |               | _       | _       | _       | _       | _       | _       | _       | —       |

|        |            | Х             | _       | _       | _       | _       | _       | ANSELE2 | ANSELE1 | ANSELE0 |

#### TABLE 15-5:ANALOG SELECT PORT REGISTERS

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|--------|-----------------------|--------|--------|--------|

| IOCAP | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3                | IOCAP2 | IOCAP1 | IOCAP0 |

| IOCAN | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3                | IOCAN2 | IOCAN1 | IOCAN0 |

| IOCAF | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3                | IOCAF2 | IOCAF1 | IOCAF0 |

| IOCBP | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3                | IOCBP2 | IOCBP1 | IOCBP0 |

| IOCBN | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3                | IOCBN2 | IOCBN1 | IOCBN0 |

| IOCBF | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3                | IOCBF2 | IOCBF1 | IOCBF0 |

| IOCCP | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3                | IOCCP2 | IOCCP1 | IOCCP0 |

| IOCCN | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3                | IOCCN2 | IOCCN1 | IOCCN0 |

| IOCCF | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3                | IOCCF2 | IOCCF1 | IOCCF0 |

| IOCEP | —      | _      | _      | _      | IOCEP3 <sup>(1)</sup> | _      | —      | —      |

| IOCEN |        |        |        |        | IOCEN3 <sup>(1)</sup> |        |        |        |

| IOCEF |        |        |        |        | IOCEF3 <sup>(1)</sup> |        |        | _      |

TABLE 16-1: IOC REGISTERS

Note 1: If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and IOC on RE3 is not available.

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------|-----------|--------|--------|--------|---------|---------|---------|---------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | IPEN   | —      | —      | INT2EDG | INT1EDG | INT0EDG | 170                 |

| IOCxF  | IOCxF7   | IOCxF6    | IOCxF5 | IOCxF4 | IOCxF3 | IOCxF2  | IOCxF1  | IOCxF0  | 211                 |

| IOCxN  | IOCxN7   | IOCxN6    | IOCxN5 | IOCxN4 | IOCxN3 | IOCxN2  | IOCxN1  | IOCxN0  | 211                 |

| IOCxP  | IOCxP7   | IOCxP6    | IOCxP5 | IOCxP4 | IOCxP3 | IOCxP2  | IOCxP1  | IOCxP0  | 211                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

# 20.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the PRx value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

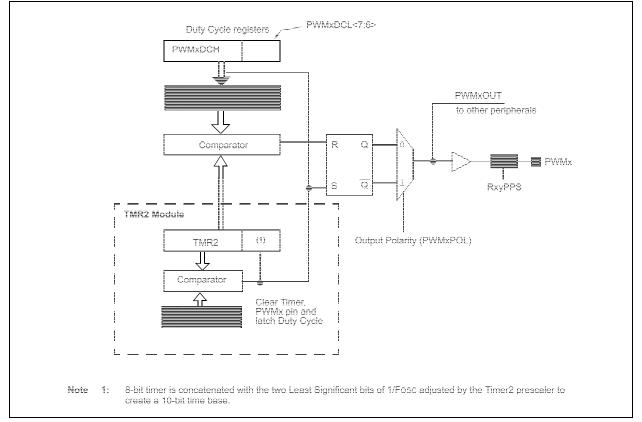

## 22.0 PULSE-WIDTH MODULATION (PWM)

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PRx

- TxCON

- PWMxDCH

- PWMxDCL

- PWMxCON

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin. Each PWM module can select the timer source that controls the module. Each module has an independent timer selection which can be accessed using the CCPTMRS register (Register 21-2). Please note that the PWM mode operation is described with respect to TMR2 in the following sections.

Figure 22-1 shows a simplified block diagram of PWM operation.

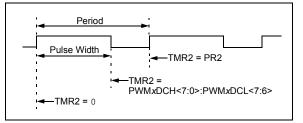

Figure 22-2 shows a typical waveform of the PWM signal.

### FIGURE 22-1: SIMPLIFIED PWM BLOCK DIAGRAM

FIGURE 22-2:

PWM OUTPUT

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 22.1.9 "Setup for PWM Operation using PWMx Pins".

| R/W-0/0         | R/W-1/1                                                                                                                                                                                                                                                                                                              | R/W-0/0                                                            | R/W-1/1 | R/W-0/0              | R/W-1/1          | R/W-0/0            | R/W-1/1 |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------|----------------------|------------------|--------------------|---------|

| P4TSEL<1:0>     |                                                                                                                                                                                                                                                                                                                      | P3TSEL<1:0>                                                        |         | C2TSEL<1:0>          |                  | C1TSEL<1:0>        |         |

| bit 7           |                                                                                                                                                                                                                                                                                                                      |                                                                    |         |                      |                  |                    | bit 0   |

|                 |                                                                                                                                                                                                                                                                                                                      |                                                                    |         |                      |                  |                    |         |

| Legend:         |                                                                                                                                                                                                                                                                                                                      |                                                                    |         |                      |                  |                    |         |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                  | W = Writable                                                       | bit     | U = Unimplen         | nented bit, read | l as '0'           |         |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                   |         | '0' = Bit is cleared |                  | x = Bit is unknown |         |

| bit 7-6         | 11 = PWM4<br>10 = PWM4                                                                                                                                                                                                                                                                                               | >: PWM4 Time<br>based on TMR<br>based on TMR<br>based on TMR<br>ed | 6<br>4  | 'S                   |                  |                    |         |

| bit 5-4         | P3TSEL<1:0>: PWM3 Timer Selection bits<br>11 = PWM3 based on TMR6<br>10 = PWM3 based on TMR4<br>01 = PWM3 based on TMR2<br>00 = Reserved                                                                                                                                                                             |                                                                    |         |                      |                  |                    |         |

| bit 3-2         | <b>C2TSEL&lt;1:0&gt;:</b> CCP2 Timer Selection bits<br>11 = CCP2 is based off Timer5 in Capture/Compare mode and Timer6 in PWM mode<br>10 = CCP2 is based off Timer3 in Capture/Compare mode and Timer4 in PWM mode<br>01 = CCP2 is based off Timer1 in Capture/Compare mode and Timer2 in PWM mode<br>00 = Reserved |                                                                    |         |                      |                  |                    |         |

| bit 1-0         | t 1-0 <b>C1TSEL&lt;1:0&gt;:</b> CCP1 Timer Selection bit<br>11 = CCP1 is based off Timer5 in Capture<br>10 = CCP1 is based off Timer3 in Capture<br>01 = CCP1 is based off Timer1 in Capture<br>00 = Reserved                                                                                                        |                                                                    |         |                      | le and Timer4 i  | n PWM mode         |         |

#### REGISTER 22-2: CCPTMRS: CCP TIMERS CONTROL REGISTER

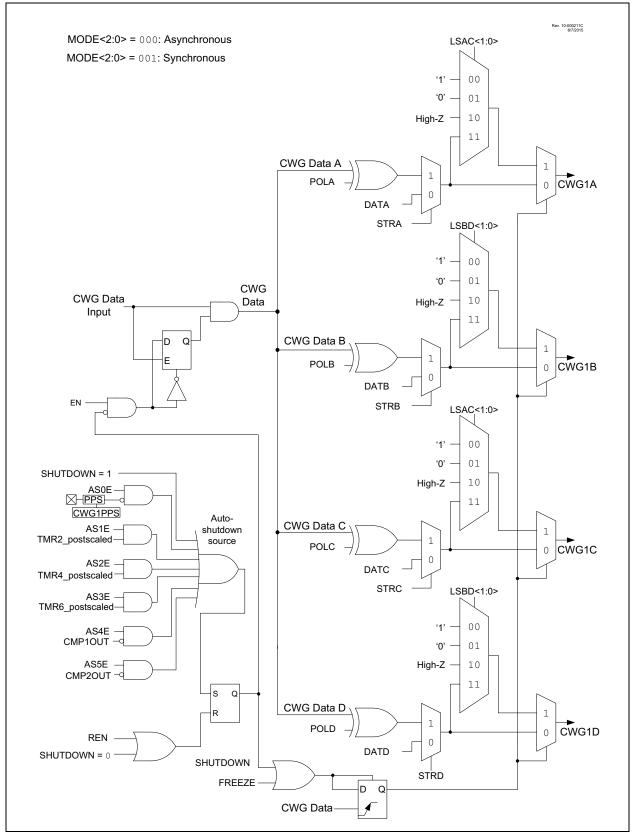

#### FIGURE 24-11: SIMPLIFIED CWG BLOCK DIAGRAM (OUTPUT STEERING MODES)

| U-0                  | U-0                                                                                                                                                                                                             | R/W-0/0                                                                                                                    | R/W-0/0              | U-0                                                   | U-0              | R/W-0/0          | R/W-0/0  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------|------------------|------------------|----------|--|--|--|

| _                    | _                                                                                                                                                                                                               | CHPOL                                                                                                                      | CHSYNC               | —                                                     | —                | CLPOL            | CLSYNC   |  |  |  |

| bit 7                |                                                                                                                                                                                                                 |                                                                                                                            |                      | ·                                                     |                  |                  | bit (    |  |  |  |

|                      |                                                                                                                                                                                                                 |                                                                                                                            |                      |                                                       |                  |                  |          |  |  |  |

| Legend:              |                                                                                                                                                                                                                 |                                                                                                                            |                      |                                                       |                  |                  |          |  |  |  |

| R = Reada            | ble bit                                                                                                                                                                                                         | W = Writable bit                                                                                                           |                      | U = Unimplemented bit, read as '0'                    |                  |                  |          |  |  |  |

| u = Bit is unchanged |                                                                                                                                                                                                                 | x = Bit is unknown                                                                                                         |                      | -n/n = Value at POR and BOR/Value at all other Resets |                  |                  |          |  |  |  |

| '1' = Bit is s       | set                                                                                                                                                                                                             | '0' = Bit is clea                                                                                                          | '0' = Bit is cleared |                                                       |                  |                  |          |  |  |  |

|                      |                                                                                                                                                                                                                 |                                                                                                                            |                      |                                                       |                  |                  |          |  |  |  |

| bit 7-6              | Unimplem                                                                                                                                                                                                        | ented: Read as '                                                                                                           | 0'                   |                                                       |                  |                  |          |  |  |  |

| bit 5                | CHPOL: M                                                                                                                                                                                                        | odulator High Ca                                                                                                           | rrier Polarity S     | elect bit                                             |                  |                  |          |  |  |  |

|                      | 1 = Select                                                                                                                                                                                                      | 1 = Selected high carrier signal is inverted                                                                               |                      |                                                       |                  |                  |          |  |  |  |

|                      | 0 = Select                                                                                                                                                                                                      | 0 = Selected high carrier signal is not inverted                                                                           |                      |                                                       |                  |                  |          |  |  |  |

| bit 4                | CHSYNC:                                                                                                                                                                                                         | CHSYNC: Modulator High Carrier Synchronization Enable bit                                                                  |                      |                                                       |                  |                  |          |  |  |  |

|                      |                                                                                                                                                                                                                 | 1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the<br>low time carrier |                      |                                                       |                  |                  |          |  |  |  |

|                      | 0 = Modula                                                                                                                                                                                                      | 0 = Modulator output is not synchronized to the high time carrier signal <sup>(1)</sup>                                    |                      |                                                       |                  |                  |          |  |  |  |

| bit 3-2              | Unimplem                                                                                                                                                                                                        | Unimplemented: Read as '0'                                                                                                 |                      |                                                       |                  |                  |          |  |  |  |

| bit 1                | CLPOL: M                                                                                                                                                                                                        | CLPOL: Modulator Low Carrier Polarity Select bit                                                                           |                      |                                                       |                  |                  |          |  |  |  |

|                      | 1 = Select                                                                                                                                                                                                      | 1 = Selected low carrier signal is inverted                                                                                |                      |                                                       |                  |                  |          |  |  |  |

|                      | 0 = Select                                                                                                                                                                                                      | 0 = Selected low carrier signal is not inverted                                                                            |                      |                                                       |                  |                  |          |  |  |  |

| bit 0                | <ul> <li>CLSYNC: Modulator Low Carrier Synchronization Enable bit</li> <li>1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the hi<br/>time carrier</li> </ul> |                                                                                                                            |                      |                                                       |                  | itch to the hig  |          |  |  |  |

|                      | 0 = Modula                                                                                                                                                                                                      | 0 = Modulator output is not synchronized to the low time carrier signal <sup>(1)</sup>                                     |                      |                                                       |                  |                  |          |  |  |  |

| Noto 1.No.           | rrowed carrier p                                                                                                                                                                                                | ulee widthe or en                                                                                                          |                      | in the signal s                                       | troom if the cor | rior is not sync | bronizod |  |  |  |

#### REGISTER 25-2: MDCON1: MODULATION CONTROL REGISTER 1

Note 1:Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| U-0              | U-0              | U-0                                                                                | R/W-0/0              | R/W-0/0       | R/W-0/0            | R/W-0/0            | R/W-0/0 |  |  |  |

|------------------|------------------|------------------------------------------------------------------------------------|----------------------|---------------|--------------------|--------------------|---------|--|--|--|

| _                | _                | —                                                                                  |                      |               | ADACT<4:0>         |                    |         |  |  |  |

| bit 7            |                  |                                                                                    |                      |               |                    |                    | bit     |  |  |  |

|                  |                  |                                                                                    |                      |               |                    |                    |         |  |  |  |

| Legend:          |                  |                                                                                    |                      |               |                    |                    |         |  |  |  |

| R = Readab       | le bit           | W = Writable b                                                                     | it                   | U = Unimpleme | ented bit, read as | s 'O'              |         |  |  |  |

| u = Bit is une   | changed          | x = Bit is unkno                                                                   | x = Bit is unknown   |               | POR and BOR/       | /alue at all other | Resets  |  |  |  |

| '1' = Bit is set |                  | '0' = Bit is clea                                                                  | '0' = Bit is cleared |               |                    |                    |         |  |  |  |

| bit 7-5          | Unimplom         | nented: Read as '0'                                                                |                      |               |                    |                    |         |  |  |  |

|                  | •                |                                                                                    | Time Oalest          | Dite          |                    |                    |         |  |  |  |

| bit 4-0          |                  | ADACT<4:0>: Auto-Conversion Trigger Select Bits<br>11111 = Software write to ADPCH |                      |               |                    |                    |         |  |  |  |

|                  |                  | 11111 = Software write to ADPCH<br>11110 = Reserved, do not use                    |                      |               |                    |                    |         |  |  |  |

|                  |                  | 1110 = Software read of ADRESH                                                     |                      |               |                    |                    |         |  |  |  |

|                  | 11100 <b>=</b> S | 11100 = Software read of ADERRH                                                    |                      |               |                    |                    |         |  |  |  |

|                  | 11011 <b>= F</b> | 11011 = Reserved, do not use                                                       |                      |               |                    |                    |         |  |  |  |

|                  | •                |                                                                                    |                      |               |                    |                    |         |  |  |  |

|                  | •                |                                                                                    |                      |               |                    |                    |         |  |  |  |

|                  | •<br>10000 = F   | •<br>10000 = Reserved, do not use                                                  |                      |               |                    |                    |         |  |  |  |

|                  |                  | 01111 = Interrupt-on-change Interrupt Flag                                         |                      |               |                    |                    |         |  |  |  |

|                  |                  | 01110 = C2 out                                                                     |                      |               |                    |                    |         |  |  |  |

|                  | 01101 <b>= C</b> | 01101 = C1_out                                                                     |                      |               |                    |                    |         |  |  |  |

|                  |                  | 01100 = PWM4_out                                                                   |                      |               |                    |                    |         |  |  |  |

|                  |                  | 01011 = PWM3_out                                                                   |                      |               |                    |                    |         |  |  |  |

|                  |                  | 01010 = CCP2_trigger                                                               |                      |               |                    |                    |         |  |  |  |

|                  |                  | 01001 = CCP1_trigger<br>01000 = TMR6 postscaled                                    |                      |               |                    |                    |         |  |  |  |

|                  |                  | 00111 = TMR5_overflow                                                              |                      |               |                    |                    |         |  |  |  |

|                  |                  | 00110 = TMR4_postscaled                                                            |                      |               |                    |                    |         |  |  |  |

|                  | 00101 <b>= T</b> | 00101 = TMR3_overflow                                                              |                      |               |                    |                    |         |  |  |  |

|                  |                  | MR2_postscaled                                                                     |                      |               |                    |                    |         |  |  |  |

|                  |                  | MR1_overflow                                                                       |                      |               |                    |                    |         |  |  |  |

|                  |                  | MR0_overflow                                                                       |                      |               |                    |                    |         |  |  |  |

|                  |                  | Pin selected by ADAC<br>External Trigger Disal                                     |                      |               |                    |                    |         |  |  |  |

|                  | 00000 = E        | -xternar myyer Disar                                                               | Jieu                 |               |                    |                    |         |  |  |  |

## REGISTER 31-32: ADACT: ADC AUTO CONVERSION TRIGGER CONTROL REGISTER

#### 35.1.1 STANDARD INSTRUCTION SET

| ADDLW                                               | ADD liter             | ADD literal to W                                                                          |            |  |  |  |  |

|-----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Syntax:                                             | ADDLW                 | ADDLW k                                                                                   |            |  |  |  |  |

| Operands:                                           | $0 \le k \le 255$     | 5                                                                                         |            |  |  |  |  |

| Operation:                                          | (W) + k $\rightarrow$ | $(W) + k \to W$                                                                           |            |  |  |  |  |

| Status Affected:                                    | N, OV, C, [           | N, OV, C, DC, Z                                                                           |            |  |  |  |  |

| Encoding:                                           | 0000                  | 1111 kk                                                                                   | kk kkkk    |  |  |  |  |

| Description:                                        |                       | The contents of W are added to the<br>8-bit literal 'k' and the result is placed in<br>W. |            |  |  |  |  |

| Words:                                              | 1                     | 1                                                                                         |            |  |  |  |  |

| Cycles:                                             | 1                     | 1                                                                                         |            |  |  |  |  |

| Q Cycle Activity                                    | <u>.</u>              |                                                                                           |            |  |  |  |  |

| Q1                                                  | Q2                    | Q3                                                                                        | Q4         |  |  |  |  |

| Decode                                              | Read<br>literal 'k'   | Process<br>Data                                                                           | Write to W |  |  |  |  |

| Example:<br>Before Inst<br>W<br>After Instru<br>W = | ruction<br>= 10h      | 15h                                                                                       |            |  |  |  |  |