#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 4.1 Overview

The oscillator module has multiple clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 4-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz-crystal resonators and ceramic resonators. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, ECH, ECM, ECL) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability of crystal oscillator sources.

The RSTOSC bits of Configuration Word 1 (Register 3-1) determine the type of oscillator that will be used when the device runs after Reset, including when it is first powered up.

If an external clock source is selected, the FEXTOSC bits of Configuration Word 1 must be used in conjunction with the RSTOSC bits to select the External Clock mode.

The external oscillator module can be configured in one of the following clock modes, by setting the FEXTOSC<2:0> bits of Configuration Word 1:

- 1. ECL External Clock Low-Power mode (below 100 kHz)

- 2. ECM External Clock Medium Power mode (100 kHz to 8 MHz)

- 3. ECH External Clock High-Power mode (above 8 MHz)

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (between 100 kHz and 8 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (above 4 MHz)

The ECH, ECM, and ECL Clock modes rely on an external logic level signal as the device clock source. The LP, XT, and HS Clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The internal oscillator block produces low and high-frequency clock sources, designated LFINTOSC and HFINTOSC. (see Internal Oscillator Block, Figure 4-1). Multiple device clock frequencies may be derived from these clock sources.

| U-0            | R/W-0/0                       | R/W-0/0           | U-0           | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0              |

|----------------|-------------------------------|-------------------|---------------|----------------|------------------|------------------|----------------------|

| _              | DACMD                         | ADCMD             |               | —              | CMP2MD           | CMP1MD           | ZCDMD <sup>(1)</sup> |

| bit 7          |                               |                   |               |                |                  |                  | bit C                |

|                |                               |                   |               |                |                  |                  |                      |

| Legend:        |                               |                   |               |                |                  |                  |                      |

| R = Reada      | ble bit                       | W = Writable      | bit           | U = Unimpler   | mented bit, read | d as '0'         |                      |

| u = Bit is u   | nchanged                      | x = Bit is unkr   | iown          | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets         |

| '1' = Bit is s | set                           | '0' = Bit is clea | ared          | q = Value dep  | pends on condit  | tion             |                      |

|                |                               |                   |               |                |                  |                  |                      |

| bit 7          | Unimplemer                    | nted: Read as 'o  | )'            |                |                  |                  |                      |

| bit 6          | DACMD: Dis                    | able DAC bit      |               |                |                  |                  |                      |

|                |                               | dule disabled     |               |                |                  |                  |                      |

|                | 0 = DAC mo                    | dule enabled      |               |                |                  |                  |                      |

| bit 5          | ADCMD: Dis                    | able ADC bit      |               |                |                  |                  |                      |

|                |                               | dule disabled     |               |                |                  |                  |                      |

|                |                               | dule enabled      |               |                |                  |                  |                      |

| bit 4-3        | Unimplemer                    | nted: Read as '   | )'            |                |                  |                  |                      |

| bit 2          | CMP2MD: D                     | isable Compara    | tor CMP2 bit  |                |                  |                  |                      |

|                |                               | nodule disabled   |               |                |                  |                  |                      |

|                |                               | nodule enabled    |               |                |                  |                  |                      |

| bit 1          |                               | isable Compara    | tor CMP1 bit  |                |                  |                  |                      |

|                |                               | nodule disabled   |               |                |                  |                  |                      |

|                |                               | nodule enabled    |               | (1)            |                  |                  |                      |

| bit 0          |                               | able Zero-Cross   | S Detect modu | ule bit"       |                  |                  |                      |

|                | 1 = ZCD mod                   |                   |               |                |                  |                  |                      |

|                | 0 = ZCD mod                   | dule enabled      |               |                |                  |                  |                      |

| Note 1         | Subject to $\overline{7CD}$ k |                   | 4             |                |                  |                  |                      |

#### REGISTER 7-3: PMD2: PMD CONTROL REGISTER 2

**Note 1:** Subject to ZCD bit in CONFIG2H.

| Address | Name     | Bit 7           | Bit 6                      | Bit 5            | Bit 4             | Bit 3          | Bit 2     | Bit 1  | Bit 0    | <u>Value on</u><br>POR, BOR |

|---------|----------|-----------------|----------------------------|------------------|-------------------|----------------|-----------|--------|----------|-----------------------------|

| FC1h    | TMR5L    | Holding Registe | er for the Least           | Significant Byte | e of the 16-bit T | MR5 Register   |           |        |          | 00000000                    |

| FC0h    | T2RST    | —               | _                          | —                | _                 |                | RSEL      | <3:0>  |          | 0000                        |

| FBFh    | T2CLKCON | -               | _                          | _                | _                 |                | CS<       | :3:0>  |          | 0000                        |

| FBEh    | T2HLT    | PSYNC           | CPOL                       | CSYNC            |                   |                | MODE<4:0> |        |          | 00000000                    |

| FBDh    | T2CON    | ON              |                            | CKPS<2:0>        |                   |                | OUTP      | S<3:0> |          | 00000000                    |

| FBCh    | T2PR     | TMR2 Period R   | egister                    |                  |                   |                |           |        |          | 11111111                    |

| FBBh    | T2TMR    | Holding Registe | er for the 8-bit 1         | MR2 Register     |                   |                |           |        |          | 00000000                    |

| FBAh    | T4RST    | —               | _                          | —                | _                 |                | RSEL      | <3:0>  |          | 0000                        |

| FB9h    | T4CLKCON | -               | _                          | _                | _                 |                |           | 0000   |          |                             |

| FB8h    | T4HLT    | PSYNC           | CPOL                       | CSYNC            |                   |                | MODE<4:0> |        |          | 00000000                    |

| FB7h    | T4CON    | ON              |                            | CKPS<2:0>        |                   |                | OUTP      | S<3:0> |          | 00000000                    |

| FB6h    | T4PR     | TMR4 Period R   | egister                    |                  |                   |                |           |        |          | 11111111                    |

| FB5h    | T4TMR    | Holding Registe | er for the 8-bit 1         | MR4 Register     |                   |                |           |        |          | 00000000                    |

| FB4h    | T6RST    | -               | _                          | _                | _                 |                | RSEL      | <3:0>  |          | 0000                        |

| FB3h    | T6CLKCON | _               | _                          | _                | _                 |                | CS<       | :3:0>  |          | 0000                        |

| FB2h    | T6HLT    | PSYNC           | PSYNC CPOL CSYNC MODE<4:0> |                  |                   |                |           |        | 00000000 |                             |

| FB1h    | T6CON    | ON              | DN CKPS<2:0> OUTPS<3:0>    |                  |                   |                |           |        | 00000000 |                             |

| FB0h    | T6PR     | TMR6 Period R   | egister                    |                  |                   |                |           |        |          | 11111111                    |

| FAFh    | T6TMR    | Holding Registe | er for the 8-bit 1         | MR6 Register     |                   |                |           |        |          | 00000000                    |

| FAEh    | CCPTMRS  | P4TSEL          | <1:0>                      | P3TSE            | L<1:0>            | C2TSI          | EL<1:0>   | C1TS   | EL<1:0>  | 01010101                    |

| FADh    | CCP1CAP  | -               | _                          | _                | _                 | -              | —         | CTS    | S<1:0>   | 00                          |

| FACh    | CCP1CON  | EN              | _                          | OUT              | FMT               |                | MODE      | =<3:0> |          | 0-000000                    |

| FABh    | CCPR1H   | Capture/Compa   | are/PWM Regis              | ster 1 (MSB)     |                   |                |           |        |          | xxxxxxxx                    |

| FAAh    | CCPR1L   | Capture/Compa   | are/PWM Regis              | ster 1 (LSB)     |                   |                |           |        |          | xxxxxxx                     |

| FA9h    | CCP2CAP  | —               | _                          | _                | —                 | -              | —         | CTS    | S<1:0>   | 00                          |

| FA8h    | CCP2CON  | EN              | _                          | OUT              | FMT               |                | MODE      | =<3:0> |          | 0-000000                    |

| FA7h    | CCPR2H   | Capture/Compa   | are/PWM Regis              | ster 2 (MSB)     |                   |                |           |        |          | xxxxxxxx                    |

| FA6h    | CCPR2L   | Capture/Compa   | are/PWM Regis              | ster 2 (LSB)     |                   |                |           |        |          | xxxxxxxx                    |

| FA5h    | PWM3CON  | EN              | _                          | OUT              | POL               | -              | —         | —      | _        | 0-00                        |

| FA4h    | PWM3DCH  |                 |                            |                  | DC                | <7:0>          |           |        |          | xxxxxxxx                    |

| FA3h    | PWM3DCL  | DC<9            | 9:8>                       | _                | _                 | -              | —         | —      | _        | xx                          |

| FA2h    | PWM4CON  | EN              | —                          | OUT              | POL               | —              | —         | —      | —        | 0-00                        |

| FA1h    | PWM4DCH  |                 |                            |                  | DC                | 27:0>          |           |        |          | xxxxxxxx                    |

| FA0h    | PWM4DCL  | DC<9            | 9:8>                       | —                | —                 | -              | —         | —      | —        | xx                          |

| F9Fh    | BAUD1CON | ABDOVF          | RCIDL                      | _                | SCKP              | BRG16          | _         | WUE    | ABDEN    | 01-00-00                    |

| F9Eh    | TX1STA   | CSRC            | TX9                        | TXEN             | SYNC              | SENDB          | BRGH      | TRMT   | TX9D     | 00000010                    |

| F9Dh    | RC1STA   | SPEN            | RX9                        | SREN             | CREN              | ADDEN          | FERR      | OERR   | RX9D     | 00000000                    |

| F9Ch    | SP1BRGH  |                 |                            | EUSA             | RT1 Baud Rat      | e Generator, H | igh Byte  |        |          | 00000000                    |

#### TABLE 10-5:REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

**3:** Not available on PIC18(L)F45K40 devices.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

#### 10.6.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

## 10.7 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

## 10.7.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 10.7.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 10-7.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 35.2.1 "Extended Instruction Syntax"**.

|                 |                                |                  |                | = = = = = = =    | . (              |                |         |  |  |  |  |  |

|-----------------|--------------------------------|------------------|----------------|------------------|------------------|----------------|---------|--|--|--|--|--|

| R/W-0/0         | R/W-0/0                        | R/W-0/0          | U-0            | U-0              | U-0              | U-0            | R/W-0/0 |  |  |  |  |  |

| SCANIF          | CRCIF                          | NVMIF            | —              | _                | —                | —              | CWG1IF  |  |  |  |  |  |

| bit 7           |                                |                  |                |                  |                  |                | bit 0   |  |  |  |  |  |

|                 |                                |                  |                |                  |                  |                |         |  |  |  |  |  |

| Legend:         |                                |                  |                |                  |                  |                |         |  |  |  |  |  |

| R = Readable    | bit                            | W = Writable I   | bit            | U = Unimpler     | mented bit, read | l as '0'       |         |  |  |  |  |  |

| -n = Value at I | POR                            | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unk | nown    |  |  |  |  |  |

|                 |                                |                  |                |                  |                  |                |         |  |  |  |  |  |

| bit 7           | SCANIF: SC/                    | AN Interrupt Fla | ıg bit         |                  |                  |                |         |  |  |  |  |  |

|                 | 1 = SCAN inte                  | errupt has occu  | rred (must be  | e cleared in sof | tware)           |                |         |  |  |  |  |  |

|                 | 0 = SCAN inte                  | errupt has not o | occurred or ha | as not been sta  | irted            |                |         |  |  |  |  |  |

| bit 6           | CRCIF: CRC                     | Interrupt Flag b | bit            |                  |                  |                |         |  |  |  |  |  |

|                 | 1 = CRC inter                  | rrupt has occuri | red (must be   | cleared in softw | vare)            |                |         |  |  |  |  |  |

|                 | 0 = CRC inter                  | rrupt has not oc | curred or has  | s not been star  | ted              |                |         |  |  |  |  |  |

| bit 5           | NVMIF: NVM                     | Interrupt Flag I | oit            |                  |                  |                |         |  |  |  |  |  |

|                 | 1 = NVM inte                   | rrupt has occur  | red (must be   | cleared in soft  | ware)            |                |         |  |  |  |  |  |

|                 | 0 = NVM inte                   | rrupt has not oc | curred or has  | s not been star  | ted              |                |         |  |  |  |  |  |

| bit 4-1         | Unimplemen                     | ited: Read as 'd | )'             |                  |                  |                |         |  |  |  |  |  |

| bit 0           | CWG1IF: CWG Interrupt Flag bit |                  |                |                  |                  |                |         |  |  |  |  |  |

|                 |                                | errupt has occur |                |                  |                  |                |         |  |  |  |  |  |

|                 | 0 = CWG inte                   | errupt has not o | ccurred or ha  | s not been star  | ted              |                |         |  |  |  |  |  |

## REGISTER 14-9: PIR7: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 7

## 16.0 INTERRUPT-ON-CHANGE

PORTA, PORTB, PORTC and pin RE3 of PORTE can be configured to operate as Interrupt-on-Change (IOC) pins on PIC18(L)F2x/4xK40 family devices. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 16-1 is a block diagram of the IOC module.

## 16.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 16.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 16.3 Interrupt Flags

The IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits located in the IOCAF, IOCBF, IOCCF and IOCEF registers respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIRO register reflects the status of all IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits.

## 16.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 16-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

| MOVLW | 0xff   |              |

|-------|--------|--------------|

| XORWF | IOCAF, | W            |

| ANDWF | IOCAF, | F            |

|       |        |              |

|       | XORWF  | XORWF IOCAF, |

## 16.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

## PIC18(L)F26/45/46K40

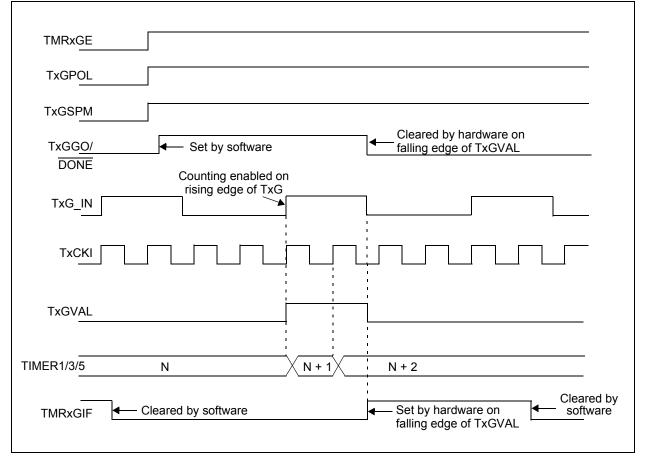

| FIGURE 19-5: | TIMER1/3/5 GATE TOGGLE MODE           |

|--------------|---------------------------------------|

|              |                                       |

| TMRxGE       |                                       |

| TxGPOL       |                                       |

| TxGTM        |                                       |

| TxTxG_IN     |                                       |

| ТхСКІ        |                                       |

| TxGVAL       |                                       |

| TIMER1/3/5   | N XN+1XN+2XN+3X N+4 XN+5XN+6XN+7X N+8 |

|              |                                       |

## FIGURE 19-6: TIMER1/3/5 GATE SINGLE-PULSE MODE

| Mada              | MODE  | <4:0> | Output                            | On creation                                               |                            | Timer Control |                                          |

|-------------------|-------|-------|-----------------------------------|-----------------------------------------------------------|----------------------------|---------------|------------------------------------------|

| Mode              | <4:3> | <2:0> | Operation                         | Operation                                                 | Start                      | Reset         | Stop                                     |

|                   |       | 000   |                                   | Software gate (Figure 20-4)                               | <b>ON =</b> 1              | _             | ON = 0                                   |

|                   |       | 001   | Period<br>Pulse                   | Hardware gate, active-high<br>(Figure 20-5)               | ON = 1 and<br>TMRx_ers = 1 | _             | ON = 0 or<br>TMRx_ers = 0                |

|                   |       | 010   | Fuise                             | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0 | _             | ON = 0 or<br>TMRx_ers = 1                |

| Free              | 0.0   | 011   |                                   | Rising or falling edge Reset                              |                            | TMRx_ers      |                                          |

| Running<br>Period | 00    | 100   | Period                            | Rising edge Reset (Figure 20-6)                           |                            | TMRx_ers ↑    | <b>ON =</b> 0                            |

|                   |       | 101   | Pulse                             | Falling edge Reset                                        |                            | TMRx_ers ↓    |                                          |

|                   |       | 110   | with<br>Hardware                  | Low level Reset                                           | ON = 1                     | TMRx_ers = 0  | ON = 0 or<br>TMRx_ers = 0                |

|                   |       | 111   | Reset                             | High level Reset (Figure 20-7)                            |                            | TMRx_ers = 1  | ON = 0 or<br>TMRx_ers = 1                |

|                   |       | 000   | One-shot                          | Software start (Figure 20-8)                              | <b>ON =</b> 1              | _             |                                          |

|                   |       | 001   | Edge                              | Rising edge start (Figure 20-9)                           | ON = 1 and<br>TMRx_ers ↑   | _             |                                          |

|                   |       | 010   | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _             |                                          |

|                   |       | 011   | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _             | ON = 0<br>or<br>Next clock               |

| One-shot          | 01    | 100   | Edge                              | Rising edge start and<br>Rising edge Reset (Figure 20-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑    | after<br>TMRx = PRx<br>( <b>Note 2</b> ) |

|                   |       | 101   | triggered<br>start                | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓    |                                          |

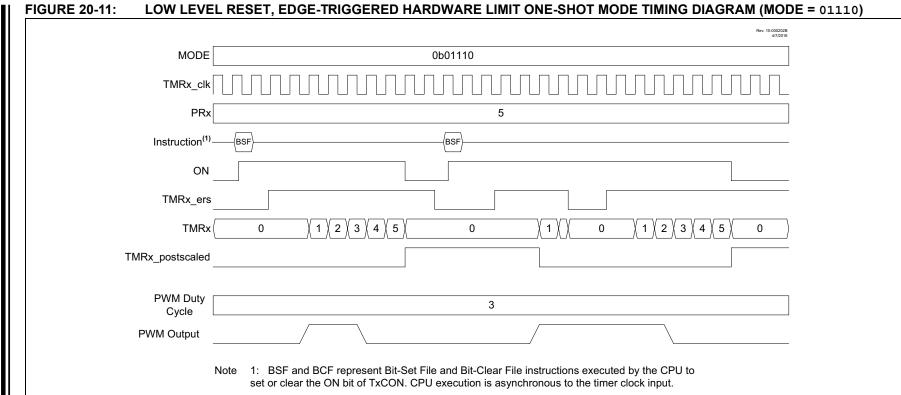

|                   |       | 110   | and<br>hardware<br>Reset          | Rising edge start and<br>Low level Reset (Figure 20-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0  |                                          |

|                   |       | 111   | (Note 1)                          | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1  |                                          |

|                   |       | 000   |                                   | Rese                                                      | rved                       |               |                                          |

|                   |       | 001   | Edge                              | Rising edge start<br>(Figure 20-12)                       | ON = 1 and<br>TMRx_ers ↑   | —             | ON = 0<br>or                             |

| Mono-stable       |       | 010   | triggered<br>start                | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _             | Next clock<br>after                      |

|                   |       | 011   | (Note 1)                          | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _             | TMRx = PRx<br>( <b>Note 3</b> )          |

| Reserved          | 10    | 100   |                                   | Rese                                                      | rved                       |               | •                                        |

| Reserved          |       | 101   |                                   | Rese                                                      | rved                       |               |                                          |

|                   |       | 110   | Level<br>triggered                | High level start and<br>Low level Reset (Figure 20-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0  | ON = 0 or                                |

| One-shot          |       | 111   | start<br>and<br>hardware<br>Reset | Low level start &<br>High level Reset                     | ON = 1 and<br>TMRx_ers = 0 | TMRx_ers = 1  | Held in Reset<br>(Note 2)                |

| Reserved          | 11    | xxx   |                                   | Rese                                                      | rved                       |               |                                          |

#### TABLE 20-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

## 23.0 ZERO-CROSS DETECTION (ZCD) MODULE

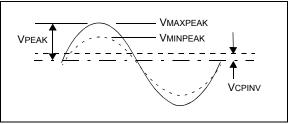

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 23-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- Low EMI cycle switching

## 23.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 23-1 and Figure 23-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

## EQUATION 23-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 23-1: EXTERNAL VOLTAGE

#### EQUATION 23-2: R-C CALCULATIONS

- VPEAK = External voltage source peak voltage

- f = External voltage source frequency

- C = Series capacitor

- R = Series resistor

- $V_{\rm C}$  = Peak capacitor voltage

- $\Phi$  = Capacitor induced zero crossing phase advance in radians

- $T_\Phi\,$  = Time ZC event occurs before actual zero crossing

$$Z = \frac{VPEAK}{3 \times 10^{-4}}$$

$$XC = \frac{1}{2\pi fC}$$

$$R = \sqrt{Z^2 - Xc^2}$$

$$VC = XC(3 \times 10^{-4})$$

$$\Phi = Tan^{-1}\left(\frac{XC}{R}\right)$$

$$T\Phi = \frac{\Phi}{2\pi f}$$

#### EXAMPLE 23-1: R-C CALCULATIONS

VRMS = 120

VPEAK = VRMS \*

$$\sqrt{2}$$

= 169.7

f = 60 Hz

C = 0.1 µF

$$Z = \frac{VPEAK}{3 \times 10^{-4}} = \frac{169.7}{3 \times 10^{-4}} = 565.7 k\Omega$$

XC =  $\frac{1}{2\pi fC} = \frac{1}{(2\pi \times 60 \times 1 \times 10^{-7})} = 26.53 k\Omega$

R =  $\sqrt{(Z^2 \times Xc^2)} = 565.1 k\Omega$  (computed)

R = 560k $\Omega$  (used)

ZR =  $\sqrt{R^2 + Xc^2} = 560.6 k\Omega$  (using actual resistor)

IPEAK =  $\frac{VPEAK}{ZR} = 302.7 \times 10^{-6}$

VC = XC × Ipeak = 8.0V

$\Phi = Tan^{-1}(\frac{XC}{R}) = 0.047$  radians

T $\Phi = \frac{\Phi}{2\pi f} = 125.6 \mu s$

#### 23.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 23-3.

## EQUATION 23-3: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to VSS. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 23-4.

## EQUATION 23-4: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - V_{CPINV})}{V_{CPINV}}$$

When External Signal is relative to VDD:

$$R_{PULLDOWN} = \frac{R_{SERIES}(VCPINV)}{(VDD - VCPINV)}$$

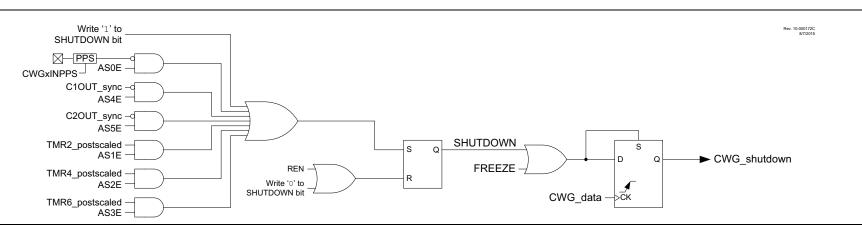

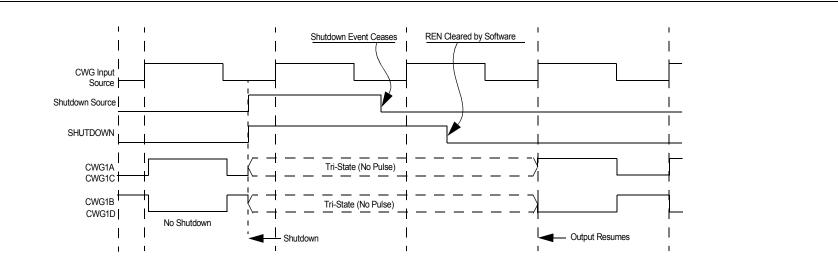

### FIGURE 24-15: SHUTDOWN FUNCTIONALITY, AUTO-RESTART DISABLED (REN = 0, LSAC = 01, LSBD = 01)

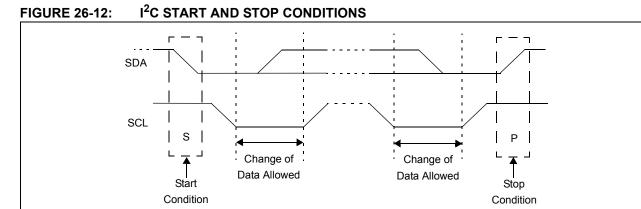

#### 26.8.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 26-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the I<sup>2</sup>C Specification that states no bus collision can occur on a Start.

#### 26.8.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

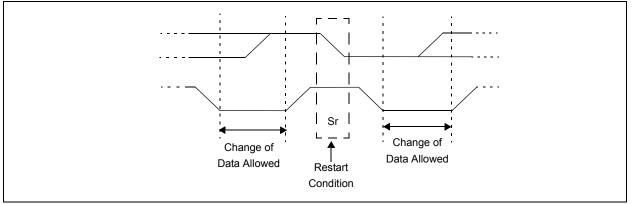

## 26.8.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 26-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with R/W clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with R/W clear, or high address match fails.

#### 26.8.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

© 2015-2017 Microchip Technology Inc.

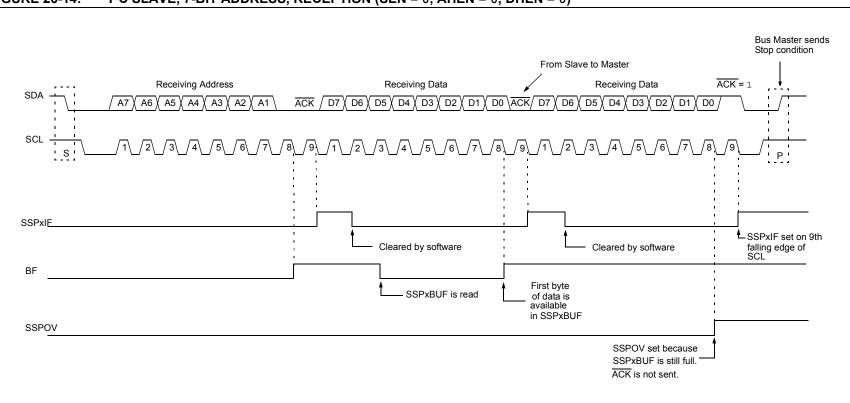

## FIGURE 26-14: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0)

PIC18(L)F26/45/46K40

#### 26.10.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |

|-------|--------------------------------------------|

|       | writing to the lower five bits of SSPxCON2 |

|       | is disabled until the Start condition is   |

|       | complete.                                  |

#### 26.10.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

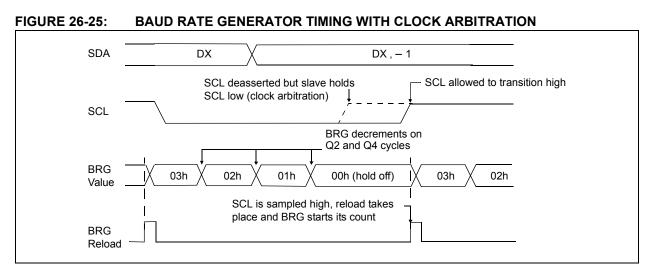

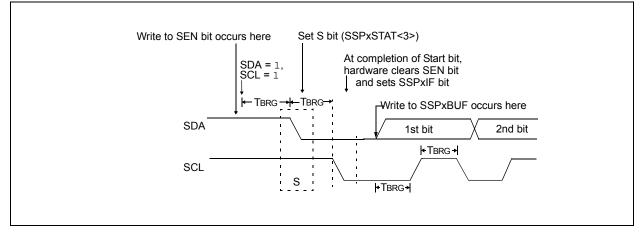

To initiate a Start condition (Figure 26-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is

FIGURE 26-26: FIRST START BIT TIMING

the Start condition and causes the S bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

© 2015-2017 Microchip Technology Inc.

|        |                  |            |                             | -                | SYNC       | <b>=</b> 0, BRGH            | <b>i =</b> 1, BRO | <b>G16 =</b> 0 |                             |                  |            |                             |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |                |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                | _          | —                           | _                |            | _                           | _                 | _              | _                           | 300              | 0.16       | 207                         |

| 1200   | —                | —          | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00           | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00           | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00           | 23                          | —                | _          | _                           |

| 10417  | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53           | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00           | 11                          | _                | _          | _                           |

| 57.6k  | 55556            | -3.55      | 8                           | —                | _          | _                           | 57.60k            | 0.00           | 3                           | —                | _          | _                           |

| 115.2k | —                |            | —                           | —                |            | —                           | 115.2k            | 0.00           | 1                           | _                | —          | —                           |

## TABLE 27-5: SAMPLE BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   |            |                             |                | SYNC              | <b>C =</b> 0, <b>BRG</b>    | I = 0, BRO     | <b>616 =</b> 1    |                             |                |                    |                             |  |

|--------|-------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |            |                             | Fosc           | Fosc = 20.000 MHz |                             |                | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0             | 0.00       | 6666                        | 300.0          | -0.01             | 4166                        | 300.0          | 0.00              | 3839                        | 300.0          | 0.00               | 2303                        |  |

| 1200   | 1200              | -0.02      | 3332                        | 1200           | -0.03             | 1041                        | 1200           | 0.00              | 959                         | 1200           | 0.00               | 575                         |  |

| 2400   | 2401              | -0.04      | 832                         | 2399           | -0.03             | 520                         | 2400           | 0.00              | 479                         | 2400           | 0.00               | 287                         |  |

| 9600   | 9615              | 0.16       | 207                         | 9615           | 0.16              | 129                         | 9600           | 0.00              | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417             | 0.00       | 191                         | 10417          | 0.00              | 119                         | 10378          | -0.37             | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k            | 0.16       | 103                         | 19.23k         | 0.16              | 64                          | 19.20k         | 0.00              | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k            | -0.79      | 34                          | 56.818         | -1.36             | 21                          | 57.60k         | 0.00              | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.6k            | 2.12       | 16                          | 113.636        | -1.36             | 10                          | 115.2k         | 0.00              | 9                           | 115.2k         | 0.00               | 5                           |  |

|        |                  |            |                             |                                        | SYNC | <b>C =</b> 0, <b>BRG</b> | l = 0, BRG        | <b>616 =</b> 1              |                |                  |                             |     |

|--------|------------------|------------|-----------------------------|----------------------------------------|------|--------------------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|-----|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz                       |      |                          | Fosc = 3.6864 MHz |                             |                | Fosc = 1.000 MHz |                             |     |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual % SPBRG<br>Rate Error (decimal) |      | Actual<br>Rate           | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |     |

| 300    | 299.9            | -0.02      | 1666                        | 300.1                                  | 0.04 | 832                      | 300.0             | 0.00                        | 767            | 300.5            | 0.16                        | 207 |

| 1200   | 1199             | -0.08      | 416                         | 1202                                   | 0.16 | 207                      | 1200              | 0.00                        | 191            | 1202             | 0.16                        | 51  |

| 2400   | 2404             | 0.16       | 207                         | 2404                                   | 0.16 | 103                      | 2400              | 0.00                        | 95             | 2404             | 0.16                        | 25  |

| 9600   | 9615             | 0.16       | 51                          | 9615                                   | 0.16 | 25                       | 9600              | 0.00                        | 23             | _                | _                           | _   |

| 10417  | 10417            | 0.00       | 47                          | 10417                                  | 0.00 | 23                       | 10473             | 0.53                        | 21             | 10417            | 0.00                        | 5   |

| 19.2k  | 19.23k           | 0.16       | 25                          | 19.23k                                 | 0.16 | 12                       | 19.20k            | 0.00                        | 11             | _                | _                           | _   |

| 57.6k  | 55556            | -3.55      | 8                           | —                                      | —    | _                        | 57.60k            | 0.00                        | 3              | —                | _                           | _   |

| 115.2k | —                | _          | _                           | —                                      | _    | _                        | 115.2k            | 0.00                        | 1              | —                | _                           | _   |

#### REGISTER 31-8: ADPCH: ADC POSITIVE CHANNEL SELECTION REGISTER

| U-0              | U-0                  | R/W-0/0                    | R/W-0/0                   | R/W-0/0        | R/W-0/0                  | R/W-0/0            | R/W-0/0 |

|------------------|----------------------|----------------------------|---------------------------|----------------|--------------------------|--------------------|---------|

| —                | _                    |                            |                           | ADP            | CH<5:0>                  |                    |         |

| oit 7            |                      |                            |                           |                |                          |                    | bit     |

|                  |                      |                            |                           |                |                          |                    |         |

| Legend:          |                      |                            |                           |                |                          |                    |         |

| R = Readable I   | bit                  | W = Writable bit           |                           | U = Unimpler   | mented bit, read as      | ; 'O'              |         |

| u = Bit is uncha | anged                | x = Bit is unknow          | n                         | -n/n = Value a | at POR and BOR/\         | /alue at all other | Resets  |

| '1' = Bit is set | -                    | '0' = Bit is cleared       | t                         |                |                          |                    |         |

|                  |                      |                            |                           |                |                          |                    |         |

| bit 7-6          | Unimplemen           | ted: Read as '0'           |                           |                |                          |                    |         |

| bit 5-0          | ADPCH<5:0>           | : ADC Positive Inpu        | t Channel Se              | lection bits   |                          |                    |         |

|                  | 111111 =             | Fixed Voltage Refe         | rence (FVR) <sup>(2</sup> | <b>2)</b> 0101 | 111 = ANC7               |                    |         |

|                  | 1111110 =            | DAC1 output <sup>(1)</sup> |                           |                | 110 = ANC6               |                    |         |

|                  |                      | Temperature Indica         | tor <sup>(3)</sup>        | 0101           | L01 = ANC5               |                    |         |

|                  | 111100 =             | AVss (Analog Grou          | ind)                      | 0101           | L00 <b>= ANC4</b>        |                    |         |

|                  | 111011 =             | Reserved. No chan          | nel connecte              | d. 0100        | 11 = ANC3                |                    |         |

|                  | •                    |                            |                           |                | 10 = ANC2                |                    |         |

|                  | •                    |                            |                           |                | 001 = ANC1               |                    |         |

|                  | •                    |                            |                           |                | 000 <b>= ANC0</b>        |                    |         |

|                  | 100010 =             |                            |                           |                | 111 = ANB7               |                    |         |

|                  | 100001 =             |                            |                           |                | L10 = ANB6               |                    |         |

|                  | 100000 =             |                            |                           |                | L01 = ANB5               |                    |         |

|                  | 011111 =             | $AND^{(4)}$                |                           |                | L00 = ANB4               |                    |         |

|                  | 011110 =<br>011101 = |                            |                           |                | 11 = ANB3                |                    |         |

|                  | 011101 =             |                            |                           |                | 10 = ANB2                |                    |         |

|                  | 011100 =             |                            |                           |                | 001 = ANB1<br>000 = ANB0 |                    |         |

|                  | 011011 =             |                            |                           |                | 111 = ANA7               |                    |         |

|                  | 011001 =             |                            |                           |                | 111 = ANA7<br>110 = ANA6 |                    |         |

|                  | 011000 =             |                            |                           |                | L01 = ANA5               |                    |         |

|                  | 011000 -             |                            |                           |                | L01 = ANA3               |                    |         |

|                  |                      |                            |                           |                | 111 = ANA3               |                    |         |

|                  |                      |                            |                           |                | 10 = ANA2                |                    |         |

|                  |                      |                            |                           |                | 001 = ANA1               |                    |         |

|                  |                      |                            |                           |                | 000 = ANA0               |                    |         |

Note 1: See Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information.

2: See Section 28.0 "Fixed Voltage Reference (FVR)" for more information.

3: See Section 29.0 "Temperature Indicator Module" for more information.

4: PIC18F45/46K40 only.

# PIC18(L)F26/45/46K40

| BZ                                                                                          |                 | Branch if                                                                                 | Branch if Zero                                                                                                                                                                                                                                                     |                 |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:                                                                                     |                 | BZ n                                                                                      | BZ n                                                                                                                                                                                                                                                               |                 |  |  |  |  |

| Operands:                                                                                   |                 | -128 ≤ n ≤ 1                                                                              | 27                                                                                                                                                                                                                                                                 |                 |  |  |  |  |

| Operation:                                                                                  |                 |                                                                                           | if ZERO bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                               |                 |  |  |  |  |

| Statu                                                                                       | is Affected:    | None                                                                                      |                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Enco                                                                                        | oding:          | 1110                                                                                      | 1110 0000 nnnn nnnn                                                                                                                                                                                                                                                |                 |  |  |  |  |

| Description:                                                                                |                 | will branch.<br>The 2's con<br>added to the<br>have incren<br>instruction,<br>PC + 2 + 2r | If the ZERO bit is '1', then the program will branch.<br>The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a 2-cvcle instruction. |                 |  |  |  |  |

| Word                                                                                        | ls:             | 1                                                                                         |                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Cycle                                                                                       | es:             | 1(2)                                                                                      |                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                               |                 |                                                                                           |                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

|                                                                                             | Q1              | Q2                                                                                        | Q3                                                                                                                                                                                                                                                                 | Q4              |  |  |  |  |

|                                                                                             | Decode          | Read literal<br>'n'                                                                       | Process<br>Data                                                                                                                                                                                                                                                    | Write to PC     |  |  |  |  |

|                                                                                             | No<br>operation | No<br>operation                                                                           | No<br>operation                                                                                                                                                                                                                                                    | No<br>operation |  |  |  |  |

| lf No                                                                                       | o Jump:         |                                                                                           |                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

|                                                                                             | Q1              | Q2                                                                                        | Q3                                                                                                                                                                                                                                                                 | Q4              |  |  |  |  |

|                                                                                             | Decode          | Read literal<br>'n'                                                                       | Process<br>Data                                                                                                                                                                                                                                                    | No<br>operation |  |  |  |  |

| Example:<br>Before Instruction<br>PC<br>After Instruction<br>If ZERO<br>PC<br>If ZERO<br>PC |                 | = ado<br>= 1;<br>= ado<br>= 0;                                                            | BZ Jump<br>dress (HERE)<br>dress (Jump)<br>dress (HERE                                                                                                                                                                                                             | )               |  |  |  |  |

| Syntax:                                             | CALL k {,                                                                                                                                                   | CALL k {,s}                                                                                                                          |                                                                                                            |                                                                                              |                                                                                             |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

| Operands:                                           | 0 ≤ k ≤ 104<br>s ∈ [0,1]                                                                                                                                    | $0 \leq k \leq 1048575$                                                                                                              |                                                                                                            |                                                                                              |                                                                                             |  |  |  |

| Operation:                                          | $k \rightarrow PC < 20$<br>if s = 1<br>(W) $\rightarrow$ WS<br>(Status) $\rightarrow$                                                                       | $(PC) + 4 \rightarrow TOS, k \rightarrow PC<20:1>,$                                                                                  |                                                                                                            |                                                                                              |                                                                                             |  |  |  |

| Status Affected:                                    | None                                                                                                                                                        |                                                                                                                                      |                                                                                                            |                                                                                              |                                                                                             |  |  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                | 110s<br>k <sub>19</sub> kkk                                                                                                          | k <sub>7</sub> kk<br>kkkł                                                                                  |                                                                                              | kkkk <sub>0</sub><br>kkkk <sub>8</sub>                                                      |  |  |  |

| Description:                                        | memory ra<br>(PC + 4) is                                                                                                                                    | pushed of                                                                                                                            | t, returr<br>onto the                                                                                      | n ado<br>e ret                                                                               | dress<br>urn                                                                                |  |  |  |

| שפטווינויו.                                         | memory ra                                                                                                                                                   | nge. Firs<br>pushed of<br>= 1, the '<br>re also pu<br>shadow r<br>and BSR<br>curs (defa<br>e 'k' is loa                              | t, return<br>onto the<br>W, Stat<br>ushed in<br>register<br>S. If 's'<br>oult). Th<br>ided int             | n ado<br>e retitus a<br>nto t<br>rs, W<br>= 0,<br>nen, f<br>to PC                            | dress<br>urn<br>nd BSR<br>heir<br>/S,<br>no<br>the                                          |  |  |  |

| Words:                                              | memory ra<br>(PC + 4) is<br>stack. If 's'<br>registers a<br>respective<br>STATUSS<br>update occ<br>20-bit value                                             | nge. Firs<br>pushed of<br>= 1, the '<br>re also pu<br>shadow r<br>and BSR<br>curs (defa<br>e 'k' is loa                              | t, return<br>onto the<br>W, Stat<br>ushed in<br>register<br>S. If 's'<br>oult). Th<br>ided int             | n ado<br>e retitus a<br>nto t<br>rs, W<br>= 0,<br>nen, f<br>to PC                            | dress<br>urn<br>nd BSR<br>heir<br>/S,<br>no<br>the                                          |  |  |  |

|                                                     | memory ra<br>(PC + 4) is<br>stack. If 's'<br>registers a<br>respective<br>STATUSS<br>update occ<br>20-bit value<br>CALL is a                                | nge. Firs<br>pushed of<br>= 1, the '<br>re also pu<br>shadow r<br>and BSR<br>curs (defa<br>e 'k' is loa                              | t, return<br>onto the<br>W, Stat<br>ushed in<br>register<br>S. If 's'<br>oult). Th<br>ided int             | n ado<br>e retitus a<br>nto t<br>rs, W<br>= 0,<br>nen, f<br>to PC                            | dress<br>urn<br>nd BSR<br>heir<br>/S,<br>no<br>the                                          |  |  |  |