Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.5 Register Definitions: Reference Clock

Long bit name prefixes for the Reference Clock peripherals are shown in Table 5-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

## TABLE 5-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CLKR       | CLKR            |

## REGISTER 5-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|---------|-----|-----|---------|---------|---------|----------|---------|

| EN      | —   | —   | DC<1:0> |         |         | DIV<2:0> |         |

| bit 7   |     |     |         |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Reference Clock Module Enable bit                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Reference clock module enabled</li><li>0 = Reference clock module is disabled</li></ul>                                                                                                                                                                                                          |

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| bit 4-3 | DC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Clock outputs duty cycle of 75%</li> <li>10 = Clock outputs duty cycle of 50%</li> <li>01 = Clock outputs duty cycle of 25%</li> <li>00 = Clock outputs duty cycle of 0%</li> </ul>                                                                                                            |

| bit 2-0 | DIV<2:0>: Reference Clock Divider bits                                                                                                                                                                                                                                                                       |

|         | 111 = Base clock value divided by 128<br>110 = Base clock value divided by 64<br>101 = Base clock value divided by 32<br>100 = Base clock value divided by 16<br>011 = Base clock value divided by 8<br>010 = Base clock value divided by 4<br>001 = Base clock value divided by 2<br>000 = Base clock value |

**Note 1:** Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

## 6.4 Register Definitions: Voltage Regulator Control

## **REGISTER 6-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0              | U-0   | U-0               | U-0  | U-0                                              | U-0              | R/W-0/0 | R/W-1/1     |

|------------------|-------|-------------------|------|--------------------------------------------------|------------------|---------|-------------|

| _                | —     | —                 | —    | —                                                | _                | VREGPM  | Reserved    |

| bit 7            |       |                   |      |                                                  |                  |         | bit 0       |

|                  |       |                   |      |                                                  |                  |         |             |

| Legend:          |       |                   |      |                                                  |                  |         |             |

| R = Readable b   | oit   | W = Writable      | bit  | U = Unimpler                                     | mented bit, read | as '0'  |             |

| u = Bit is uncha | anged | x = Bit is unkr   | nown | -n/n = Value at POR and BOR/Value at all other F |                  |         | ther Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                                                  |                  |         |             |

bit 7-2 Unimplemented: Read as '0'

VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup>

- Draws lowest current in Sleep, slower wake-up

- 0 =Normal Power mode enabled in Sleep<sup>(2)</sup>

- Draws higher current in Sleep, faster wake-up

bit 0 **Reserved:** Read as '1'. Maintain this bit set.

Note 1: PIC18F2x/4xK40 only.

bit 1

2: See Section 37.0 "Electrical Specifications".

| Name    | Bit 7  | Bit 6       | Bit 5     | Bit 4          | Bit 3   | Bit 2 | Bit 1    | Bit 0   | Register<br>on Page |  |

|---------|--------|-------------|-----------|----------------|---------|-------|----------|---------|---------------------|--|

| PCON0   | STKOVF | STKUNF      | WDTWV     | RWDT           | RMCLR   | RI    | POR      | BOR     | 76                  |  |

| STATUS  | _      | _           | _         | TO             | PD      | Z     | DC       | С       | 118                 |  |

| WDTCON0 | _      | _           |           | WDTPS<4:0> SEN |         |       |          |         |                     |  |

| WDTCON1 | _      | V           | /DTCS<2:0 | >              | _       | WI    | NDOW<2:0 | >       | 86                  |  |

| WDTPSL  |        |             |           | PSC            | NT<7:0> |       |          |         | 87                  |  |

| WDTPSH  |        | PSCNT<15:8> |           |                |         |       |          |         |                     |  |

| WDTTMR  |        | W           | DTTMR<4:  | 0>             |         | STATE | PSCNT    | <17:16> | 88                  |  |

## TABLE 9-3: SUMMARY OF REGISTERS ASSOCIATED WITH WINDOWED WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Windowed Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WINDOWED WATCHDOG TIMER

| Name Bits Bit -/7 Bit -/6 Bit 13/5 | Bit 12/4 Bit 11/3 | Bit 10/2 Bit 9/1 |  | egister<br>n Page |

|------------------------------------|-------------------|------------------|--|-------------------|

|------------------------------------|-------------------|------------------|--|-------------------|

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Windowed Watchdog Timer.

## 10.1.1 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 10.2.3.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

## 10.1.2 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, or as a 35-word by 21-bit RAM with a 6-bit Stack Pointer in ICD mode. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special File registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits in the PCON0 register indicate if the stack is full or has overflowed or has underflowed.

## 10.1.2.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 10-1). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the Global Interrupt Enable (GIE) bits while accessing the stack to prevent inadvertent stack corruption.

| Address | Name                   | Bit 7   | Bit 6   | Bit 5     | Bit 4   | Bit 3  | Bit 2       | Bit 1  | Bit 0    | <u>Value on</u><br>POR, BOR |

|---------|------------------------|---------|---------|-----------|---------|--------|-------------|--------|----------|-----------------------------|

| EFFh    | RD0PPS <sup>(2)</sup>  | _       | —       | —         |         |        | RD0PPS<4:0> |        |          | 00000                       |

| EFEh    | RC7PPS                 | _       | _       | _         |         |        | RC7PPS<4:0> |        |          | 00000                       |

| EFDh    | RC6PPS                 | _       | _       | _         |         |        | RC6PPS<4:0> |        |          | 00000                       |

| EFCh    | RC5PPS                 | _       | _       | _         |         |        | RC5PPS<4:0> |        |          | 00000                       |

| EFBh    | RC4PPS                 | _       | _       | _         |         |        | RC4PPS<4:0> |        |          | 00000                       |

| EFAh    | RC3PPS                 | _       | _       | _         |         |        | RC3PPS<4:0> |        |          | 00000                       |

| EF9h    | RC2PPS                 | _       | _       | _         |         |        | RC2PPS<4:0> |        |          | 00000                       |

| EF8h    | RC1PPS                 | _       | —       | —         |         |        | RC1PPS<4:0> |        |          | 00000                       |

| EF7h    | RC0PPS                 | _       | —       | _         |         |        | RC0PPS<4:0> | •      |          | 00000                       |

| EF6h    | RB7PPS                 | _       | —       | —         |         |        | RB7PPS<4:0> |        |          | 00000                       |

| EF5h    | RB6PPS                 | _       | —       | _         |         |        | RB6PPS<4:0> |        |          | 00000                       |

| EF4h    | RB5PPS                 | _       | —       | _         |         |        | RB5PPS<4:0> |        |          | 00000                       |

| EF3h    | RB4PPS                 | _       | —       | _         |         |        | RB4PPS<4:0> |        |          | 00000                       |

| EF2h    | RB3PPS                 | _       | —       | _         |         |        | RB3PPS<4:0> |        |          | 00000                       |

| EF1h    | RB2PPS                 | _       | —       | _         |         |        | RB2PPS<4:0> |        |          | 00000                       |

| EF0h    | RB1PPS                 | _       | —       | —         |         |        | RB1PPS<4:0> |        |          | 00000                       |

| EEFh    | RB0PPS                 | _       | —       | _         |         |        | RB0PPS<4:0> |        |          | 00000                       |

| EEEh    | RA7PPS                 | _       | —       | _         |         |        | RA7PPS<4:0> |        |          | 00000                       |

| EEDh    | RA6PPS                 | _       | —       | _         |         |        | RA6PPS<4:0> |        |          | 00000                       |

| EECh    | RA5PPS                 | _       | —       | —         |         |        | RA5PPS<4:0> |        |          | 00000                       |

| EEBh    | RA4PPS                 | _       | —       | _         |         |        | RA4PPS<4:0> |        |          | 00000                       |

| EEAh    | RA3PPS                 | _       | —       | —         |         |        | RA3PPS<4:0> |        |          | 00000                       |

| EE9h    | RA2PPS                 | _       | —       | —         |         |        | RA2PPS<4:0> |        |          | 00000                       |

| EE8h    | RA1PPS                 | _       | —       | —         |         |        | RA1PPS<4:0> |        |          | 00000                       |

| EE7h    | RA0PPS                 | _       | —       | _         |         |        | RA0PPS<4:0> |        |          | 00000                       |

| EE6h    | PMD5                   | _       | —       | —         | —       | —      | —           | —      | DSMMD    | 0                           |

| EE5h    | PMD4                   | UART2MD | UART1MD | MSSP2MD   | MSSP1MD | —      | —           | —      | CWG1MD   | 00000                       |

| EE4h    | PMD3                   | _       | —       | —         | —       | PWM4MD | PWM3MD      | CCP2MD | CCP1MD   | 0000                        |

| EE3h    | PMD2                   | _       | DACMD   | ADCMD     | _       | —      | CMP2MD      | CMP1MD | ZCDMD    | -00000                      |

| EE2h    | PMD1                   | _       | TMR6MD  | TMR5MD    | TMR4MD  | TMR3MD | TMR2MD      | TMR1MD | TMR0MD   | -0000000                    |

| EE1h    | PMD0                   | SYSCMD  | FVRMD   | HLVDMD    | CRCMD   | SCANMD | NVMMD       | CLKRMD | IOCMD    | 00x00000                    |

| EE0h    | BORCON                 | SBOREN  | —       | —         | —       | —      | —           | —      | BORRDY   | 1q                          |

| EDFh    | VREGCON <sup>(1)</sup> | -       | —       | _         | _       | —      | —           | VREGPM | Reserved | 01                          |

| EDEh    | OSCFRQ                 | _       | —       | —         | —       |        | HFFR        | Q<3:0> |          | 1111                        |

| EDDh    | OSCTUNE                | _       | —       |           |         | HFTU   | JN<5:0>     |        |          | 100000                      |

| EDCh    | OSCEN                  | EXTOEN  | HFOEN   | MFOEN     | LFOEN   | SOSCEN | ADOEN       |        | —        | 000000                      |

| EDBh    | OSCSTAT                | EXTOR   | HFOR    | MFOR      | LFOR    | SOR    | ADOR        |        | PLLR     | dddddd-d                    |

| EDAh    | OSCCON3                | CSWHOLD | SOSCPWR | —         | ORDY    | NOSCR  | _           | —      | _        | 00-00                       |

| ED9h    | OSCCON2                | _       |         | COSC<2:0> | 1       |        | CDIV        | /<3:0> |          | -ddddddd                    |

## TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40 devices.

## 11.1.5 ERASING PROGRAM FLASH MEMORY

The minimum erase block is 32 or 64 words (refer to Table 11-3). Only through the use of an external programmer, or through ICSP™ control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

For example, when initiating an erase sequence from a microcontroller with erase row size of 32 words, a block of 32 words (64 bytes) of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The NVMCON1 register commands the erase operation. The NVMREG<1:0> bits must be set to point to the Program Flash Memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The NVM unlock sequence described in **Section 11.1.4 "NVM Unlock Sequence"** should be used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

## 11.1.5.1 Program Flash Memory Erase Sequence

The sequence of events for erasing a block of internal program memory is:

- 1. NVMREG bits of the NVMCON1 register point to PFM

- 2. Set the FREE and WREN bits of the NVMCON1 register

- 3. Perform the unlock sequence as described in Section 11.1.4 "NVM Unlock Sequence"

If the PFM address is write-protected, the WR bit will be cleared and the erase operation will not take place, WRERR is signaled in this scenario.

The operation erases the memory row indicated by masking the LSBs of the current TBLPTR.

While erasing PFM, CPU operation is suspended and it resumes when the operation is complete. Upon completion the WR bit is cleared in hardware, the NVMIF is set and an interrupt will occur if the NVMIE bit is also set.

Write latch data is not affected by erase operations and WREN will remain unchanged.

Note 1: If a write or erase operation is terminated by an unexpected event, WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

- 2: WRERR is set if WR is written to '1' while TBLPTR points to a write-protected address.

- **3:** WRERR is set if WR is written to '1' while TBLPTR points to an invalid address location (Table 10-2 and Table 11-1).

#### EXAMPLE 11-3: ERASING A PROGRAM FLASH MEMORY BLOCK

; This sample row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in variables TBLPTR register

; 2. ADDRH and ADDRL are located in common RAM (locations  $0 \mathrm{x} 70$  -  $0 \mathrm{x} 7 \mathrm{F})$

|            | MOVLW | CODE_ADDR_UPPER  | ; load TBLPTR with the base     |

|------------|-------|------------------|---------------------------------|

|            | MOVWF | TBLPTRU          | ; address of the memory block   |

|            | MOVLW | CODE_ADDR_HIGH   |                                 |

|            | MOVWF | TBLPTRH          |                                 |

|            | MOVLW | CODE_ADDR_LOW    |                                 |

|            | MOVWF | TBLPTRL          |                                 |

| ERASE_BLOC | CK    |                  |                                 |

|            | BCF   | NVMCON1, NVMREG0 | ; point to Program Flash Memory |

|            | BSF   | NVMCON1, NVMREG1 | ; access Program Flash Memory   |

|            | BSF   | NVMCON1, WREN    | ; enable write to memory        |

|            | BSF   | NVMCON1, FREE    | ; enable block Erase operation  |

|            | BCF   | INTCON, GIE      | ; disable interrupts            |

| Required   | MOVLW | 55h              |                                 |

| Sequence   | MOVWF | NVMCON2          | ; write 55h                     |

|            | MOVLW | AAh              |                                 |

|            | MOVWF | NVMCON2          | ; write AAh                     |

|            | BSF   | NVMCON1, WR      | ; start erase (CPU stalls)      |

|            | BSF   | INTCON, GIE      | ; re-enable interrupts          |

|            |       |                  |                                 |

|            |       |                  |                                 |

## **REGISTER 11-5: NVMDAT: DATA EEPROM MEMORY DATA**

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|------------------|---------|-------------------|---------|------------------|------------------|----------|---------|

|                  |         |                   | NVMD    | AT<7:0>          |                  |          |         |

| bit 7            |         |                   |         |                  |                  |          | bit 0   |

|                  |         |                   |         |                  |                  |          |         |

| Legend:          |         |                   |         |                  |                  |          |         |

| R = Readable     | bit     | W = Writable I    | oit     | U = Unimpler     | nented bit, read | d as '0' |         |

| x = Bit is unkne | own     | '0' = Bit is clea | ared    | '1' = Bit is set |                  |          |         |

| -n = Value at F  | POR     |                   |         |                  |                  |          |         |

bit 7-0 **NVMDAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

#### TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

| Name                   | Bit 7                 | Bit 6       | Bit 5     | Bit 4        | Bit 3         | Bit 2        | Bit 1       | Bit 0   | Register<br>on Page |  |  |  |

|------------------------|-----------------------|-------------|-----------|--------------|---------------|--------------|-------------|---------|---------------------|--|--|--|

| NVMCON1                | NVMRE                 | G<1:0>      | _         | FREE         | WRERR         | WREN         | WR          | RD      | 145                 |  |  |  |

| NVMCON2                | Unlock Pattern        |             |           |              |               |              |             |         |                     |  |  |  |

| NVMADRL                |                       | NVMADR<7:0> |           |              |               |              |             |         |                     |  |  |  |

| NVMADRH <sup>(1)</sup> | — — — — — NVMADR<9:8> |             |           |              |               |              |             |         |                     |  |  |  |

| NVMDAT                 | NVMDAT<7:0>           |             |           |              |               |              |             |         |                     |  |  |  |

| TBLPTRU                | _                     | _           |           | Program N    | lemory Table  | Pointer (TBL | PTR<21:16>) |         | 127*                |  |  |  |

| TBLPTRH                |                       |             | Program N | lemory Table | e Pointer (TB | LPTR<15:8>)  |             |         | 127*                |  |  |  |

| TBLPTRL                |                       |             | Program I | Memory Table | e Pointer (TB | LPTR<7:0>)   |             |         | 127*                |  |  |  |

| TABLAT                 |                       |             |           | TA           | BLAT          |              |             |         | 126*                |  |  |  |

| INTCON                 | GIE/GIEH              | PEIE/GIEL   | IPEN      | —            | _             | INT2EDG      | INT1EDG     | INT0EDG | 170                 |  |  |  |

| PIE7                   | SCANIE                | CRCIE       | NVMIE     | —            | —             | —            | —           | CWG1IE  | 186                 |  |  |  |

| PIR7                   | SCANIF                | CRCIF       | NVMIF     | _            | _             | _            | _           | CWG1IF  | 178                 |  |  |  |

| IPR7                   | SCANIP                | CRCIP       | NVMIP     | —            | —             | _            | —           | CWG1IP  | 194                 |  |  |  |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

Note 1: The NVMADRH register is not implemented on PIC18(L)F26/45/46K40.

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|--|--|

| ACC<7:0>         |         |                   |         |                |                  |                  |             |  |  |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |  |  |

|                  |         |                   |         |                |                  |                  |             |  |  |

| Legend:          |         |                   |         |                |                  |                  |             |  |  |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |  |  |

| u = Bit is unch  | anged   | x = Bit is unkn   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |  |  |

bit 7-0

**ACC<7:0>:** CRC Accumulator Register bits Writing to this register writes to the CRC accumulator register through the CRC write bus. Reading from this register reads the CRC accumulator.

## REGISTER 13-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |

|-------------|-----|-----|-----|-----|-----|-----|-----|--|

| SHIFT<15:8> |     |     |     |     |     |     |     |  |

| bit 7       |     |     |     |     |     |     |     |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<15:8>: CRC Shifter Register bits Reading from this register reads the CRC Shifter.

#### REGISTER 13-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|------------|-----|-----|-----|-----|-----|-----|-----|

| SHIFT<7:0> |     |     |     |     |     |     |     |

| bit 7      |     |     |     |     |     |     |     |

|            |     |     |     |     |     |     |     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<7:0>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

<sup>© 2015-2017</sup> Microchip Technology Inc.

## 16.0 INTERRUPT-ON-CHANGE

PORTA, PORTB, PORTC and pin RE3 of PORTE can be configured to operate as Interrupt-on-Change (IOC) pins on PIC18(L)F2x/4xK40 family devices. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 16-1 is a block diagram of the IOC module.

## 16.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 16.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 16.3 Interrupt Flags

The IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits located in the IOCAF, IOCBF, IOCCF and IOCEF registers respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIRO register reflects the status of all IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits.

## 16.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx, IOCCFx and IOCEF3 bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

## EXAMPLE 16-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

| MOVLW | 0xff   |              |

|-------|--------|--------------|

| XORWF | IOCAF, | W            |

| ANDWF | IOCAF, | F            |

|       |        |              |

|       | XORWF  | XORWF IOCAF, |

## 16.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

## 19.7 Timer1/3/5 16-Bit Read/Write Mode

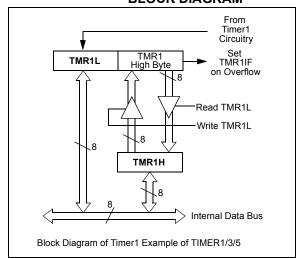

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time. Reference the block diagram in Figure 19-2 for more details.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

#### FIGURE 19-2:

#### TIMER1/3/5 16-BIT READ/WRITE MODE BLOCK DIAGRAM

## 19.8 Timer1/3/5 Gate

Timer1/3/5 can be configured to count freely or the count can be enabled and disabled using Timer1/3/5 gate circuitry. This is also referred to as Timer1/3/5 gate enable.

Timer1/3/5 gate can also be driven by multiple selectable sources.

## 19.8.1 TIMER1/3/5 GATE ENABLE

The Timer1/3/5 Gate Enable mode is enabled by setting the TMRxGE bit of the TxGCON register. The polarity of the Timer1/3/5 Gate Enable mode is configured using the TxGPOL bit of the TxGCON register.

When Timer1/3/5 Gate Enable mode is enabled, Timer1/3/5 will increment on the rising edge of the Timer1/3/5 clock source. When Timer1/3/5 Gate signal is inactive, the timer will not increment and hold the current count. Enable mode is disabled, no incrementing will occur and Timer1/3/5 will hold the current count. See Figure 19-4 for timing details.

| TABLE 19-3: | TIMER1/3/5 GATE ENABLE |

|-------------|------------------------|

|             | SELECTIONS             |

| TMRxCLK    | TxGPOL | TxG | Timer1/3/5<br>Operation |

|------------|--------|-----|-------------------------|

| $\uparrow$ | 1      | 1   | Counts                  |

| $\uparrow$ | 1      | 0   | Holds Count             |

| 1          | 0      | 1   | Holds Count             |

| $\uparrow$ | 0      | 0   | Counts                  |

## REGISTER 21-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

bit 3-0 MODE<3:0>: CCPx Mode Select bits

| MODE | Operating<br>Mode | Operation                                | Set CCPxIF |

|------|-------------------|------------------------------------------|------------|

| 11xx | PWM               | PWM operation                            | Yes        |

| 1011 |                   | Pulse output; clear TMR1 <sup>(2)</sup>  | Yes        |

| 1010 | Comparo           | Pulse output                             | Yes        |

| 1001 |                   | Clear output <sup>(1)</sup>              | Yes        |

| 1000 |                   | Set output <sup>(1)</sup>                | Yes        |

| 0111 |                   | Every 16th rising edge of CCPx input     | Yes        |

| 0110 |                   | Every 4th rising edge of CCPx input      | Yes        |

| 0101 | Capture           | Every rising edge of CCPx input          | Yes        |

| 0100 |                   | Every falling edge of CCPx input         | Yes        |

| 0011 |                   | Every edge of CCPx input                 | Yes        |

| 0010 | Compara           | Toggle output                            | Yes        |

| 0001 | Compare           | Toggle output; clear TMR1 <sup>(2)</sup> | Yes        |

| 0000 | Disabled          |                                          | —          |

- **Note 1:** The set and clear operations of the Compare mode are reset by setting MODE = 4 'b0000 or EN = 0.

- 2: When MODE = 0001 or 1011, then the timer associated with the CCP module is cleared. TMR1 is the default selection for the CCP module, so it is used for indication purpose only.

| R/W-0/0         | R/W-1/1                      | R/W-0/0                                                            | R/W-1/1                          | R/W-0/0                                              | R/W-1/1          | R/W-0/0         | R/W-1/1 |

|-----------------|------------------------------|--------------------------------------------------------------------|----------------------------------|------------------------------------------------------|------------------|-----------------|---------|

| P4TSE           | EL<1:0>                      | P3TSEL<1:0>                                                        |                                  | C2TSEL<1:0>                                          |                  | C1TSEL<1:0>     |         |

| bit 7           |                              |                                                                    |                                  |                                                      |                  |                 | bit 0   |

|                 |                              |                                                                    |                                  |                                                      |                  |                 |         |

| Legend:         |                              |                                                                    |                                  |                                                      |                  |                 |         |

| R = Readable    | bit                          | W = Writable                                                       | bit                              | U = Unimplen                                         | nented bit, read | l as '0'        |         |

| -n = Value at I | POR                          | '1' = Bit is set                                                   |                                  | '0' = Bit is clea                                    | ared             | x = Bit is unkr | nown    |

| bit 7-6         | 11 = PWM4<br>10 = PWM4       | >: PWM4 Time<br>based on TMR<br>based on TMR<br>based on TMR<br>ed | 6<br>4                           | S                                                    |                  |                 |         |

| bit 5-4         | 11 = PWM3<br>10 = PWM3       | >: PWM3 Time<br>based on TMR<br>based on TMR<br>based on TMR<br>ed | 6<br>4                           | is                                                   |                  |                 |         |

| bit 3-2         | 11 = CCP2 is<br>10 = CCP2 is | based off Time<br>based off Time                                   | er5 in Capture<br>er3 in Capture | s<br>e/Compare mod<br>e/Compare mod<br>e/Compare mod | le and Timer4 i  | n PWM mode      |         |

| bit 1-0         | 11 = CCP1 is<br>10 = CCP1 is | based off Time<br>based off Time                                   | er5 in Capture<br>er3 in Capture | s<br>e/Compare mod<br>e/Compare mod<br>e/Compare mod | le and Timer4 i  | n PWM mode      |         |

## REGISTER 21-2: CCPTMRS: CCP TIMERS CONTROL REGISTER

| Name   | Bit 7  | Bit 6 | Bit 5         | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0   | Register<br>on page |

|--------|--------|-------|---------------|--------|-------|--------|---------|---------|---------------------|

| PIE2   | HLVDIE | ZCDIE | _             | _      | _     | —      | C2IE    | C1IE    | 181                 |

| PIR2   | HLVDIF | ZCDIF | _             | _      | _     | —      | C2IF    | C1IF    | 173                 |

| IPR2   | HLVDIP | ZCDIP | _             | _      | _     | —      | C2IP    | C1IP    | 189                 |

| ZCDCON | ZCDSEN |       | ZCDOUT        | ZCDPOL | —     | —      | ZCDINTP | ZCDINTN | 294                 |

| PMD2   | _      | DACMD | <b>ADC</b> MD | _      | _     | CMP2MD | CMP1MD  | ZCDMD   | 70                  |

## TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

## TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit 15/7 | Bit 14/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|----------|----------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 15:8 | XINST    | _        | DEBUG    | STVREN   | PPS1WAY  | ZCD      | BORV1   | BORV0   | 24                  |

|         | 7:0  | BOREN1   | BOREN0   | LPBOREN  | _        | _        | _        | PWRTE   | MCLRE   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

## 24.9 Dead-Band Jitter

When the rising and falling edges of the input source are asynchronous to the CWG clock, it creates jitter in the dead-band time delay. The maximum jitter is equal to one CWG clock period. Refer to Equation 24-1 for more details.

## EQUATION 24-1: DEAD-BAND DELAY TIME CALCULATION

$T_{DEAD - BAND\_MIN} = \frac{1}{F_{CWG} CLOCK} \bullet DBx < 4:0>$   $T_{DEAD - BANDMAX} = \frac{1}{F_{CWG} CLOCK} \bullet DBx < 4:0>+1$   $T_{JITTER} = T_{DEAD - BAND\_MAX} - T_{DEAD - BAND\_MIN}$   $T_{JITTER} = \frac{1}{F_{CWG\_CLOCK}}$   $T_{DEAD - BAND\_MAX} = T_{DEAD - BAND\_MIN} + T_{JITTER}$  EXAMPLE DBR < 4:0>= 0x0A = 10  $F_{CWG\_CLOCK} = 8 MHz$   $T_{JITTER} = \frac{1}{8MHz} = 125 \text{ ns}$   $T_{DEAD - BAND\_MIN} = 125 \text{ ns} *10 = 125 \text{ µs}$   $T_{DEAD - BAND\_MIN} = 1.25 \text{ µs} + 0.125 \text{ µs} = 1.37 \text{µs}$

## 25.1 Register Definitions: Modulation Control

Long bit name prefixes for the Modulation peripheral is shown in Table 25-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

## TABLE 25-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| MD         | MD              |

## REGISTER 25-1: MDCON0: MODULATION CONTROL REGISTER 0

| R/W-0/0     | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |  |

|-------------|-----|---------|---------|-----|-----|-----|---------|--|

| EN          | —   | OUT     | OPOL    | —   | —   | —   | BIT     |  |

| bit 7 bit 0 |     |         |         |     |     |     |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Modulator Module Enable bit                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Modulator module is enabled and mixing input signals</li> <li>0 = Modulator module is disabled and has no output</li> </ul>                                                    |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5   | OUT: Modulator Output bit                                                                                                                                                                   |

|         | Displays the current output value of the Modulator module. <sup>(1)</sup>                                                                                                                   |

| bit 4   | OPOL: Modulator Output Polarity Select bit                                                                                                                                                  |

|         | <ul> <li>1 = Modulator output signal is inverted; idle high output</li> <li>0 = Modulator output signal is not inverted; idle low output</li> </ul>                                         |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 0   | BIT: Allows software to manually set modulation source input to module <sup>(2)</sup>                                                                                                       |

| Note 1: | The modulated output frequency can be greater and asynchronous from the clock that updates this register bit, the bit value may not be valid for higher speed modulator or carrier signals. |

| 2:      | MDBIT must be selected as the modulation source in the MDSRC register for this operation.                                                                                                   |

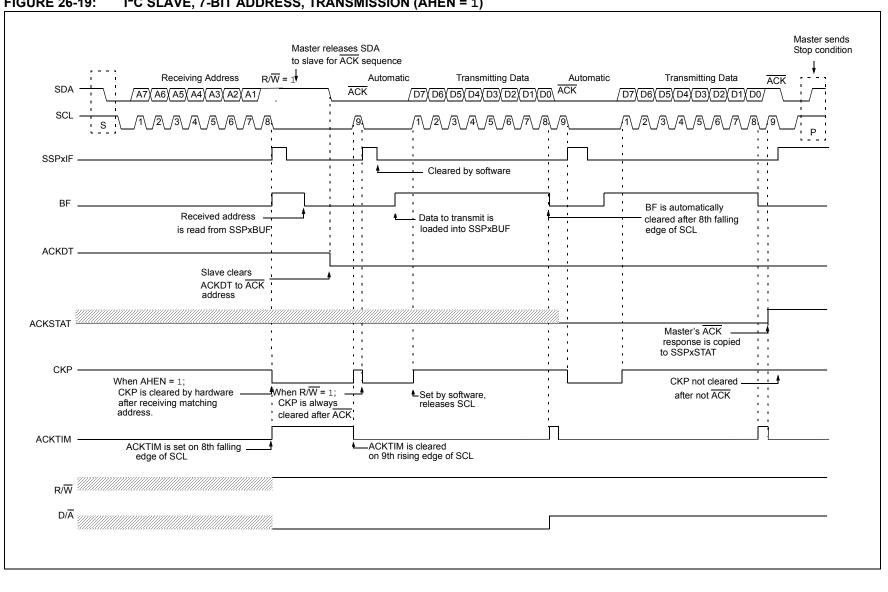

# **FIGURE 26-19:**

PIC18(L)F26/45/46K40

-n/n = Value at POR and BOR/Value at all other Resets

## REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

x = Bit is unknown

| R-x              | R-x | R-x              | R-x  | R-x                                | R-x | R-x | R-x   |  |  |

|------------------|-----|------------------|------|------------------------------------|-----|-----|-------|--|--|

|                  |     |                  | ADER | R<7:0>                             |     |     |       |  |  |

| bit 7            |     |                  |      |                                    |     |     | bit 0 |  |  |

|                  |     |                  |      |                                    |     |     |       |  |  |

| Legend:          |     |                  |      |                                    |     |     |       |  |  |

| R = Readable bit |     | W = Writable bit |      | U = Unimplemented bit, read as '0' |     |     |       |  |  |

| '1' = Bit is set | '0' = Bit is cleared                                                                           |

|------------------|------------------------------------------------------------------------------------------------|

|                  |                                                                                                |

| bit 7-0          | ADERR<7:0>: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined |

## REGISTER 31-28 ADI THH: ADC I OWER THRESHOLD HIGH BYTE REGISTER

by ADCALC bits of ADCON3, see Register 23-1 for more details.

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |  |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| ADLTH<15:8> |         |         |         |         |         |         |         |  |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |  |

|             |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADLTH<15:8>: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

## REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| ADLTH<7:0> |         |         |         |         |         |         |         |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |

|            |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADLTH<7:0>: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2015-2017 Microchip Technology Inc.

u = Bit is unchanged

| REGISTER 32-4. |     | -4. CIVIXE | CWAPCH. COMPARATOR & NON-INVERTING CHANNEL SELECT REGISTER |     |     |          |         |         |  |

|----------------|-----|------------|------------------------------------------------------------|-----|-----|----------|---------|---------|--|

|                | U-0 | U-0        | U-0                                                        | U-0 | U-0 | R/W-0/0  | R/W-0/0 | R/W-0/0 |  |

|                |     | _          | _                                                          |     | _   | PCH<2:0> |         |         |  |

| REGISTER 32-4: | CMxPCH: COMPARATOR x NON-INVERTING CHANNEL SELECT REGISTER |

|----------------|------------------------------------------------------------|

|----------------|------------------------------------------------------------|

| bit 7             |                  |                                    | b                  | oit O |

|-------------------|------------------|------------------------------------|--------------------|-------|

|                   |                  |                                    |                    |       |

| Legend:           |                  |                                    |                    |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |       |

| bit 7-3 | Unimplemented: Read as '0'                                   |

|---------|--------------------------------------------------------------|

| bit 2-0 | PCH<2:0>: Comparator Non-Inverting Input Channel Select bits |

|         | 111 <b>=</b> AVss                                            |

|         | 110 = FVR_Buffer2                                            |

|         | 101 = DAC_Output                                             |

|         | 100 = CxPCH not connected                                    |

|         | 011 = CxPCH not connected                                    |

|         | 010 = CxPCH not connected                                    |

|         | 001 = CxIN1+                                                 |

|         | 000 = CxIN0+                                                 |

|         |                                                              |

## REGISTER 32-5: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | _   | —   | —   | MC2OUT | MC1OUT |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 1 MC2OUT: Mirror copy of C2OUT bit

| bit 0 | MC10UT: Mirror copy of C10UT bit |

|-------|----------------------------------|

|-------|----------------------------------|

## 36.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 36.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker