Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k40t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 Register Definitions: Configuration Words

| REGISTER 3-1: Configuration word 1L (30 0000n): Oscillators |                            |                   |       |                                    |              |                   |       |  |  |  |

|-------------------------------------------------------------|----------------------------|-------------------|-------|------------------------------------|--------------|-------------------|-------|--|--|--|

| U-1                                                         | R/W-1                      | R/W-1             | R/W-1 | U-1                                | R/W-1        | R/W-1             | R/W-1 |  |  |  |

| _                                                           |                            | RSTOSC<2:0> — FEX |       |                                    | FEXTOSC<2:0> |                   |       |  |  |  |

| bit 7                                                       | it 7                       |                   |       |                                    |              |                   | bit 0 |  |  |  |

|                                                             |                            |                   |       |                                    |              |                   |       |  |  |  |

| Legend:                                                     |                            |                   |       |                                    |              |                   |       |  |  |  |

| R = Readable bi                                             | dable bit W = Writable bit |                   |       | U = Unimplemented bit, read as '1' |              |                   |       |  |  |  |

| -n = Value for blank device                                 |                            | '1' = Bit is set  |       | '0' = Bit is cle                   | eared        | x = Bit is unknow | /n    |  |  |  |

|                                                             |                            |                   |       |                                    |              |                   |       |  |  |  |

#### **REGISTER 3-1:** Configuration Word 1L (30 0000h): Oscillators

bit 7 Unimplemented: Read as '1'

#### RSTOSC<2:0>: Power-up Default Value for COSC bits bit 6-4 This value is the Reset default value for COSC and selects the oscillator first used by user software. Refer to COSC operation. 111 = EXTOSC operating per FEXTOSC bits (device manufacturing default) 110 = HFINTOSC with HFFRQ = 4 MHz (Register 4-5) and CDIV = 4:1 (Register 4-2) 101 = LFINTOSC 100 = SOSC 011 = Reserved 010 = EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits 001 = Reserved 000 = HFINTOSC with HFFRQ = 64 MHz (Register 4-5) and CDIV = 1:1 (Register 4-2). Resets COSC/NOSC to 3'b110. bit 3 Unimplemented: Read as '1' bit 2-0 FEXTOSC<2:0>: FEXTOSC External Oscillator Mode Selection bits 111 = EC (external clock) above 8 MHz; PFM set to high power (device manufacturing default) 110 = EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power 101 = EC (external clock) below 500 kHz; PFM set to low power 100 = Oscillator not enabled 011 = Reserved (do not use) 010 = HS (crystal oscillator) above 8 MHz; PFM set to high power

- 001 = XT (crystal oscillator) above 500 kHz, below 8 MHz; PFM set to medium power

- 000 = LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

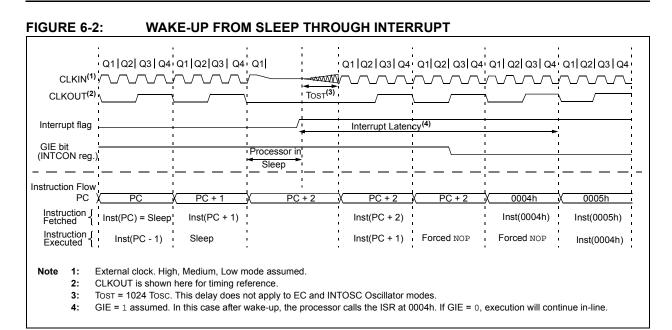

# 6.2.3 LOW-POWER SLEEP MODE

The PIC18F2x/4xK40 device family contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC18F2x/4xK40 devices allows the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register.

# 6.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

# 7.5 Register Definitions: Peripheral Module Disable

| R/W-0/0                 | R/W-0/0                         | R/W-0/0                                                                            | R/W-0/0                        | R/W-0/0                                       | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-------------------------|---------------------------------|------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|------------------|------------------|--------------|

| SYSCMD                  | FVRMD                           | HLVDMD                                                                             | CRCMD                          | SCANMD                                        | NVMMD            | CLKRMD           | IOCMD        |

| 7                       | •                               | •                                                                                  | •                              | •                                             |                  | •                |              |

|                         |                                 |                                                                                    |                                |                                               |                  |                  |              |

| Legend:<br>R = Readable | , hit                           | W = Writable                                                                       | hit                            | II – Unimplor                                 | nented bit, read |                  |              |

| u = Bit is uncl         |                                 | x = Bit is unkn                                                                    |                                | •                                             |                  | R/Value at all o | thar Pasata  |

| '1' = Bit is set        | •                               | 0' = Bit is clear                                                                  |                                |                                               |                  |                  |              |

|                         |                                 |                                                                                    | areu                           | q – value dep                                 | ends on condi    |                  |              |

| bit 7                   | See descript<br>1 = System      | isable Periphera<br>ion in <b>Section 7</b><br>clock network di<br>clock network e | .4 "System Cl<br>sabled (Fosc) | k Network bit <sup>(1)</sup><br>ock Disable". |                  |                  |              |

| bit 6                   | 1 = FVR mo                      | able Fixed Volta<br>dule disabled<br>dule enabled                                  | ge Reference                   | bit                                           |                  |                  |              |

| bit 5                   | 1 = HLVD m                      | isable Low-Volta<br>nodule disabled<br>nodule enabled                              | ige Detect bit                 |                                               |                  |                  |              |

| bit 4                   | 1 = CRC mc                      | able CRC Engir<br>odule disabled<br>odule enabled                                  | ne bit                         |                                               |                  |                  |              |

| bit 3                   | 1 = NVM M                       | isable NVM Me<br>emory Scan mo<br>emory Scan mo                                    | dule disabled                  | bit <sup>(2)</sup>                            |                  |                  |              |

| bit 2                   | 1 = All Mem                     | M Module Disal<br>ory reading and<br>odule enabled                                 |                                | bled; NVMCON                                  | registers canr   | not be written   |              |

| bit 1                   | 1 = CLKR m                      | isable Clock Re<br>odule disabled<br>odule enabled                                 | ference bit                    |                                               |                  |                  |              |

| bit 0                   | 1 = IOC mod                     | able Interrupt-on<br>dule(s) disabled<br>dule(s) enabled                           | -Change bit, A                 | ll Ports                                      |                  |                  |              |

|                         | earing the SYS<br>Fosc/4 are no | SCMD bit disable of affected.                                                      | es the system                  | clock (Fosc) to                               | peripherals, h   | owever periphe   | rals clocked |

# REGISTER 7-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

### 11.1.2 CONTROL REGISTERS

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the following registers:

- NVMCON1 register

- NVMCON2 register

- TABLAT register

- TBLPTR registers

#### 11.1.2.1 NVMCON1 and NVMCON2 Registers

The NVMCON1 register (Register 11-1) is the control register for memory accesses. The NVMCON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading NVMCON2 will read all '0's.

The NVMREG<1:0> control bits determine if the access will be to Data EEPROM Memory locations. PFM locations or User IDs, Configuration bits, Rev ID and Device ID. When NVMREG<1:0> = 00, any subsequent operations will operate on the Data EEPROM Memory. When NVMREG<1:0> = 10, any subsequent operations will operate on the program memory. When NVMREG<1:0> = x1, any subsequent operations will operate on the program memory. When NVMREG<1:0> = x1, any subsequent operations will operate on the Data Device ID.

The FREE bit allows the program memory erase operation. When the FREE bit is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled. This bit is applicable only to the PFM and not to data EEPROM.

When set, the WREN bit will allow a program/erase operation. The WREN bit is cleared on power-up.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is successfully complete.

The WR control bit initiates erase/write cycle operation when the NVMREG<1:0> bits point to the Data EEPROM Memory location, and it initiates a write operation when the NVMREG<1:0> bits point to the PFM location. The WR bit cannot be cleared by firmware; it can only be set by firmware. Then the WR bit is cleared by hardware at the completion of the write operation.

The NVMIF Interrupt Flag bit of the PIR7 register is set when the write is complete. The NVMIF flag stays set until cleared by firmware.

#### 11.1.2.2 TABLAT – Table Latch Register

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

# 11.1.2.3 TBLPTR – Table Pointer Register

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22<sup>nd</sup> bit allows access to the Device ID, the User ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

#### 11.1.2.4 Table Pointer Boundaries

TBLPTR is used in reads, writes and erases of the Program Flash Memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 11-3). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the Flash memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during Flash memory writes. For more detail, see **Section 11.1.6 "Writing to Program Flash Memory"**.

Figure 11-3 describes the relevant boundaries of TBLPTR based on Program Flash Memory operations.

### EXAMPLE 11-4: WRITING TO PROGRAM FLASH MEMORY

|             | MOVLW          | D'64′                      | ; number of bytes in erase block      |

|-------------|----------------|----------------------------|---------------------------------------|

|             | MOVWF          | COUNTER                    |                                       |

|             | MOVLW          | BUFFER_ADDR_HIGH           | ; point to buffer                     |

|             | MOVWF          | FSR0H                      |                                       |

|             | MOVLW          | BUFFER_ADDR_LOW            |                                       |

|             | MOVWF          | FSROL – –                  |                                       |

|             | MOVLW          | CODE_ADDR_UPPER            | ; Load TBLPTR with the base           |

|             | MOVWF          | TBLPTRU                    | ; address of the memory block         |

|             | MOVLW          | CODE_ADDR_HIGH             |                                       |

|             | MOVWF          | TBLPTRH                    |                                       |

|             | MOVLW          | CODE_ADDR_LOW              |                                       |

|             | MOVWF          | TBLPTRL                    |                                       |

| READ_BLOCK  |                |                            |                                       |

|             | TBLRD*+        |                            | ; read into TABLAT, and inc           |

|             | MOVF           | TABLAT, W                  | ; get data                            |

|             | MOVWF          | POSTINC0                   | ; store data                          |

|             | DECFSZ         | COUNTER                    | ; done?                               |

|             | BRA            | READ_BLOCK                 | ; repeat                              |

| MODIFY_WORD | )              |                            |                                       |

|             | MOVLW          | BUFFER_ADDR_HIGH           | ; point to buffer                     |

|             | MOVWF          | FSR0H                      |                                       |

|             | MOVLW          | BUFFER_ADDR_LOW            |                                       |

|             | MOVWF          | FSROL                      |                                       |

|             | MOVLW          | NEW_DATA_LOW               | ; update buffer word                  |

|             | MOVWF          | POSTINC0                   |                                       |

|             | MOVLW          | NEW_DATA_HIGH              |                                       |

|             | MOVWF          | INDF0                      |                                       |

| ERASE_BLOCK |                | CODE ADDE HDDED            | ; load TBLPTR with the base           |

|             | MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU | ; address of the memory block         |

|             | MOVLW          | CODE_ADDR_HIGH             | , address of the memory brock         |

|             | MOVWF          | TBLPTRH                    |                                       |

|             | MOVLW          | CODE_ADDR_LOW              |                                       |

|             | MOVWF          | TBLPTRL                    |                                       |

|             | BCF            | NVMCON1, NVMREG0           | ; point to Program Flash Memory       |

|             | BSF            | NVMCON1, NVMREG1           | ; point to Program Flash Memory       |

|             | BSF            | NVMCON1, WREN              | ; enable write to memory              |

|             | BSF            | NVMCON1, FREE              | ; enable Erase operation              |

|             | BCF            | INTCON, GIE                | ; disable interrupts                  |

|             | MOVLW          | 55h                        |                                       |

| Required    | MOVWF          | NVMCON2                    | ; write 55h                           |

| Sequence    | MOVLW          | AAh                        |                                       |

|             | MOVWF          | NVMCON2                    | ; write OAAh                          |

|             | BSF            | NVMCON1, WR                | ; start erase (CPU stall)             |

|             | BSF            | INTCON, GIE                | ; re-enable interrupts                |

|             | TBLRD*-        |                            | ; dummy read decrement                |

|             | MOVLW          | BUFFER_ADDR_HIGH           | ; point to buffer                     |

|             | MOVWF          | FSROH                      |                                       |

|             | MOVLW          | BUFFER_ADDR_LOW            |                                       |

|             | MOVWF          | FSROL                      |                                       |

| WRITE_BUFFE | _              |                            |                                       |

|             | MOVLW          | BlockSize                  | ; number of bytes in holding register |

|             | MOVWF          | COUNTER                    |                                       |

|             | MOVLW          | D'64'/BlockSize            | ; number of write blocks in 64 bytes  |

|             | MOVWF          | COUNTER2                   |                                       |

|             |                |                            |                                       |

# 14.8 Register Definitions: Interrupt Control

| REGISTER 14-1: | <b>INTCON: INTERRUPT</b> | CONTROL REGISTER |

|----------------|--------------------------|------------------|

|                |                          |                  |

| R/W-0/0               | R/W-0/0                                                                                                  | R/W-0/0                                                                       | U-0                                              | U-0             | R/W-1/1          | R/W-1/1            | R/W-1/1        |

|-----------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------|-----------------|------------------|--------------------|----------------|

| GIE/GIEH              | PEIE/GIEL                                                                                                | IPEN                                                                          | —                                                | -               | INT2EDG          | INT1EDG            | INT0EDG        |

| bit 7                 |                                                                                                          | •                                                                             |                                                  | •               |                  | •                  | bit (          |

|                       |                                                                                                          |                                                                               |                                                  |                 |                  |                    |                |

| Legend:               |                                                                                                          |                                                                               |                                                  |                 |                  |                    |                |

| R = Readabl           | e bit                                                                                                    | W = Writable                                                                  | bit                                              | U = Unimple     | emented bit, rea | d as '0'           |                |

| -n = Value at         | POR                                                                                                      | '1' = Bit is set                                                              |                                                  | '0' = Bit is c  | leared           | x = Bit is unk     | nown           |

| bit 7                 | <b>GIE/GIEH:</b> G<br>If IPEN = 1:                                                                       | lobal Interrupt I                                                             | Enable bit                                       |                 |                  |                    |                |

|                       |                                                                                                          | ables all unma<br>sables all interr                                           |                                                  | pts and cleared | by hardware for  | r high-priority ir | nterrupts only |

|                       | 1 = En                                                                                                   | ables all unmas<br>sables all interru                                         |                                                  | ots and cleared | by hardware for  | all interrupts     |                |

| bit 6                 |                                                                                                          | Peripheral Inter                                                              | rupt Enable                                      | bit             |                  |                    |                |

|                       | 0 = Dis                                                                                                  | ables all low-pr<br>sables all low-p                                          |                                                  |                 | d by hardware fo | r low-priority in  | terrupts only  |

|                       |                                                                                                          | ables all unma<br>sables all peripl                                           |                                                  | -               |                  |                    |                |

| bit 5                 | 1 = Enable                                                                                               | pt Priority Enab<br>priority levels o<br>priority levels o                    | n interrupts                                     | i               |                  |                    |                |

| bit 4-3               | Unimplemen                                                                                               | ited: Read as 'd                                                              | )'                                               |                 |                  |                    |                |

| bit 2                 | 1 = Interrup                                                                                             | xternal Interrup<br>at on rising edge<br>at on falling edge                   | e of INT2 pir                                    | ı               |                  |                    |                |

| bit 1                 | 1 = Interrup                                                                                             | xternal Interrupt<br>at on rising edge<br>at on falling edge                  | e of INT1 pir                                    | ı               |                  |                    |                |

| bit 0                 | 1 = Interrup                                                                                             | xternal Interrupt<br>at on rising edge<br>at on falling edge                  | e of INT0 pir                                    | ı               |                  |                    |                |

| co<br>its<br>er<br>th | iterrupt flag bits a<br>ondition occurs, r<br>s corresponding<br>nable bit. User s<br>le appropriate inf | egardless of the<br>enable bit or the<br>software should<br>terrupt flag bits | e state of<br>ne global<br>d ensure<br>are clear |                 |                  |                    |                |

prior to enabling an interrupt. This feature

allows for software polling.

| R/W-x/u                                               | R/W-x/u                         | R/W-x/u              | R/W-x/u      | R/W-x/u            | R/W-x/u  | R/W-x/u | R/W-x/u |  |

|-------------------------------------------------------|---------------------------------|----------------------|--------------|--------------------|----------|---------|---------|--|

| LATx7                                                 | LATx6                           | LATx5                | LATx4        | LATx3              | LATx2    | LATx1   | LATx0   |  |

| bit 7                                                 |                                 |                      |              |                    |          |         | bit 0   |  |

|                                                       |                                 |                      |              |                    |          |         |         |  |

| Legend:                                               |                                 |                      |              |                    |          |         |         |  |

| R = Readable                                          | = Readable bit W = Writable bit |                      | U = Unimpler | nented bit, read   | 1 as '0' |         |         |  |

| '1' = Bit is set                                      |                                 | '0' = Bit is cleared |              | x = Bit is unknown |          |         |         |  |

| -n/n = Value at POR and BOR/Value at all other Resets |                                 |                      |              |                    |          |         |         |  |

# REGISTER 15-3: LATx: LATx REGISTER<sup>(1)</sup>

bit 7-0 LATx<7:0>: Rx7:Rx0 Output Latch Value bits

**Note 1:** Writes to LATx are equivalent with writes to the corresponding PORTx register. Reads from LATx register return register values, not I/O pin values.

|      | Dev        | vice          |       |       |       |       |       |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| LATA | Х          | Х             | LATA7 | LATA6 | LATA5 | LATA4 | LATA3 | LATA2 | LATA1 | LATA0 |

| LATB | Х          | Х             | LATB7 | LATB6 | LATB5 | LATB4 | LATB3 | LATB2 | LATB1 | LATB0 |

| LATC | Х          | Х             | LATC7 | LATC6 | LATC5 | LATC4 | LATC3 | LATC2 | LATC1 | LATC0 |

| LATD | Х          |               | _     | _     | _     | _     | —     | _     | —     | _     |

|      |            | Х             | LATD7 | LATD6 | LATD5 | LATD4 | LATD3 | LATD2 | LATD1 | LATD0 |

| LATE | Х          |               | _     | —     | —     | —     | —     | _     | —     | _     |

|      |            | Х             | _     | _     | —     | _     | —     | LATE2 | LATE1 | LATE0 |

#### TABLE 15-4: LAT REGISTERS

#### **REGISTER 17-3: PPSLOCK: PPS LOCK REGISTER**

|             |  | PPSLOCKED |  |  |  |  |  |  |  |

|-------------|--|-----------|--|--|--|--|--|--|--|

|             |  |           |  |  |  |  |  |  |  |

| bit 7 bit 0 |  |           |  |  |  |  |  |  |  |

|             |  |           |  |  |  |  |  |  |  |

|             |  |           |  |  |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 0 PPSLOCKED: PPS Locked bit

1 = PPS is locked. PPS selections can not be changed.

0 = PPS is not locked. PPS selections can be changed.

### TABLE 17-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

| Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3        | Bit 2      | Bit 1   | Bit 0     | Register<br>on page |  |

|------------|-------|-------|-------|-------------|--------------|------------|---------|-----------|---------------------|--|

| PPSLOCK    | —     | _     | _     | —           | —            | —          | —       | PPSLOCKED | 219                 |  |

| INTOPPS    | —     | _     | _     |             |              | INT0PPS<   | 4:0>    | •         | 216                 |  |

| INT1PPS    | —     | _     | _     |             |              | INT1PPS<   | 4:0>    |           | 216                 |  |

| INT2PPS    | —     | _     | _     |             |              | INT2PPS<   | 4:0>    |           | 216                 |  |

| TOCKIPPS   | —     | _     |       |             |              | T0CKIPPS<  | <4:0>   |           | 216                 |  |

| T1CKIPPS   | _     | _     | _     |             |              | T1CKIPPS<  | <4:0>   |           | 216                 |  |

| T1GPPS     | —     | _     | _     |             |              | T1GPPS<    | 4:0>    |           | 216                 |  |

| T3CKIPPS   | —     | _     |       |             |              | T3CKIPPS<  | <4:0>   |           | 216                 |  |

| T3GPPS     | _     | _     | _     |             |              | T3GPPS<    | 4:0>    |           | 216                 |  |

| T5CKIPPS   | —     | _     | _     |             |              | T5CKIPPS<  | <4:0>   |           | 216                 |  |

| T5GPPS     | —     | _     |       |             |              | T5GPPS<    | 4:0>    |           | 216                 |  |

| T2INPPS    | _     |       |       |             | T2INPPS<4:0> |            |         |           |                     |  |

| T4INPPS    | —     | _     | _     |             | T4INPPS<4:0> |            |         |           |                     |  |

| T6INPPS    | —     | _     | _     |             | T6INPPS<4:0> |            |         |           |                     |  |

| CCP1PPS    | —     | _     | _     |             |              | CCP1PPS<   | :4:0>   |           | 216                 |  |

| CCP2PPS    | —     | _     | _     |             |              | CCP2PPS<   | :4:0>   |           | 216                 |  |

| CWG1PPS    | —     | _     | _     |             |              | CWG1PPS    | <4:0>   |           | 216                 |  |

| MDCARLPPS  | —     | _     | _     |             | Ν            | /IDCARLPPS | 6<4:0>  |           | 216                 |  |

| MDCARHPPS  | —     | _     | _     |             | Ν            | IDCARHPP   | S<4:0>  |           | 216                 |  |

| MDSRCPPS   | —     | _     | _     |             |              | MDSRCPPS   | <4:0>   |           | 216                 |  |

| ADACTPPS   | —     | _     | _     |             |              | ADACTPPS   | <4:0>   |           | 216                 |  |

| SSP1CLKPPS | —     | _     | _     |             | S            | SP1CLKPP   | S<4:0>  |           | 216                 |  |

| SSP1DATPPS | —     | _     | _     |             | S            | SP1DATPP   | S<4:0>  |           | 216                 |  |

| SSP1SSPPS  | —     | _     | _     |             | S            | SSP1SSPPS  | \$<4:0> |           | 216                 |  |

| RX1PPS     | —     | _     | —     |             |              | RX1PPS<    | 4:0>    |           | 218                 |  |

| TX1PPS     | —     | _     | _     | TX1PPS<4:0> |              |            |         |           | 216                 |  |

| SSP2CLKPPS | —     | _     | _     |             | S            | SP2CLKPP   | S<4:0>  |           | 216                 |  |

| SSP2DATPPS | —     | _     | —     |             | S            | SP2DATPP   | S<4:0>  |           | 216                 |  |

© 2015-2017 Microchip Technology Inc.

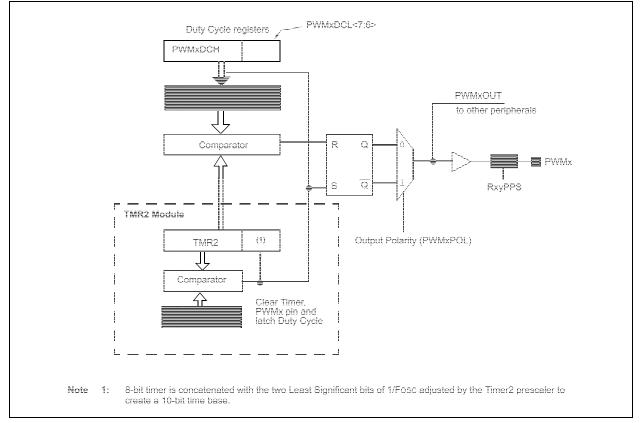

# 22.0 PULSE-WIDTH MODULATION (PWM)

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PRx

- TxCON

- PWMxDCH

- PWMxDCL

- PWMxCON

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin. Each PWM module can select the timer source that controls the module. Each module has an independent timer selection which can be accessed using the CCPTMRS register (Register 21-2). Please note that the PWM mode operation is described with respect to TMR2 in the following sections.

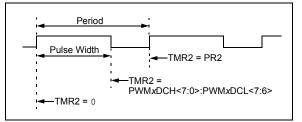

Figure 22-1 shows a simplified block diagram of PWM operation.

Figure 22-2 shows a typical waveform of the PWM signal.

# FIGURE 22-1: SIMPLIFIED PWM BLOCK DIAGRAM

FIGURE 22-2:

PWM OUTPUT

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 22.1.9 "Setup for PWM Operation using PWMx Pins".

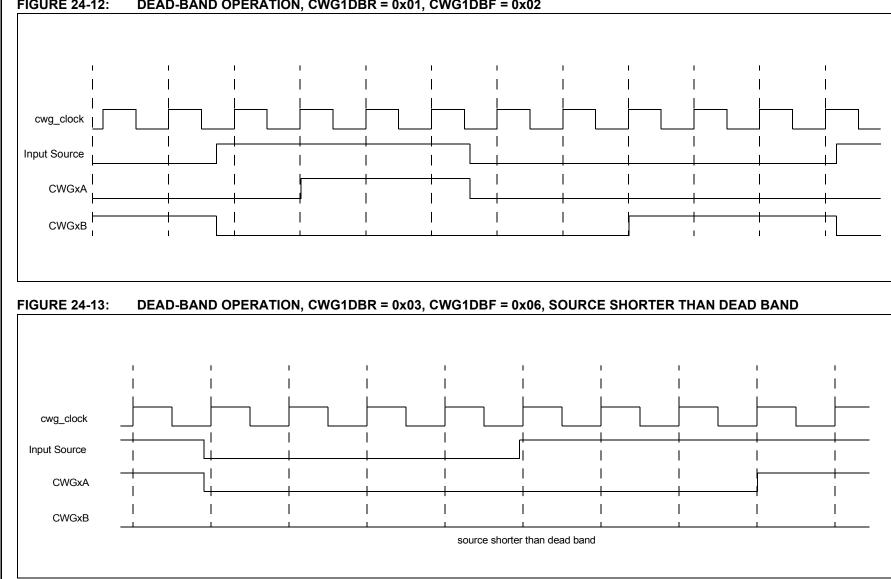

#### FIGURE 24-12: DEAD-BAND OPERATION, CWG1DBR = 0x01, CWG1DBF = 0x02

PIC18(L)F26/45/46K40

#### **Register Definitions: MSSP Control** 26.4

| R/W-0        | R/W-0                                                                                                        | R-0                | R-0            | R-0                  | R-0             | R-0                | R-0   |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------|--------------------|----------------|----------------------|-----------------|--------------------|-------|--|--|

| SMP          | CKE <sup>(1)</sup>                                                                                           | D/A                | Р              | S                    | R/W             | UA                 | BF    |  |  |

| bit 7        |                                                                                                              | ł                  |                | L.                   |                 | I.                 | bit C |  |  |

|              |                                                                                                              |                    |                |                      |                 |                    |       |  |  |

| Legend:      |                                                                                                              |                    |                |                      |                 |                    |       |  |  |

| R = Readab   | le bit                                                                                                       | W = Writable bit   |                | U = Unimplen         | nented bit, rea | id as '0'          |       |  |  |

| -n = Value a | It POR                                                                                                       | '1' = Bit is set   |                | '0' = Bit is cleared |                 | x = Bit is unknown |       |  |  |

|              |                                                                                                              | 1. 1.9             |                |                      |                 |                    |       |  |  |

| bit 7        | SMP: Samp                                                                                                    |                    |                |                      |                 |                    |       |  |  |

|              | <u>SPI Master mode:</u><br>1 = Input data is sampled at the end of data output time                          |                    |                |                      |                 |                    |       |  |  |

|              | 0 = Input data is sampled at the middle of data output time                                                  |                    |                |                      |                 |                    |       |  |  |

|              | SPI Slave mode:                                                                                              |                    |                |                      |                 |                    |       |  |  |

|              | SMP must b                                                                                                   | be cleared when    | SPI is used in | n Slave mode.        |                 |                    |       |  |  |

| bit 6        | CKE: SPI Clock Select bit <sup>(1)</sup>                                                                     |                    |                |                      |                 |                    |       |  |  |

|              | 1 = Transmit occurs on the transition from active to Idle clock state                                        |                    |                |                      |                 |                    |       |  |  |

|              | 0 = Transmit occurs on the transition from Idle to active clock state                                        |                    |                |                      |                 |                    |       |  |  |

| bit 5        | D/A: Data/Address bit                                                                                        |                    |                |                      |                 |                    |       |  |  |

|              | Used in I <sup>2</sup> C mode only.                                                                          |                    |                |                      |                 |                    |       |  |  |

| bit 4        | P: Stop bit                                                                                                  |                    |                |                      |                 |                    |       |  |  |

|              | Used in I <sup>2</sup> C mode only. This bit is cleared when the MSSPx module is disabled; SSPEN is cleared. |                    |                |                      |                 |                    |       |  |  |

| bit 3        | S: Start bit                                                                                                 |                    |                |                      |                 |                    |       |  |  |

|              | Used in I <sup>2</sup> C mode only.                                                                          |                    |                |                      |                 |                    |       |  |  |

| bit 2        | R/W: Read/Write Information bit                                                                              |                    |                |                      |                 |                    |       |  |  |

|              | Used in I <sup>2</sup> C mode only.                                                                          |                    |                |                      |                 |                    |       |  |  |

| bit 1        | UA: Update Address bit                                                                                       |                    |                |                      |                 |                    |       |  |  |

|              | Used in I <sup>2</sup> C mode only.                                                                          |                    |                |                      |                 |                    |       |  |  |

| bit 0        | BF: Buffer Full Status bit (Receive mode only)                                                               |                    |                |                      |                 |                    |       |  |  |

|              | 1 = Receive is complete, SSPxBUF is full                                                                     |                    |                |                      |                 |                    |       |  |  |

|              | 0 = Receive                                                                                                  | e is not complete  | , SSPxBUF is   | sempty               |                 |                    |       |  |  |

| Note 1: F    | olarity of clock                                                                                             | state is set by th | ne CKP bit (S  | SPxCON1<4>).         |                 |                    |       |  |  |

|              |                                                                                                              |                    |                |                      |                 |                    |       |  |  |

#### REGISTER 26-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

### 26.9.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 26-14 and Figure 26-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

# 26.9.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 26-16 displays a module using both address and data holding. Figure 26-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

# 26.10.7 I<sup>2</sup>C Master Mode Reception

Master mode reception (Figure 26-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSP1CON2 register.

| Note: | The MSSP module must be in an Idle      |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | state before the RCEN bit is set or the |  |  |  |  |  |

|       | RCEN bit will be disregarded.           |  |  |  |  |  |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPxCON2 register.

### 26.10.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPSR. It is cleared when the SSPxBUF register is read.

# 26.10.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

# 26.10.7.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 26.10.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- 2. SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. User writes SSPxBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 6. The MSSP module shifts in the  $\overline{ACK}$  bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 7. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 8. User sets the RCEN bit of the SSPxCON2 register and the master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCL, SSPxIF and BF are set.

- 10. Master clears SSPxIF and reads the received byte from SSPUF, clears BF.

- 11. Master sets the ACK value sent to slave in the ACKDT bit of the SSPxCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Master's ACK is clocked out to the slave and SSPxIF is set.

- 13. User clears SSPxIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

#### 26.10.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 26.10.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 26.10.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

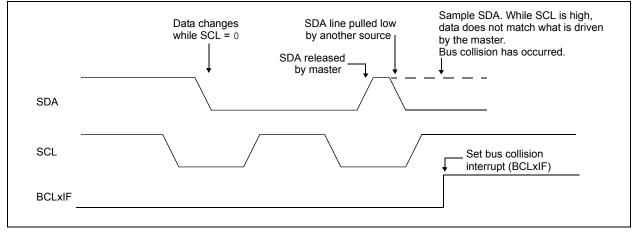

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 26.10.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF and reset the I<sup>2</sup>C port to its Idle state (Figure 26-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 26-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### 27.2.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 27-2. The data is received on the RXx/DTx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCxREG register.

### 27.2.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RXx/DTx I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 27.2.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 27.2.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCxIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

# 27.2.2.3 Receive Interrupts

The RCxIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCxIF interrupts are enabled by setting all of the following bits:

- RCxIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

# 31.0 ANALOG-TO-DIGITAL CONVERTER WITH COMPUTATION (ADC<sup>2</sup>) MODULE

The Analog-to-Digital Converter with Computation  $(ADC^2)$  allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair).

Additionally, the following features are provided within the ADC module:

- 8-bit Acquisition Timer

- Hardware Capacitive Voltage Divider (CVD) support:

- 8-bit precharge timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- · Automatic repeat and sequencing:

- Automated double sample conversion for CVD

- Two sets of result registers (Result and Previous result)

- Auto-conversion trigger

- Internal retrigger

- Computation features:

- Averaging and low-pass filter functions

- Reference comparison

- 2-level threshold comparison

- Selectable interrupts

Figure 31-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion and upon threshold comparison. These interrupts can be used to wake-up the device from Sleep.

# REGISTER 31-4: ADCON3: ADC CONTROL REGISTER 3

| U-0     | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W/HC-0 | R/W-0/0 | R/W-0/0    | R/W-0/0 |

|---------|---------|-------------|---------|----------|---------|------------|---------|

| _       |         | ADCALC<2:0> |         | ADSOI    |         | ADTMD<2:0> |         |

| bit 7   |         |             |         |          |         |            | bit 0   |

|         |         |             |         |          |         |            |         |

| Legend. |         |             |         |          |         |            |         |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 ADCALC<2:0>: ADC Error Calculation Mode Select bits

|        | Action During                                                | Application           |                                                              |

|--------|--------------------------------------------------------------|-----------------------|--------------------------------------------------------------|

| ADCALC | ADDSEN = 0ADDSEN = 1 CVDSingle-Sample ModeDouble-Sample Mode |                       |                                                              |

| 111    | Reserved                                                     | Reserved              | Reserved                                                     |

| 110    | Reserved                                                     | Reserved              | Reserved                                                     |

| 101    | ADLFTR-ADSTPT                                                | ADFLTR-ADSTPT         | Average/filtered value vs. setpoint                          |

| 100    | ADPREV-ADFLTR                                                | ADPREV-ADFLTR         | First derivative of filtered value <sup>(3)</sup> (negative) |

| 011    | Reserved                                                     | Reserved              | Reserved                                                     |

| 010    | ADRES-ADFLTR                                                 | (ADRES-ADPREV)-ADFLTR | Actual result vs.<br>averaged/filtered value                 |

| 001    | ADRES-ADSTPT                                                 | (ADRES-ADPREV)-ADSTPT | Actual result vs.setpoint                                    |

| 000    | ADRES-ADPREV                                                 | ADRES-ADPREV          | First derivative of single measurement <sup>(2)</sup>        |

|        |                                                              |                       | Actual CVD result in CVD mode <sup>(2)</sup>                 |

bit 3 ADSOI: ADC Stop-on-Interrupt bit

#### If ADCONT = 1:

- 1 = ADGO is cleared when the threshold conditions are met, otherwise the conversion is retriggered

- 0 = ADGO is not cleared by hardware, must be cleared by software to stop retriggers

#### bit 2-0 ADTMD<2:0>: Threshold Interrupt Mode Select bits

- 111 = Interrupt regardless of threshold test results

- 110 = Interrupt if ADERR>ADUTH

- 101 = Interrupt if ADERR≤ADUTH

- 100 = Interrupt if ADERR<ADLTH or ADERR>ADUTH

- 011 = Interrupt if ADERR>ADLTH and ADERR<ADUTH

- 010 = Interrupt if ADERR≥ADLTH

- 001 = Interrupt if ADERR<ADLTH

- 000 = Never interrupt

- Note 1: When ADPSIS = 0, the value of ADRES-ADPREV) is the value of (S2-S1) from Table 31-3.

- 2: When ADPSIS = 0

- 3: When ADPSIS = 1.

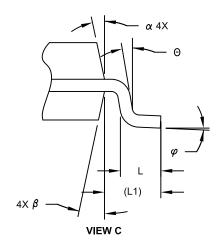

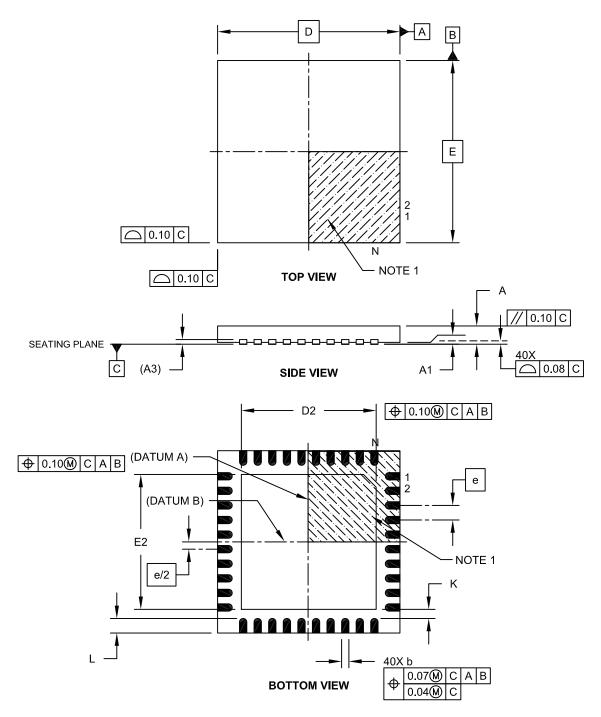

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |  |

|--------------------------|-------------|-----------|-----|------|--|--|

| Dimension Limits         |             | MIN       | NOM | MAX  |  |  |

| Number of Pins           | N           | 28        |     |      |  |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |  |

| Overall Height           | A           | -         | -   | 2.65 |  |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |  |

| Overall Length           | D           | 17.90 BSC |     |      |  |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |  |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |  |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -   | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

# 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© -2017, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-1639-5