Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

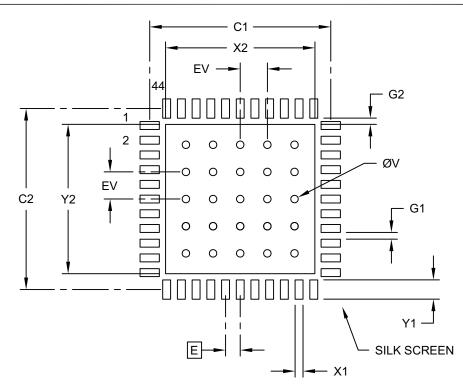

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-1         | R/W-1                                                                                     | R/W-1                                                                                                              | U-1                                                     | U-1                                                       | U-1             | R/W-1           | R/W-1 |

|---------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|-----------------|-----------------|-------|

|               | REN<1:0>                                                                                  | LPBOREN                                                                                                            | _                                                       | _                                                         | _               | PWRTE           | MCLRE |

| bit 7         |                                                                                           |                                                                                                                    |                                                         |                                                           |                 |                 | bit 0 |

|               |                                                                                           |                                                                                                                    |                                                         |                                                           |                 |                 |       |

| Legend:       |                                                                                           |                                                                                                                    |                                                         |                                                           |                 |                 |       |

| R = Readabl   | le bit                                                                                    | W = Writable b                                                                                                     | it                                                      | U = Unimple                                               | mented bit, rea | ad as '1'       |       |

| -n = Value fo | or blank device                                                                           | '1' = Bit is set                                                                                                   |                                                         | '0' = Bit is cle                                          | eared           | x = Bit is unki | nown  |

| bit 7-6       | When enabled<br>11 = Brown-o<br>10 = Brown-o<br>01 = Brown-o                              | Brown-out Res<br>d, Brown-out Res<br>out Reset enable<br>out Reset enable<br>out Reset enable<br>out Reset disable | set Voltage<br>d, SBOREN<br>d while runr<br>d according | (VBOR) is set by<br>I bit is ignored<br>hing, disabled in |                 | REN is ignored  |       |

| bit 5         | 1 = Low-Pov                                                                               | ow-Power BOR I<br>wer Brown-out R<br>wer Brown-out R                                                               | eset is disa                                            |                                                           |                 |                 |       |

| bit 4-2       | Unimplement                                                                               | ted: Read as '1'                                                                                                   |                                                         |                                                           |                 |                 |       |

| bit 1         | PWRTE: Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                 |                                                                                                                    |                                                         |                                                           |                 |                 |       |

| bit 0         | $\frac{\text{If LVP} = 1}{\text{RE3 pin fu}}$ $\frac{\text{If LVP} = 0}{1 = \text{MCLF}}$ | ter Clear (MCLR<br>nction is MCLR<br>pin is MCLR<br>pin function is p                                              |                                                         |                                                           |                 |                 |       |

#### **REGISTER 3-3:** Configuration Word 2L (30 0002h): Supervisor

# 4.3 Clock Source Types

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

A 4x PLL is provided that can be used in conjunction with the external clock. When used with the HFINTOSC the 4x PLL has input frequency limitations.See **Section 4.3.1.4 "4x PLL"** for more details.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce 1, 2, 4, 8, 12, 16, 32, 48 and 64 MHz clock. The frequency can be controlled through the OSCFRQ register (Register 4-5). The Low-Frequency Internal Oscillator (LFINTOSC) generates a fixed 31 kHz frequency.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 4.4 "Clock Switching"** for additional information. The system clock can be made available on the OSC2/CLKOUT pin for any of the modes that do not use the OSC2 pin. The clock out functionality is governed by the CLKOUTEN bit in the CONFIG1H register (Register 3-2). If enabled, the clock out signal is always at a frequency of FOSC/4.

# 4.3.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> and FEXTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> and NDIV<3:0> bits in the OSCCON1 register to switch the system clock source.

See **Section 4.4 "Clock Switching"** for more information.

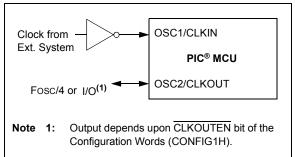

# 4.3.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 4-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, above 8 MHz

- ECM Medium power, 100 kHz-8 MHz

- ECL Low power, below 100 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 4-2: EXTERNAL CLOCK (EC) MODE OPERATION

# 4.3.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification (above 100 kHz - 8 MHz).

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting (above 8 MHz).

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

# 4.3.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 64 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (Fosc = 1 MHz) or '000' (Fosc = 64 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4 "Clock Switching" for more information.

The HFINTOSC frequency can be selected by setting the HFFRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

#### 4.3.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

#### 4.3.2.3 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 4-3).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE **does not affect** the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), WWDT, Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# 4.3.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Windowed Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4, Clock Switching for more information.

## 4.3.2.5 ADCRC

The ADCRC is an oscillator dedicated to the  $ADC^2$  module. The ADCRC oscillator can be manually enabled using the ADOEN bit of the OSCEN register. The ADCRC runs at a fixed frequency of 600 kHz. ADCRC is automatically enabled if it is selected as the clock source for the  $ADC^2$  module.

# 10.5 Register Definitions: Status

| REGISTER '    | 10-2: STATL                                                          | JS: STATUS                          |                  |                      |                               |                   |           |

|---------------|----------------------------------------------------------------------|-------------------------------------|------------------|----------------------|-------------------------------|-------------------|-----------|

| U-0           | R-1/q                                                                | R-1/q                               | R/W-0/u          | R/W-0/u              | R/W-0/u                       | R/W-0/u           | R/W-0/u   |

| _             | TO                                                                   | PD                                  | Ν                | OV                   | Z                             | DC                | С         |

| oit 7         |                                                                      |                                     |                  |                      |                               |                   | bit       |

|               |                                                                      |                                     |                  |                      |                               |                   |           |

| Legend:       |                                                                      |                                     |                  |                      |                               |                   |           |

| R = Readable  |                                                                      | W = Writable                        |                  | •                    | nented bit, read              |                   |           |

| -n = Value at | POR                                                                  | '1' = Bit is se                     | l                | '0' = Bit is cle     | ared                          | x = Bit is unkr   | nown      |

| bit 7         | Unimplomor                                                           | ited: Read as                       | 0'               |                      |                               |                   |           |

| bit 6         | TO: Time-Ou                                                          |                                     | U                |                      |                               |                   |           |

|               |                                                                      |                                     | execution of CI  | LRWDT <b>OF</b> SLEE | P instruction                 |                   |           |

|               |                                                                      | ime-out occurr                      |                  |                      |                               |                   |           |

| bit 5         | PD: Power-D                                                          | own bit                             |                  |                      |                               |                   |           |

|               |                                                                      |                                     |                  | LRWDT instructi      | on                            |                   |           |

|               | •                                                                    | xecution of the                     |                  |                      |                               |                   |           |

| bit 4         | ALU MSb = 1                                                          |                                     | ned arithmetic   | (2's compleme        | ent); indicates if            | the result is ne  | egative,  |

|               | 1 = The resu                                                         |                                     |                  |                      |                               |                   |           |

|               | 0 = The resu                                                         |                                     |                  |                      |                               |                   |           |

| bit 3         |                                                                      |                                     |                  |                      |                               | an overflow of    | the 7-bit |

|               | -                                                                    |                                     |                  | 7) to change st      |                               |                   |           |

|               | 1 = Overflow 0 = No overflow 1 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = |                                     | urrent signed    | arithmetic oper      | ration                        |                   |           |

| bit 2         | Z: Zero bit                                                          |                                     |                  |                      |                               |                   |           |

|               | 1 = The resu                                                         | It of an arithme                    | etic or logic op | eration is zero      |                               |                   |           |

|               |                                                                      |                                     | •                | eration is not z     |                               |                   |           |

| bit 1         | •                                                                    | •                                   |                  |                      | rF instructions) <sup>(</sup> | 1)                |           |

|               |                                                                      | out from the 4th<br>-out from the 4 |                  | of the result of     | ccurred                       |                   |           |

| bit 0         | -                                                                    |                                     |                  | JW, SUBWF instr      | (1,2)                         |                   |           |

|               | •                                                                    | •                                   |                  | bit of the result    | ,                             |                   |           |

|               |                                                                      |                                     |                  | nt bit of the resu   |                               |                   |           |

|               | Borrow, the pola                                                     | arity is reversed                   | d. A subtractio  | n is executed b      | by adding the tw              | vo's complemer    | nt of the |

|               | ond operand.                                                         | <i>.</i>                            |                  |                      |                               |                   | •         |

| 2: For        | Rotate (RRF, RL                                                      | F) Instructions,                    | this bit is load | ded with either      | the high or low-              | -order bit of the | Source    |

# REGISTER 10-2: STATUS: STATUS REGISTER

2: For Rotate (RRF, RLF) instructions, this bit is loaded with either the high or low-order bit of the Source register.

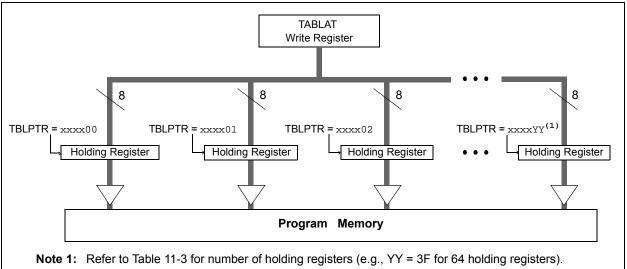

#### FIGURE 11-8: TABLE WRITES TO PROGRAM FLASH MEMORY

# 11.1.6.1 Program Flash Memory Write Sequence

The sequence of events for programming an internal program memory location should be:

- 1. Read appropriate number of bytes into RAM. Refer to Table 11-2 for Write latch size.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- Write the n-byte block into the holding registers with auto-increment. Refer to Table 11-2 for Write latch size.

- 7. Set NVMREG<1:0> bits to point to program memory.

- 8. Clear FREE bit and set WREN bit in NVMCON1 register.

- 9. Disable interrupts.

- 10. Execute the unlock sequence (see Section 11.1.4 "NVM Unlock Sequence").

- 11. WR bit is set in NVMCON1 register.

- 12. The CPU will stall for the duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 11-4.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

#### 13.11.7 IN-CIRCUIT DEBUG (ICD) INTERACTION

The scanner freezes when an ICD halt occurs, and remains frozen until user-mode operation resumes. The debugger may inspect the SCANCON0 and SCANLADR registers to determine the state of the scan.

The ICD interaction with each operating mode is summarized in Table 13-4.

|                     |                                                                                                                                                                                                                                                                                                                                                             | Scanner Operating Mode                                                                                                                                                         |                                                                                                                                                                                                                                                           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICD Halt            | Peek                                                                                                                                                                                                                                                                                                                                                        | Concurrent<br>Triggered                                                                                                                                                        | Burst                                                                                                                                                                                                                                                     |

| External<br>Halt    |                                                                                                                                                                                                                                                                                                                                                             | If external halt is asserted during<br>a scan cycle, the instruction<br>(delayed by scan) may or may<br>not execute before ICD entry,<br>depending on external halt<br>timing. | If external halt is asserted during<br>the BSF (SCANCON.GO), ICD<br>entry occurs, and the burst is<br>delayed until ICD exit.<br>Otherwise, the current NVM-<br>access cycle will complete, and<br>then the scanner will be<br>interrupted for ICD entry. |

|                     | If external halt is asserted during<br>the cycle immediately prior to the<br>scan cycle, both scan and<br>instruction execution happen<br>after the ICD exits.                                                                                                                                                                                              |                                                                                                                                                                                | If external halt is asserted during<br>the burst, the burst is suspended<br>and will resume with ICD exit.                                                                                                                                                |

| PC<br>Breakpoint    | If scanner would peek an<br>instruction that is not executed<br>(because of ICD entry), the peek                                                                                                                                                                                                                                                            | Scan cycle occurs before ICD<br>entry and instruction execution<br>happens after the ICD exits.                                                                                | If PCPB (or single step) is on                                                                                                                                                                                                                            |

| Data<br>Breakpoint  | will occur after ICD exit, when the nstruction executes. The instruction with the dataBP executes and ICD entry occurs immediately after. If scan is requested during that cycle, the scan cycle is postponed until the ICD exits. If a scan cycle is ready after the debug instruction is executed, the scan will read PFM and then the ICD is re-entered. |                                                                                                                                                                                | BSF (SCANCON, GO), the ICD is<br>entered before execution;<br>execution of the burst will occur<br>at ICD exit, and the burst will run<br>to completion.                                                                                                  |

| Single Step         |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                | Note that the burst can be interrupted by an external halt.                                                                                                                                                                                               |

| SWBP and<br>ICDINST |                                                                                                                                                                                                                                                                                                                                                             | If scan would stall a SWBP, the scan cycle occurs and the ICD is entered.                                                                                                      | If SWBP replaces<br>BSF(SCANCON.GO), the ICD will<br>be entered; instruction execution<br>will occur at ICD exit (from<br>ICDINSTR register), and the<br>burst will run to completion.                                                                    |

| <b>TABLE 13-4</b> : | ICD AND SCANNER INTERACTIONS |

|---------------------|------------------------------|

|                     |                              |

# 13.11.8 PERIPHERAL MODULE DISABLE

Both the CRC and scanner module can be disabled individually by setting the CRCMD and SCANMD bits of the PMD0 register (Register 7-1). The SCANMD can be used to enable or disable to the scanner module only if the SCANE bit of Configuration Word 4 is set. If the SCANE bit is cleared, then the scanner module is not available for use and the SCANMD bit is ignored.

|                                      |                                                              |                                                              |                | = = = = = = =    | . (              |                |         |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|----------------|------------------|------------------|----------------|---------|--|--|--|--|

| R/W-0/0                              | R/W-0/0                                                      | R/W-0/0                                                      | U-0            | U-0              | U-0              | U-0            | R/W-0/0 |  |  |  |  |

| SCANIF                               | CRCIF                                                        | NVMIF                                                        | _              | _                | —                | —              | CWG1IF  |  |  |  |  |

| bit 7                                |                                                              |                                                              |                |                  |                  |                | bit 0   |  |  |  |  |

|                                      |                                                              |                                                              |                |                  |                  |                |         |  |  |  |  |

| Legend:                              |                                                              |                                                              |                |                  |                  |                |         |  |  |  |  |

| R = Readable                         | bit                                                          | W = Writable I                                               | bit            | U = Unimpler     | mented bit, read | l as '0'       |         |  |  |  |  |

| -n = Value at I                      | POR                                                          | '1' = Bit is set                                             |                | '0' = Bit is cle | ared             | x = Bit is unk | nown    |  |  |  |  |

|                                      |                                                              |                                                              |                |                  |                  |                |         |  |  |  |  |

| bit 7                                | SCANIF: SC/                                                  | AN Interrupt Fla                                             | ıg bit         |                  |                  |                |         |  |  |  |  |

|                                      | 1 = SCAN inte                                                | errupt has occu                                              | rred (must be  | e cleared in sof | tware)           |                |         |  |  |  |  |

|                                      | 0 = SCAN inte                                                | errupt has not o                                             | occurred or ha | as not been sta  | irted            |                |         |  |  |  |  |

| bit 6                                | CRCIF: CRC                                                   | Interrupt Flag b                                             | bit            |                  |                  |                |         |  |  |  |  |

|                                      | 1 = CRC inter                                                | rrupt has occuri                                             | red (must be   | cleared in softw | vare)            |                |         |  |  |  |  |

|                                      | 0 = CRC inter                                                | rrupt has not oc                                             | curred or has  | s not been star  | ted              |                |         |  |  |  |  |

| bit 5                                | NVMIF: NVM                                                   | Interrupt Flag I                                             | oit            |                  |                  |                |         |  |  |  |  |

|                                      | 1 = NVM interrupt has occurred (must be cleared in software) |                                                              |                |                  |                  |                |         |  |  |  |  |

|                                      | 0 = NVM interrupt has not occurred or has not been started   |                                                              |                |                  |                  |                |         |  |  |  |  |

| bit 4-1                              | Unimplemented: Read as '0'                                   |                                                              |                |                  |                  |                |         |  |  |  |  |

| bit 0 CWG1IF: CWG Interrupt Flag bit |                                                              |                                                              |                |                  |                  |                |         |  |  |  |  |

|                                      |                                                              | 1 = CWG interrupt has occurred (must be cleared in software) |                |                  |                  |                |         |  |  |  |  |

|                                      | 0 = CWG interrupt has not occurred or has not been started   |                                                              |                |                  |                  |                |         |  |  |  |  |

# REGISTER 14-9: PIR7: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 7

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------|-----------|--------|--------|--------|---------|---------|---------|---------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | IPEN   | _      | —      | INT2EDG | INT1EDG | INT0EDG | 170                 |

| PIE0   |          | _         | TMR0IE | IOCIE  | _      | INT2IE  | INT1IE  | INT0IE  | 179                 |

| PIE1   | OSCFIE   | CSWIE     | _      | _      | —      | _       | ADTIE   | ADIE    | 180                 |

| PIE2   | HLVDIE   | ZCDIE     | _      | _      | _      | _       | C2IE    | C1IE    | 181                 |

| PIE3   | RC2IE    | TX2IE     | RC1IE  | TX1IE  | BCL2IE | SSP2IE  | BCL1IE  | SSP1IE  | 182                 |

| PIE4   | —        | —         | TMR6IE | TMR5IE | TMR4IE | TMR3IE  | TMR2IE  | TMR1IE  | 183                 |

| PIE5   | _        | —         | —      | _      | —      | TMR5GIE | TMR3GIE | TMR1GIE | 184                 |

| PIE6   | —        | _         | _      | —      | —      | —       | CCP2IE  | CCP1IE  | 185                 |

| PIE7   | SCANIE   | CRCIE     | NVMIE  | _      | —      | _       | —       | CWG1IE  | 186                 |

| PIR0   |          | _         | TMR0IF | IOCIF  | _      | INT2IF  | INT1IF  | INTOIF  | 171                 |

| PIR1   | OSCFIF   | CSWIF     | _      | _      | —      | _       | ADTIF   | ADIF    | 172                 |

| PIR2   | HLVDIF   | ZCDIF     | _      | —      | —      | —       | C2IF    | C1IF    | 173                 |

| PIR3   | RC2IF    | TX2IF     | RC1IF  | TX1IF  | BCL2IF | SSP2IF  | BCL1IF  | SSP1IF  | 174                 |

| PIR4   |          | —         | TMR6IF | TMR5IF | TMR4IF | TMR3IF  | TMR2IF  | TMR1IF  | 175                 |

| PIR5   | _        | _         | _      | —      | —      | TMR5GIF | TMR3GIF | TMR1GIF | 176                 |

| PIR6   | —        | _         | _      | —      | —      | —       | CCP2IF  | CCP1IF  | 177                 |

| PIR7   | SCANIF   | CRCIF     | NVMIF  | _      | —      | _       | —       | CWG1IF  | 178                 |

| IPR0   | —        | _         | TMR0IP | IOCIP  | —      | INT2IP  | INT1IP  | INT0IP  | 187                 |

| IPR1   | OSCFIP   | CSWIP     | _      | —      | —      | —       | ADTIP   | ADIP    | 188                 |

| IPR2   | HLVDIP   | ZCDIP     | _      | _      | _      | _       | C2IP    | C1IP    | 189                 |

| IPR3   | RC2IP    | TX2IP     | RC1IP  | TX1IP  | BCL2IP | SSP2IP  | BCL1IP  | SSP1IP  | 190                 |

| IPR4   | —        | —         | TMR6IP | TMR5IP | TMR4IP | TMR3IP  | TMR2IP  | TMR1IP  | 191                 |

| IPR5   | —        | _         | —      | —      | —      | TMR5GIP | TMR3GIP | TMR1GIP | 192                 |

| IPR6   | _        | _         | _      | _      | _      | _       | CCP2IP  | CCP1IP  | 193                 |

| IPR7   | SCANIP   | CRCIP     | NVMIP  | —      | _      | _       | —       | CWG1IP  | 194                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Interrupts.

| R/W-0/0         R/W-0/0 <t< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<> |                                                       |         |                   |         |                 |                  |          |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-------------------|---------|-----------------|------------------|----------|---------|

| bit 7     bit       Legend:     W = Writable bit     U = Unimplemented bit, read as '0'       '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0/0                                               | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0 |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | WPUx7                                                 | WPUx6   | WPUx5             | WPUx4   | WPUx3           | WPUx2            | WPUx1    | WPUx0   |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7                                                 |         |                   |         |                 |                  | •        | bit 0   |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |         |                   |         |                 |                  |          |         |

| '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Legend:                                               |         |                   |         |                 |                  |          |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readable                                          | bit     | W = Writable      | bit     | U = Unimplen    | nented bit, read | d as '0' |         |

| -n/n = Value at POR and BOR/Value at all other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                      |         | '0' = Bit is clea | ared    | x = Bit is unkr | nown             |          |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -n/n = Value at POR and BOR/Value at all other Resets |         |                   |         |                 |                  |          |         |

#### REGISTER 15-5: WPUx: WEAK PULL-UP REGISTER

bit 7-0

WPUx<7:0>: Weak Pull-up PORTx Control bits

1 = Weak Pull-up enabled

0 = Weak Pull-up disabled

|      | Dev        | /ice          |       |       |       |       |                      |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|----------------------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

| WPUA | Х          | Х             | WPUA7 | WPUA6 | WPUA5 | WPUA4 | WPUA3                | WPUA2 | WPUA1 | WPUA0 |

| WPUB | Х          | Х             | WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3                | WPUB2 | WPUB1 | WPUB0 |

| WPUC | Х          | Х             | WPUC7 | WPUC6 | WPUC5 | WPUC4 | WPUC3                | WPUC2 | WPUC1 | WPUC0 |

| WPUD | Х          |               | _     | _     | _     | _     | —                    | _     | _     | _     |

|      |            | Х             | WPUD7 | WPUD6 | WPUD5 | WPUD4 | WPUD3                | WPUD2 | WPUD1 | WPUD0 |

| WPUE | Х          |               | _     | _     | _     | _     | WPUE3 <sup>(1)</sup> | _     | _     | _     |

|      |            | Х             | —     | _     | —     | —     | WPUE3 <sup>(1)</sup> | WPUE2 | WPUE1 | WPUE0 |

#### TABLE 15-6: WEAK PULL-UP PORT REGISTERS

Note 1: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

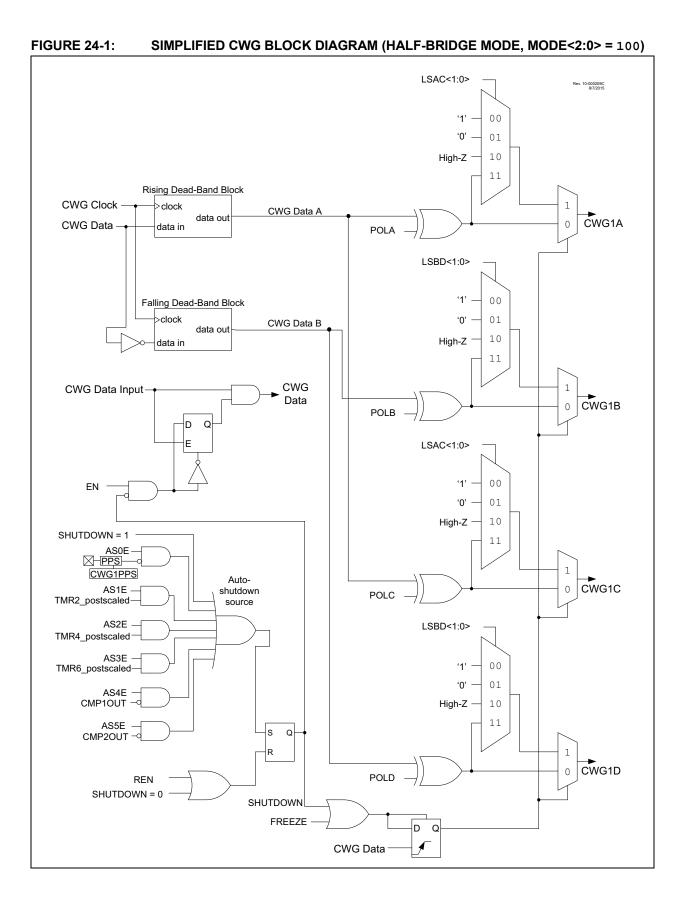

# 24.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWG1A output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWG1B is affected.

The CWG1DBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBR register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 24-1) is set. Refer to Figure 24-12 for an example.

# 24.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWG1B output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWG1D is affected.

The CWG1DBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBF register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 24-1) is set. Refer to Figure 24-13 for an example.

# 27.5.1.5 Synchronous Master Reception

Data is received at the RXx/DTx pin. The RXx/DTx pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RXx/DTx pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RCxIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

## 27.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TXx/CKx pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

# 27.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

## 27.5.1.8 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

# 27.5.1.9 Synchronous Master Reception Setup:

- Initialize the SPxBRGH:SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RXx pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCxIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

|                    |      | Bit Clear Conditions                                  | Value after Trigger completion                                                           |                                                             | Threshold Operations                                                                                                                                                                   |                        |                        | Value at ADTIF interrupt |                          |       |

|--------------------|------|-------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|--------------------------|-------|

| Mode               | ADMD | ADACC and ADCNT                                       | ADACC                                                                                    | ADCNT                                                       | Retrigger                                                                                                                                                                              | Threshold<br>Test      | Interrupt              | ADAOV                    | ADFLTR                   | ADCNT |

| Basic              | 0    | ADACLR = 1                                            | Unchanged                                                                                | Unchanged                                                   | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | N/A                      | N/A                      | count |

| Accumulate         | 1    | ADACLR = 1                                            | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Average            | 2    | ADACLR = 1 or<br>ADCNT>=ADRPT at ADGO<br>or retrigger | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Burst<br>Average   | 3    | ADACLR = 1 or ADGO set or<br>retrigger                | Each repetition: same as<br>Average<br>End with sum of all<br>samples                    | Each repetition: same as<br>Average<br>End with ADCNT=ADRPT | Repeat while<br>ADCNT <adrpt< td=""><td>lf<br/>ADCNT&gt;=<br/>ADRPT</td><td>If thresh-<br/>old=true</td><td>ADACC Overflow</td><td>ADACC/2<sup>ADCRS</sup></td><td>ADRPT</td></adrpt<> | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | ADRPT |

| Low-pass<br>Filter | 4    | ADACLR = 1                                            | S+ADACC-ADACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ADACC-ADACC/<br>2 <sup>ADCRS</sup> | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | Filtered Value           | count |

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = ADREV and S2 = ADRES.

TABLE 35-2: INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | Civalaa    | 16-Bit Instruction Wo |      |      | /ord | Status          | Nataa      |

|-----------------------|---------------------------------|------------------------------------------|------------|-----------------------|------|------|------|-----------------|------------|

|                       |                                 | Description                              | Cycles     | MSb                   |      |      | LSb  | Affected        | Notes      |

| BYTE-ORI              | ENTED (                         | OPERATIONS                               |            |                       |      |      |      |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                  | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and CARRY bit to f              | 1          | 0010                  | 00da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                  | 01da | ffff | ffff | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                  | 101a | ffff | ffff | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                  | 11da | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110                  | 001a | ffff | ffff | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110                  | 010a | ffff | ffff | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110                  | 000a | ffff | ffff | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1          | 0000                  | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                  | 11da | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                  | 11da | ffff | ffff | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          | 0010                  | 10da | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                  | 11da | ffff | ffff | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                  | 10da | ffff | ffff | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                  | 00da | ffff | ffff | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101                  | 00da | ffff | ffff | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                  | ffff | ffff | ffff | None            |            |

|                       | 3/ U                            | f <sub>d</sub> (destination) 2nd word    |            | 1111                  | ffff | ffff | ffff |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110                  | 111a | ffff | ffff | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000                  | 001a | ffff | ffff | None            | 1, 2       |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110                  | 110a | ffff | ffff | C, DC, Z, OV, N | ,          |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                  | 01da | ffff | ffff | C, Z, N         | 1, 2       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                  | 01da | ffff | ffff | Z, N            | •, =       |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                  | 00da | ffff | ffff | C, Z, N         |            |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                  | 00da | ffff | ffff | Z, N            |            |

| SETF                  | f, a                            | Set f                                    | 1          | 0110                  | 100a | ffff | ffff | None            | 1, 2       |

| SUBFWB                | f, d, a                         | Subtract f from WREG with<br>borrow      | 1          | 0101                  | 01da | ffff | ffff | C, DC, Z, OV, N | ,          |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                  | 11da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                | 1          | 0101                  | 10da | ffff | ffff | C, DC, Z, OV, N | ,          |

|                       |                                 | borrow                                   |            |                       |      |      |      |                 |            |

| SWAPF                 | f, d, a                         | Swap nibbles in f                        | 1          | 0011                  | 10da | ffff | ffff | None            | 4          |

| TSTFSZ                | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110                  | 011a | ffff | ffff | None            | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                  | 10da | ffff | ffff | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

# 35.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                    | ADD liter                         | al to W         |      |          |  |  |

|----------------------------------------------------------|-----------------------------------|-----------------|------|----------|--|--|

| Syntax:                                                  | ADDLW                             | k               |      |          |  |  |

| Operands:                                                | $0 \le k \le 255$                 |                 |      |          |  |  |

| Operation:                                               | (W) + k $\rightarrow$             | W               |      |          |  |  |

| Status Affected:                                         | N, OV, C, E                       | DC, Z           |      |          |  |  |

| Encoding:                                                | 0000                              | 1111            | kkkk | kkkk     |  |  |

| Description:                                             | The conten<br>8-bit literal<br>W. |                 |      |          |  |  |

| Words:                                                   | 1                                 |                 |      |          |  |  |

| Cycles:                                                  | 1                                 | 1               |      |          |  |  |