#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# 3.2 Register Definitions: Configuration Words

| REGISTER 3-1                                 | : Config | guration word | 12 (30 000 | Jun): Oscillat   | ors             |                   |       |

|----------------------------------------------|----------|---------------|------------|------------------|-----------------|-------------------|-------|

| U-1                                          | R/W-1    | R/W-1         | R/W-1      | U-1              | R/W-1           | R/W-1             | R/W-1 |

| - RSTOSC<2:0> - FEXTOSC<2:0                  |          |               |            |                  |                 |                   |       |

| bit 7                                        |          |               |            |                  |                 |                   | bit 0 |

|                                              |          |               |            |                  |                 |                   |       |

| Legend:                                      |          |               |            |                  |                 |                   |       |

| R = Readable bi                              | t        | W = Writable  | bit        | U = Unimple      | mented bit, rea | ad as '1'         |       |

| -n = Value for blank device '1' = Bit is set |          |               |            | '0' = Bit is cle | eared           | x = Bit is unknow | /n    |

|                                              |          |               |            |                  |                 |                   |       |

#### **REGISTER 3-1:** Configuration Word 1L (30 0000h): Oscillators

bit 7 Unimplemented: Read as '1'

#### RSTOSC<2:0>: Power-up Default Value for COSC bits bit 6-4 This value is the Reset default value for COSC and selects the oscillator first used by user software. Refer to COSC operation. 111 = EXTOSC operating per FEXTOSC bits (device manufacturing default) 110 = HFINTOSC with HFFRQ = 4 MHz (Register 4-5) and CDIV = 4:1 (Register 4-2) 101 = LFINTOSC 100 = SOSC 011 = Reserved 010 = EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits 001 = Reserved 000 = HFINTOSC with HFFRQ = 64 MHz (Register 4-5) and CDIV = 1:1 (Register 4-2). Resets COSC/NOSC to 3'b110. bit 3 Unimplemented: Read as '1' bit 2-0 FEXTOSC<2:0>: FEXTOSC External Oscillator Mode Selection bits 111 = EC (external clock) above 8 MHz; PFM set to high power (device manufacturing default) 110 = EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power 101 = EC (external clock) below 500 kHz; PFM set to low power 100 = Oscillator not enabled 011 = Reserved (do not use) 010 = HS (crystal oscillator) above 8 MHz; PFM set to high power

- 001 = XT (crystal oscillator) above 500 kHz, below 8 MHz; PFM set to medium power

- 000 = LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

|                                                                     | • • ••g                                                      |                            |                |                  |                  |                |          |  |

|---------------------------------------------------------------------|--------------------------------------------------------------|----------------------------|----------------|------------------|------------------|----------------|----------|--|

| U-1                                                                 | U-1                                                          | R/W-1                      | U-1            | R/W-1            | U-1              | U-1            | R/W-1    |  |

| _                                                                   | _                                                            | FCMEN                      | _              | CSWEN            |                  | _              | CLKOUTEN |  |

| bit 7                                                               | ·                                                            |                            |                |                  | •                |                | bit 0    |  |

|                                                                     |                                                              |                            |                |                  |                  |                |          |  |

| Legend:                                                             |                                                              |                            |                |                  |                  |                |          |  |

| R = Readabl                                                         | le bit                                                       | W = Writable               | bit            | U = Unimple      | mented bit, read | d as '1'       |          |  |

| -n = Value fo                                                       | or blank device                                              | '1' = Bit is set           |                | '0' = Bit is cle | eared            | x = Bit is unk | nown     |  |

|                                                                     |                                                              |                            |                |                  |                  |                |          |  |

| bit 7-6                                                             | Unimplemen                                                   | ted: Read as '1            | 3              |                  |                  |                |          |  |

| bit 5                                                               |                                                              | Safe Clock Mor             | nitor Enable b | it               |                  |                |          |  |

|                                                                     | 1 = FSCM tin<br>0 = FSCM tin                                 |                            |                |                  |                  |                |          |  |

| bit 4                                                               | Unimplemen                                                   | ted: Read as '1            | ,              |                  |                  |                |          |  |

| bit 3                                                               | CSWEN: Cloo                                                  | ck Switch Enabl            | e bit          |                  |                  |                |          |  |

|                                                                     |                                                              | NOSC and ND                |                |                  |                  |                |          |  |

| <b>h</b> #0.4                                                       |                                                              | C and NDIV bit             |                | nanged by use    | er soπware       |                |          |  |

| bit 2-1                                                             | Unimplemen                                                   | Unimplemented: Read as '1' |                |                  |                  |                |          |  |

| bit 0                                                               | CLKOUTEN: Clock Out Enable bit                               |                            |                |                  |                  |                |          |  |

| If FEXTOSC = HS. XT. LP. then this bit is ignored<br>Otherwise:     |                                                              |                            |                |                  |                  |                |          |  |

| 1 = CLKOUT function is disabled; I/O or oscillator function on OSC2 |                                                              |                            |                |                  |                  |                |          |  |

|                                                                     | 0 = CLKOUT function is enabled; FOSC/4 clock appears at OSC2 |                            |                |                  |                  |                |          |  |

|                                                                     |                                                              |                            |                |                  |                  |                |          |  |

#### REGISTER 3-2: Configuration Word 1H (30 0001h): Oscillators

# 3.6 Device ID and Revision ID

The 16-bit device ID word is located at 3F FFFEh and the 16-bit revision ID is located at 3F FFFCh. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. Refer to **11.0** "Nonvolatile Memory (NVM) Control" for more information on accessing these locations.

# 3.7 Register Definitions: Device and Revision

| REGISTER 3-12: | DEVICE ID: DEVICE ID REGISTER |

|----------------|-------------------------------|

|----------------|-------------------------------|

| R      | R     | R     | R     | R     | R     | R    | R     |

|--------|-------|-------|-------|-------|-------|------|-------|

| DEV15  | DEV14 | DEV13 | DEV12 | DEV11 | DEV10 | DEV9 | DEV8  |

| bit 15 |       |       |       |       |       |      | bit 8 |

|        |       |       |       |       |       |      |       |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

### Legend:

| R = Readable bit | '1' = Bit is set | 0' = Bit is cleared | x = Bit is unknown |

|------------------|------------------|---------------------|--------------------|

|------------------|------------------|---------------------|--------------------|

bit 15-0 DEV<15:0>: Device ID bits

| Device       | Device ID |

|--------------|-----------|

| PIC18F26K40  | 6980h     |

| PIC18F45K40  | 6940h     |

| PIC18F46K40  | 6920h     |

| PIC18LF26K40 | 6A60h     |

| PIC18LF45K40 | 6A20h     |

| PIC18LF46K40 | 6A00h     |

| U-0                             | R/W-0/0    | R/W-0/0           | R/W-0/0 | R/W-0/0       | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|---------------------------------|------------|-------------------|---------|---------------|------------------|------------------|-------------|

|                                 | TMR6MD     | TMR5MD            | TMR4MD  | TMR3MD        | TMR2MD           | TMR1MD           | TMR0MD      |

| bit 7                           |            |                   |         |               |                  |                  | bit         |

| Legend:                         |            |                   |         |               |                  |                  |             |

| R = Reada                       | hla hit    | W = Writable      | bit     | II – Unimplom | nented bit, read |                  |             |

|                                 |            | x = Bit is unkr   |         | •             | -                | R/Value at all c | thar Dagata |

| u = Bit is uı<br>'1' = Bit is s | •          |                   |         |               |                  |                  | iner Reseis |

|                                 | Sel        | '0' = Bit is clea | areu    | q = value dep | ends on condit   | 1011             |             |

| bit 7                           | Unimplemer | ted: Read as '    | )'      |               |                  |                  |             |

| bit 6                           | TMR6MD: Di | sable Timer TM    | IR6 bit |               |                  |                  |             |

|                                 | 1 = TMR6 m | nodule disabled   |         |               |                  |                  |             |

|                                 | 0 = TMR6 m | nodule enabled    |         |               |                  |                  |             |

| bit 5                           | TMR5MD: Di | sable Timer TM    | IR5 bit |               |                  |                  |             |

|                                 | 1 = TMR5 m | nodule disabled   |         |               |                  |                  |             |

|                                 | 0 = TMR5 m | nodule enabled    |         |               |                  |                  |             |

| bit 4                           | TMR4MD: Di | sable Timer TM    | IR4 bit |               |                  |                  |             |

|                                 | 1 = TMR4 m | nodule disabled   |         |               |                  |                  |             |

|                                 | 0 = TMR4 m | nodule enabled    |         |               |                  |                  |             |

| bit 3                           | TMR3MD: Di | sable Timer TM    | IR3 bit |               |                  |                  |             |

|                                 | -          | nodule disabled   |         |               |                  |                  |             |

|                                 | 0 = TMR3 n | nodule enabled    |         |               |                  |                  |             |

| bit 2                           | TMR2MD: Di | sable Timer TM    | IR2 bit |               |                  |                  |             |

|                                 |            | odule disabled    |         |               |                  |                  |             |

| L:1. A                          |            | odule enabled     |         |               |                  |                  |             |

| bit 1                           |            | sable Timer TM    | IR'I DI |               |                  |                  |             |

|                                 |            | odule disabled    |         |               |                  |                  |             |

| bit 0                           |            | isable Timer TM   | IR0 bit |               |                  |                  |             |

|                                 |            | odule disabled    |         |               |                  |                  |             |

|                                 |            | odule enabled     |         |               |                  |                  |             |

### REGISTER 7-2: PMD1: PMD CONTROL REGISTER 1

| Address | Name                   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2       | Bit 1   | Bit 0   | <u>Value on</u><br>POR, BOR |

|---------|------------------------|---------|---------|---------|---------|---------|-------------|---------|---------|-----------------------------|

| F26h    | ANSELD <sup>(2)</sup>  | ANSELD7 | ANSELD6 | ANSELD5 | ANSELD4 | ANSELD3 | ANSELD2     | ANSELD1 | ANSELD0 | 11111111                    |

| F25h    | WPUD <sup>(2)</sup>    | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3   | WPUD2       | WPUD1   | WPUD0   | 00000000                    |

| F24h    | ODCOND <sup>(2)</sup>  | ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3   | ODCD2       | ODCD1   | ODCD0   | 00000000                    |

| F23h    | SLRCOND <sup>(2)</sup> | SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2       | SLRD1   | SLRD0   | 11111111                    |

| F22h    | INLVLD <sup>(2)</sup>  | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2     | INLVLD1 | INLVLD0 | 10000000                    |

| F21h    | ANSELC                 | ANSELC7 | ANSELC6 | ANSELC5 | ANSELC4 | ANSELC3 | ANSELC2     | ANSELC1 | ANSELC0 | 11111111                    |

| F20h    | WPUC                   | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2       | WPUC1   | WPUC0   | 00000000                    |

| F1Fh    | ODCONC                 | ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3   | ODCC2       | ODCC1   | ODCC0   | 00000000                    |

| F1Eh    | SLRCONC                | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2       | SLRC1   | SLRC0   | 11111111                    |

| F1Dh    | INLVLC                 | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2     | INLVLC1 | INLVLC0 | 11111111                    |

| F1Ch    | IOCCP                  | IOCCP7  | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2      | IOCCP1  | IOCCP0  | 00000000                    |

| F1Bh    | IOCCN                  | IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2      | IOCCN1  | IOCCN0  | 00000000                    |

| F1Ah    | IOCCF                  | IOCCF7  | IOCCF6  | IOCCF5  | IOCCF4  | IOCCF3  | IOCCF2      | IOCCF1  | IOCCF0  | 00000000                    |

| F19h    | ANSELB                 | ANSELB7 | ANSELB6 | ANSELB5 | ANSELB4 | ANSELB3 | ANSELB2     | ANSELB1 | ANSELB0 | 11111111                    |

| F18h    | WPUB                   | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2       | WPUB1   | WPUB0   | 00000000                    |

| F17h    | ODCONB                 | ODCB7   | ODCB6   | ODCB5   | ODCB4   | ODCB3   | ODCB2       | ODCB1   | ODCB0   | 00000000                    |

| F16h    | SLRCONB                | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2       | SLRB1   | SLRB0   | 11111111                    |

| F15h    | INLVLB                 | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2     | INLVLB1 | INLVLB0 | 11111111                    |

| F14h    | IOCBP                  | IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2      | IOCBP1  | IOCBP0  | 00000000                    |

| F13h    | IOCBN                  | IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2      | IOCBN1  | IOCBN0  | 00000000                    |

| F12h    | IOCBF                  | IOCBF7  | IOCBF6  | IOCBF5  | IOCBF4  | IOCBF3  | IOCBF2      | IOCBF1  | IOCBF0  | 00000000                    |

| F11h    | ANSELA                 | ANSELA7 | ANSELA6 | ANSELA5 | ANSELA4 | ANSELA3 | ANSELA2     | ANSELA1 | ANSELA0 | 11111111                    |

| F10h    | WPUA                   | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2       | WPUA1   | WPUA0   | 00000000                    |

| F0Fh    | ODCONA                 | ODCA7   | ODCA6   | ODCA5   | ODCA4   | ODCA3   | ODCA2       | ODCA1   | ODCA0   | 00000000                    |

| F0Eh    | SLRCONA                | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2       | SLRA1   | SLRA0   | 11111111                    |

| F0Dh    | INLVLA                 | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2     | INLVLA1 | INLVLA0 | 11111111                    |

| F0Ch    | IOCAP                  | IOCAP7  | IOCAP6  | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2      | IOCAP1  | IOCAP0  | 00000000                    |

| F0Bh    | IOCAN                  | IOCAN7  | IOCAN6  | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2      | IOCAN1  | IOCAN0  | 00000000                    |

| F0Ah    | IOCAF                  | IOCAF7  | IOCAF6  | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2      | IOCAF1  | IOCAF0  | 00000000                    |

| F09h    | RE2PPS <sup>(2)</sup>  | —       | —       | —       |         |         | RE2PPS<4:0> |         |         | 00000                       |

| F08h    | RE1PPS <sup>(2)</sup>  | —       | —       | —       |         |         | RE1PPS<4:0> |         |         | 00000                       |

| F07h    | RE0PPS <sup>(2)</sup>  | _       | —       | —       |         |         | RE0PPS<4:0> |         |         | 00000                       |

| F06h    | RD7PPS <sup>(2)</sup>  | —       | —       | —       |         |         | RD7PPS<4:0> |         |         | 00000                       |

| F05h    | RD6PPS <sup>(2)</sup>  | —       | —       | —       |         |         | RD6PPS<4:0> |         |         | 00000                       |

| F04h    | RD5PPS <sup>(2)</sup>  | —       | —       | —       |         |         | RD5PPS<4:0> |         |         | 00000                       |

| F03h    | RD4PPS <sup>(2)</sup>  | _       |         | _       |         |         | RD4PPS<4:0> |         |         | 00000                       |

| F02h    | RD3PPS <sup>(2)</sup>  | —       | —       | -       |         |         | RD3PPS<4:0> |         |         | 00000                       |

| F01h    | RD2PPS <sup>(2)</sup>  | —       | —       | —       |         |         | RD2PPS<4:0> |         |         | 00000                       |

| F00h    | RD1PPS <sup>(2)</sup>  | _       | —       | _       |         |         | RD1PPS<4:0> |         |         | 00000                       |

# TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40 devices.

| Address | Name                   | Bit 7   | Bit 6   | Bit 5     | Bit 4       | Bit 3       | Bit 2       | Bit 1  | Bit 0    | <u>Value on</u><br>POR, BOR |

|---------|------------------------|---------|---------|-----------|-------------|-------------|-------------|--------|----------|-----------------------------|

| EFFh    | RD0PPS <sup>(2)</sup>  | _       | —       | —         | RD0PPS<4:0> |             |             |        |          | 00000                       |

| EFEh    | RC7PPS                 | _       | _       | _         |             | RC7PPS<4:0> |             |        |          |                             |

| EFDh    | RC6PPS                 | _       | _       | _         |             |             | RC6PPS<4:0> |        |          | 00000                       |

| EFCh    | RC5PPS                 | _       | _       | _         |             |             | RC5PPS<4:0> |        |          | 00000                       |

| EFBh    | RC4PPS                 | _       | _       | _         |             |             | RC4PPS<4:0> |        |          | 00000                       |

| EFAh    | RC3PPS                 | _       | _       | _         |             |             | RC3PPS<4:0> |        |          | 00000                       |

| EF9h    | RC2PPS                 | _       | _       | _         |             |             | RC2PPS<4:0> |        |          | 00000                       |

| EF8h    | RC1PPS                 | _       | —       | —         |             |             | RC1PPS<4:0> |        |          | 00000                       |

| EF7h    | RC0PPS                 | _       | —       | _         |             |             | RC0PPS<4:0> | •      |          | 00000                       |

| EF6h    | RB7PPS                 | _       | —       | —         |             |             | RB7PPS<4:0> |        |          | 00000                       |

| EF5h    | RB6PPS                 | _       | —       | _         |             |             | RB6PPS<4:0> |        |          | 00000                       |

| EF4h    | RB5PPS                 | _       | —       | _         |             |             | RB5PPS<4:0> |        |          | 00000                       |

| EF3h    | RB4PPS                 | _       | —       | _         |             |             | RB4PPS<4:0> |        |          | 00000                       |

| EF2h    | RB3PPS                 | _       | —       | _         |             |             | RB3PPS<4:0> |        |          | 00000                       |

| EF1h    | RB2PPS                 | _       | —       | _         |             |             | RB2PPS<4:0> |        |          | 00000                       |

| EF0h    | RB1PPS                 | _       | —       | —         |             |             | RB1PPS<4:0> |        |          | 00000                       |

| EEFh    | RB0PPS                 | _       | —       | _         |             |             | RB0PPS<4:0> |        |          | 00000                       |

| EEEh    | RA7PPS                 | _       | —       | _         |             |             | RA7PPS<4:0> |        |          | 00000                       |

| EEDh    | RA6PPS                 | _       | —       | _         |             |             | RA6PPS<4:0> |        |          | 00000                       |

| EECh    | RA5PPS                 | _       | —       | —         |             |             | RA5PPS<4:0> |        |          | 00000                       |

| EEBh    | RA4PPS                 | _       | —       | _         |             |             | RA4PPS<4:0> |        |          | 00000                       |

| EEAh    | RA3PPS                 | _       | —       | —         |             |             | RA3PPS<4:0> |        |          | 00000                       |

| EE9h    | RA2PPS                 | _       | —       | —         |             |             | RA2PPS<4:0> |        |          | 00000                       |

| EE8h    | RA1PPS                 | _       | —       | —         |             |             | RA1PPS<4:0> |        |          | 00000                       |

| EE7h    | RA0PPS                 | _       | —       | _         |             |             | RA0PPS<4:0> |        |          | 00000                       |

| EE6h    | PMD5                   | _       | —       | —         | —           | —           | —           | —      | DSMMD    | 0                           |

| EE5h    | PMD4                   | UART2MD | UART1MD | MSSP2MD   | MSSP1MD     | —           | —           | —      | CWG1MD   | 00000                       |

| EE4h    | PMD3                   | _       | —       | —         | —           | PWM4MD      | PWM3MD      | CCP2MD | CCP1MD   | 0000                        |

| EE3h    | PMD2                   | _       | DACMD   | ADCMD     | _           | —           | CMP2MD      | CMP1MD | ZCDMD    | -00000                      |

| EE2h    | PMD1                   | _       | TMR6MD  | TMR5MD    | TMR4MD      | TMR3MD      | TMR2MD      | TMR1MD | TMR0MD   | -0000000                    |

| EE1h    | PMD0                   | SYSCMD  | FVRMD   | HLVDMD    | CRCMD       | SCANMD      | NVMMD       | CLKRMD | IOCMD    | 00x00000                    |

| EE0h    | BORCON                 | SBOREN  | —       | —         | —           | —           | —           | —      | BORRDY   | 1q                          |

| EDFh    | VREGCON <sup>(1)</sup> | -       | —       | _         | _           | —           | —           | VREGPM | Reserved | 01                          |

| EDEh    | OSCFRQ                 | _       | —       | —         | —           |             | HFFR        | Q<3:0> |          | 1111                        |

| EDDh    | OSCTUNE                | _       | —       |           |             | HFTU        | JN<5:0>     |        |          | 100000                      |

| EDCh    | OSCEN                  | EXTOEN  | HFOEN   | MFOEN     | LFOEN       | SOSCEN      | ADOEN       |        | —        | 000000                      |

| EDBh    | OSCSTAT                | EXTOR   | HFOR    | MFOR      | LFOR        | SOR         | ADOR        |        | PLLR     | dddddd-d                    |

| EDAh    | OSCCON3                | CSWHOLD | SOSCPWR | —         | ORDY        | NOSCR       | _           | —      | _        | 00-00                       |

| ED9h    | OSCCON2                | _       |         | COSC<2:0> | 1           |             | CDIV        | /<3:0> |          | -ddddddd                    |

#### TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F26/45/46K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F26K40 (28-pin variants).

3: Not available on PIC18(L)F45K40 devices.

#### 13.11.7 IN-CIRCUIT DEBUG (ICD) INTERACTION

The scanner freezes when an ICD halt occurs, and remains frozen until user-mode operation resumes. The debugger may inspect the SCANCON0 and SCANLADR registers to determine the state of the scan.

The ICD interaction with each operating mode is summarized in Table 13-4.

|                     |                                                                                                                                                                | Scanner Operating Mode                                                                                                                                                         |                                                                                                                                                                                                                                                           |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ICD Halt            | Peek                                                                                                                                                           | Concurrent<br>Triggered                                                                                                                                                        | Burst                                                                                                                                                                                                                                                     |  |  |

| External<br>Halt    |                                                                                                                                                                | If external halt is asserted during<br>a scan cycle, the instruction<br>(delayed by scan) may or may<br>not execute before ICD entry,<br>depending on external halt<br>timing. | If external halt is asserted during<br>the BSF (SCANCON.GO), ICD<br>entry occurs, and the burst is<br>delayed until ICD exit.<br>Otherwise, the current NVM-<br>access cycle will complete, and<br>then the scanner will be<br>interrupted for ICD entry. |  |  |

|                     | If external halt is asserted during<br>the cycle immediately prior to the<br>scan cycle, both scan and<br>instruction execution happen<br>after the ICD exits. |                                                                                                                                                                                | If external halt is asserted during<br>the burst, the burst is suspended<br>and will resume with ICD exit.                                                                                                                                                |  |  |

| PC<br>Breakpoint    | If scanner would peek an<br>instruction that is not executed<br>(because of ICD entry), the peek                                                               | nstruction that is not executed entry and instruction execution                                                                                                                |                                                                                                                                                                                                                                                           |  |  |

| Data<br>Breakpoint  | will occur after ICD exit, when the instruction executes.                                                                                                      |                                                                                                                                                                                |                                                                                                                                                                                                                                                           |  |  |

| Single Step         |                                                                                                                                                                | If a scan cycle is ready after the debug instruction is executed, the scan will read PFM and then the ICD is re-entered.                                                       | Note that the burst can be interrupted by an external halt.                                                                                                                                                                                               |  |  |

| SWBP and<br>ICDINST |                                                                                                                                                                | If scan would stall a SWBP, the scan cycle occurs and the ICD is entered.                                                                                                      | If SWBP replaces<br>BSF(SCANCON.GO), the ICD will<br>be entered; instruction execution<br>will occur at ICD exit (from<br>ICDINSTR register), and the<br>burst will run to completion.                                                                    |  |  |

| <b>TABLE 13-4</b> : | ICD AND SCANNER INTERACTIONS |

|---------------------|------------------------------|

|                     |                              |

# 13.11.8 PERIPHERAL MODULE DISABLE

Both the CRC and scanner module can be disabled individually by setting the CRCMD and SCANMD bits of the PMD0 register (Register 7-1). The SCANMD can be used to enable or disable to the scanner module only if the SCANE bit of Configuration Word 4 is set. If the SCANE bit is cleared, then the scanner module is not available for use and the SCANMD bit is ignored.

#### REGISTER 18-3: TMR0L: TIMER0 COUNT REGISTER

|                  | ••••••• |                   |         |                |                  |                  |              |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|                  |         |                   | TMR     | 0<7:0>         |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable b   | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is uncha | inged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 TMR0<7:0>:TMR0 Counter bits <7:0>

#### REGISTER 18-4: TMR0H: TIMER0 PERIOD REGISTER

| R/W-1/1    | /W-1/1 R/W-1/1 R/W-1/1 R/W-1/1 R/W-1/1 R/W-1/1 |  |  |  | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |

|------------|------------------------------------------------|--|--|--|---------|---------|---------|--|--|--|

| TMR0<15:8> |                                                |  |  |  |         |         |         |  |  |  |

| bit 7      |                                                |  |  |  |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 When T016BIT = 0 PR0<7:0>:TMR0 Period Register Bits <7:0> When T016BIT = 1 TMR0<15:8>: TMR0 Counter bits <15:8>

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name            | Bit 7      | Bit 6     | Bit 5  | Bit 4   | Bit 3                        | Bit 2     | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------|------------|-----------|--------|---------|------------------------------|-----------|---------|---------|---------------------|

| TMR0L           |            | •         |        | TMR     | )<7:0>                       | •         | •       |         | 226                 |

| TMR0H           | TMR0<15:8> |           |        |         |                              |           |         |         |                     |

| T0CON0          | T0EN       | —         | TOOUT  | T016BIT |                              | TOOUTPS   | <3:0>   |         | 224                 |

| T0CON1          |            | T0CS<2:0> |        | TOASYNC |                              | T0CKPS<   | :3:0>   |         | 225                 |

| <b>T0CKIPPS</b> | —          | —         | —      |         | TOCK                         | IPPS<4:0> |         |         | 216                 |

| TMR0PPS         | _          | —         | _      |         | TMRC                         | )PPS<4:0> |         |         | 216                 |

| INTCON          | GIE/GIEH   | PEIE/GIEL | IPEN   | —       | —                            | INT2EDG   | INT1EDG | INT0EDG | 170                 |

| PIR0            | _          | —         | TMR0IF | IOCIF   | —                            | INT2IF    | INT1IF  | INT0IF  | 171                 |

| PIE0            | —          | —         | TMR0IE | IOCIE   | IOCIE — INT2IE INT1IE INT0IE |           |         |         | 179                 |

| IPR0            | —          | —         | TMR0IP | IOCIP   | —                            | INT2IP    | INT1IP  | INT0IP  | 187                 |

| PMD1            | _          | TMR6MD    | TMR5MD | TMR4MD  | TMR3MD                       | TMR2MD    | TMR1MD  | TMR0MD  | 69                  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

© 2015-2017 Microchip Technology Inc.

| Name     | Bit 7    | Bit 6     | Bit 5       | Bit 4         | Bit 3          | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|-------------|---------------|----------------|------------|---------|---------|---------------------|

| CCPTMRS  | P4TSE    | L<1:0>    | P3TSE       | L<1:0>        | C2TSE          | L<1:0>     | C1TSE   | EL<1:0> | 286                 |

| PWM3CON  | EN       | _         | OUT         | POL           | _              | —          | —       | —       | 285                 |

| PWM3DCH  |          |           |             | DC<7          | :0>            |            |         |         | 287                 |

| PWM3DCL  | DC<      | 9:8>>     | _           | —             | —              | —          | —       | —       | 287                 |

| PWM4CON  | EN       | _         | OUT         | POL           | _              | —          | _       | —       | 285                 |

| PWM4DCH  |          |           |             | DC<7          | :0>            |            |         |         | 287                 |

| PWM4DCL  | DC<      | <9:8>     | _           | _             | —              | —          | _       | —       | 287                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN        | _             | —              | INT2EDG    | INT1EDG | INT0EDG | 170                 |

| PIE4     | _        | _         | TMR6IE      | TMR5IE        | TMR4IE         | TMR3IE     | TMR2IE  | TMR1IE  | 183                 |

| PIR4     | _        | _         | TMR6IF      | TMR5IF        | TMR4IF         | TMR3IF     | TMR2IF  | TMR1IF  | 175                 |

| IPR4     | _        | _         | TMR6IP      | TMR5IP        | TMR4IP         | TMR3IP     | TMR2IP  | TMR1IP  | 191                 |

| RxyPPS   | _        | _         | _           |               | R              | xyPPS<4:0> |         |         | 218                 |

| TMR2     |          |           |             | TMR2<         | 7:0>           |            |         |         | 244*                |

| PR2      |          |           |             | PR2<7         | <b>':0&gt;</b> |            |         |         | 244*                |

| T2CON    | T2ON     |           | T2CKPS<2:0> |               |                | T2OUTF     | PS<3:0> |         | 262                 |

| T2HLT    | T2PSYNC  | T2CPOL    | T2CSYNC     |               | T:             | 2MODE<4:0> | •       |         | 263                 |

| T2CLKCON | _        | _         | _           | _             |                | T2CS       | <3:0>   |         | 264                 |

| T2RST    |          | _         | _           | — T2RSEL<3:0> |                |            |         |         |                     |

| PMD3     | _        | _         | _           | _             | PWM4MD         | PWM3MD     | CCP2MD  | CCP1MD  | 71                  |

## TABLE 22-4: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM. \* Not a physical location.

#### EQUATION 23-2: R-C CALCULATIONS

- VPEAK = External voltage source peak voltage

- f = External voltage source frequency

- C = Series capacitor

- R = Series resistor

- $V_{\rm C}$  = Peak capacitor voltage

- $\Phi$  = Capacitor induced zero crossing phase advance in radians

- $T_\Phi\,$  = Time ZC event occurs before actual zero crossing

$$Z = \frac{VPEAK}{3 \times 10^{-4}}$$

$$XC = \frac{1}{2\pi fC}$$

$$R = \sqrt{Z^2 - Xc^2}$$

$$VC = XC(3 \times 10^{-4})$$

$$\Phi = Tan^{-1}\left(\frac{XC}{R}\right)$$

$$T\Phi = \frac{\Phi}{2\pi f}$$

# EXAMPLE 23-1: R-C CALCULATIONS

VRMS = 120

VPEAK = VRMS \*

$$\sqrt{2}$$

= 169.7

f = 60 Hz

C = 0.1 µF

$$Z = \frac{VPEAK}{3 \times 10^{-4}} = \frac{169.7}{3 \times 10^{-4}} = 565.7 k\Omega$$

XC =  $\frac{1}{2\pi fC} = \frac{1}{(2\pi \times 60 \times 1 \times 10^{-7})} = 26.53 k\Omega$

R =  $\sqrt{(Z^2 \times Xc^2)} = 565.1 k\Omega$  (computed)

R = 560k $\Omega$  (used)

ZR =  $\sqrt{R^2 + Xc^2} = 560.6 k\Omega$  (using actual resistor)

IPEAK =  $\frac{VPEAK}{ZR} = 302.7 \times 10^{-6}$

VC = XC × Ipeak = 8.0V

$\Phi = Tan^{-1}(\frac{XC}{R}) = 0.047$  radians

T $\Phi = \frac{\Phi}{2\pi f} = 125.6 \mu s$

# 23.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 23-3.

# EQUATION 23-3: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - VCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to VSS. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 23-4.

# EQUATION 23-4: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - V_{CPINV})}{V_{CPINV}}$$

When External Signal is relative to VDD:

$$R_{PULLDOWN} = \frac{R_{SERIES}(VCPINV)}{(VDD - VCPINV)}$$

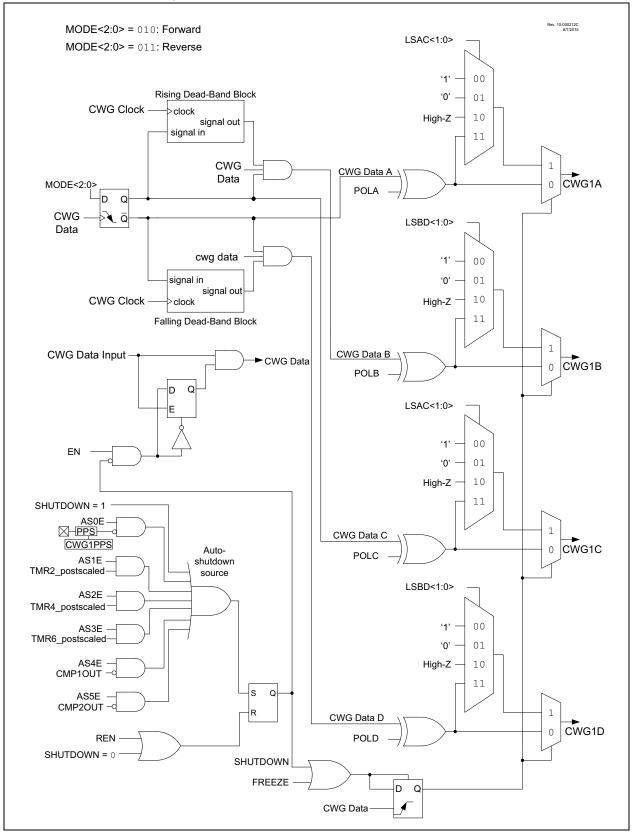

# FIGURE 24-6: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

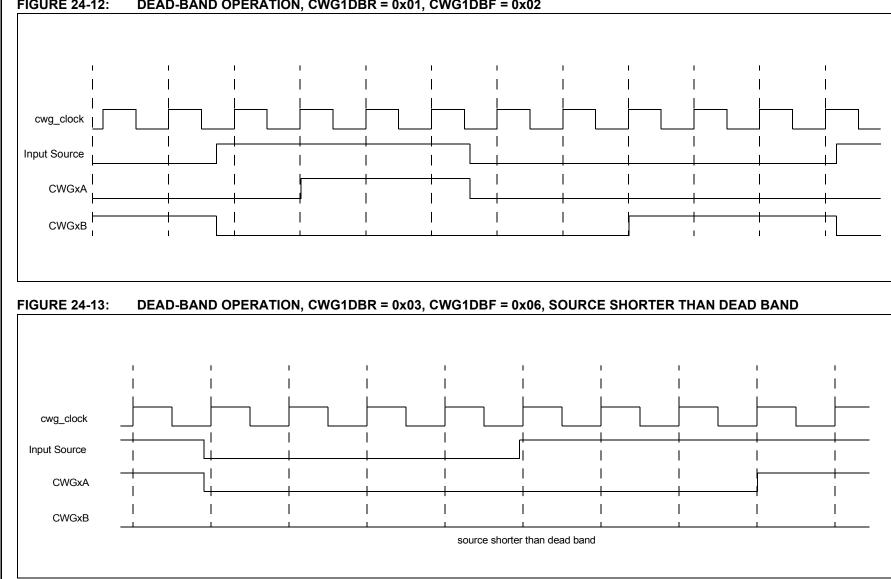

#### FIGURE 24-12: DEAD-BAND OPERATION, CWG1DBR = 0x01, CWG1DBF = 0x02

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                         |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 1211 987 0                                                                                                                                                                                                                                         |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                      |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | BC MYFUNC            |

| ADDWFC                                                                             | ADD W and CARRY bit to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                            | ADDWFC f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Operands:                                                                          | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:                                                                         | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected:                                                                   | N,OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:                                                                          | 0010 00da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                                                                    | Add W, the CARRY flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit- |  |  |  |  |  |

| Words:                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Q Cycle Activity:                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Q1                                                                                 | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Decode                                                                             | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Example:                                                                           | ADDWFC REG, 0, 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Before Instruct<br>CARRY b<br>REG<br>W<br>After Instruction<br>CARRY b<br>REG<br>W | it = 1<br>= 02h<br>= 4Dh<br>n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| AND                | DLW               | AI   | ND lite           | ral with                 | w   |    |                          |

|--------------------|-------------------|------|-------------------|--------------------------|-----|----|--------------------------|

| Synta              | ax:               | AN   | NDLW              | k                        |     |    |                          |

| Oper               | ands:             | 0 ≤  | ≤ k ≤ 258         | 5                        |     |    |                          |

| Oper               | ation:            | (W   | /) .AND.          | $k\toW$                  |     |    |                          |

| Statu              | is Affected:      | N,   | Z                 |                          |     |    |                          |

| Enco               | oding:            |      | 0000              | 1011                     | kkk | ck | kkkk                     |

| Desc               | ription:          |      |                   | nts of W a<br>'k'. The r |     |    | d with the<br>aced in W. |

| Word               | ls:               | 1    |                   |                          |     |    |                          |

| Cycle              | es:               | 1    |                   |                          |     |    |                          |

| QC                 | ycle Activity:    |      |                   |                          |     |    |                          |

|                    | Q1                |      | Q2                | Q3                       | 5   |    | Q4                       |

|                    | Decode            | Rea  | ad literal<br>'k' | Proce<br>Dat             |     | Wı | rite to W                |

| Exan               | nple:             | AN   | IDLW              | 05Fh                     |     |    |                          |

| Before Instruction |                   | tion |                   |                          |     |    |                          |

|                    | W                 | =    | A3h               |                          |     |    |                          |

|                    | After Instruction | on   |                   |                          |     |    |                          |

|                    | W                 | =    | 03h               |                          |     |    |                          |

| LFS   | R                | Load FSF                                                            | ર                                   |                                         | MOVF                          | Move f                                                                                                                               |                                                                |  |

|-------|------------------|---------------------------------------------------------------------|-------------------------------------|-----------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Synta | ax:              | LFSR f, k                                                           |                                     |                                         | Syntax:                       | MOVF f {,d {,a}}                                                                                                                     |                                                                |  |

| Oper  | ands:            | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 409 \end{array}$ | 95                                  |                                         | Operands:                     | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \end{array}$                                                                    |                                                                |  |

| Oper  | ation:           | $k \to FSRf$                                                        |                                     |                                         |                               | a ∈ [0,1]                                                                                                                            |                                                                |  |

| Statu | s Affected:      | None                                                                |                                     |                                         | Operation:                    | $f \rightarrow dest$                                                                                                                 |                                                                |  |

| Enco  | ding:            | 1110<br>1111                                                        | 1110 00<br>0000 k <sub>7</sub> k    | 11                                      | Status Affected:<br>Encoding: | N, Z<br>0101 00da fi                                                                                                                 | fff ffff                                                       |  |

| Desc  | ription:         |                                                                     | literal 'k' is loa<br>Register poin |                                         | Description:                  | The contents of register a destination dependent                                                                                     | upon the                                                       |  |

| Word  | s:               | 2                                                                   |                                     |                                         |                               | status of 'd'. If 'd' is '0', t<br>placed in W. If 'd' is '1', t                                                                     |                                                                |  |

| Cycle | es:              | 2                                                                   |                                     |                                         |                               | placed back in register "                                                                                                            |                                                                |  |

| QC    | ycle Activity:   |                                                                     |                                     |                                         |                               | Location 'f' can be anyw                                                                                                             |                                                                |  |

| i     | Q1               | Q2                                                                  | Q3                                  | Q4                                      |                               | 256-byte bank.<br>If 'a' is '0', the Access Ba                                                                                       | ank is selected                                                |  |

|       | Decode           | Read literal<br>'k' MSB                                             | Process<br>Data                     | Write<br>literal 'k'<br>MSB to<br>FSRfH |                               | If 'a' is '1', the BSR is us<br>GPR bank.<br>If 'a' is '0' and the exten-<br>set is enabled, this instri                             | ed to select the                                               |  |