Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F26/45/46K40

# PIC18(L)F2x/4xK40 Family Types

| Device         | Data Sheet Index | Program Memory Flash<br>(bytes) | Data SRAM<br>(bytes) | Data EEPROM<br>(bytes) | I/O Pins | 16-bit Timers | Comparators | 10-bit ADC <sup>2</sup> with<br>Computation (ch) | 5-bit DAC | Zero-Cross Detect | CCP/10-bit PWM | CWG | 8-bit TMR with HLT | Windowed Watchdog<br>Timer | <b>CRC</b> with Memory Scan | EUSART | I <sup>2</sup> C/SPI | Sdd | Peripheral Module Disable | Temperature Indicator | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------------|----------------------|------------------------|----------|---------------|-------------|--------------------------------------------------|-----------|-------------------|----------------|-----|--------------------|----------------------------|-----------------------------|--------|----------------------|-----|---------------------------|-----------------------|----------------------|

| PIC18(L)F24K40 | (1)              | 16k                             | 1024                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Y   | Y                         | Y                     | Ι                    |

| PIC18(L)F25K40 | (1)              | 32k                             | 2048                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Y   | Y                         | Υ                     | Ι                    |

| PIC18(L)F26K40 | (2)              | 64k                             | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Y                         | Y                     | Ι                    |

| PIC18(L)F27K40 | (3)              | 128k                            | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F45K40 | (2)              | 32k                             | 2048                 | 256                    | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F46K40 | (2)              | 64k                             | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F47K40 | (3)              | 128k                            | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

**Note 1:** Debugging Methods: (I) – Integrated on Chip.

Data Sheet Index: (Unshaded devices are described in this document.)

1. DS40001843 PIC18(L)F24/25K40 Data Sheet, 28-Pin, 8-bit Flash Microcontrollers

2. DS40001816 PIC18(L)F26/45/46K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

3. DS40001844 PIC18(L)F27/47K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

| U-0                                                                                           | U-0 | U-0               | U-0                                 | U-0          | U-0              | U-0    | R/W-0/0      |  |

|-----------------------------------------------------------------------------------------------|-----|-------------------|-------------------------------------|--------------|------------------|--------|--------------|--|

| —                                                                                             | —   | —                 | —                                   | —            | —                | —      | DSMMD        |  |

| bit 7                                                                                         |     |                   |                                     |              |                  |        | bit 0        |  |

|                                                                                               |     |                   |                                     |              |                  |        |              |  |

| Legend:                                                                                       |     |                   |                                     |              |                  |        |              |  |

| R = Readable                                                                                  | bit | W = Writable I    | oit                                 | U = Unimplem | nented bit, read | as '0' |              |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |     |                   |                                     |              |                  |        | other Resets |  |

| '1' = Bit is set                                                                              |     | '0' = Bit is clea | ared q = Value depends on condition |              |                  |        |              |  |

# REGISTER 7-6: PMD5: PMD CONTROL REGISTER 5

| bit 7-1 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 0 DSMMD: Disable Data Signal Modulator bit

1 = DSM module disabled

0 = DSM module enabled

# TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH PMD

| Name | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|------|---------|---------|---------|---------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD  | FVRMD   | HLVDMD  | CRCMD   | SCANMD | NVMMD  | CLKRMD | IOCMD  | 68                  |

| PMD1 | _       | TMR6MD  | TMR5MD  | TMR4MD  | TMR3MD | TMR2MD | TMR1MD | TMR0MD | 69                  |

| PMD2 | _       | DACMD   | ADCMD   | _       | _      | CMP2MD | CMP1MD | ZCDMD  | 70                  |

| PMD3 | _       | _       | _       | -       | PWM4MD | PWM3MD | CCP2MD | CCP1MD | 71                  |

| PMD4 | UART2MD | UART1MD | MSSP2MD | MSSP1MD | _      | _      | _      | CWG1MD | 72                  |

| PMD5 | _       |         | _       | _       | _      |        |        | DSMMD  | 73                  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the PMD.

The user needs to load the TBLPTR and TABLAT register with the address and data byte respectively before executing the write command. An unlock sequence needs to be followed for writing to the USER IDs/ DEVICE IDs/CONFIG words (Section 11.1.4, NVM Unlock Sequence). If WRTC = 0 or if TBLPTR points an invalid address location (see Table 11-3), WR bit is cleared without any effect and WRERR is set.

A single CONFIG word byte is written at once and the operation includes an implicit erase cycle for that byte (it is not necessary to set FREE). CPU execution is stalled and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The new CONFIG value takes effect when the CPU resumes operation.

# TABLE 11-4: USER ID, DEV/REV ID AND CONFIGURATION WORD ACCESS (NVMREG<1:0> = x1)

| Address           | Function                | Read Access | Write Access |

|-------------------|-------------------------|-------------|--------------|

| 20 0000h-20 000Fh | User IDs                | Yes         | Yes          |

| 3F FFFCh-3F FFFFh | Revision ID/Device ID   | Yes         | No           |

| 30 0000h-30 000Bh | Configuration Words 1-6 | Yes         | Yes          |

# **REGISTER 11-5: NVMDAT: DATA EEPROM MEMORY DATA**

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|------------------|---------|-------------------|---------|------------------|------------------|----------|---------|

|                  |         |                   | NVMD    | AT<7:0>          |                  |          |         |

| bit 7            |         |                   |         |                  |                  |          | bit 0   |

|                  |         |                   |         |                  |                  |          |         |

| Legend:          |         |                   |         |                  |                  |          |         |

| R = Readable     | bit     | W = Writable I    | oit     | U = Unimpler     | nented bit, read | d as '0' |         |

| x = Bit is unkne | own     | '0' = Bit is clea | ared    | '1' = Bit is set |                  |          |         |

| -n = Value at F  | POR     |                   |         |                  |                  |          |         |

bit 7-0 **NVMDAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

## TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

| Name                   | Bit 7    | Bit 6       | Bit 5     | Bit 4        | Bit 3         | Bit 2        | Bit 1       | Bit 0   | Register<br>on Page |  |  |  |

|------------------------|----------|-------------|-----------|--------------|---------------|--------------|-------------|---------|---------------------|--|--|--|

| NVMCON1                | NVMRE    | G<1:0>      | —         | FREE         | WRERR         | WREN         | WR RD       |         | 145                 |  |  |  |

| NVMCON2                |          |             |           | Unloc        | k Pattern     |              |             |         | 146                 |  |  |  |

| NVMADRL                |          | NVMADR<7:0> |           |              |               |              |             |         |                     |  |  |  |

| NVMADRH <sup>(1)</sup> | _        | —           | —         | —            | _             | —            | NVMA        | 146     |                     |  |  |  |

| NVMDAT                 |          | NVMDAT<7:0> |           |              |               |              |             |         | 147                 |  |  |  |

| TBLPTRU                | _        | _           |           | Program N    | lemory Table  | Pointer (TBL | PTR<21:16>) |         | 127*                |  |  |  |

| TBLPTRH                |          |             | Program N | lemory Table | e Pointer (TB | LPTR<15:8>)  |             |         | 127*                |  |  |  |

| TBLPTRL                |          |             | Program I | Memory Table | e Pointer (TB | LPTR<7:0>)   |             |         | 127*                |  |  |  |

| TABLAT                 |          |             |           | TA           | BLAT          |              |             |         | 126*                |  |  |  |

| INTCON                 | GIE/GIEH | PEIE/GIEL   | IPEN      | —            | _             | INT2EDG      | INT1EDG     | INT0EDG | 170                 |  |  |  |

| PIE7                   | SCANIE   | CRCIE       | NVMIE     | —            | —             | —            | —           | CWG1IE  | 186                 |  |  |  |

| PIR7                   | SCANIF   | CRCIF       | NVMIF     | _            | _             | _            | _           | CWG1IF  | 178                 |  |  |  |

| IPR7                   | SCANIP   | CRCIP       | NVMIP     | —            | —             | _            | —           | CWG1IP  | 194                 |  |  |  |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

Note 1: The NVMADRH register is not implemented on PIC18(L)F26/45/46K40.

# REGISTER 13-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W-x/x         | R/W-x/x | R/W-x/x         | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|-------------|

|                 |         |                 | X<1     | 5:8>           |                  |                  |             |

| bit 7           |         |                 |         |                |                  |                  | bit 0       |

|                 |         |                 |         |                |                  |                  |             |

| Legend:         |         |                 |         |                |                  |                  |             |

| R = Readable    | bit     | W = Writable    | bit     | U = Unimplen   | nented bit, read | as '0'           |             |

| u = Bit is unch | anged   | x = Bit is unkr | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 X<15:8>: XOR of Polynomial Term XN Enable bits

# REGISTER 13-10: CRCXORL: CRC XOR LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

|         |         |         |         |         |         |         |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 X<7:1>: XOR of Polynomial Term XN Enable bits

bit 0 Unimplemented: Read as '1'

'1' = Bit is set

|               |                      |                                         |               |                  | · · ·            |                 |                 |

|---------------|----------------------|-----------------------------------------|---------------|------------------|------------------|-----------------|-----------------|

| R/W-0/0       | R/W-0/0              | U-0                                     | U-0           | U-0              | U-0              | R/W-0/0         | R/W-0/0         |

| OSCFIF        | CSWIF <sup>(1)</sup> | —                                       | _             | _                | —                | ADTIF           | ADIF            |

| bit 7         |                      |                                         |               |                  |                  | •               | bit 0           |

|               |                      |                                         |               |                  |                  |                 |                 |

| Legend:       |                      |                                         |               |                  |                  |                 |                 |

| R = Readabl   | e bit                | W = Writable b                          | it            | U = Unimpler     | mented bit, read | as '0'          |                 |

| -n = Value at | POR                  | '1' = Bit is set                        |               | '0' = Bit is cle | ared             | x = Bit is unki | nown            |

|               |                      |                                         |               |                  |                  |                 |                 |

| bit 7         | OSCFIF: Osc          | cillator Fail Interr                    | upt Flag bit  |                  |                  |                 |                 |

|               |                      | scillator failed, c                     | lock input ha | s changed to I   | HFINTOSC (mu     | st be cleared b | y software)     |

|               |                      | lock operating                          | <i>(</i> 1)   |                  |                  |                 |                 |

| bit 6         |                      | k-Switch Interrup                       | •             |                  |                  |                 |                 |

|               |                      | illator is ready fo                     | •             |                  | • • •            | e Figure 4-6 ar | nd Figure 4-7)  |

|               |                      | illator is not read                     | -             | or has not bee   | n started        |                 |                 |

| bit 5-2       | -                    | nted: Read as '0                        |               |                  |                  |                 |                 |

| bit 1         |                      | Threshold Interr                        |               |                  |                  |                 |                 |

|               |                      | reshold interrupt<br>reshold event is i |               | •                | •                | e)              |                 |

| bit 0         | ADIF: ADC II         | nterrupt Flag bit                       |               |                  |                  |                 |                 |

|               | 1 = An A/D c         | onversion compl                         | eted (must b  | e cleared by so  | oftware)         |                 |                 |

|               | 0 = The A/D          | conversion is not                       | t complete or | has not been     | started          |                 |                 |

| Note 1: 1     | The CSWIF inter      | rupt will not wak                       | e the systen  | n from Sleep.    | The system will  | sleep until an  | other interrupt |

# REGISTER 14-3: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

causes the wake-up.

|                |                                                                                   |                          | -   | -                |                  |                 |         |

|----------------|-----------------------------------------------------------------------------------|--------------------------|-----|------------------|------------------|-----------------|---------|

| R/W-1/1        | R/W-1/1                                                                           | R/W-1/1                  | U-0 | U-0              | U-0              | U-0             | R/W-1/1 |

| SCANIP         | CRCIP                                                                             | NVMIP                    | _   | —                | —                | —               | CWG1IP  |

| bit 7          | ·                                                                                 |                          |     |                  |                  | •               | bit 0   |

|                |                                                                                   |                          |     |                  |                  |                 |         |

| Legend:        |                                                                                   |                          |     |                  |                  |                 |         |

| R = Readable   | bit                                                                               | W = Writable             | bit | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at  | POR                                                                               | '1' = Bit is set         |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7<br>bit 6 | 1 = High prio<br>0 = Low prior                                                    | rity                     | -   |                  |                  |                 |         |

|                | <b>CRCIP:</b> CRC Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |                          |     |                  |                  |                 |         |

| bit 5          |                                                                                   |                          |     |                  |                  |                 |         |

| bit 4-1        | Unimplemen                                                                        | ted: Read as '           | כ'  |                  |                  |                 |         |

| bit 0          | -                                                                                 | /G Interrupt Pri<br>rity |     |                  |                  |                 |         |

# REGISTER 14-25: IPR7: PERIPHERAL INTERRUPT PRIORITY REGISTER 7

# 17.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- CCP module

- Note: The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible. RB1 and RB2 are additional pins. RC4 and RC3 are default MMP1 pins and are SMBus compatible. Clock and data signals can be routed to any pin, however pins without I<sup>2</sup>C compatibility will operate at standard TTL/ST logic levels as selected by the INVLV register.

# 17.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 17-1.

# EXAMPLE 17-1: PPS LOCK SEQUENCE

| ; Disable interrupts:<br>BCF INTCON,GIE                                                      |

|----------------------------------------------------------------------------------------------|

| ; Bank to PPSLOCK register<br>BANKSEL PPSLOCK<br>MOVLB PPSLOCK<br>MOVLW 55h                  |

| ; Required sequence, next 4 instructions<br>MOVWF PPSLOCK<br>MOVLW AAh<br>MOVWF PPSLOCK      |

| ; Set PPSLOCKED bit to disable writes<br>; Only a BSF instruction will work<br>BSF PPSLOCK,0 |

| ; Enable Interrupts<br>BSF INTCON,GIE                                                        |

### EXAMPLE 17-2: PPS UNLOCK SEQUENCE

```

; Disable interrupts:

BCF

INTCON, GIE

; Bank to PPSLOCK register

BANKSEL PPSLOCK

MOVLB

PPSLOCK

MOVIW

55h

; Required sequence, next 4 instructions

MOVWF

PPSLOCK

MOVLW

AAh

MOVWF

PPSLOCK

; Clear PPSLOCKED bit to enable writes

; Only a BCF instruction will work

BCF

PPSLOCK,0

; Enable Interrupts

BSF

INTCON.GIE

```

# 17.5 PPS One-Way Lock

Using the PPS1WAY Configuration bit, the PPS settings can be locked in. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

# 17.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

# 17.7 Effects of a Reset

A device Power-on-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in the **Section "Pin Allocation Tables"**. The PPS one-way is also removed.

| R/W-x/x | R/W-x/x          | R/W-x/x         | R/W-x/x                     | R/W-x/x                                         | R/W-x/x         | R/W-x/x                                                |

|---------|------------------|-----------------|-----------------------------|-------------------------------------------------|-----------------|--------------------------------------------------------|

|         |                  | CCPR            | x<15:8>                     |                                                 |                 |                                                        |

|         |                  |                 |                             |                                                 |                 | bit 0                                                  |

|         |                  |                 |                             |                                                 |                 |                                                        |

|         |                  |                 |                             |                                                 |                 |                                                        |

| it      | W = Writable     | bit             | U = Unimplem                | ented bit, read                                 | l as '0'        |                                                        |

| DR      | '1' = Bit is set |                 | '0' = Bit is clea           | red                                             | x = Bit is unkr | nown                                                   |

|         | it               | it W = Writable | CCPR<br>it W = Writable bit | CCPRx<15:8><br>it W = Writable bit U = Unimplem | CCPRx<15:8>     | it W = Writable bit U = Unimplemented bit, read as '0' |

# REGISTER 21-5: CCPRxH: CCPx REGISTER HIGH BYTE

bit 7-0

MODE = Capture Mode:

CCPRxH<7:0>: MSB of captured TMR1 value

MODE = Compare Mode:

CCPRxH<7:0>: MSB compared to TMR1 value

MODE = PWM Mode && FMT = 0:

CCPRxH<7:2>: Not used

CCPRxH<7:2>: Not used

CCPRxH<1:0>: CCPW<9:8> – Pulse-Width MS 2 bits

MODE = PWM Mode && FMT = 1:

CCPRxH<7:0>: CCPW<9:2> – Pulse-Width MS 8 bits

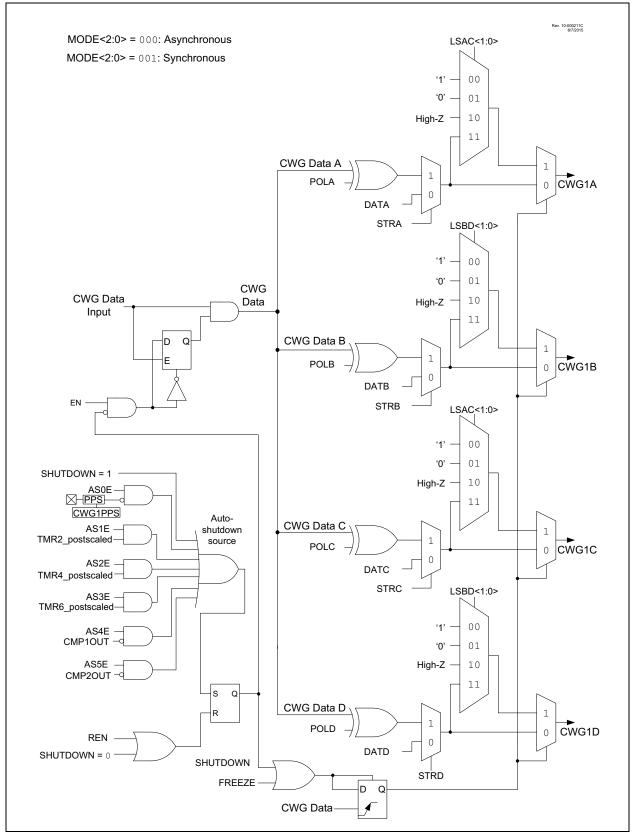

# FIGURE 24-11: SIMPLIFIED CWG BLOCK DIAGRAM (OUTPUT STEERING MODES)

| U-0                                   | U-0                                               | R/W-0/0                                                                                                     | R/W-0/0                               | U-0             | U-0                          | R/W-0/0         | R/W-0/0          |  |  |  |  |

|---------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|------------------------------|-----------------|------------------|--|--|--|--|

| _                                     | —                                                 | CHPOL                                                                                                       | CHSYNC                                |                 | —                            | CLPOL           | CLSYNC           |  |  |  |  |

| bit 7                                 |                                                   |                                                                                                             |                                       |                 |                              |                 | bit 0            |  |  |  |  |

|                                       |                                                   |                                                                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

| Legend:                               |                                                   |                                                                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

| R = Reada                             | ble bit                                           | W = Writable                                                                                                | bit                                   | U = Unimple     | mented bit, rea              | d as '0'        |                  |  |  |  |  |

| u = Bit is u                          | nchanged                                          | x = Bit is unkr                                                                                             | iown                                  | -n/n = Value    | at POR and BO                | OR/Value at all | other Resets     |  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                                   |                                                                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       |                                                   |                                                                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

| bit 7-6                               | Unimplem                                          | Unimplemented: Read as '0'                                                                                  |                                       |                 |                              |                 |                  |  |  |  |  |

| bit 5                                 | CHPOL: Modulator High Carrier Polarity Select bit |                                                                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       | 1 = Selecte                                       | 1 = Selected high carrier signal is inverted                                                                |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       |                                                   | 0                                                                                                           | I high carrier signal is not inverted |                 |                              |                 |                  |  |  |  |  |

| bit 4                                 |                                                   | CHSYNC: Modulator High Carrier Synchronization Enable bit                                                   |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       |                                                   | 1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the      |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       |                                                   | low time carrier<br>0 = Modulator output is not synchronized to the high time carrier signal <sup>(1)</sup> |                                       |                 |                              |                 |                  |  |  |  |  |

| bit 3-2                               |                                                   | ented: Read as '                                                                                            |                                       |                 | e carrier eignar             |                 |                  |  |  |  |  |

| bit 1                                 | -                                                 |                                                                                                             |                                       | elect bit       |                              |                 |                  |  |  |  |  |

|                                       |                                                   | <b>CLPOL:</b> Modulator Low Carrier Polarity Select bit<br>1 = Selected low carrier signal is inverted      |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       | 0 = Selecte                                       | 0 = Selected low carrier signal is not inverted                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

| bit 0                                 |                                                   | Modulator Low C                                                                                             |                                       |                 |                              |                 |                  |  |  |  |  |

|                                       | 1 = Modula<br>time c                              | ator waits for a fa                                                                                         | lling edge on th                      | e low time carr | rier signal befor            | e allowing a sw | itch to the high |  |  |  |  |

|                                       |                                                   | ator output is not                                                                                          | synchronized t                        | to the low time | carrier signal <sup>(1</sup> | )               |                  |  |  |  |  |

| Note 1.Nor                            |                                                   | ulse widths or sn                                                                                           |                                       |                 |                              |                 | aronizod         |  |  |  |  |

# REGISTER 25-2: MDCON1: MODULATION CONTROL REGISTER 1

Note 1:Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### **Register Definitions: MSSP Control** 26.4

| R/W-0                                | R/W-0                                                                                                                                         | R-0                                 | R-0              | R-0           | R-0             | R-0             | R-0           |  |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------|---------------|-----------------|-----------------|---------------|--|--|--|--|

| SMP                                  | CKE <sup>(1)</sup>                                                                                                                            | D/A                                 | Р                | S             | R/W             | UA              | BF            |  |  |  |  |

| bit 7                                |                                                                                                                                               | 1                                   |                  | 1             |                 | 1               | bit C         |  |  |  |  |

|                                      |                                                                                                                                               |                                     |                  |               |                 |                 |               |  |  |  |  |

| Legend:                              |                                                                                                                                               |                                     |                  |               |                 |                 |               |  |  |  |  |

| R = Readab                           | ole bit                                                                                                                                       | W = Writable                        | bit              | U = Unimplen  | nented bit, rea | id as '0'       |               |  |  |  |  |

| -n = Value at POR<br>bit 7 SMP: Samp |                                                                                                                                               | '1' = Bit is set                    | '1' = Bit is set |               | ared            | x = Bit is unkr | nown          |  |  |  |  |

|                                      |                                                                                                                                               | 1. 1.9                              |                  |               |                 |                 |               |  |  |  |  |

| DIT /                                |                                                                                                                                               |                                     |                  |               |                 |                 |               |  |  |  |  |

|                                      |                                                                                                                                               | SPI Master mode:                    |                  |               |                 |                 |               |  |  |  |  |

|                                      | <ol> <li>I = Input data is sampled at the end of data output time</li> <li>Input data is sampled at the middle of data output time</li> </ol> |                                     |                  |               |                 |                 |               |  |  |  |  |

|                                      | SPI Slave mode:                                                                                                                               |                                     |                  |               |                 |                 |               |  |  |  |  |

|                                      | SMP must b                                                                                                                                    | be cleared when                     | SPI is used in   | n Slave mode. |                 |                 |               |  |  |  |  |

| bit 6                                | CKE: SPI Clock Select bit <sup>(1)</sup>                                                                                                      |                                     |                  |               |                 |                 |               |  |  |  |  |

|                                      | 1 = Transmit occurs on the transition from active to Idle clock state                                                                         |                                     |                  |               |                 |                 |               |  |  |  |  |

|                                      | 0 = Transmit occurs on the transition from Idle to active clock state                                                                         |                                     |                  |               |                 |                 |               |  |  |  |  |

| bit 5                                | D/A: Data/A                                                                                                                                   | D/A: Data/Address bit               |                  |               |                 |                 |               |  |  |  |  |

|                                      | Used in I <sup>2</sup> C                                                                                                                      | mode only.                          |                  |               |                 |                 |               |  |  |  |  |

| bit 4                                | P: Stop bit                                                                                                                                   | P: Stop bit                         |                  |               |                 |                 |               |  |  |  |  |

|                                      | Used in I <sup>2</sup> C                                                                                                                      | mode only. This                     | bit is cleared   | when the MSSF | Px module is d  | isabled; SSPEN  | l is cleared. |  |  |  |  |

| bit 3                                | S: Start bit                                                                                                                                  |                                     |                  |               |                 |                 |               |  |  |  |  |

|                                      | Used in I <sup>2</sup> C                                                                                                                      | -                                   |                  |               |                 |                 |               |  |  |  |  |

| bit 2                                |                                                                                                                                               | R/W: Read/Write Information bit     |                  |               |                 |                 |               |  |  |  |  |

|                                      | Used in I <sup>2</sup> C                                                                                                                      | Used in I <sup>2</sup> C mode only. |                  |               |                 |                 |               |  |  |  |  |

| bit 1                                |                                                                                                                                               | Address bit                         |                  |               |                 |                 |               |  |  |  |  |

|                                      | Used in I <sup>2</sup> C                                                                                                                      | mode only.                          |                  |               |                 |                 |               |  |  |  |  |

| bit 0                                | BF: Buffer F                                                                                                                                  | Full Status bit (Re                 | eceive mode      | only)         |                 |                 |               |  |  |  |  |

|                                      |                                                                                                                                               | e is complete, SS                   |                  |               |                 |                 |               |  |  |  |  |

|                                      | 0 = Receive                                                                                                                                   | e is not complete                   | , SSPxBUF is     | sempty        |                 |                 |               |  |  |  |  |

| Note 1: F                            | Polarity of clock                                                                                                                             | state is set by th                  | ne CKP bit (S    | SPxCON1<4>).  |                 |                 |               |  |  |  |  |

|                                      |                                                                                                                                               |                                     |                  |               |                 |                 |               |  |  |  |  |

#### REGISTER 26-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

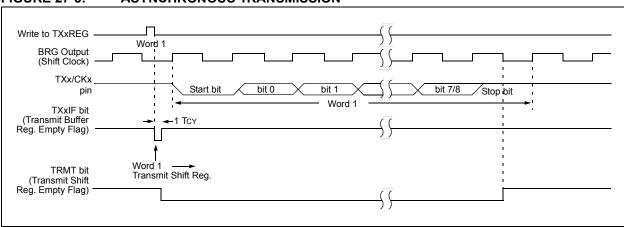

# 27.2.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

# 27.2.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 27.2.2.7 "Address Detection"** for more information on the Address mode.

# 27.2.1.7 Asynchronous Transmission Setup:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXxIF interrupt bit to be set.

- If interrupts are desired, set the TXxIE interrupt enable bit of the PIE3 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

# FIGURE 27-3: ASYNCHRONOUS TRANSMISSION

# **30.6 Register Definitions: DAC Control**

Long bit name prefixes for the DAC peripheral is shown in Table 30-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

# TABLE 30-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| DAC        | DAC             |

# REGISTER 30-1: DAC1CON0: DAC CONTROL REGISTER

| R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | U-0 | R/W-0/0 |

|---------|-----|---------|---------|----------|---------|-----|---------|

| EN      | —   | OE1     | OE2     | PSS<1:0> |         | —   | NSS     |

| bit 7   |     |         |         |          |         |     | bit 0   |

|         |     |         |         |          |         |     |         |

I

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 5   | <ul> <li>OE1: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is output on the DAC1OUT1 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT1 pin</li> </ul> |

| bit 4   | <ul> <li>OE2: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is output on the DAC1OUT2 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT2 pin</li> </ul> |

| bit 3-2 | PSS<1:0>: DAC Positive Source Select bit<br>11 = Reserved<br>10 = FVR buffer<br>01 = VREF+<br>00 = AVDD                                                                                  |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 0   | NSS: DAC Negative Source Select bit<br>1 = VREF-<br>0 = AVSS                                                                                                                             |

# 31.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 31-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 31-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 31-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

# EQUATION 31-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega$  5.0V VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 2\mu s + 892ns + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

|                    |      | Bit Clear Conditions Value after Trigger completion   |                                                                                          |                                                             | Threshold Operations                                                                                                                                                                   |                        |                        | Value at ADTIF interrupt |                          |       |

|--------------------|------|-------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|--------------------------|-------|

| Mode               | ADMD | ADACC and ADCNT                                       | ADACC                                                                                    | ADCNT                                                       | Retrigger                                                                                                                                                                              | Threshold<br>Test      | Interrupt              | ADAOV                    | ADFLTR                   | ADCNT |

| Basic              | 0    | ADACLR = 1                                            | Unchanged                                                                                | Unchanged                                                   | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | N/A                      | N/A                      | count |

| Accumulate         | 1    | ADACLR = 1                                            | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | Every<br>Sample        | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Average            | 2    | ADACLR = 1 or<br>ADCNT>=ADRPT at ADGO<br>or retrigger | S + ADACC<br>or<br>(S2-S1) + ADACC                                                       | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | count |

| Burst<br>Average   | 3    | ADACLR = 1 or ADGO set or<br>retrigger                | Each repetition: same as<br>Average<br>End with sum of all<br>samples                    | Each repetition: same as<br>Average<br>End with ADCNT=ADRPT | Repeat while<br>ADCNT <adrpt< td=""><td>lf<br/>ADCNT&gt;=<br/>ADRPT</td><td>If thresh-<br/>old=true</td><td>ADACC Overflow</td><td>ADACC/2<sup>ADCRS</sup></td><td>ADRPT</td></adrpt<> | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | ADACC/2 <sup>ADCRS</sup> | ADRPT |

| Low-pass<br>Filter | 4    | ADACLR = 1                                            | S+ADACC-ADACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ADACC-ADACC/<br>2 <sup>ADCRS</sup> | If (ADCNT=FF): ADCNT,<br>otherwise: ADCNT+1                 | No                                                                                                                                                                                     | lf<br>ADCNT>=<br>ADRPT | If thresh-<br>old=true | ADACC Overflow           | Filtered Value           | count |

Note: S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = ADREV and S2 = ADRES.

-n/n = Value at POR and BOR/Value at all other Resets

# REGISTER 31-27: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

x = Bit is unknown

| R-x              | R-x | R-x              | R-x  | R-x          | R-x              | R-x      | R-x   |

|------------------|-----|------------------|------|--------------|------------------|----------|-------|

|                  |     |                  | ADER | R<7:0>       |                  |          |       |

| bit 7            |     |                  |      |              |                  |          | bit 0 |

|                  |     |                  |      |              |                  |          |       |

| Legend:          |     |                  |      |              |                  |          |       |

| R = Readable bit |     | W = Writable bit |      | U = Unimplen | nented bit, read | d as '0' |       |

| '1' = Bit is set | '0' = Bit is cleared                                                                           |

|------------------|------------------------------------------------------------------------------------------------|

|                  |                                                                                                |

| bit 7-0          | ADERR<7:0>: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined |

# REGISTER 31-28 ADI THH: ADC I OWER THRESHOLD HIGH BYTE REGISTER

by ADCALC bits of ADCON3, see Register 23-1 for more details.

| ILE OIOTEIL O | LO. ADEN |         |         |         | DITEREOR |         |         |

|---------------|----------|---------|---------|---------|----------|---------|---------|

| R/W-x/x       | R/W-x/x  | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x  | R/W-x/x | R/W-x/x |

|               |          |         | ADLTH   | <15:8>  |          |         |         |

| bit 7         |          |         |         |         |          |         | bit 0   |

|               |          |         |         |         |          |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADLTH<15:8>: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

# REGISTER 31-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADLTH   | l<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADLTH<7:0>: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2015-2017 Microchip Technology Inc.

u = Bit is unchanged

| EN<br>bit 7     | _                 |                                    |                     |                                 |                                | -               |       |

|-----------------|-------------------|------------------------------------|---------------------|---------------------------------|--------------------------------|-----------------|-------|

| nit 7           |                   | OUT                                | RDY                 | -                               | _                              | INTH            | INTL  |

| 5107            |                   |                                    |                     |                                 | •                              | •               | bit C |

| Legend:         |                   |                                    |                     |                                 |                                |                 |       |

| R = Readable bi | it                | W = Writable                       | bit                 | U = Unimpler                    | mented bit, read               | d as '0'        |       |

| n = Value at PC | DR                | '1' = Bit is set                   |                     | '0' = Bit is cle                | eared                          | x = Bit is unkr | nown  |

|                 |                   |                                    |                     |                                 |                                |                 |       |

| bit 7           | EN: High/Low-     | -voltage Detec                     | t Power Enab        | ole bit                         |                                |                 |       |

|                 |                   |                                    |                     | cuit and suppo<br>and supportin | rting reference<br>g circuitry | circuitry       |       |

| bit 6           | Unimplement       | ed: Read as '                      | )'                  |                                 |                                |                 |       |

| bit 5           | OUT: HLVD C       | omparator Out                      | put bit             |                                 |                                |                 |       |

|                 | 1 = Voltage       |                                    | ,                   | ,                               |                                |                 |       |

|                 | 0 = Voltage ≥     | selected determination             | ection limit (HI    | LVDL<3:0>)                      |                                |                 |       |

| bit 4           | RDY: Band Ga      | ap Reference \                     | /oltages Stab       | le Status Flag                  | bit                            |                 |       |

|                 |                   |                                    | •                   | l output is stab                | le                             |                 |       |

|                 |                   | HLVD Module                        | ,                   |                                 |                                |                 |       |

|                 | Unimplement       |                                    |                     |                                 |                                |                 |       |

| bit 1           |                   |                                    |                     | ) Interrupt Enal                |                                |                 |       |

|                 |                   |                                    | n voltage $\geq$ se | elected detecti                 | on limit (HLVDS                | SEL<3:0>)       |       |

|                 | • • • • • • • • • | will not be set                    |                     |                                 | L.I.                           |                 |       |

|                 |                   |                                    |                     | ) Interrupt Ena                 |                                |                 |       |

|                 |                   | will be set whe<br>will not be set | In voltage $\leq$ s | selected detect                 | ion limit (HLVD                | SEL<3:0>)       |       |

# REGISTER 33-2: HLVDCON0: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER 0

| TABLE 33-2: F | REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE |

|---------------|----------------------------------------------------------|

|---------------|----------------------------------------------------------|

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|----------|----------|-----------|--------|-------|--------|---------|---------|---------|---------------------|

| HLVDCON0 | EN       | -         | OUT    | RDY   | -      | -       | INTH    | INTL    | 482                 |

| HLVDCON1 | _        | -         | -      | -     |        | SEL<    | :3:0>   |         | 481                 |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN   | -     | -      | INT2EDG | INT1EDG | INT0EDG | 170                 |

| PIR2     | HLVDIF   | ZCDIF     | -      | -     | -      | -       | C2IF    | C1IF    | 173                 |

| PIE2     | HLVDIE   | ZCDIE     | -      | -     | -      | -       | C2IE    | C1IE    | 181                 |

| IPR2     | HLVDIP   | ZCDIP     | -      | -     | -      | -       | C2IP    | C1IP    | 189                 |

| PMD0     | SYSCMD   | FVRMD     | HLVDMD | CRCMD | SCANMD | NVMMD   | CLKRMD  | IOCMD   | 68                  |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

| <b>TABLE 37-3</b> : | POWER-DOWN CURRENT (IPD) <sup>(1,2)</sup> |

|---------------------|-------------------------------------------|

|---------------------|-------------------------------------------|

| PIC18LF26/45/46K40 |             |                                           |        |                        | Standard Operating Conditions (unless otherwise stated) |           |         |         |                                  |  |  |

|--------------------|-------------|-------------------------------------------|--------|------------------------|---------------------------------------------------------|-----------|---------|---------|----------------------------------|--|--|

| PIC18F2            | 26/45/46K40 |                                           |        | <b>Standa</b><br>VREGF |                                                         | ating Con | ditions | (unless | otherwise stated)                |  |  |

| Param.             | Symbol      | Device Characteristics                    | Min.   | Turn ±                 | Max.                                                    | Max.      | Units   |         | Conditions                       |  |  |

| No.                | Symbol      | Device Characteristics                    | wiiri. | Тур.†                  | +85°C                                                   | +125°C    | Units   | VDD     | Note                             |  |  |

| D200               | IPD         | IPD Base                                  |        | 0.05                   | 2                                                       | 9         | μΑ      | 3.0V    |                                  |  |  |

| D200               | IPD         | IPD Base                                  | _      | 0.4                    | 4                                                       | 12        | μA      | 3.0V    |                                  |  |  |

| D200A              |             |                                           |        | 20                     |                                                         |           | μΑ      | 3.0V    | VREGPM = 0                       |  |  |

| D201               | IPD_WDT     | Low-Frequency Internal Oscillator/<br>WDT | _      | 0.4                    | 3                                                       | 10        | μΑ      | 3.0V    |                                  |  |  |

| D201               | IPD_WDT     | Low-Frequency Internal Oscillator/<br>WDT |        | 0.6                    | 5                                                       | 13        | μΑ      | 3.0V    |                                  |  |  |

| D202               | IPD_SOSC    | Secondary Oscillator (Sosc)               |        | 0.6                    | 5                                                       | 13        | μΑ      | 3.0V    |                                  |  |  |

| D202               | IPD_SOSC    | Secondary Oscillator (SOSC)               | _      | 0.8                    | 8.5                                                     | 15        | μΑ      | 3.0V    |                                  |  |  |

| D203               | IPD_FVR     | FVR                                       |        | 31                     | —                                                       | —         | μΑ      | 3.0V    | FVRCON = 0X81 or 0x84            |  |  |

| D203               | IPD_FVR     | FVR                                       |        | 32                     |                                                         | _         | μΑ      | 3.0V    | FVRCON = 0X81 or 0x84            |  |  |

| D204               | IPD_BOR     | Brown-out Reset (BOR)                     | I      | 9                      | 14                                                      | 18        | μΑ      | 3.0V    |                                  |  |  |

| D204               | IPD_BOR     | Brown-out Reset (BOR)                     |        | 14                     | 19                                                      | 21        | μΑ      | 3.0V    |                                  |  |  |

| D205               | IPD_LPBOR   | Low-Power Brown-out Reset (LPBOR)         | I      | 0.5                    |                                                         | —         | μΑ      | 3.0V    |                                  |  |  |

| D205               | IPD_LPBOR   | Low-Power Brown-out Reset (LPBOR)         |        | 0.7                    | _                                                       | —         | μΑ      | 3.0V    |                                  |  |  |

| D206               | IPD_HLVD    | High/Low Voltage Detect (HLVD)            |        | 31                     | _                                                       | —         | μΑ      | 3.0V    |                                  |  |  |

| D206               | IPD_HLVD    | High/Low Voltage Detect (HLVD)            | _      | 32                     | _                                                       | —         | μΑ      | 3.0V    |                                  |  |  |

| D207               | IPD_ADCA    | ADC - Active                              | _      | 250                    | —                                                       | —         | μΑ      | 3.0V    | ADC is converting (4)            |  |  |