Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | Device Overview                                                           |     |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18(L)F27/47K40 Microcontrollers    |     |

| 3.0  | Device Configuration                                                      |     |

| 4.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |     |

| 5.0  | Reference Clock Output Module                                             |     |

| 6.0  | Power-Saving Operation Modes                                              |     |

| 7.0  | Peripheral Module Disable (PMD)                                           |     |

| 8.0  | Resets                                                                    |     |

| 9.0  | Windowed Watchdog Timer (WWDT)                                            |     |

| 10.0 |                                                                           |     |

| 11.0 |                                                                           |     |

| 12.0 | 8x8 Hardware Multiplier                                                   |     |

| 13.0 |                                                                           |     |

|      | Interrupts                                                                |     |

|      | I/O Ports                                                                 |     |

|      | Interrupt-on-Change                                                       |     |

|      | Peripheral Pin Select (PPS) Module                                        |     |

|      | Timer0 Module                                                             |     |

| 19.0 |                                                                           |     |

|      | Timer2/4/6 Module                                                         |     |

|      | Capture/Compare/PWM Module                                                |     |

| 22.0 | Pulse-Width Modulation (PWM)                                              |     |

|      | Zero-Cross Detection (ZCD) Module                                         |     |

|      | Complementary Waveform Generator (CWG) Module                             |     |

| 25.0 |                                                                           |     |

| 26.0 | Master Synchronous Serial Port Module                                     |     |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

| 28.0 |                                                                           |     |

| 29.0 | Temperature Indicator Module                                              |     |

|      | 5-Bit Digital-to-Analog Converter (DAC) Module                            |     |

|      | Analog-to-Digital Converter with Computation (ADC2) Module                |     |

|      | Comparator Module                                                         |     |

| 33.0 | High/Low-Voltage Detect (HLVD)                                            |     |

| 34.0 | In-Circuit Serial Programming™ (ICSP™)                                    |     |

|      | Instruction Set Summary                                                   |     |

| 36.0 | Development Support                                                       | 535 |

| 37.0 | Electrical Specifications                                                 | 539 |

|      | DC and AC Characteristics Graphs and Tables                               |     |

|      | Packaging Information                                                     |     |

|      | endix A: Revision History                                                 |     |

|      | endix B: Device Differences                                               |     |

|      | Microchip Website                                                         |     |

| Cust | omer Change Notification Service                                          |     |

| Cust | omer Support                                                              | 596 |

| Prod | luct Identification System                                                | 597 |

|      |                                                                           |     |

## 1.2 Other Special Features

- **Memory Endurance:** The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles up to 10K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a boot loader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F2x/ 4xK40 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced Peripheral Pin Select: The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins.

- Enhanced Addressable EUSART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-bit A/D Converter with Computation:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead. It has a new module called ADC<sup>2</sup> with computation features, which provides a digital filter and threshold interrupt functions.

- Windowed Watchdog Timer (WWDT):

- Timer monitoring of overflow and underflow events

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

## 1.3 Details on Individual Family Members

Devices in the PIC18(L)F2x/4xK40 family are available in 28-pin and 40/44-pin packages. The block diagram for this device is shown in Figure 1-1.

The devices have the following differences:

- 1. Program Flash Memory

- 2. Data Memory SRAM

- 3. Data Memory EEPROM

- 4. A/D channels

- 5. I/O ports

- 6. Enhanced USART

- 7. Input Voltage Range/Power Consumption

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in the pin summary tables (Table 1 and Table 2).

|              | PIC18(L)F24K40                      | PIC18(L)F25K40<br>PIC18(L)F45K40 | PIC18(L)F26K40<br>PIC18(L)F46K40 | PIC18(L)F27K40<br>PIC18(L)F47K40 |                |  |  |  |  |

|--------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------|--|--|--|--|

| Γ            | PC<21:0>                            | PC<21:0>                         | PC<21:0>                         | PC<21:0>                         |                |  |  |  |  |

|              | Ŧ                                   | Ť                                | Ŧ                                | Ŧ                                | _              |  |  |  |  |

| Note 1       | Stack (31 levels)                   | Stack (31 levels)                | Stack (31 levels)                | Stack (31 levels)                | Note           |  |  |  |  |

|              | ł                                   | +                                | . ↓                              | +                                | _              |  |  |  |  |

| 0000h        | Reset Vector                        | Reset Vector                     | Reset Vector                     | Reset Vector                     | 00 000         |  |  |  |  |

| •••          | • • •                               | •••                              | •••                              | •••                              | •••            |  |  |  |  |

| 0008h        | Interrupt Vector High               | Interrupt Vector High            | Interrupt Vector High            | Interrupt Vector High            | 00 000         |  |  |  |  |

| •••          | • • •                               | •••                              | •••                              | •••                              | •••            |  |  |  |  |

| 0018h        | Interrupt Vector Low                | Interrupt Vector Low             | Interrupt Vector Low             | Interrupt Vector Low             | 00 00          |  |  |  |  |

| 001Ah        | User Flash Memory                   |                                  |                                  |                                  | 00 00          |  |  |  |  |

| •<br>3FFFh   | (8KW)                               | User Flash Memory                |                                  |                                  | •<br>00 3FI    |  |  |  |  |

| 4000h        |                                     | (16KW)                           |                                  |                                  | 00 400         |  |  |  |  |

| •            |                                     |                                  | User Flash Memory                |                                  | •              |  |  |  |  |

| 7FFFh        |                                     |                                  | (32KW)                           | PFM Flash Memory                 | 00 7FF         |  |  |  |  |

| 8000h        |                                     |                                  |                                  | (64KW)                           | 00 800         |  |  |  |  |

| •            |                                     |                                  |                                  |                                  | •              |  |  |  |  |

| FFFFh        | Not present <sup>(1)</sup>          |                                  |                                  |                                  | 00 FF          |  |  |  |  |

| 0000h        |                                     | Not present <sup>(1)</sup>       |                                  |                                  | 01 000         |  |  |  |  |

| FFFFh        |                                     | Not present                      | (4)                              |                                  | 01 FF          |  |  |  |  |

| 0000h        |                                     |                                  | Not present <sup>(1)</sup>       |                                  | 02 000         |  |  |  |  |

| •            |                                     |                                  |                                  | Not present <sup>(1)</sup>       | •              |  |  |  |  |

| FFFFh        |                                     |                                  |                                  |                                  | 1F FF          |  |  |  |  |

| 0000h        |                                     | Lises IDs.                       | (0.) (o. refe.)                  |                                  | 20 000         |  |  |  |  |

| •••<br>000Fh |                                     | User IDs                         | (8 vvoras)                       |                                  | 20 000         |  |  |  |  |

| 0010h        |                                     |                                  |                                  |                                  | 20 00          |  |  |  |  |

| •••          |                                     | Rese                             | rved                             |                                  | •••            |  |  |  |  |

| FFFFh        |                                     |                                  |                                  |                                  | 2F FF          |  |  |  |  |

| 0000h        |                                     |                                  |                                  |                                  | 30 000         |  |  |  |  |

| •••<br>000Bh |                                     | Configuration W                  | fords (6 Words)                  |                                  | 30 000         |  |  |  |  |

| 000Ch        |                                     |                                  |                                  |                                  | 30 000         |  |  |  |  |

| •••          |                                     | Rese                             | rved                             |                                  |                |  |  |  |  |

| FFFFh        |                                     |                                  |                                  |                                  | 30 FF          |  |  |  |  |

| 0000h        | DataEl                              | EByte0                           | DataEE                           | ERvita                           | 31 000         |  |  |  |  |

| •••          |                                     |                                  | DataLL                           | LDyteo                           | •••            |  |  |  |  |

| 00FFh        | DataEE                              | Byte255                          | •••                              | •                                |                |  |  |  |  |

|              | Unimple                             | emented                          |                                  |                                  |                |  |  |  |  |

| 03FFh        | Chimple                             |                                  | DataEEB                          | syte1023                         | 31 03          |  |  |  |  |

| 0400h        |                                     |                                  |                                  |                                  | 31 040         |  |  |  |  |

| •••          |                                     | Rese                             | rved                             |                                  | •••            |  |  |  |  |

| FFFBh        |                                     |                                  |                                  |                                  | 3F FF<br>3F FF |  |  |  |  |

| FFFCh        |                                     |                                  |                                  |                                  |                |  |  |  |  |

| FFFDh        | Revision ID (1 Word) <sup>(2)</sup> |                                  |                                  |                                  |                |  |  |  |  |

| FFFEh        |                                     |                                  |                                  |                                  | 3F FF<br>3F FF |  |  |  |  |

| •••          |                                     | Device ID                        | (1 Word) <sup>(2)</sup>          |                                  | •••            |  |  |  |  |

| FFFFh        |                                     |                                  |                                  |                                  | 3F FF          |  |  |  |  |

|              |                                     | over. The region is read a       |                                  |                                  |                |  |  |  |  |

#### TABLE 10-1: PROGRAM AND DATA MEMORY MAP

#### 13.11.7 IN-CIRCUIT DEBUG (ICD) INTERACTION

The scanner freezes when an ICD halt occurs, and remains frozen until user-mode operation resumes. The debugger may inspect the SCANCON0 and SCANLADR registers to determine the state of the scan.

The ICD interaction with each operating mode is summarized in Table 13-4.

|                     | Scanner Operating Mode                                                                           |                                                                                                                                                                                          |                                                                                                                                                                                                                                                           |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ICD Halt            | Peek                                                                                             | Burst                                                                                                                                                                                    |                                                                                                                                                                                                                                                           |  |  |  |  |

| External<br>Halt    |                                                                                                  | If external halt is asserted during<br>a scan cycle, the instruction<br>(delayed by scan) may or may<br>not execute before ICD entry,<br>depending on external halt<br>timing.           | If external halt is asserted during<br>the BSF (SCANCON.GO), ICD<br>entry occurs, and the burst is<br>delayed until ICD exit.<br>Otherwise, the current NVM-<br>access cycle will complete, and<br>then the scanner will be<br>interrupted for ICD entry. |  |  |  |  |

|                     |                                                                                                  | If external halt is asserted during<br>the cycle immediately prior to the<br>scan cycle, both scan and<br>instruction execution happen<br>after the ICD exits.                           | If external halt is asserted during<br>the burst, the burst is suspended<br>and will resume with ICD exit.                                                                                                                                                |  |  |  |  |

| PC<br>Breakpoint    | If scanner would peek an<br>instruction that is not executed<br>(because of ICD entry), the peek | Scan cycle occurs before ICD<br>entry and instruction execution<br>happens after the ICD exits.                                                                                          | If PCPB (or single step) is on                                                                                                                                                                                                                            |  |  |  |  |

| Data<br>Breakpoint  | will occur after ICD exit, when the instruction executes.                                        | The instruction with the dataBP<br>executes and ICD entry occurs<br>immediately after. If scan is<br>requested during that cycle, the<br>scan cycle is postponed until the<br>ICD exits. | BSF (SCANCON, GO), the ICD is<br>entered before execution;<br>execution of the burst will occur<br>at ICD exit, and the burst will run<br>to completion.                                                                                                  |  |  |  |  |

| Single Step         |                                                                                                  | If a scan cycle is ready after the debug instruction is executed, the scan will read PFM and then the ICD is re-entered.                                                                 | Note that the burst can be interrupted by an external halt.                                                                                                                                                                                               |  |  |  |  |

| SWBP and<br>ICDINST |                                                                                                  | If scan would stall a SWBP, the scan cycle occurs and the ICD is entered.                                                                                                                | If SWBP replaces<br>BSF(SCANCON.GO), the ICD will<br>be entered; instruction execution<br>will occur at ICD exit (from<br>ICDINSTR register), and the<br>burst will run to completion.                                                                    |  |  |  |  |

| <b>TABLE 13-4</b> : | ICD AND SCANNER INTERACTIONS |

|---------------------|------------------------------|

|                     |                              |

## 13.11.8 PERIPHERAL MODULE DISABLE

Both the CRC and scanner module can be disabled individually by setting the CRCMD and SCANMD bits of the PMD0 register (Register 7-1). The SCANMD can be used to enable or disable to the scanner module only if the SCANE bit of Configuration Word 4 is set. If the SCANE bit is cleared, then the scanner module is not available for use and the SCANMD bit is ignored.

## 16.6 Register Definitions: Interrupt-on-Change Control

| R/W-0/0                                 | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0       | R/W-0/0            | R/W-0/0 | R/W-0/0 |

|-----------------------------------------|---------|-------------------------------------------------------|---------|---------------|--------------------|---------|---------|

| IOCxP7                                  | IOCxP6  | IOCxP5                                                | IOCxP4  | IOCxP3        | IOCxP2             | IOCxP1  | IOCxP0  |

| bit 7                                   |         |                                                       | •       |               |                    |         | bit 0   |

|                                         |         |                                                       |         |               |                    |         |         |

| Legend:                                 |         |                                                       |         |               |                    |         |         |

| R = Readable bi                         | t       | W = Writable bi                                       | t       | U = Unimpleme | ented bit, read as | '0'     |         |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |         |               |                    |         |         |

| '1' = Bit is set                        |         | '0' = Bit is clear                                    | ed      |               |                    |         |         |

#### **REGISTER 16-1: IOCxP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER EXAMPLE**

bit 7-0

IOCxP<7:0>: Interrupt-on-Change Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a positive-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 16-2: IOCxN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER EXAMPLE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCxN7  | IOCxN6  | IOCxN5  | IOCxN4  | IOCxN3  | IOCxN2  | IOCxN1  | IOCxN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCxN<7:0>: Interrupt-on-Change Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a negative-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 16-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER EXAMPLE

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCxF7     | IOCxF6     | IOCxF5     | IOCxF4     | IOCxF3     | IOCxF2     | IOCxF1     | IOCxF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCxF<7:0>: Interrupt-on-Change Flag bits

1 = A enabled change was detected on the associated pin. Set when IOCP[n] = 1 and a positive edge was detected on the IOCn pin, or when IOCN[n] = 1 and a negative edge was detected on the IOCn pin

0 = No change was detected, or the user cleared the detected change

| Name      | Bit 7 | Bit 6 | Bit 5 | Bit 4          | Bit 3       | Bit 2 | Bit 1 | Bit 0 | Register<br>on page |

|-----------|-------|-------|-------|----------------|-------------|-------|-------|-------|---------------------|

| SSP2SSPPS | —     | _     | _     | SSP2SSPPS<4:0> |             |       |       | 216   |                     |

| RX2PPS    | —     | _     | _     |                | RX2PPS<4:0> |       |       |       | 218                 |

| TX2PPS    | —     | _     | -     | TX2PPS<4:0>    |             |       | 216   |       |                     |

| RxyPPS    | —     |       |       |                | RxyPPS<4:0> |       |       |       | 218                 |

## TABLE 17-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

## 22.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 22-4.

## EQUATION 22-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| <b>TABLE 22-1</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|---------------------|---------------------------------------------------------|

|---------------------|---------------------------------------------------------|

| <b>PWM Frequency</b>      | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 22-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 22.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 22.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 22.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

## 24.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWG1A output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWG1B is affected.

The CWG1DBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBR register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 24-1) is set. Refer to Figure 24-12 for an example.

## 24.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWG1B output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWG1D is affected.

The CWG1DBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBF register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 24-1) is set. Refer to Figure 24-13 for an example.

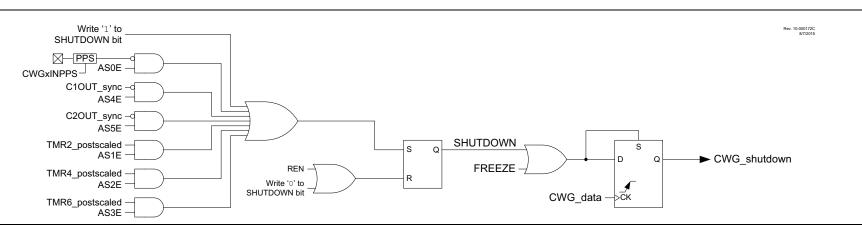

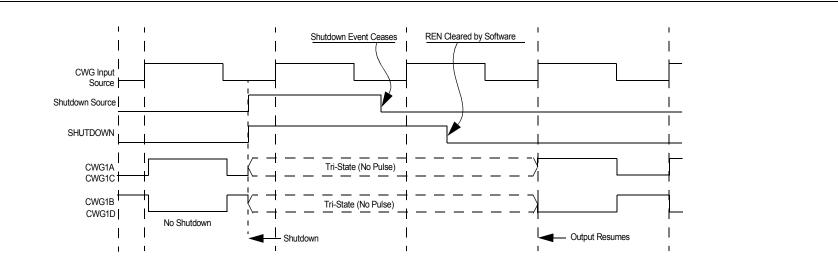

## FIGURE 24-15: SHUTDOWN FUNCTIONALITY, AUTO-RESTART DISABLED (REN = 0, LSAC = 01, LSBD = 01)

#### 26.9.2.1 7-bit Addressing Reception

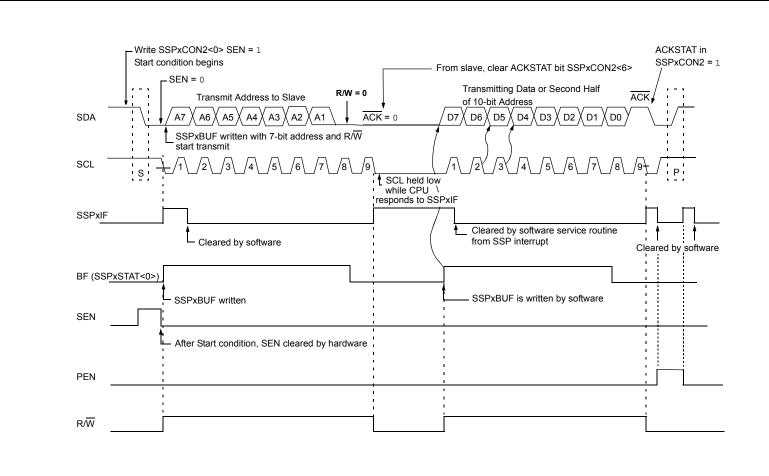

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 7-bit Addressing mode. Figure 26-14 and Figure 26-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPxIF bit.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSPxIF bit.

- 10. Software clears SSPxIF.

- 11. Software reads the received byte from SSPxBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- 13. Master sends Stop condition, setting P bit of SSPxSTAT, and the bus goes idle.

## 26.9.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 26-16 displays a module using both address and data holding. Figure 26-17 includes the operation with the SEN bit of the SSPxCON2 register set.

- 1. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPxIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPxIF.

- Slave can look at the ACKTIM bit of the SSPxCON3 register to <u>determine</u> if the SSPxIF was after or before the ACK.

- 5. Slave reads the address value from SSPxBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPxIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPxIF.

Note: SSPxIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPxIF not set

- 11. SSPxIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPxCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPxBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

PIC18(L)F26/45/46K40

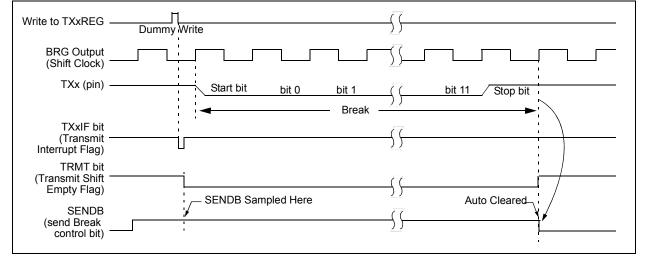

## 27.4.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXxSTA register. The Break character transmission is then initiated by a write to the TXxREG. The value of data written to TXxREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXxSTA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 27-9 for the timing of the Break character sequence.

#### 27.4.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXxREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXxREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXxREG becomes empty, as indicated by the TXxIF, the next data byte can be written to TXxREG.

## 27.4.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- · RCxIF bit is set

- FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 27.4.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCxIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

## FIGURE 27-9: SEND BREAK CHARACTER SEQUENCE

## **29.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between consecutive conversions of the temperature indicator output.

|  | TABLE 29-2: | SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR |

|--|-------------|----------------------------------------------------------------|

|--|-------------|----------------------------------------------------------------|

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFVR<1:0> |       | ADFVF | R<1:0> | 423                 |

Legend: — = Unimplemented location, read as '0'. Shaded cells are unused by the temperature indicator module.

| U-0                                     | U-0                                   | R/W-0/0         | R/W-0/0       | R/W-0/0                                               | R/W-0/0  | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------------------------------------|---------------------------------------|-----------------|---------------|-------------------------------------------------------|----------|---------|---------|--|--|--|

| _                                       |                                       |                 |               | ADCS                                                  | \$<5:0>  |         |         |  |  |  |

| bit 7                                   |                                       |                 |               |                                                       |          |         | bit 0   |  |  |  |

|                                         |                                       |                 |               |                                                       |          |         |         |  |  |  |

| Legend:                                 |                                       |                 |               |                                                       |          |         |         |  |  |  |

| R = Readable bit W = Writable bit       |                                       |                 | U = Unimplen  | nented bit, read                                      | d as '0' |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                                       |                 | nown          | -n/n = Value at POR and BOR/Value at all other Resets |          |         |         |  |  |  |

| '1' = Bit is se                         | '1' = Bit is set '0' = Bit is cleared |                 | ared          |                                                       |          |         |         |  |  |  |

|                                         |                                       |                 |               |                                                       |          |         |         |  |  |  |

| bit 7-6                                 | Unimplemen                            | ited: Read as ' | 0'            |                                                       |          |         |         |  |  |  |

| bit 5-0                                 | ADCS<5:0>:                            | ADC Conversi    | on Clock Sele | ect bits                                              |          |         |         |  |  |  |

|                                         | 111111 <b>= F</b> o                   | sc/128          |               |                                                       |          |         |         |  |  |  |

|                                         | 111110 <b>= F</b> O                   | sc/126          |               |                                                       |          |         |         |  |  |  |

| 111101 = Fosc/124                       |                                       |                 |               |                                                       |          |         |         |  |  |  |

|                                         | •                                     |                 |               |                                                       |          |         |         |  |  |  |

|                                         | •                                     |                 |               |                                                       |          |         |         |  |  |  |

|                                         | •                                     |                 |               |                                                       |          |         |         |  |  |  |

|                                         | 000000 <b>= F</b> O                   | osc/2           |               |                                                       |          |         |         |  |  |  |

## REGISTER 31-6: ADCLK: ADC CLOCK SELECTION REGISTER

## REGISTER 31-7: ADREF: ADC REFERENCE SELECTION REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | R/W-0/0     | R/W-0/0 |

|-------|-----|-----|---------|-----|-----|-------------|---------|

| —     | —   | —   | ADNREF  | —   | —   | ADPREF<1:0> |         |

| bit 7 |     |     |         |     |     |             | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5<br>bit 4 | Unimplemented: Read as '0'<br>ADNREF: ADC Negative Voltage Reference Selection bit<br>1 = VREF- is connected to external VREF-<br>0 = VREF- is connected to AVss                                                                  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-2          | Unimplemented: Read as '0'                                                                                                                                                                                                        |

| bit 1-0          | ADPREF: ADC Positive Voltage Reference Selection bits<br>11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module<br>10 = VREF+ is connected to external VREF+<br>01 = Reserved<br>00 = VREF+ is connected to VDD |

### REGISTER 31-8: ADPCH: ADC POSITIVE CHANNEL SELECTION REGISTER

| U-0                                   | U-0                  | R/W-0/0                                  | R/W-0/0                   | R/W-0/0        | R/W-0/0                  | R/W-0/0            | R/W-0/0 |

|---------------------------------------|----------------------|------------------------------------------|---------------------------|----------------|--------------------------|--------------------|---------|

| —                                     | _                    |                                          |                           | ADP            | CH<5:0>                  |                    |         |

| oit 7                                 |                      |                                          |                           |                |                          |                    | bit     |

|                                       |                      |                                          |                           |                |                          |                    |         |

| Legend:                               |                      |                                          |                           |                |                          |                    |         |

| R = Readable I                        | bit                  | W = Writable bit                         |                           | U = Unimpler   | mented bit, read as      | ; 'O'              |         |

| u = Bit is uncha                      | anged                | x = Bit is unknow                        | n                         | -n/n = Value a | at POR and BOR/\         | /alue at all other | Resets  |

| '1' = Bit is set '0' = Bit is cleared |                      |                                          |                           |                |                          |                    |         |

|                                       |                      |                                          |                           |                |                          |                    |         |

| bit 7-6                               | Unimplemen           | ted: Read as '0'                         |                           |                |                          |                    |         |

| bit 5-0                               | ADPCH<5:0>           | : ADC Positive Inpu                      | t Channel Se              | lection bits   |                          |                    |         |

|                                       | 111111 =             | Fixed Voltage Refe                       | rence (FVR) <sup>(2</sup> | <b>2)</b> 0101 | 111 = ANC7               |                    |         |

|                                       | 1111110 =            | DAC1 output <sup>(1)</sup>               |                           |                | 110 = ANC6               |                    |         |

|                                       |                      | Temperature Indica                       | tor <sup>(3)</sup>        | 0101           | L01 = ANC5               |                    |         |

|                                       | 111100 =             | AVss (Analog Grou                        | ind)                      | 0101           | L00 <b>= ANC4</b>        |                    |         |

|                                       | 111011 =             | 111011 = Reserved. No channel connected. |                           |                | 11 = ANC3                |                    |         |

|                                       | •                    |                                          |                           |                | 10 = ANC2                |                    |         |

|                                       | •                    |                                          |                           |                | 001 = ANC1               |                    |         |

|                                       | •                    |                                          |                           |                | 000 <b>= ANC0</b>        |                    |         |

|                                       | 100010 =             |                                          |                           |                | 111 = ANB7               |                    |         |

|                                       | 100001 =             |                                          |                           |                | L10 = ANB6               |                    |         |

|                                       | 100000 =             |                                          |                           |                | L01 = ANB5               |                    |         |

|                                       | 011111 =             | $AND^{(4)}$                              |                           |                | LOO = ANB4               |                    |         |

|                                       | 011110 =<br>011101 = |                                          |                           |                | 11 = ANB3                |                    |         |

|                                       | 011101 =             |                                          |                           |                | 10 = ANB2                |                    |         |

|                                       | 011100 =             |                                          |                           |                | 001 = ANB1<br>000 = ANB0 |                    |         |

|                                       | 011011 =             |                                          |                           |                | 111 = ANA7               |                    |         |

|                                       | 011001 =             |                                          |                           |                | 111 = ANA7<br>110 = ANA6 |                    |         |

|                                       | 011000 =             |                                          |                           |                | L01 = ANA5               |                    |         |

|                                       | 011000 -             |                                          |                           |                | L01 = ANA3               |                    |         |

|                                       |                      |                                          |                           |                | 111 = ANA3               |                    |         |

|                                       |                      |                                          |                           |                | 10 = ANA2                |                    |         |

|                                       |                      |                                          |                           |                | 001 = ANA1               |                    |         |

|                                       |                      |                                          |                           |                | 000 = ANA0               |                    |         |

Note 1: See Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module" for more information.

2: See Section 28.0 "Fixed Voltage Reference (FVR)" for more information.

3: See Section 29.0 "Temperature Indicator Module" for more information.

4: PIC18F45/46K40 only.

## 32.9 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-15 and Table 37-17 for more details.

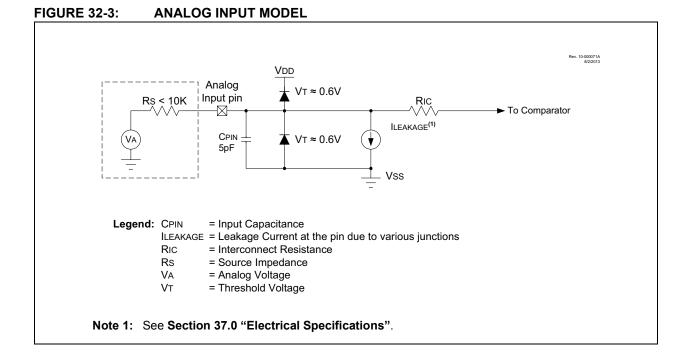

## 32.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 32-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

| Field           | Description                                                                                                                                                     |  |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| a               | RAM access bit                                                                                                                                                  |  |  |  |  |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)<br>a = 1: RAM bank is specified by BSR register                                                     |  |  |  |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |  |  |  |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |  |  |  |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |  |  |  |  |  |  |  |

| d               | Destination select bit<br>d = 0: store result in WREG<br>d = 1: store result in file register f                                                                 |  |  |  |  |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |  |  |  |  |  |  |  |

| f               | 8-bit Register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                                    |  |  |  |  |  |  |  |

| fs              | 12-bit Register file address (000h to FFFh). This is the source address.                                                                                        |  |  |  |  |  |  |  |

| fd              | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                                   |  |  |  |  |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |  |  |  |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |  |  |  |  |  |  |  |

| label           | Label name.                                                                                                                                                     |  |  |  |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions:                     |  |  |  |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |  |  |  |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |  |  |  |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for<br>CALL/BRANCH and RETURN instructions.                 |  |  |  |  |  |  |  |

| PC              | Program Counter.                                                                                                                                                |  |  |  |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                                       |  |  |  |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                                      |  |  |  |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |  |  |  |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |  |  |  |  |  |  |  |

| PD              | Power-down bit.                                                                                                                                                 |  |  |  |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |  |  |  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |  |  |  |  |  |  |  |

| S               | Fast Call/Return mode select bit<br>s = 0: do not update into/from shadow registers<br>s = 1: certain registers loaded into/from shadow registers (Fast mode)   |  |  |  |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).                                                                                                     |  |  |  |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                                              |  |  |  |  |  |  |  |

| TO              | Time-out bit.                                                                                                                                                   |  |  |  |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                                                   |  |  |  |  |  |  |  |

| u               | Unused or unchanged.                                                                                                                                            |  |  |  |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                                                 |  |  |  |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                                                 |  |  |  |  |  |  |  |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |  |  |

| Zs              | 7-bit offset value for indirect addressing of register files (source).                                                                                          |  |  |  |  |  |  |  |

| zd              | 7-bit offset value for indirect addressing of register files (destination).                                                                                     |  |  |  |  |  |  |  |

| { }             | Optional argument.                                                                                                                                              |  |  |  |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                                                   |  |  |  |  |  |  |  |

| (text)          | The contents of text.                                                                                                                                           |  |  |  |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                                  |  |  |  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                                    |  |  |  |  |  |  |  |

| < >             | Register bit field.                                                                                                                                             |  |  |  |  |  |  |  |

| e               | In the set of.                                                                                                                                                  |  |  |  |  |  |  |  |

| italics         | User defined term (font is Courier).                                                                                                                            |  |  |  |  |  |  |  |

## TABLE 35-1: OPCODE FIELD DESCRIPTIONS

## PIC18(L)F26/45/46K40

| RCALL Relative Call                                                                                                                                                                                                                                                                                                                                                 |                |                                            |                                                               |      |             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------|---------------------------------------------------------------|------|-------------|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                               | ax:            | RCALL n                                    |                                                               |      |             |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                | ands:          | -1024 ≤ n ≤                                | 1023                                                          |      |             |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                | ation:         | ( )                                        | $(PC) + 2 \rightarrow TOS,$<br>(PC) + 2 + 2n $\rightarrow$ PC |      |             |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                               | s Affected:    | None                                       |                                                               |      |             |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                | ding:          | 1101                                       | 1nnn                                                          | nnnn | nnnn        |  |  |  |

| Description:<br>Subroutine call with a jump up to 1K<br>from the current location. First, return<br>address (PC + 2) is pushed onto the<br>stack. Then, add the 2's complement<br>number '2n' to the PC. Since the PC w<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>2-cycle instruction. |                |                                            |                                                               |      |             |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                | ls:            | 1                                          |                                                               |      |             |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                               | es:            | 2                                          |                                                               |      |             |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                  | ycle Activity: |                                            |                                                               |      |             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | Q1             | Q2                                         | Q3                                                            |      | Q4          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | Decode         | Read literal<br>'n'<br>PUSH PC to<br>stack | Proce<br>Dat                                                  |      | Write to PC |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | No             | No                                         | No                                                            |      | No          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                     | operation      | operation                                  | opera                                                         | tion | operation   |  |  |  |

Example: HERE RCALL Jump

Before Instruction

PC = Address (HERE) After Instruction

PC = TOS = Address (Jump) Address (HERE + 2)

| RES   | ET             | Reset                                                                 |                                                                      |             |           |  |  |  |

|-------|----------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|-------------|-----------|--|--|--|

| Synta | ax:            | RESET                                                                 |                                                                      |             |           |  |  |  |

| Oper  | ands:          | None                                                                  |                                                                      |             |           |  |  |  |

| Oper  | ation:         | ion: Reset all registers and flags that are affected by a MCLR Reset. |                                                                      |             |           |  |  |  |

| Statu |                |                                                                       |                                                                      |             |           |  |  |  |

| Enco  | ding:          | 0000                                                                  | 0000                                                                 | 0 1111 1111 |           |  |  |  |