Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            | Antivo                                                                     |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40-i-pt |

# REGISTER 4-7: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 |

|---------|---------|---------|---------|---------|---------|-----|-----|

| EXTOEN  | HFOEN   | MFOEN   | LFOEN   | SOSCEN  | ADOEN   | _   | _   |

|         |         |         |         |         |         |     |     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EXTOEN: External Oscillator Manual Request Enable bit  1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC  0 = EXTOSC could be enabled by requesting peripheral                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | HFOEN: HFINTOSC Oscillator Manual Request Enable bit  1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ (Register 4-5)  0 = HFINTOSC could be enabled by requesting peripheral             |

| bit 5   | MFOEN: MFINTOSC (500 kHz/31.25 kHz) Oscillator Manual Request Enable bit (Derived from HFINTOSC)  1 = MFINTOSC is explicitly enabled  0 = MFINTOSC could be enabled by requesting peripheral                  |

| bit 4   | LFOEN: LFINTOSC (31 kHz) Oscillator Manual Request Enable bit  1 = LFINTOSC is explicitly enabled  0 = LFINTOSC could be enabled by requesting peripheral                                                     |

| bit 3   | SOSCEN: Secondary Oscillator Manual Request Enable bit  1 = Secondary Oscillator is explicitly enabled, operating as specified by SOSCPWR  0 = Secondary Oscillator could be enabled by requesting peripheral |

| bit 2   | ADOEN: ADC Oscillator Manual Request Enable bit  1 = ADC oscillator is explicitly enabled  0 = ADC oscillator could be enabled by requesting peripheral                                                       |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                                                                                    |

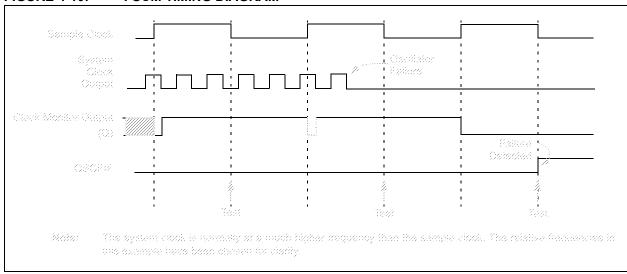

## 4.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed.

FIGURE 4-10: FSCM TIMING DIAGRAM

# REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ-ONLY)

| R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0   |

|-------------|-------|-------|-------|-------|-------|-------|---------|

| WDTTMR<4:0> |       |       |       |       | STATE | PSCNT | <17:16> |

| bit 7       |       |       |       |       |       |       | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

# bit 7-3 WDTTMR<4:0>: Watchdog Window Value bits

| WINDOW | WDT Win     | Onen Bereent |              |

|--------|-------------|--------------|--------------|

| WINDOW | Closed Open |              | Open Percent |

| 111    | N/A         | 00000-11111  | 100          |

| 110    | 00000-00011 | 00100-11111  | 87.5         |

| 101    | 00000-00111 | 01000-11111  | 75           |

| 100    | 00000-01011 | 01100-11111  | 62.5         |

| 011    | 00000-01111 | 10000-11111  | 50           |

| 010    | 00000-10011 | 10100-11111  | 37.5         |

| 001    | 00000-10111 | 11000-11111  | 25           |

| 000    | 00000-11011 | 11100-11111  | 12.5         |

bit 2 STATE: WDT Armed Status bit

1 = WDT is armed 0 = WDT is not armed

bit 1-0 **PSCNT<17:16>:** Prescale Select Upper Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### 13.6 CRC Check Value

The CRC check value will be located in the CRCACC registers after the CRC calculation has finished. The check value will depend on two mode settings of the CRCCON register: ACCM and SHIFTM.

When the ACCM bit is set, the CRC module augments the data with a number of zeros equal to the length of the polynomial to align the final check value. When the ACCM bit is not set, the CRC will stop at the end of the data. A number of zeros equal to the length of the polynomial can then be entered into CRCDAT to find the same check value as augmented mode. Alternatively, the expected check value can be entered at this point to make the final result equal 0.

When the CRC check value is computed with the SHIFTM bit set, selecting LSb first, and the ACCM bit is set then the final value in the CRCACC registers will be reversed such that the LSb will be in the MSb position and vice versa. This is the expected check value in bit reversed form. If you are creating a check value to be appended to a data stream then a bit reversal must be performed on the final value to achieve the correct checksum. You can use the CRC to do this reversal by the following method:

- · Save CRCACC value in user RAM space

- · Clear the CRCACC registers

- Clear the CRCXOR registers

- Write the saved CRCACC value to the CRCDAT input

The properly oriented check value will be in the CRCACC registers as the result.

#### 13.7 CRC Interrupt

The CRC will generate an interrupt when the BUSY bit transitions from 1 to 0. The CRCIF Interrupt Flag bit of the PIR7 register is set every time the BUSY bit transitions, regardless of whether or not the CRC interrupt is enabled. The CRCIF bit can only be cleared in software. The CRC interrupt enable is the CRCIE bit of the PIE7 register.

## 13.8 Configuring the CRC

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic program memory scan will be used with the scanner or manual calculation through the SFR interface and perform the actions specified in Section 13.5 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word - 1 (refer to Example 13-1). This determines how many times the shifter will shift into the accumulator for each data word.

- Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial -2 (refer to Example 13-1).

- Determine whether shifting in trailing zeros is desired and set the ACCM bit of the CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of the CRCCON0 register appropriately.

- 8. Write the CRCGO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of the CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has more than eight bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically stuff words into the CRCDATH/L registers as needed, as long as the SCANGO bit is set.

- 10a.If using the Flash memory scanner, monitor the SCANIF (or the SCANGO bit) for the scanner to finish pushing information into the CRCDATA registers. After the scanner is completed, monitor the BUSY bit to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set (or both BUSY and SCANGO bits are cleared), the completed CRC calculation can be read from the CRCACCH/L registers.

- 10b.If manual entry is used, monitor the BUSY bit to determine when the CRCACC registers will hold the check value.

# 14.8 Register Definitions: Interrupt Control

#### REGISTER 14-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0  | R/W-0/0   | R/W-0/0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------|-----------|---------|-----|-----|---------|---------|---------|

| GIE/GIEH | PEIE/GIEL | IPEN    | _   | _   | INT2EDG | INT1EDG | INT0EDG |

| bit 7    |           |         |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 GIE/GIEH: Global Interrupt Enable bit

If IPEN = 1:

1 = Enables all unmasked interrupts and cleared by hardware for high-priority interrupts only

0 = Disables all interrupts

If IPEN = 0:

1 = Enables all unmasked interrupts and cleared by hardware for all interrupts

0 = Disables all interrupts

bit 6 PEIE/GIEL: Peripheral Interrupt Enable bit

If IPEN = 1:

1 = Enables all low-priority interrupts and cleared by hardware for low-priority interrupts only

0 = Disables all low-priority interrupts

If IPEN = 0:

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 **IPEN:** Interrupt Priority Enable bit

1 = Enable priority levels on interrupts

0 = Disable priority levels on interrupts

bit 4-3 **Unimplemented**: Read as '0'

bit 2 **INT2EDG:** External Interrupt 2 Edge Select bit

1 = Interrupt on rising edge of INT2 pin

0 = Interrupt on falling edge of INT2 pin

bit 1 INT1EDG: External Interrupt 1 Edge Select bit

1 = Interrupt on rising edge of INT1 pin

0 = Interrupt on falling edge of INT1 pin

bit 0 INT0EDG: External Interrupt 0 Edge Select bit

1 = Interrupt on rising edge of INT0 pin

0 = Interrupt on falling edge of INT0 pin

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

# REGISTER 14-7: PIR5: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 5

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | TMR5GIF | TMR3GIF | TMR1GIF |

| bit 7 |     |     |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-3 **Unimplemented:** Read as '0'

bit 2 TMR5GIF: TMR5 Gate Interrupt Flag bit

1 = TMR5 gate interrupt occurred (must be cleared in software)

0 = No TMR5 gate occurred

bit 1 TMR3GIF: TMR3 Gate Interrupt Flag bit

1 = TMR3 gate interrupt occurred (must be cleared in software)

0 = No TMR3 gate occurred

bit 0 TMR1GIF: TMR1 Gate Interrupt Flag bit

1 = TMR1 gate interrupt occurred (must be cleared in software)

0 = No TMR1 gate occurred

## REGISTER 14-12: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|-----|-----|-----|---------|---------|

| HLVDIE  | ZCDIE   | _   | _   | _   | _   | C2IE    | C1IE    |

| bit 7   |         |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 HLVDIE: HLVD Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 ZCDIE: Zero-Cross Detect Interrupt Enable bit

1 = Enabled0 = Disabled

bit 5-2 **Unimplemented:** Read as '0'

bit 1 C2IE: Comparator 2 Interrupt Enable bit

1 = Enabled0 = Disabled

bit 0 C1IE: Comparator 1 Interrupt Enable bit

1 = Enabled0 = Disabled

# 18.8 Register Definitions: Timer0 Control

# REGISTER 18-1: TOCONO: TIMERO CONTROL REGISTER 0

| R/W-0/0 | U-0 | R-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----|-------|---------|---------|---------|---------|---------|

| T0EN    | _   | T0OUT | T016BIT |         | TOOUT   | PS<3:0> |         |

| bit 7   | •   |       |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | T0EN:TMR0 Enable bit                                                                 |  |  |  |  |

|---------|--------------------------------------------------------------------------------------|--|--|--|--|

|         | 1 = The module is enabled and operating                                              |  |  |  |  |

|         | 0 = The module is disabled and in the lowest power mode                              |  |  |  |  |

| bit 6   | Unimplemented: Read as '0'                                                           |  |  |  |  |

| bit 5   | TOOUT:TMR0 Output bit (read-only)                                                    |  |  |  |  |

|         | TMR0 output bit                                                                      |  |  |  |  |

| bit 4   | <b>T016BIT:</b> TMR0 Operating as 16-Bit Timer Select bit 1 = TMR0 is a 16-bit timer |  |  |  |  |

|         | 0 = TMR0 is an 8-bit timer                                                           |  |  |  |  |

| bit 3-0 | T00UTPS<3:0>: TMR0 Output Postscaler (Divider) Select bits                           |  |  |  |  |

|         | 1111 = 1:16 Postscaler                                                               |  |  |  |  |

|         | 1110 = 1:15 Postscaler                                                               |  |  |  |  |

|         | 1101 = 1:14 Postscaler                                                               |  |  |  |  |

|         | 1100 = 1:13 Postscaler                                                               |  |  |  |  |

|         | 1011 <b>= 1:12 Postscaler</b>                                                        |  |  |  |  |

|         | 1010 <b>= 1:11 Postscaler</b>                                                        |  |  |  |  |

|         | 1001 <b>= 1:10 Postscaler</b>                                                        |  |  |  |  |

|         | 1000 <b>= 1:9 Postscaler</b>                                                         |  |  |  |  |

|         | 0111 <b>= 1:8 Postscaler</b>                                                         |  |  |  |  |

|         | 0110 <b>= 1:7 Postscaler</b>                                                         |  |  |  |  |

|         | 0101 = 1:6 Postscaler                                                                |  |  |  |  |

|         | 0100 <b>= 1:5 Postscaler</b>                                                         |  |  |  |  |

|         | 0011 = 1:4 Postscaler                                                                |  |  |  |  |

|         | 0010 <b>= 1:3 Postscaler</b>                                                         |  |  |  |  |

|         | 0001 <b>= 1:2 Postscaler</b>                                                         |  |  |  |  |

|         | 0000 = 1:1 Postscaler                                                                |  |  |  |  |

# 20.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

## TABLE 21-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

# TABLE 21-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 21.5.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

# 21.5.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 4.0 "Oscillator Module (with Fail-Safe Clock Monitor)"** for additional details.

## 21.5.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

PIC18(L)F26/45/46K40

#### 26.9.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an  $\overline{ACK}$  pulse is sent by the slave on the ninth bit.

Following the  $\overline{ACK}$ , slave hardware clears the CKP bit and the SCL pin is held low (see **Section 26.9.6 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This  $\overline{ACK}$  value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the not  $\overline{ACK}$  is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 26.9.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIR register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 26.9.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 26-18 can be used as a reference to this list.

- Master sends a Start condition on SDA and SCI

- S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7. R/W is set so CKP was automatically cleared after the ACK.

- The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- **Note 1:** If the master  $\overline{\mathsf{ACK}}$ s the clock will be stretched.

- **2:** ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPxCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCL low and allowing SDA to float.

# 26.10.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPxSTAT register is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

## 26.10.6.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

The WCOL bit must be cleared by software before the next transmission.

## 26.10.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPxCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

## 26.10.6.4 Typical transmit sequence:

- The user generates a Start condition by setting the SEN bit of the SSPxCON2 register.

- SSPxIF is set by hardware on completion of the Start.

- 3. SSPxIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- The user loads the SSPxBUF with the slave address to transmit.

- Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPxBUF is written to.

- 7. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- The user loads the SSPxBUF with eight bits of data.

- Data is shifted out the SDA pin until all eight bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPxCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPxCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

TABLE 27-7: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name     | Bit 7                                 | Bit 6                          | Bit 5   | Bit 4     | Bit 3        | Bit 2      | Bit 1   | Bit 0   | Register<br>on Page |

|----------|---------------------------------------|--------------------------------|---------|-----------|--------------|------------|---------|---------|---------------------|

| BAUDxCON | ABDOVF                                | RCIDL                          | _       | SCKP      | BRG16        | _          | WUE     | ABDEN   | 395                 |

| INTCON   | GIE/GIEH                              | PEIE/GIEL                      | IPEN    | _         | _            | INT2EDG    | INT1EDG | INT0EDG | 170                 |

| PIE3     | RC2IE                                 | TX2IE                          | RC1IE   | TX1IE     | BCL2IE       | SSP2IE     | BCL1IE  | SSP1IE  | 182                 |

| PIR3     | RC2IF                                 | TX2IF                          | RC1IF   | TX1IF     | BCL2IF       | SSP2IF     | BCL1IF  | SSP1IF  | 174                 |

| IPR3     | RC2IP                                 | TX2IP                          | RC1IP   | TX1IP     | BCL2IP       | SSP2IP     | BCL1IP  | SSP1IP  | 190                 |

| RCxSTA   | SPEN                                  | RX9                            | SREN    | CREN      | ADDEN        | FERR       | OERR    | RX9D    | 394                 |

| RxyPPS   | _                                     | _                              | 1       |           |              | RxyPPS<4:0 | >       |         | 218                 |

| TXxPPS   | _                                     | _                              | 1       |           |              | TXPPS<4:0> | >       |         | 216                 |

| SPxBRGH  |                                       |                                | EUSARTx | Baud Rate | Generator, H | igh Byte   |         |         | 404*                |

| SPxBRGL  | EUSARTx Baud Rate Generator, Low Byte |                                |         |           |              | 404*       |         |         |                     |

| TXxREG   |                                       | EUSARTx Transmit Data Register |         |           |              |            | 396*    |         |                     |

| TXxSTA   | CSRC                                  | TX9                            | TXEN    | SYNC      | SENDB        | BRGH       | TRMT    | TX9D    | 393                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

<sup>\*</sup> Page provides register information.

## 31.2 ADC Operation

### 31.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. A conversion may be started by any of the following:

- Software setting the ADGO bit of ADCON0 to '1'

- An external trigger (selected by Register 31-3)

- A continuous-mode retrigger (see section Section 31.5.8 "Continuous Sampling mode")

Note: The ADGO bit should not be set in the same instruction that turns on the ADC. Refer to Section 31.2.6 "ADC Conversion Procedure (Basic Mode)".

## 31.2.2 COMPLETION OF A CONVERSION

When any individual conversion is complete, the value already in ADRES is written into ADPREV (if ADPSIS = 1) and the new conversion results appear in ADRES. When the conversion completes, the ADC module will:

- Clear the ADGO bit (unless the ADCONT bit of ADCON0 is set)

- · Set the ADIF Interrupt Flag bit

- · Set the ADMATH bit

- Update ADACC

When ADDSEN = 0 then after every conversion, or when ADDSEN = 1 then after every other conversion, the following events occur:

- · ADERR is calculated

- ADTIF is set if ADERR calculation meets threshold comparison

Importantly, filter and threshold computations occur after the conversion itself is complete. As such, interrupt handlers responding to ADIF should check ADTIF before reading filter and threshold results.

#### 31.2.3 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

# 31.2.4 EXTERNAL TRIGGER DURING SLEEP

If the external trigger is received during sleep while ADC clock source is set to the FRC, ADC module will perform the conversion and set the ADIF bit upon completion.

If an external trigger is received when the ADC clock source is something other than FRC, the trigger will be recorded, but the conversion will not begin until the device exits Sleep.

## 31.2.5 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the ADGO bit is set by hardware.

The Auto-conversion Trigger source is selected with the ADACT<4:0> bits of the ADACT register.

Using the Auto-conversion Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. See Table 31-2 for auto-conversion sources.

TABLE 31-2: ADC AUTO-CONVERSION TABLE

| Source<br>Peripheral | Description                                           |

|----------------------|-------------------------------------------------------|

| ADCACTPPS            | Pin selected by ADCACTPPS                             |

| TMR0                 | Timer0 overflow condition                             |

| TMR1/3/5             | Timer1/3/5 overflow condition                         |

| TMR2/4/6             | Match between Timer2/4/6 postscaled value and PR2/4/6 |

| CCP1/2               | CCP1/2 output                                         |

| PWM3/4               | PWM3/4 output                                         |

| C1/2                 | Comparator C1/2 output                                |

| IOC                  | Interrupt-on-change interrupt trigger                 |

| ADERR                | Read of ADERRH register                               |

| ADRESH               | Read of ADRESH register                               |

| ADPCH                | Write of ADPCH register                               |

# 31.4 Capacitive Voltage Divider (CVD) Features

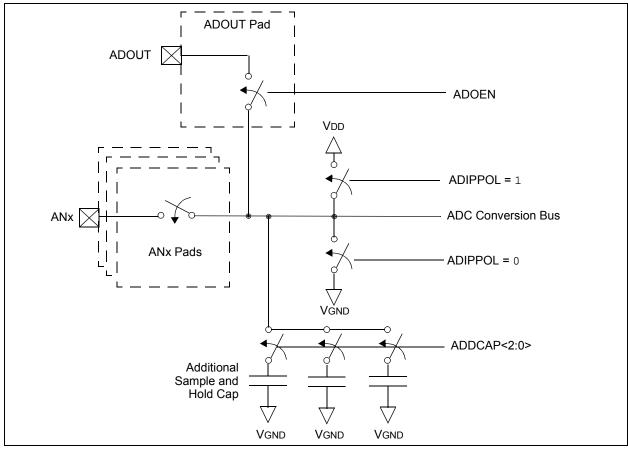

The ADC module contains several features that allow the user to perform a relative capacitance measurement on any ADC channel using the internal ADC sample and hold capacitance as a reference. This relative capacitance measurement can be used to implement capacitive touch or proximity sensing applications. Figure 31-6 shows the basic block diagram of the CVD portion of the ADC module.

FIGURE 31-6: HARDWARE CAPACITIVE VOLTAGE DIVIDER BLOCK DIAGRAM

# PIC18(L)F26/45/46K40

| BCF              | Bit Clear                                                                       | f      |      |      |

|------------------|---------------------------------------------------------------------------------|--------|------|------|

| Syntax:          | BCF f, b                                                                        | ) {,a} |      |      |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                           | 5      |      |      |

| Operation:       | $0 \rightarrow f < b >$                                                         |        |      |      |

| Status Affected: | None                                                                            |        |      |      |

| Encoding:        | 1001                                                                            | bbba   | ffff | ffff |

| Description:     | Bit 'b' in register 'f' is cleared.  If 'a' is '0' the Access Bank is selected. |        |      |      |

If 'a' is '0', the Access Bank is selected.

If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BCF FLAG\_REG, 7, 0

Before Instruction

FLAG\_REG = C7h

After Instruction

FLAG\_REG = 47h

| BN | Branch if Negative |

|----|--------------------|

|----|--------------------|

Syntax: BN n

Operands:  $-128 \le n \le 127$

Operation: if NEGATIVE bit is '1'  $(PC) + 2 + 2n \rightarrow PC$

(1 0) . 2 . 211

Status Affected: None

Encoding: 1110 0110 nnnn nnnn

Description: If the NEGATIVE bit is '1', then the program will branch.

The 2's complement number '2n' is

added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words: 1

Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | 'n'          | Data    | operation |

Example: HERE BN Jump

Before Instruction

PC = address (HERE)

After Instruction

If NEGATIVE = 1;

PC = address (Jump)

If NEGATIVE = 0

PC = address (HERE + 2)

# PIC18(L)F26/45/46K40

| CLRF             | Clear f                                                                                   |      |      |      |

|------------------|-------------------------------------------------------------------------------------------|------|------|------|

| Syntax:          | CLRF f{                                                                                   | ,a}  |      |      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                           |      |      |      |

| Operation:       | $000h \rightarrow f$ $1 \rightarrow Z$                                                    |      |      |      |

| Status Affected: | Z                                                                                         |      |      |      |

| Encoding:        | 0110                                                                                      | 101a | ffff | ffff |

| Description:     | Clears the contents of the specified register.  If 'a' is '0' the Access Bank is selected |      |      |      |

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: CLRF FLAG\_REG, 1

Before Instruction

FLAG\_REG = 5Ah

After Instruction

$FLAG_REG = 00h$

CLRWDT Clear Watchdog Timer

Syntax: CLRWDT Operands: None

Operation:  $000h \rightarrow WDT$ ,

$\begin{array}{c} 000h \xrightarrow{\longrightarrow} WDT \text{ postscaler,} \\ 1 \xrightarrow{\longrightarrow} TO, \end{array}$

$\begin{array}{c}

1 \to \overline{PD} \\

\overline{TO}, \overline{PD}

\end{array}$

**Encoding**: 0000 0000 0000

Description: CLRWDT instruction resets the

Watchdog Timer. It also resets the post-scaler of the WDT. Status bits, TO and

0100

PD, are set.

Words: 1

Cycles: 1

Q Cycle Activity:

Status Affected:

| Q1     | Q2        | Q3      | Q4        |

|--------|-----------|---------|-----------|

| Decode | No        | Process | No        |

|        | operation | Data    | operation |

Example: CLRWDT

Before Instruction

WDT Counter = ?

After Instruction

WDT Counter

=

00h

WDT Postscaler

=

0

TO

=

1

PD

=

1

## 35.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18(L)F2x/4xK40 devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for indexed addressing. Two of the instructions,  ${\tt ADDFSR}$  and  ${\tt SUBFSR},$  each have an additional special instantiation for using FSR2. These versions ( ${\tt ADDULNK}$  and  ${\tt SUBULNK}$ ) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- · function pointer invocation

- · software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 35-3. Detailed descriptions are provided in **Section 35.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 35-1 apply to both the standard and extended PIC18 instruction sets.

| Note: | The instruction set extension and the       |

|-------|---------------------------------------------|

|       | Indexed Literal Offset Addressing mode      |

|       | were designed for optimizing applications   |

|       | written in C; the user may likely never use |

|       | these instructions directly in assembler.   |

|       | The syntax for these commands is pro-       |

|       | vided as a reference for users who may be   |

|       | reviewing code that has been generated      |

|       | by a compiler.                              |

#### 35.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. MPASM™ Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byte-oriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 35.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

| Note: | In the past, square brackets have been used to denote optional arguments in the |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | PIC18 and earlier instruction sets. In this                                     |  |  |  |  |  |  |  |

|       | text and going forward, optional                                                |  |  |  |  |  |  |  |

|       | arguments are denoted by braces ("{ }").                                        |  |  |  |  |  |  |  |

TABLE 35-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

| Mnemonic,<br>Operands |               | Description                              | Cycles | 16-Bit Instruction Word |      |      |      | Status   |

|-----------------------|---------------|------------------------------------------|--------|-------------------------|------|------|------|----------|

|                       |               |                                          |        | MSb                     |      |      | LSb  | Affected |

| ADDFSR                | f, k          | Add literal to FSR                       | 1      | 1110                    | 1000 | ffkk | kkkk | None     |

| ADDULNK               | k             | Add literal to FSR2 and return           | 2      | 1110                    | 1000 | 11kk | kkkk | None     |

| CALLW                 |               | Call subroutine using WREG               | 2      | 0000                    | 0000 | 0001 | 0100 | None     |

| MOVSF                 | $z_s$ , $f_d$ | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 0zzz | ZZZZ | None     |

|                       |               | f <sub>d</sub> (destination) 2nd word    |        | 1111                    | ffff | ffff | ffff |          |

| MOVSS                 | $z_s, z_d$    | Move z <sub>s</sub> (source) to 1st word | 2      | 1110                    | 1011 | 1zzz | ZZZZ | None     |

|                       |               | z <sub>d</sub> (destination) 2nd word    |        | 1111                    | xxxx | XZZZ | ZZZZ |          |

| PUSHL                 | k             | Store literal at FSR2,<br>decrement FSR2 | 1      | 1110                    | 1010 | kkkk | kkkk | None     |

| SUBFSR                | f, k          | Subtract literal from FSR                | 1      | 1110                    | 1001 | ffkk | kkkk | None     |

| SUBULNK               | k             | Subtract literal from FSR2 and return    | 2      | 1110                    | 1001 | 11kk | kkkk | None     |

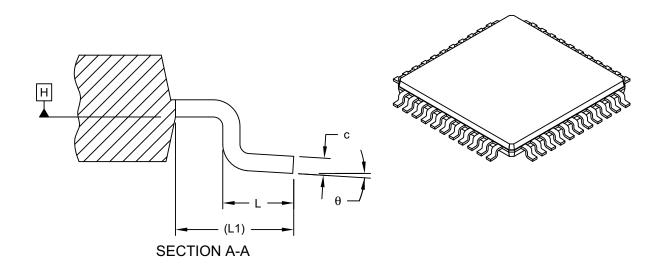

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |  |

|--------------------------|-------------|-----------|------|------|--|--|

| Dimension                | MIN         | NOM       | MAX  |      |  |  |

| Number of Leads          | N           | 44        |      |      |  |  |

| Lead Pitch               | е           | 0.80 BSC  |      |      |  |  |

| Overall Height           | Α           | 1.20      |      |      |  |  |

| Standoff                 | A1          | 0.05      | -    | 0.15 |  |  |

| Molded Package Thickness | A2          | 0.95      | 1.00 | 1.05 |  |  |

| Overall Width            |             | 12.00 BSC |      |      |  |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |  |

| Lead Width               | b           | 0.30      | 0.37 | 0.45 |  |  |

| Lead Thickness           | С           | 0.09      | -    | 0.20 |  |  |

| Lead Length              | L           | 0.45      | 0.60 | 0.75 |  |  |

| Footprint L1             |             | 1.00 REF  |      |      |  |  |

| Foot Angle               | θ           | 0°        | 3.5° | 7°   |  |  |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Exact shape of each corner is optional.

- 3. Dimensioning and tolerancing per ASME Y14.5M

${\tt BSC: Basic \ Dimension. \ Theoretically \ exact \ value \ shown \ without \ tolerances.}$

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2