Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k40t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

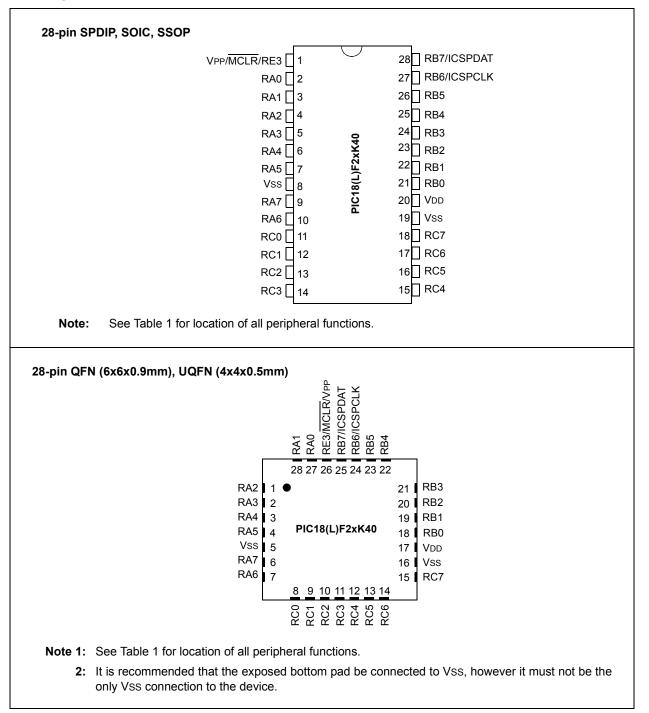

# **Pin Diagrams**

| IADL               | ABLE 2: 40/44-PIN ALLOCATION TABLE (PIC18(L)F45/46K40) (CONTINUED) |             |                  |             |                |           |                              |                                  |                     |     |                                                                                                      |           |                              |     |                                              |                    |          |

|--------------------|--------------------------------------------------------------------|-------------|------------------|-------------|----------------|-----------|------------------------------|----------------------------------|---------------------|-----|------------------------------------------------------------------------------------------------------|-----------|------------------------------|-----|----------------------------------------------|--------------------|----------|

| I/O <sup>(2)</sup> | 40-Pin PDIP                                                        | 40-Pin UQFN | 44-Pin QFN       | 44-Pin TQFP | A/D            | Reference | Comparator                   | Timers                           | ссР                 | ЭМЭ | ZCD                                                                                                  | Interrupt | EUSART                       | WSQ | MSSP                                         | dn-llud            | Basic    |

| RC2                | 17                                                                 | 32          | 36               | 36          | ANC2           | _         | _                            | T5CKI <sup>(1)</sup>             | CCP1 <sup>(1)</sup> | _   | _                                                                                                    | IOCC2     | _                            | _   | _                                            | Y                  | _        |

| RC3                | 18                                                                 | 33          | 37               | 37          | ANC3           | _         | —                            | T2AIN <sup>(1)</sup>             | —                   | _   | —                                                                                                    | IOCC3     | —                            | _   | SCK1 <sup>(1)</sup><br>SCL1 <sup>(3,4)</sup> | Y                  | _        |

| RC4                | 23                                                                 | 38          | 42               | 42          | ANC4           | _         | _                            | —                                | —                   | _   | —                                                                                                    | IOCC4     | —                            | _   | SDI1 <sup>(1)</sup><br>SDA1 <sup>(3,4)</sup> | —                  | _        |

| RC5                | 24                                                                 | 39          | 43               | 43          | ANC5           | _         | _                            | T4AIN <sup>(1)</sup>             | _                   | _   | _                                                                                                    | IOCC5     | _                            | _   | _                                            | Y                  | _        |

| RC6                | 25                                                                 | 40          | 44               | 44          | ANC6           | _         | _                            | _                                | _                   | _   | _                                                                                                    | IOCC6     | CK1 <sup>(1)</sup>           | _   | _                                            | Y                  | _        |

| RC7                | 26                                                                 | 1           | 1                | 1           | ANC7           | _         | _                            | _                                | _                   | -   | _                                                                                                    | IOCC7     | RX1/DT1 <sup>(1)</sup>       | _   | _                                            | Y                  |          |

| RD0                | 19                                                                 | 34          | 38               | 38          | AND0           | _         | _                            | _                                | _                   | _   | _                                                                                                    | IOCD0     | _                            | _   | _                                            | Y                  | _        |

| RD1                | 20                                                                 | 35          | 39               | 39          | AND1           | _         | _                            | _                                | _                   | _   | _                                                                                                    | IOCD1     | _                            | _   | _                                            | Y                  | _        |

| RD2                | 21                                                                 | 36          | 40               | 40          | AND2           | _         | —                            | _                                | _                   | _   | _                                                                                                    | IOCD2     | _                            | _   |                                              | Y                  | _        |

| RD3                | 22                                                                 | 37          | 41               | 41          | AND3           | _         | _                            | _                                | _                   | _   | _                                                                                                    | IOCD3     | _                            | _   | —                                            | Y                  | _        |

| RD4                | 27                                                                 | 2           | 2                | 2           | AND4           | _         | _                            | _                                | _                   | _   | _                                                                                                    | IOCD4     | _                            | _   | —                                            | Y                  | _        |

| RD5                | 28                                                                 | 3           | 3                | 3           | AND5           | _         | _                            | -                                | _                   | _   | _                                                                                                    | IOCD5     | _                            | _   | —                                            | Y                  | _        |

| RD6                | 29                                                                 | 4           | 4                | 4           | AND6           | _         | _                            | _                                | _                   | _   | _                                                                                                    | IOCD6     | _                            | _   | —                                            | Y                  | _        |

| RD7                | 30                                                                 | 5           | 5                | 5           | AND7           |           | —                            | _                                | —                   |     | —                                                                                                    | IOCD7     | _                            | _   | —                                            | Y                  | _        |

| RE0                | 8                                                                  | 23          | 25               | 25          | ANE0           |           | —                            | _                                | _                   |     | —                                                                                                    | —         | _                            | —   | —                                            | Y                  | _        |

| RE1                | 9                                                                  | 24          | 26               | 26          | ANE1           |           | —                            | —                                | _                   |     | —                                                                                                    | —         | —                            | —   | —                                            | Y                  | _        |

| RE2                | 10                                                                 | 25          | 27               | 27          | ANE2           | _         | —                            | —                                | —                   | —   | —                                                                                                    | —         | —                            | —   | —                                            | Y                  | —        |

| RE3                | 1                                                                  | 16          | 18               | 18          | —              | _         | —                            | —                                | _                   | _   | —                                                                                                    | IOCE3     | —                            | _   | _                                            | Y                  | VPP/MCLR |

| Vss                | 12                                                                 | 6           | 6                | 6           | —              | _         | —                            | —                                | —                   | _   | —                                                                                                    | —         | —                            | _   | _                                            | —                  | Vss      |

| VDD                | 11                                                                 | 7           | 7                | 7           | _              |           | _                            | _                                | _                   | _   | _                                                                                                    | _         | _                            | _   | _                                            |                    | Vdd      |

| VDD                | 32                                                                 | 26          | 28               | 28          | —              | _         | —                            | —                                | —                   | _   | —                                                                                                    | —         | —                            | _   | _                                            | —                  | Vdd      |

| Vss                | 31                                                                 | 27          | 30               | 29          | —              | _         | —                            | —                                | —                   | _   | —                                                                                                    | —         | —                            | _   | —                                            | —                  | Vss      |

| OUT <sup>(2)</sup> | _                                                                  | _           | ADGRDA<br>ADGRDB | _           | C1OUT<br>C2OUT | TMR0      | CCP1<br>CCP2<br>PWM3<br>PWM4 | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D | _                   | _   | TX1/<br>CK1 <sup>(3)</sup><br>DT1 <sup>(3)</sup><br>TX2/<br>CK2 <sup>(3)</sup><br>DT2 <sup>(3)</sup> | DSM       | SDO1<br>SCK1<br>SDO2<br>SCK2 | _   | _                                            | OUT <sup>(2)</sup> | _        |

#### TABLE 2: 40/44-PIN ALLOCATION TABLE (PIC18(L)F45/46K40) (CONTINUED)

**Note** 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I2C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I2C specific or SMBus input buffer thresholds.

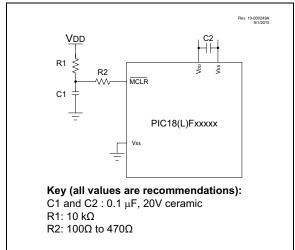

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18(L)F26/45/46K40 MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18(L)F26/45/46K40 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP<sup>™</sup> Pins"**)

- OSCI and OSCO pins when an external oscillator source is used (see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

The minimum mandatory connections are shown in Figure 2-1.

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

# 2.2 Power Supply Pins

# 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins (VDD and VSS) is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

# 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 4.2 Register Definitions: Oscillator Control

REGISTER 4-1: OSCCON1: OSCILLATOR CONTROL REGISTER1

| U-0                               | R/W-f/f | R/W-f/f   | R/W-f/f | R/W-q/q      | R/W-q/q          | R/W-q/q  | R/W-q/q |  |  |

|-----------------------------------|---------|-----------|---------|--------------|------------------|----------|---------|--|--|

| —                                 |         | NOSC<2:0> |         | NDIV<3:0>    |                  |          |         |  |  |

| bit 7                             |         |           |         |              |                  |          | bit 0   |  |  |

|                                   |         |           |         |              |                  |          |         |  |  |

| Legend:                           |         |           |         |              |                  |          |         |  |  |

| R = Readable bit W = Writable bit |         |           |         | U = Unimpler | nented bit, read | d as '0' |         |  |  |

|                      |                      | 0 - Onimplemented bit, read as 0                      |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by fuse setting                        |

|                      |                      | q = Reset value is determined by hardware             |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits <sup>(1,2,3)</sup>            |

|         | The setting requests a source oscillator and PLL combination per Table 4-2. |

|         | POR value = RSTOSC (Register 3-1).                                          |

| bit 3-0 | NDIV<3:0>: New Divider Selection Request bits <sup>(2,3)</sup>              |

The setting determines the new postscaler division ratio per Table 4-2.

- Note1: The default value (f/f) is determined by the RSTOSC Configuration bits. See Table 4-1below.

- 2: If NOSC is written with a reserved value (Table 4-2), the operation is ignored and neither NOSC nor NDIV is written.

- 3: When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

| TABLE 4-1: | DEFAULT OSCILLATOR SETTINGS USING RSTOSC BITS |

|------------|-----------------------------------------------|

|------------|-----------------------------------------------|

| DOTOCO | SF        | R Reset Value | S       |                        |  |  |  |  |  |

|--------|-----------|---------------|---------|------------------------|--|--|--|--|--|

| RSTOSC | NOSC/COSC | CDIV          | OSCFRQ  | Initial Fosc Frequency |  |  |  |  |  |

| 111    | 111       | 1:1           |         | EXTOSC per FEXTOSC     |  |  |  |  |  |

| 110    | 110       | 4:1           | 4 1411- | Fosc = 1 MHz (4 MHz/4) |  |  |  |  |  |

| 101    | 101       | 1:1           | 4 MHz   | LFINTOSC               |  |  |  |  |  |

| 100    | 100       | 1:1           |         | SOSC                   |  |  |  |  |  |

| 011    |           |               | Reserve | ed                     |  |  |  |  |  |

| 010    | 010       | 1:1           | 4 MHz   | EXTOSC + 4xPLL (1)     |  |  |  |  |  |

| 001    |           | Reserved      |         |                        |  |  |  |  |  |

| 000    | 110       | 1:1           | 64 MHz  | Fosc = 64 MHz          |  |  |  |  |  |

**Note 1:** EXTOSC must meet the PLL specifications (Table 37-9).

| TADLE IT-J.        | TABLE I OINTER OF ERATIONS WITH THERE AND THEM INSTRUCTIONS |  |  |  |  |  |

|--------------------|-------------------------------------------------------------|--|--|--|--|--|

| Example            | Operation on Table Pointer                                  |  |  |  |  |  |

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                                      |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write                  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write                  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write                 |  |  |  |  |  |

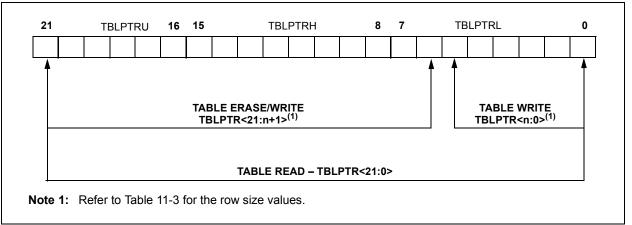

# TABLE 11-3: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

#### **FIGURE 11-3**:

TABLE POINTER BOUNDARIES BASED ON OPERATION

# 13.9 Program Memory Scan Configuration

If desired, the program memory scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the scanner to work with the CRC you need to perform the following steps:

- Set the Enable bit in both the CRCCON0 and SCANCON0 registers. If they get disabled, all internal states of the scanner and the CRC are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 13.11 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 13.11.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- 5. The CRCGO bit must be set before setting the SCANGO bit. Setting the SCANGO bit starts the scan. Both CRCEN and CRCGO bits must be enabled to use the scanner. When either of these bits are disabled, the scan aborts and the INVALID bit SCANCON0 is set. The scanner will wait for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

# 13.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

# 13.11 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 13-2.

# 13.11.1 BURST MODE

When MODE = 01, the scanner is in Burst mode. In Burst mode, CPU operation is stalled beginning with the operation after the one that sets the SCANGO bit, and the scan begins, using the instruction clock to execute. The CPU is held in its current state until the scan stops. Note that because the CPU is not executing instructions, the SCANGO bit cannot be cleared in software, so the CPU will remain stalled until one of the hardware endconditions occurs. Burst mode has the highest throughput for the scanner, but has the cost of stalling other execution while it occurs.

# 13.11.2 CONCURRENT MODE

When MODE = 00, the scanner is in Concurrent mode. Concurrent mode, like Burst mode, stalls the CPU while performing accesses of memory. However, while Burst mode stalls until all accesses are complete, Concurrent mode allows the CPU to execute in between access cycles.

#### 13.11.3 TRIGGERED MODE

When MODE = 11, the scanner is in Triggered mode. Triggered mode behaves identically to Concurrent mode, except instead of beginning the scan immediately upon the SCANGO bit being set, it waits for a rising edge from a separate trigger clock, the source of which is determined by the SCANTRIG register.

# 13.11.4 PEEK MODE

When MODE = 10, the scanner is in Peek mode. Peek mode waits for an instruction cycle in which the CPU does not need to access the NVM (such as a branch instruction) and uses that cycle to do its own NVM access. This results in the lowest throughput for the NVM access (and can take a much longer time to complete a scan than the other modes), but does so without any impact on execution times, unlike the other modes.

| R/W-1/1       | R/W-1/1                                                                        | R/W-1/1                                            | R/W-1/1           | R/W-1/1           | R/W-1/1         | R/W-1/1         | R/W-1/1 |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------|----------------------------------------------------|-------------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|

| RC2IP         | TX2IP                                                                          | RC1IP                                              | TX1IP             | BCL2IP            | SSP2IP          | BCL1IP          | SSP1IP  |  |  |  |  |  |

| bit 7         |                                                                                |                                                    |                   |                   |                 |                 | bit (   |  |  |  |  |  |

|               |                                                                                |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

| Legend:       |                                                                                |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

| R = Readable  | e bit                                                                          | W = Writable                                       | bit               | •                 | nented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value at | POR                                                                            | '1' = Bit is set                                   |                   | '0' = Bit is clea | ared            | x = Bit is unki | nown    |  |  |  |  |  |

| bit 7         | RC2IP: FUS                                                                     | ART2 Receive                                       | Interrunt Priori  | ity hit           |                 |                 |         |  |  |  |  |  |

|               | 1 = High pri                                                                   |                                                    | interrupt i non   |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Low price                                                                  |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

| bit 6         | TX2IP: EUS                                                                     | ART2 Transmit                                      | Interrupt Prior   | ity bit           |                 |                 |         |  |  |  |  |  |

|               | 1 = High prie                                                                  | •                                                  |                   |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Low price                                                                  | ority                                              |                   |                   |                 |                 |         |  |  |  |  |  |

| bit 5         |                                                                                | ART1 Receive                                       | Interrupt Priori  | ity bit           |                 |                 |         |  |  |  |  |  |

|               | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul>                |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

| h:+ 4         | •                                                                              | •                                                  |                   | :4. / L. :4       |                 |                 |         |  |  |  |  |  |

| bit 4         | 1 = High prior                                                                 | ART1 Transmit                                      | interrupt Phor    |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Low price                                                                  |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

| bit 3         | •                                                                              | -                                                  | ion Interrupt P   | riority bit       |                 |                 |         |  |  |  |  |  |

|               | <b>BCL2IP:</b> MSSP2 Bus Collision Interrupt Priority bit<br>1 = High priority |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Low priority                                                               |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

| bit 2         | SSP2IP: Syr                                                                    | nchronous Seria                                    | al Port 2 Interru | upt Priority bit  |                 |                 |         |  |  |  |  |  |

|               | 1 = High priority                                                              |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Low price                                                                  | •                                                  |                   |                   |                 |                 |         |  |  |  |  |  |

| bit 1         |                                                                                | BCL1IP: MSSP1 Bus Collision Interrupt Priority bit |                   |                   |                 |                 |         |  |  |  |  |  |

|               | 1 = High prid0 = Low prid                                                      | •                                                  |                   |                   |                 |                 |         |  |  |  |  |  |

| bit 0         | •                                                                              | nchronous Seria                                    | al Port 1 Intern  | int Priority hit  |                 |                 |         |  |  |  |  |  |

|               | 1 = High pri                                                                   |                                                    |                   |                   |                 |                 |         |  |  |  |  |  |

|               | 0 = Low price                                                                  | ,                                                  |                   |                   |                 |                 |         |  |  |  |  |  |

# REGISTER 14-21: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|--------|-----------------------|--------|--------|--------|

| IOCAP | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3                | IOCAP2 | IOCAP1 | IOCAP0 |

| IOCAN | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3                | IOCAN2 | IOCAN1 | IOCAN0 |

| IOCAF | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3                | IOCAF2 | IOCAF1 | IOCAF0 |

| IOCBP | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3                | IOCBP2 | IOCBP1 | IOCBP0 |

| IOCBN | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3                | IOCBN2 | IOCBN1 | IOCBN0 |

| IOCBF | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3                | IOCBF2 | IOCBF1 | IOCBF0 |

| IOCCP | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3                | IOCCP2 | IOCCP1 | IOCCP0 |

| IOCCN | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3                | IOCCN2 | IOCCN1 | IOCCN0 |

| IOCCF | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3                | IOCCF2 | IOCCF1 | IOCCF0 |

| IOCEP | —      | _      | _      | _      | IOCEP3 <sup>(1)</sup> | _      | —      | —      |

| IOCEN |        |        |        |        | IOCEN3 <sup>(1)</sup> |        |        |        |

| IOCEF |        |        |        |        | IOCEF3 <sup>(1)</sup> |        |        | _      |

TABLE 16-1: IOC REGISTERS

Note 1: If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and IOC on RE3 is not available.

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|--------|----------|-----------|--------|--------|--------|---------|---------|---------|---------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | IPEN   | —      | —      | INT2EDG | INT1EDG | INT0EDG | 170                 |

| IOCxF  | IOCxF7   | IOCxF6    | IOCxF5 | IOCxF4 | IOCxF3 | IOCxF2  | IOCxF1  | IOCxF0  | 211                 |

| IOCxN  | IOCxN7   | IOCxN6    | IOCxN5 | IOCxN4 | IOCxN3 | IOCxN2  | IOCxN1  | IOCxN0  | 211                 |

| IOCxP  | IOCxP7   | IOCxP6    | IOCxP5 | IOCxP4 | IOCxP3 | IOCxP2  | IOCxP1  | IOCxP0  | 211                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

| R/W-0/u       | R/W-0/u                                                | R/W-0/u                                                                                                                                                                                        | R/W-0/u         | R/W-0/u             | R-x              | U-0             | U-0   |  |  |

|---------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|------------------|-----------------|-------|--|--|

| GE            | GPOL                                                   | GTM                                                                                                                                                                                            | GSPM            | GGO/DONE            | GVAL             |                 | _     |  |  |

| bit 7         | -                                                      |                                                                                                                                                                                                |                 |                     |                  |                 | bit C |  |  |

| Legend:       |                                                        |                                                                                                                                                                                                |                 |                     |                  |                 |       |  |  |

| R = Readable  | e bit                                                  | W = Writable                                                                                                                                                                                   | bit             | U = Unimpleme       | nted bit, read a | ıs '0'          |       |  |  |

| -n = Value at | POR                                                    | '1' = Bit is se                                                                                                                                                                                | t               | '0' = Bit is cleare |                  | x = Bit is unkr | nown  |  |  |

| bit 7         | If TMRxON =<br>1 = Timerx<br>0 = Timerx<br>If TMRxON = | counting is co<br>is always cou                                                                                                                                                                | ontrolled by th | e Timerx gate fur   | ction            |                 |       |  |  |

| bit 6         | GPOL: Time                                             | <b>POL:</b> Timerx Gate Polarity bit<br>Timerx gate is active-high (Timerx counts when gate is high)                                                                                           |                 |                     |                  |                 |       |  |  |

| bit 5         | 1 = Timerx<br>0 = Timerx                               | GTM: Timerx Gate Toggle Mode bit                                                                                                                                                               |                 |                     |                  |                 |       |  |  |

| bit 4         | <b>GSPM:</b> Time<br>1 = Timerx                        | <ul> <li>PM: Timerx Gate Single Pulse Mode bit</li> <li>Timerx Gate Single Pulse mode is enabled and is controlling Timerx gate)</li> <li>Timerx Gate Single Pulse mode is disabled</li> </ul> |                 |                     |                  |                 |       |  |  |

| bit 3         | GGO/DONE<br>1 = Timerx<br>0 = Timerx                   | <b>GO/DONE:</b> Timerx Gate Single Pulse Acquisition Status bit<br>= Timerx Gate Single Pulse Acquisition is ready, waiting for an edge                                                        |                 |                     |                  |                 |       |  |  |

| bit 2         | GVAL: Time<br>Indicates the                            | AL: Timerx Gate Current State bit<br>cates the current state of the Timerx gate that could be provided to TMRxH:TMRxL<br>ffected by Timerx Gate Enable (TMRxGE)                                |                 |                     |                  |                 |       |  |  |

| bit 1-0       | Unimpleme                                              | Unimplemented: Read as '0'                                                                                                                                                                     |                 |                     |                  |                 |       |  |  |

# REGISTER 19-2: TxGCON: TIMERx GATE CONTROL REGISTER

#### REGISTER 19-3: TMRxCLK: TIMERx CLOCK REGISTER

| -         -         CS<3:0>           bit 7         -         -         -         CS<3:0> | -0/u  | R/W-0/u R/W-0/ | R/W-0/u | R/W-0/u | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------|-------|----------------|---------|---------|-----|-----|-----|-------|

| bit 7                                                                                     |       | 3:0>           | CS      |         | _   | —   | —   | —     |

|                                                                                           | bit 0 | ł              |         |         |     |     |     | bit 7 |

|                                                                                           |       |                |         |         |     |     |     |       |

| Legend:           |                  |                             |               |

|-------------------|------------------|-----------------------------|---------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | u = unchanged |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 **CS<3:0>:** Timerx Clock Source Selection bits

| cs        | Timer1             | Timer3             | Timer5             |

|-----------|--------------------|--------------------|--------------------|

| 03        | Clock Source       | Clock Source       | Clock Source       |

| 1111-1100 | Reserved           | Reserved           | Reserved           |

| 1011      | TMR5 overflow      | TMR5 overflow      | Reserved           |

| 1010      | TMR3 overflow      | Reserved           | TMR3 overflow      |

| 1001      | Reserved           | TMR1 overflow      | TMR1 overflow      |

| 1000      | TMR0 overflow      | TMR0 overflow      | TMR0 overflow      |

| 0111      | CLKREF             | CLKREF             | CLKREF             |

| 0110      | SOSC               | SOSC               | SOSC               |

| 0101      | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) |

| 0100      | LFINTOSC           | LFINTOSC           | LFINTOSC           |

| 0011      | HFINTOSC           | HFINTOSC           | HFINTOSC           |

| 0010      | Fosc               | Fosc               | Fosc               |

| 0001      | Fosc/4             | Fosc/4             | Fosc/4             |

| 0000      | T1CKIPPS           | T3CKIPPS           | T5CKIPPS           |

#### 20.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 20-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

| Rev. 10.000 1988<br>5/30/2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| TMRx_ers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PRx 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| $TMRx \left( \begin{array}{c} 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2$ |  |

| TMRx_postscaled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| PWM Duty   3     Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

#### 26.9.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 26-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- 2. Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

Note: If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

# 26.9.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 26-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 26-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| Name     | Bit 7                                  | Bit 6     | Bit 5   | Bit 4                           | Bit 4 Bit 3 Bit 2 Bit 1 Bit 0     |        |        |        |      |  |

|----------|----------------------------------------|-----------|---------|---------------------------------|-----------------------------------|--------|--------|--------|------|--|

| BAUDxCON | ABDOVF                                 | RCIDL     |         | SCKP                            | SCKP BRG16 — WUE ABDEN            |        |        |        |      |  |

| INTCON   | GIE/GIEH                               | PEIE/GIEL | IPEN    | -                               | — — INT2EDG INT1EDG INT0EDG       |        |        |        |      |  |

| PIE3     | RC2IE                                  | TX2IE     | RC1IE   | TX1IE                           | BCL2IE                            | SSP2IE | BCL1IE | SSP1IE | 182  |  |

| PIR3     | RC2IF                                  | TX2IF     | RC1IF   | TX1IF                           | TX1IF BCL2IF SSP2IF BCL1IF SSP1IF |        |        |        |      |  |

| IPR3     | RC2IP                                  | TX2IP     | RC1IP   | TX1IP                           | TX1IP BCL2IP SSP2IP BCL1IP SSP1IP |        |        |        |      |  |

| RCxREG   |                                        |           | EL      | JSARTx Rec                      | RTx Receive Register              |        |        |        | 399* |  |

| RCxSTA   | SPEN                                   | RX9       | SREN    | CREN                            | CREN ADDEN FERR OERR RX9D         |        |        |        |      |  |

| RxyPPS   | _                                      | _         | _       |                                 | RxyPPS<4:0>                       |        |        |        | 218  |  |

| RXxPPS   | _                                      | _         | _       |                                 | RXPPS<4:0>                        |        |        |        |      |  |

| SPxBRGH  | EUSARTx Baud Rate Generator, High Byte |           |         |                                 |                                   | 404*   |        |        |      |  |

| SPxBRGL  |                                        |           | EUSART> | x Baud Rate Generator, Low Byte |                                   |        |        | 404*   |      |  |

| TXxSTA   | CSRC                                   | TX9       | TXEN    | SYNC                            | SENDB                             | BRGH   | TRMT   | TX9D   | 393  |  |

### TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception. \* Page provides register information.

| FIGURE 27-12:                                       | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                    |

|-----------------------------------------------------|------------------------------------------------------------------------------|

| RXx/DTx<br>pin<br>TXx/CKx pin<br>(SCKP = 0)         |                                                                              |

| TXx/CKx pin<br>(SCKP = 1)<br>Write to<br>bit SREN   |                                                                              |

| SREN bit                                            | ·0'                                                                          |

| RCxIF bit<br>(Interrupt) ———<br>Read<br>RCxREG ———— |                                                                              |

| Note: Timing dia                                    | agram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

# TABLE 27-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name     | Bit 7    | Bit 6                                  | Bit 5   | Bit 4       | Bit 4 Bit 3 Bit 2 Bit 1 Bit 0           |         |      |      |      |  |

|----------|----------|----------------------------------------|---------|-------------|-----------------------------------------|---------|------|------|------|--|

| ANSELB   | ANSELB7  | ANSELB6                                | ANSELB5 | ANSELB4     | NSELB4 ANSELB3 ANSELB2 ANSELB1 ANSELB0  |         |      |      |      |  |

| ANSELC   | ANSELC7  | ANSELC6                                | ANSELC5 | ANSELC4     | ANSELC4 ANSELC3 ANSELC2 ANSELC1 ANSELC0 |         |      |      |      |  |

| BAUDxCON | ABDOVF   | RCIDL                                  |         | SCKP        | SCKP BRG16 — WUE ABDEN                  |         |      |      |      |  |

| INTCON   | GIE/GIEH | PEIE/GIEL                              | IPEN    | -           | — — INT2EDG INT1EDG INT0EDG             |         |      |      |      |  |

| PIE3     | RC2IE    | TX2IE                                  | RC1IE   | TX1IE       | TX1IE BCL2IE SSP2IE BCL1IE SSP1IE       |         |      |      |      |  |

| PIR3     | RC2IF    | TX2IF                                  | RC1IF   | TX1IF       | TX1IF BCL2IF SSP2IF BCL1IF SSP1IF       |         |      |      |      |  |

| IPR3     | RC2IP    | TX2IP                                  | RC1IP   | TX1IP       | TX1IP BCL2IP SSP2IP BCL1IP SSP1IP       |         |      |      |      |  |

| RCxREG   |          |                                        | EUS     | ARTx Receiv | RTx Receive Data Register               |         |      |      |      |  |

| RCxSTA   | SPEN     | RX9                                    | SREN    | CREN        | CREN ADDEN FERR OERR RX9D               |         |      |      |      |  |

| RxyPPS   | _        | _                                      | _       |             | RxyPPS<4:0>                             |         |      |      |      |  |

| RXxPPS   | _        | _                                      | _       |             | RXPPS<4:0>                              |         |      |      |      |  |

| SPxBRGH  |          | EUSARTx Baud Rate Generator, High Byte |         |             |                                         |         | 404* |      |      |  |

| SPxBRGL  |          |                                        | EUSART  | x Baud Rate | Generator, Lo                           | ow Byte |      |      | 404* |  |

| TXxSTA   | CSRC     | TX9                                    | TXEN    | SYNC        | SENDB                                   | BRGH    | TRMT | TX9D | 393  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

# REGISTER 31-4: ADCON3: ADC CONTROL REGISTER 3

| U-0     | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W/HC-0 | R/W-0/0 | R/W-0/0    | R/W-0/0 |

|---------|---------|-------------|---------|----------|---------|------------|---------|

| _       |         | ADCALC<2:0> |         | ADSOI    |         | ADTMD<2:0> |         |

| bit 7   |         |             |         |          |         |            | bit 0   |

|         |         |             |         |          |         |            |         |

| Legend. |         |             |         |          |         |            |         |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 ADCALC<2:0>: ADC Error Calculation Mode Select bits

|        | Action During                                                                                            | 1st Precharge Stage   |                                                              |

|--------|----------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------|

| ADCALC | ADDSEN = 0         ADDSEN = 1 CVD           Single-Sample Mode         Double-Sample Mode <sup>(1)</sup> |                       | Application                                                  |

| 111    | Reserved                                                                                                 | Reserved              | Reserved                                                     |

| 110    | Reserved                                                                                                 | Reserved              | Reserved                                                     |

| 101    | ADLFTR-ADSTPT                                                                                            | ADFLTR-ADSTPT         | Average/filtered value vs. setpoint                          |

| 100    | ADPREV-ADFLTR                                                                                            | ADPREV-ADFLTR         | First derivative of filtered value <sup>(3)</sup> (negative) |

| 011    | Reserved                                                                                                 | Reserved              | Reserved                                                     |

| 010    | ADRES-ADFLTR                                                                                             | (ADRES-ADPREV)-ADFLTR | Actual result vs.<br>averaged/filtered value                 |

| 001    | ADRES-ADSTPT                                                                                             | (ADRES-ADPREV)-ADSTPT | Actual result vs.setpoint                                    |

| 000    | ADRES-ADPREV                                                                                             | ADRES-ADPREV          | First derivative of single measurement <sup>(2)</sup>        |

|        |                                                                                                          |                       | Actual CVD result in CVD mode <sup>(2)</sup>                 |

bit 3 ADSOI: ADC Stop-on-Interrupt bit

#### If ADCONT = 1:

- 1 = ADGO is cleared when the threshold conditions are met, otherwise the conversion is retriggered

- 0 = ADGO is not cleared by hardware, must be cleared by software to stop retriggers

#### bit 2-0 ADTMD<2:0>: Threshold Interrupt Mode Select bits

- 111 = Interrupt regardless of threshold test results

- 110 = Interrupt if ADERR>ADUTH

- 101 = Interrupt if ADERR≤ADUTH

- 100 = Interrupt if ADERR<ADLTH or ADERR>ADUTH

- 011 = Interrupt if ADERR>ADLTH and ADERR<ADUTH

- 010 = Interrupt if ADERR≥ADLTH

- 001 = Interrupt if ADERR<ADLTH

- 000 = Never interrupt

- Note 1: When ADPSIS = 0, the value of ADRES-ADPREV) is the value of (S2-S1) from Table 31-3.

- 2: When ADPSIS = 0

- 3: When ADPSIS = 1.

# PIC18(L)F26/45/46K40

| BTFSC                                                                                     | Bit Test Fil                                                                                                                                                                                                                 | e, Skip if Cle                                                                                                                                                                                                                                                                                 | ear                                                                                                                                                                                                  | BTFSS                | Bit Te                                                                                                                                         | est File, Ski                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ip if Set        |                 |  |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--|

| Syntax:                                                                                   | BTFSC f, b                                                                                                                                                                                                                   | {,a}                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      | Syntax:              | BTFS                                                                                                                                           | BTFSS f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                 |  |

| Operands:                                                                                 | Operands:                                                                                                                                                                                                                    | 0 ≤ f ≤<br>0 ≤ b ·<br>a ∈ [0                                                                                                                                                                                                                                                                   | < 7                                                                                                                                                                                                  |                      |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                 |  |

| Operation:                                                                                | peration: $skip \text{ if } (f < b >) = 0$ Operation: $skip \text{ if } (f < b >) = 1$                                                                                                                                       |                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                      |                      |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                 |  |